Professional Documents

Culture Documents

A Low Power Efficient Design of Full Adder Using Transmission Gates

Uploaded by

surendar147Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Low Power Efficient Design of Full Adder Using Transmission Gates

Uploaded by

surendar147Copyright:

Available Formats

International Journal of Communication and Computer Technologies

Volume 05 No. 09, Issue: 01 March 2017

ISSN NUMBER : 2278-9723

A LOW POWER EFFICIENT DESIGN OF FULL

ADDER USING TRANSMISSION GATES

P.Alagu Pandian1 K.Sakthivel2 K.Sheik Alavudeen3 R.Lakshmi Priya4

UG Student123 Assistant Professor of Electronics and Communication Engineering4,

Theni Kammavar Sangam College of Technology, Theni

Abstract: A Full adder circuit is a very important component of the design of integrated circuits in VLSI design. In this paper

represents a full adder using transmission gates at supply voltage is 1.8 dc voltages. The result of the post layout simulation (using

CADENCE EDA TOOL) have been compare with the results of similar previously reported for adder circuits. In this proposed

transmission gate circuits is very high efficient in terms of power, delay and area consumption compare too many other full adder

circuits.

Key words: Pass Transistor Logic (PTL), Power-Delay Product (PDP), and Transmission gate (TG), Electronic Design Automation (EDA).

I.INTRODUCTION II.FULL ADDER BASICS

Full adder is a fundamental unit of arithmetic The full adder circuit have three inputs a, b & c and

operations. The important parameters of VLSI system in the outputs will be Sum and carry. Fig.1 shows basic block

measuring performance based speed, coverage area & power diagram of full adder.

consumption. High efficient circuits are desirable for any

electronics gadgets. For supporting hardware should be

equally inexpensive and compact. Arithmetic operations are

useful in all the digital electronics system like digital image

processing, image processing, video processing, arithmetic

and logical units. Designing of low power and high speed full

adder circuits with better performance. Here the full adders are

designed with less supply voltages. Performance analysis is

measured by taking different considerations like power

consumption, total propagation delay and transistor count. In

our work, a new transmission gates based 1 bit full adder has

been proposed in its designing of improving performance.

This paragraph of the first footnote will contain the date on which you

submitted your paper for review. It will also contain support information,

including sponsor and financial support acknowledgment. For example,

This work was supported in part by the U.S. Department of Commerce

under Grant BS123456.

The next few paragraphs should contain the authors current affiliations, Fig.1 Full adder circuit

including current address and e-mail. For example, F. A. Author is with the

National Institute of Standards and Technology, Boulder, CO 80305 USA III.PREVIOUS WORK

(e-mail: author@ boulder.nist.gov).

S. B. Author, Jr., was with Rice University, Houston, TX 77005 USA. The existing design of NMOS based low power 1 bit full

He is now with the Department of Physics, Colorado State University, Fort

Collins, CO 80523 USA (e-mail: author@lamar.colostate.edu).

adder has been designed using PTL technique. The existing

T. C. Author is with the Electrical Engineering Department, University adder has shown in fig.2

of Colorado, Boulder, CO 80309 USA, on leave from the National

Research Institute for Metals, Tsukuba, Japan (e-mail: author@nrim.go.jp).

Volume 05 No.8, Issue: 01 Page 61

International Journal of Communication and Computer Technologies www.ijccts.org

International Journal of Communication and Computer Technologies

Volume 05 No. 09, Issue: 01 March 2017

ISSN NUMBER : 2278-9723

IV.PROPOSED WORK

A transmission gate is both PMOS and NMOS parallel with

each other. It is similar to a relay that can conduct in both

directions. It is CMOS based switch in which PMOS passes

a strong 1 but poor 0 and NMOS passes strong 0 but poor 1.

Both PMOS and NMOS work together simultaneously.

The Proposed design is transmission gates of low power 1

bit full adder shown in fig.3

Fig.2 Existing 1 bit full adder

Sum = A B C

And Carry = AB + BC + CA

= AB + BC (A+A) + CA (B+B)

= AB + ABC + ABC + ABC

= AB (1+C) + (AB + AB) C

= AB + (A B) C

The first transistor M1 is generating output AB

while M3 is generating AB. The two outputs together

generate (A B) at point p. Outputs of M2 and M4 are

AB and AB respectively. It produce (A B) after

meeting at point q. The logic at the outputs of M5 and M6

are (A B) C and (A B) C. So the Sum output is

Fig.3 The Proposed adder circuit

Sum = (A B) C + (A B) C = A B C

Similarly, the output logics of M7 and M8, (A B) A and V.SIMULATION RESULTS

(A B) C, together generate Carry output as:

Carry = (A B) A + (A B) C

= (AB + AB) A + (A B) C

= AB + (A B) C

The logic values at the output levels are listed in Table 1:

A B C M M M M M M M M Sum Carry

1 2 3 4 5 6 7 8

0 0 0 0 1 0 0 0 0 0 0 0 0

0 0 1 0 1 0 0 0 1 0 0 1 0

0 1 0 0 0 1 0 1 0 0 0 1 0

0 1 1 0 0 1 0 0 0 0 1 0 1

1 0 0 1 0 0 0 1 0 0 0 1 0

1 0 1 1 0 0 0 0 0 0 1 0 1

1 1 0 0 0 0 1 0 0 1 0 0 1

1 1 1 0 0 0 1 0 1 1 0 1 1 Fig.4 Schematic Of Existing Design

Table1. Truth table of existing full adder

Volume 05 No.8, Issue: 01 Page 62

International Journal of Communication and Computer Technologies www.ijccts.org

International Journal of Communication and Computer Technologies

Volume 05 No. 09, Issue: 01 March 2017

ISSN NUMBER : 2278-9723

VI.CONCLUSION

In this paper, the proposed design of transmission gates

using 1 bit full adder is very useful technique to reduce

power and chip area. So we conclude the transmission gate

design analysis is to find better results compare to previous

design of full adders. The Performance degradation and the

internal load capacitance of this circuit are much less

compared to previous design. So the proposed full adder

circuit provides better power delay product compared to

NMOS based 1 bit full adder.

Fig.5 Output of Existing Design REFERENCES

[1] De banjana data, Debarshi Datta, A novel power

efficient N-MOS based 1 bit full adder IEEE

issue,2016.

[2 ] Weste and K. Eshraghian, Principles of of CMOS

VLSI Design, A System prospective, 1993.

[3] A. M. Shams and M. Bayoumi, A novel high-

performance CMOS1- bit full adder cell, IEEE

Transaction on Circuits Systems II, Analog Digital

Fig.5 Schematic Of Proposed Design Signal Process, Vol. 47, no. 5, pp. 478481, May,

2000.

[4] M. Kumar, S. K. Arya and S. Pandey, Single bit

full adder design using 8 transistors with novel 3

transistors XNOR gate, International Journal of

VLSI design & Communication Systems (VLSICS)

Vol.2, No.4, December, 2011.

[5] Surendar, A., M. Arun, and P. S. Periasamy. "A

parallel reconfigurable platform for efficient

sequence alignment." African Journal of

Biotechnology 13.33 (2014).

Fig.5 Schematic Of Proposed Design

[6] Surendar, A., and M. Arun. "Efficient DNA

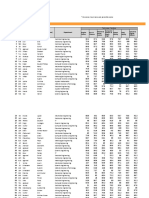

VI.RESULTS COMPARISON Sequence Analysis for Reduced Gene

Design Power Delay PDP Selection Using Frequency Analysis."

N-MOS based [7] Reddy, and G. Karthik, "Low power-area designs of

807.82uW 9.354102ns 7.5664PJ

full adder

1bit full adder in cadence virtuoso platform,"

Transmission International Journal of VLSI Design &

Gates using full 737.69uW 1.25337ns 0.9245PJ Communication Systems, 2013.

adder

Table 2. Results comparison

Volume 05 No.8, Issue: 01 Page 63

International Journal of Communication and Computer Technologies www.ijccts.org

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- A Sourcebook in Chinese LongevityDocument34 pagesA Sourcebook in Chinese Longevitytanpausing67% (3)

- Manual de Servicio CX 350B 84355067-Dmc Site OnlyDocument127 pagesManual de Servicio CX 350B 84355067-Dmc Site Onlyabel jairo santos cabello100% (2)

- Fruits Basket - MemoryDocument1 pageFruits Basket - Memorywane10132100% (1)

- Bus Depot Design Guidelines PDFDocument102 pagesBus Depot Design Guidelines PDFgregoblue100% (2)

- SmartForm - Invoice TutorialDocument17 pagesSmartForm - Invoice TutorialShelly McRay100% (5)

- Zerkle Dalcroze Workshop HandoutDocument2 pagesZerkle Dalcroze Workshop HandoutEricDoCarmoNo ratings yet

- How To Build TelescopeDocument50 pagesHow To Build TelescopeSachin VermaNo ratings yet

- Astm D448Document3 pagesAstm D448Mutyaba Johnson100% (5)

- College Management System Based On ArduinoDocument4 pagesCollege Management System Based On Arduinosurendar147No ratings yet

- 3dtransistors 131104120433 Phpapp01Document18 pages3dtransistors 131104120433 Phpapp01surendar147No ratings yet

- Sensor Node Failure Detection Using Round Trip Delay in Wireless Sensor NetworkDocument9 pagesSensor Node Failure Detection Using Round Trip Delay in Wireless Sensor Networksurendar147No ratings yet

- Smart Ticket MachineDocument5 pagesSmart Ticket Machinesurendar1470% (1)

- Energy Sentient Qos Implemented Node-Disjoint Multipath Routing Protocolfor ManetDocument10 pagesEnergy Sentient Qos Implemented Node-Disjoint Multipath Routing Protocolfor Manetsurendar147No ratings yet

- Design of Planar Antenna Using Micro Strip Feed For Biomedical ApplicationsDocument7 pagesDesign of Planar Antenna Using Micro Strip Feed For Biomedical Applicationssurendar147No ratings yet

- 3 WirelessDocument3 pages3 Wirelesssurendar147No ratings yet

- Automatic Street Light Control System Using WSN Based On Vehicle Movement and Atmospheric ConditionDocument8 pagesAutomatic Street Light Control System Using WSN Based On Vehicle Movement and Atmospheric Conditionsurendar147No ratings yet

- 6-Bit, 180nm Digital To Analog Converter (DAC) Using Tanner EDA Tool For Low Power ApplicationsDocument7 pages6-Bit, 180nm Digital To Analog Converter (DAC) Using Tanner EDA Tool For Low Power Applicationssurendar147No ratings yet

- International Conference On Advances in Electrical, Electronics and Computational Intelligence (Icaeeci'16)Document542 pagesInternational Conference On Advances in Electrical, Electronics and Computational Intelligence (Icaeeci'16)surendar147No ratings yet

- Paper ID - EC087 - : Registration FormDocument2 pagesPaper ID - EC087 - : Registration Formsurendar147No ratings yet

- Hour Att SlipDocument1 pageHour Att Slipsurendar147No ratings yet

- V4I206Document8 pagesV4I206surendar147No ratings yet

- Mg2351 PomDocument83 pagesMg2351 Pomsurendar147100% (2)

- VLSIDocument22 pagesVLSIMoulana YasinNo ratings yet

- Lesson Plan CMOSDocument3 pagesLesson Plan CMOSsurendar147No ratings yet

- Terminal 2Document3 pagesTerminal 2surendar147No ratings yet

- 15G FormDocument2 pages15G Formsurendar147No ratings yet

- EE423 Syllabus Teaching Plan Spring 2012GDocument2 pagesEE423 Syllabus Teaching Plan Spring 2012Gsurendar147No ratings yet

- ECE II To VIIIDocument119 pagesECE II To VIIIEce ThirdyearNo ratings yet

- Antenna & Wave PropagationDocument14 pagesAntenna & Wave Propagationsurendar147No ratings yet

- Hour Att SlipDocument1 pageHour Att Slipsurendar147No ratings yet

- B. Extra BooksDocument3 pagesB. Extra Bookssurendar147No ratings yet

- Microprocessors and Micro ControllersDocument1 pageMicroprocessors and Micro Controllerssurendar147No ratings yet

- SundarDocument2 pagesSundarsurendar147No ratings yet

- Safety Instrumented Systems SummersDocument19 pagesSafety Instrumented Systems SummersCh Husnain BasraNo ratings yet

- Delegate Handbook: The National Final of The Evatt Trophy CompetitionDocument19 pagesDelegate Handbook: The National Final of The Evatt Trophy Competitionevatt2012No ratings yet

- STIers Meeting Industry ProfessionalsDocument4 pagesSTIers Meeting Industry ProfessionalsAdrian Reloj VillanuevaNo ratings yet

- 2998 1-Emt Fibre Optic Cable-Cat LRDocument32 pages2998 1-Emt Fibre Optic Cable-Cat LRsubramanyaNo ratings yet

- Abstract - Freezing Point Depression Is ADocument5 pagesAbstract - Freezing Point Depression Is AMinahNo ratings yet

- MODBUSDocument19 pagesMODBUSJosé Luis MartínezNo ratings yet

- Proposal Kerja PraktekDocument11 pagesProposal Kerja PraktekBilly Dentiala Irvan100% (1)

- Innoventure List of Short Listed CandidatesDocument69 pagesInnoventure List of Short Listed CandidatesgovindmalhotraNo ratings yet

- SAHCorporateBrochure WEBDocument72 pagesSAHCorporateBrochure WEBKrsna SinghNo ratings yet

- Belarc Advisory I7g8Document5 pagesBelarc Advisory I7g8Roberto AlladoNo ratings yet

- 23 Encoding PDFDocument5 pages23 Encoding PDFBharghav RoyNo ratings yet

- Airworthiness Officer QuestionDocument1 pageAirworthiness Officer QuestionnanthakumarmaniNo ratings yet

- Exp#4-Gas TurbineDocument9 pagesExp#4-Gas TurbineLilo17xiNo ratings yet

- IO Chapter6 FinalDocument10 pagesIO Chapter6 FinalJulia MoplaNo ratings yet

- 9 Clonezilla LiveDocument4 pages9 Clonezilla LivegixplayNo ratings yet

- Fieldglass Testing DocmentDocument32 pagesFieldglass Testing DocmentAthul NairNo ratings yet

- Dürer's Rhinoceros Springer Esteban JMDocument29 pagesDürer's Rhinoceros Springer Esteban JMmiguelestebanNo ratings yet

- PreliminaryDocument65 pagesPreliminarysame.pxtNo ratings yet

- Labour WelfareDocument250 pagesLabour WelfareArundhathi AdarshNo ratings yet

- Vmod Pht3d TutorialDocument32 pagesVmod Pht3d TutorialluisgeologoNo ratings yet

- Tables Log ActivatedDocument575 pagesTables Log ActivateddcdiasNo ratings yet

- Maria Bolboaca - Lucrare de LicentaDocument68 pagesMaria Bolboaca - Lucrare de LicentaBucurei Ion-AlinNo ratings yet