Professional Documents

Culture Documents

Cb3lv-3i 100M0000

Uploaded by

amiteshtripathiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cb3lv-3i 100M0000

Uploaded by

amiteshtripathiCopyright:

Available Formats

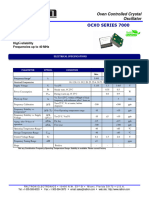

Model CB3 & CB3LV

HCMOS/TTL Clock Oscillator

FEATURES

Standard 7.0mm x 5.0mm 4-Pad Surface Mount Package

HCMOS/TTL Compatible Output

Fundamental and 3rd Overtone Crystal Designs

Frequency Range 1 200 MHz

Frequency Stability 50 ppm Standard, 25 ppm and 20 ppm Available

Operating Voltages +5.0Vdc or +3.3Vdc

Operating Temperature to -40C to +85C

Output Enable Standard

Tape & Reel Packaging

RoHS/Green Compliant (6/6)

APPLICATIONS

Applications for Model CB3 and CB3LV include digital video, networking equipment, wireless communications,

broadband access, Ethernet/Gigabit Ethernet, microprocessors/DSP/FPGA, storage area networks, fiber channel,

computers and peripherals, test and measurement, SONET/SDH/DWDM, base stations and Pico cells.

ORDERING INFORMATION

CB3 - - M

SUPPLY VOLTAGE FREQUENCY IN MHz

LV = +3.3Vdc 3

M - indicates MHz and decimal point.

Blank = +5.0Vdc

FREQUENCY STABILITY OPERATING TEMPERATURE RANGE

1 C = -20C to +70C [standard]

6 = 20 ppm 7 = 32 ppm

2

5 = 25 ppm 2

I = -40C to +85C 1

2 = 100 ppm

3 = 50 ppm [std]

1] 6I Stability/Temperature combination is not available.

2] These stabilities are not recommended for new designs.

3] Frequency is recorded with only leading significant digits before the M and 4 - 6 significant digits after the M (including zeros).

[Ex. 3.579545 MHz, code as 3M579545; 14.31818 MHz, code as 14M31818; 125 MHz, code as 125M0000]

4] CTS Distributors may add a -T or -1 at the end of the part number to indicate Tape and Reel packaging.

Not all performance combinations and frequencies may be available.

Contact your local CTS Representative or CTS Customer Service for availability.

PACKAGING INFORMATION [reference]

Device quantity is 1,000 pieces maximum per reel.

Document No. 008-0256-0 Page 1- 3 Rev. G

www.ctscorp.com

Model CB3 & CB3LV

7.0mm x 5.0mm Low Cost

HCMOS/TTL Clock Oscillator

ELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT

Maximum Supply Voltage VCC - -0.5 - +7.0 V

Storage Temperature TSTG - -40 - +100 C

Frequency Range

CB3 fO - 1.5 - 107 MHz

CB3LV - 1.5 - 200

Frequency Stability f/fO See Note 1 and Ordering Information - - 20,25,50 or 100 ppm

Aging f First year - 3 5 ppm

Operating Temperature

Commercial TA - -20 +70 C

25

Industrial -40 +85

Supply Voltage

CB3 VCC 10% 4.5 5.0 5.5 V

CB3LV 3.0 3.3 3.6

Supply Current Frequency Range

Tested load condition noted for typical values.

CB3 1.5MHz to 20MHz CL=50pF - 10 25

20.001MHz to 80MHz CL=50pF - 30 50

ICC CL=15pF mA

80.001MHz to 107MHz - 40 80

CB3LV 1.5MHz to 20MHz CL=15pF - 7 12

20.001MHz to 80MHz CL=15pF - 20 40

80.001MHz to 200MHz CL=15pF - 30 60

ELECTRICAL PARAMETERS

1.5MHz to 50MHz - - 50

Output Load CL 50.001MHz to 80MHz - - 30 pF

80.001MHz to 200MHz - - 15

Output Voltage Levels

Logic '1' Level CMOS Load 90%VCC

VOH - -

10 TTL LOAD VCC-0.6V V

Logic '0' Level CMOS 10%VCC

VOL - -

TTL Load 0.4

Output Current

Logic '1' Level IOH VOH = 3.9V/2.2V VCC = 4.5V/3.0V - - -16/-8 mA

Logic '0' Level IOL VOL = 0.4V VCC = 4.5V/3.0V - - +16/+8

Output Duty Cycle SYM @ 50% Level 45 - 55 %

Rise and Fall Time @ 10% - 90% Levels

Tested load condition noted for typical values.

CB3 1.5MHz to 20MHz CL=50pF - 8 10

20.001MHz to 80MHz CL=50pF - 5 8

TR, TF CL=15pF ns

80.001MHz to 200MHz - 2.5 5

CB3LV 1.5MHz to 20MHz CL=15pF - 6 8

20.001MHz to 80MHz CL=15pF - 3 5

80.001MHz to 200MHz CL=15pF - 1.5 3

Start Up Time TS Application of VCC - - 10 ms

Enable Function

Enable Input Voltage VIH Pin 1 Logic '1', Output Enabled 2.0 - - V

Disable Input Voltage VIL Pin 1 Logic '0', Output Disabled - - 0.8

Enable Time TPLZ Pin 1 Logic '1' - - 200 ns

Standby Current IST Pin 1 Logic '0', Output Disabled - - 10 A

Period Jitter, Pk-Pk - - - - 50

Period Jitter, RMS - - - - 5 ps

Phase Jitter, RMS - Bandwidth 12kHz - 20MHz - - 1

Notes:

1. Inclusive of initial tolerance at time of shipment, changes in supply voltage, load, temperature and 1st year aging.

Document No. 008-0256-0 Page 2 - 3 Rev. G

Model CB3 & CB3LV

7.0mm x 5.0mm Low Cost

HCMOS/TTL Clock Oscillator

ELECTRICAL CHARACTERISTICS

LVCMOS OUTPUT WAVEFORM TEST CIRCUIT, CMOS LOAD

ENABLE TRUTH TABLE D.U.T. PIN ASSIGNMENTS

PIN SYMBOL DESCRIPTION

PIN 1 PIN 3

Logic 1 Output 1 EOH Enable

Open Output 2 GND Circuit & Package Ground

Logic 0 High Imp.

3 Output RF Output

4 VCC Supply Voltage

MECHANICAL SPECIFICATIONS

PACKAGE DRAWING MARKING INFORMATION

1. ** Manufacturing Site Code.

[Note a dash may follow the site code and is acceptable.]

2. XXXMXXXXXX Frequency is marked with only

leading significant digits before the M and

4 6 digits after the M (including zeros).

CTS**CB3 Ex. XMXXXXXX [3M579545]

XXMXXXXX [14M31818]

XXXMXXXXXX XXXMXXXX [125M0000]

YYWWSTV 3. YYWW Date code, YY year, WW week.

4. ST Frequency stability/temperature code.

[Refer to Ordering Information.]

5. V Voltage code. 3 = 3.3V, 5 = 5.0V.

NOTES

1. Termination pads [e4]. Barrier-plating is nickel

[Ni] with gold [Au] flash plate.

2. Reflow conditions per JEDEC J-STD-020, 260C

maximum.

3. Moisture Sensitivity Level 1 per JEDEC J-STD-020.

SUGGESTED SOLDER PAD GEOMETRY

CBYPASS should be 0.01 uF.

Document No. 008-0256-0 Page 3 - 3 Rev. G

You might also like

- Datasheet 636Document4 pagesDatasheet 636agus satyaNo ratings yet

- Ecs 3225S-1064150Document3 pagesEcs 3225S-1064150miri10861No ratings yet

- Tcxo - 0749c Older Datasheet - Presently Using in LewDocument3 pagesTcxo - 0749c Older Datasheet - Presently Using in LewMohendra PatiNo ratings yet

- Ecs Txo 2520Document2 pagesEcs Txo 2520miri10861No ratings yet

- Standard Specifications:: Applications: FeaturesDocument3 pagesStandard Specifications:: Applications: FeaturesNguyen HuanNo ratings yet

- ABL Series: Standard SpecificationsDocument3 pagesABL Series: Standard SpecificationsVinny SinghNo ratings yet

- STC53K SeriesDocument4 pagesSTC53K SeriesonallpelinNo ratings yet

- Parameters Minimum Typical Maximum Units NotesDocument4 pagesParameters Minimum Typical Maximum Units NotesKiran PatelNo ratings yet

- Vectron: InternationalDocument5 pagesVectron: Internationalm3y54mNo ratings yet

- QCL Series: General Specifi Cations Equivalent Series Resistance (ESR)Document2 pagesQCL Series: General Specifi Cations Equivalent Series Resistance (ESR)Alberto Fernández VázquezNo ratings yet

- SiT1552 DatasheetDocument12 pagesSiT1552 DatasheetMustafa TuncNo ratings yet

- ABM8GDocument2 pagesABM8GJorge LealNo ratings yet

- Abracom ABM3Document2 pagesAbracom ABM3Joseph Abou El OulaNo ratings yet

- Abm8Aig Abm8AigDocument4 pagesAbm8Aig Abm8AigpepeNo ratings yet

- ABMMDocument2 pagesABMMenrique.ci.martinezNo ratings yet

- OX7000 Series DatasheetDocument4 pagesOX7000 Series Datasheetsanjubonik2017No ratings yet

- NIC Components NAWE SeriesDocument4 pagesNIC Components NAWE SeriesNICCompNo ratings yet

- MF-2500DS-T12-18x/19x/20x/21x MF-2500DS-R13-18x MF-2500DS-R14-19x/20x/21xDocument9 pagesMF-2500DS-T12-18x/19x/20x/21x MF-2500DS-R13-18x MF-2500DS-R14-19x/20x/21xGabriel RacovskyNo ratings yet

- NTH089 C3Document3 pagesNTH089 C3Javier LopezNo ratings yet

- OLT-C-Optical-Module PotenciasDocument8 pagesOLT-C-Optical-Module PotenciasWilmer MonteroNo ratings yet

- BR93H86RF-2LB: 125 Operation Microwire BUS EEPROM (3-Wire)Document29 pagesBR93H86RF-2LB: 125 Operation Microwire BUS EEPROM (3-Wire)Tomi OzzyNo ratings yet

- ABNTC-0201: MSL Level: 2A (This Product Is Packed With Dry Packaging)Document3 pagesABNTC-0201: MSL Level: 2A (This Product Is Packed With Dry Packaging)ricky syandiNo ratings yet

- Standard Specifications:: Applications: FeaturesDocument2 pagesStandard Specifications:: Applications: FeaturespepeNo ratings yet

- SP GB LX CDFM ZTDocument9 pagesSP GB LX CDFM ZTJoyner Daniel Garcia DuarteNo ratings yet

- 40-000MHZX09 DatasheetDocument2 pages40-000MHZX09 DatasheetsongdashengNo ratings yet

- 50-000MHZX09 DatasheetDocument2 pages50-000MHZX09 DatasheetsongdashengNo ratings yet

- 6C WDM 0220BDDocument7 pages6C WDM 0220BDNugi Anugrah M1221562No ratings yet

- TS0021ADocument8 pagesTS0021AitflyiljulwhzthzxfNo ratings yet

- Abl 16.000MHZ B2 PDFDocument3 pagesAbl 16.000MHZ B2 PDFkarthik4096No ratings yet

- TS0016ADocument8 pagesTS0016AitflyiljulwhzthzxfNo ratings yet

- Typical Applications Features: 10 MHZ - 200 MHZ 10, 19.44, 20.48, 38.88, 77.76MhzDocument6 pagesTypical Applications Features: 10 MHZ - 200 MHZ 10, 19.44, 20.48, 38.88, 77.76MhzdexkezzNo ratings yet

- 6C WDM 0240adDocument7 pages6C WDM 0240adIdris KusumaNo ratings yet

- SMD Crystal: Operating Conditions / Electrical CharacteristicsDocument2 pagesSMD Crystal: Operating Conditions / Electrical CharacteristicsManu MathewNo ratings yet

- ABMM2Document3 pagesABMM2QAISER IJAZNo ratings yet

- 6C WDM 0240BDDocument7 pages6C WDM 0240BDIdris KusumaNo ratings yet

- 40GBASE-ZR4 QSFP+ 1310nm 80km DDM SMF Transceiver P/N: QT-QSFP+-ZR4Document12 pages40GBASE-ZR4 QSFP+ 1310nm 80km DDM SMF Transceiver P/N: QT-QSFP+-ZR4Utel TVNo ratings yet

- Ecs 2520SMV EcsDocument2 pagesEcs 2520SMV EcsVictor GomesNo ratings yet

- F230TSDocument2 pagesF230TScuentadosngrokNo ratings yet

- Anexa 3 Qxp85b4 02d ViDocument14 pagesAnexa 3 Qxp85b4 02d Vistelea7577No ratings yet

- 1.25Gb 20klm 1490T-1310R SM (Standard Code)Document6 pages1.25Gb 20klm 1490T-1310R SM (Standard Code)Sean SerinNo ratings yet

- SiT1534 Rev1p31Document12 pagesSiT1534 Rev1p31Oleh SehedaNo ratings yet

- SiT1533 Rev1.4 03202018Document13 pagesSiT1533 Rev1.4 03202018Oleh SehedaNo ratings yet

- Dsk321std Car enDocument1 pageDsk321std Car en천일계전No ratings yet

- 7W-25.000MBA - CMOS OscillatorsDocument2 pages7W-25.000MBA - CMOS OscillatorsLau LauNo ratings yet

- NIC Components NMC High CV SeriesDocument4 pagesNIC Components NMC High CV SeriesNICCompNo ratings yet

- Abls7M2: Standard SpecificationsDocument5 pagesAbls7M2: Standard Specificationssteven MelgarejoNo ratings yet

- 1.25Gb 20klm SM 1550nm LC (Cisco Coded)Document7 pages1.25Gb 20klm SM 1550nm LC (Cisco Coded)Sean SerinNo ratings yet

- Description Features: 1 To 26 Mhz, Ultra-Small Μpower OscillatorDocument10 pagesDescription Features: 1 To 26 Mhz, Ultra-Small Μpower OscillatorSantiago OspinaNo ratings yet

- Shenzhen Hifibercom Technology Co.,Ltd 10G Bidi 20km Optical ModuleDocument8 pagesShenzhen Hifibercom Technology Co.,Ltd 10G Bidi 20km Optical Modulehifibercom comNo ratings yet

- D O S O: Ifferential Utput Ilicon ScillatorDocument8 pagesD O S O: Ifferential Utput Ilicon ScillatorkynixNo ratings yet

- ASDMBDocument5 pagesASDMBTcppunkNo ratings yet

- AXIOM75 50 25 1B - Rev.6 10.000MHzDocument4 pagesAXIOM75 50 25 1B - Rev.6 10.000MHzTürkay PektürkNo ratings yet

- Cfps 72 73Document2 pagesCfps 72 73Istvan KovasznaiNo ratings yet

- HYG050N10NS1MFDocument10 pagesHYG050N10NS1MFequimarNo ratings yet

- KI 118F Specifiaction1Document3 pagesKI 118F Specifiaction1tierranuevaNo ratings yet

- Features Applications: 220 To 725 MHZ Ultra-Low Jitter Differential OscillatorDocument12 pagesFeatures Applications: 220 To 725 MHZ Ultra-Low Jitter Differential OscillatorÇağrı GürleyükNo ratings yet

- Datasheet TP TemperatureDocument12 pagesDatasheet TP Temperaturebtheo91190No ratings yet

- 1.25Gb/s SFP (Small Form Pluggable) Long Wavelength (1310nm) TransceiverDocument8 pages1.25Gb/s SFP (Small Form Pluggable) Long Wavelength (1310nm) TransceiverHuy DoanNo ratings yet

- Product Features: Applications:: 3.2 MM X 5 MM Ceramic Package SMD TCXODocument2 pagesProduct Features: Applications:: 3.2 MM X 5 MM Ceramic Package SMD TCXOandcamiloq3199No ratings yet

- Samtec ASP 134488 01 DatasheetDocument4 pagesSamtec ASP 134488 01 DatasheetamiteshtripathiNo ratings yet

- Paper 22Document21 pagesPaper 22amiteshtripathiNo ratings yet

- Advanced MEMS Packaging 2017 (Class 1)Document24 pagesAdvanced MEMS Packaging 2017 (Class 1)amiteshtripathiNo ratings yet

- (Ebook - Electronics) - Analog and Mixed Signal Vlsi CircuitDocument418 pages(Ebook - Electronics) - Analog and Mixed Signal Vlsi CircuitPuja GuptaNo ratings yet

- Prohibited Properties in HyderbadDocument33 pagesProhibited Properties in HyderbadamiteshtripathiNo ratings yet

- VLSI Interview QuestionDocument17 pagesVLSI Interview QuestionamiteshtripathiNo ratings yet

- Pipelined Multistep AdcDocument40 pagesPipelined Multistep AdcamiteshtripathiNo ratings yet

- Defence Research and Development Organisation PDFDocument296 pagesDefence Research and Development Organisation PDFSourav MondalNo ratings yet

- Diagnostic Techniques For Vibration Analysis of BearingsDocument9 pagesDiagnostic Techniques For Vibration Analysis of BearingsMohd Asiren Mohd Sharif100% (1)

- DTFT From FTDocument4 pagesDTFT From FTGodwinNo ratings yet

- Article - The Truth and Untruth About Electrically Small Antennas John S. (Jack) Belrose, VE2CV, VY9CRCDocument8 pagesArticle - The Truth and Untruth About Electrically Small Antennas John S. (Jack) Belrose, VE2CV, VY9CRCResistor100% (1)

- Example For Configuring Intersecting ERPS Rings: S1720&S2700&S5700&S6720 Series Ethernet Switches Product DocumentationDocument9 pagesExample For Configuring Intersecting ERPS Rings: S1720&S2700&S5700&S6720 Series Ethernet Switches Product DocumentationWalterFilhoNo ratings yet

- Curso ETL 600 EnelvenDocument129 pagesCurso ETL 600 EnelvenfrbuenoNo ratings yet

- Recommended System Configuration - Products - FURUNODocument4 pagesRecommended System Configuration - Products - FURUNOrfffffNo ratings yet

- Bently Nevada MmsDocument30 pagesBently Nevada MmsMohamed Hamed100% (1)

- Analog AssignmentDocument3 pagesAnalog AssignmentSiti SarahNo ratings yet

- Assign Hysteresis Parameter For Ericsson BTS PowerDocument7 pagesAssign Hysteresis Parameter For Ericsson BTS Powermola argawNo ratings yet

- Ieee 802.11Document8 pagesIeee 802.11محمد حيدر انعيمNo ratings yet

- DSP Lab Expt 4 Manual EECE GITAM-1-6Document6 pagesDSP Lab Expt 4 Manual EECE GITAM-1-6gowri thumburNo ratings yet

- Analisa Harga: Pekerjaan: ElektrikalDocument2 pagesAnalisa Harga: Pekerjaan: ElektrikalMuhammad AndreNo ratings yet

- PDF Course Module 2 For Foundation of Inclusive and Special Education DDDocument24 pagesPDF Course Module 2 For Foundation of Inclusive and Special Education DDglennell castillanoNo ratings yet

- XXX Pol Panel Antenna: 790-960/2×1710-2170Mhz 65°/65° 15/18dbi 0-15°/0-8° MetDocument2 pagesXXX Pol Panel Antenna: 790-960/2×1710-2170Mhz 65°/65° 15/18dbi 0-15°/0-8° MetBie BieNo ratings yet

- Satellite SubstationDocument37 pagesSatellite SubstationjagadishNo ratings yet

- 2843 MPR038 MPR038ML1 Tridadi 4G 4101 11 4166 402 128 130038 1FBF6 35911 35912 35913 35914Document53 pages2843 MPR038 MPR038ML1 Tridadi 4G 4101 11 4166 402 128 130038 1FBF6 35911 35912 35913 35914Ikhsan Miner HakkuNo ratings yet

- 参量混频双光梳信道化接收机Document9 pages参量混频双光梳信道化接收机Gosoviet XINGNo ratings yet

- WSN Unit 4Document38 pagesWSN Unit 4Amol YadavNo ratings yet

- Project Review: by Vamsikrishna Chemudupati 14BEC0022Document35 pagesProject Review: by Vamsikrishna Chemudupati 14BEC0022VAMSIKRISHNA CHEMUDUPATI 14BEC0022No ratings yet

- Adc - DacDocument20 pagesAdc - DachandywriterNo ratings yet

- Cap 15 Transmission Lines CircuitDocument43 pagesCap 15 Transmission Lines CircuitRony BenitezNo ratings yet

- 3GPP TR - 125942v110000pDocument137 pages3GPP TR - 125942v110000ppontoeengenhariaNo ratings yet

- OFDM Air InterfaceDocument351 pagesOFDM Air InterfaceYousaf Real EstatewalaNo ratings yet

- Fibre-Optics: 21st Century Communication BackboneDocument12 pagesFibre-Optics: 21st Century Communication BackboneНеля ЗаяцNo ratings yet

- High Efficiency Vehicle Bomb JammerDocument4 pagesHigh Efficiency Vehicle Bomb Jammerjax almarNo ratings yet

- Unit - 2 Diff Amp Objective QuestionsDocument3 pagesUnit - 2 Diff Amp Objective QuestionsRaviNo ratings yet

- Series Operation ManualDocument8 pagesSeries Operation ManualVion VionNo ratings yet

- MC 22 ManDocument11 pagesMC 22 Manrobelamare617No ratings yet

- Wireless Data Encryption and Decryption Using RFDocument4 pagesWireless Data Encryption and Decryption Using RFsanthosh100% (1)