Professional Documents

Culture Documents

Lecture B

Uploaded by

M Madan GopalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture B

Uploaded by

M Madan GopalCopyright:

Available Formats

i oh C842 NE CE

U M & A saxeT

ECEN248 Texas A&M University

Sections: Choi

Introduction to Digital Logic Design

With Verilog Lab

Lecture B

-Logic Minimization and Manipulation

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.1. The function f (x1, x2, x3) = m(0, 2, 4, 5, 6).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2 x1

x2

0 0 m0 0 1

0 1 m1 0 m0 m2

1 0 m2

1 m1 m3

1 1 m3

(a) Truth table (b) Karnaugh map

Figure 4.2. Location of two-variable minterms.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

x2

0 1

0 1 0

f = x2 + x1

1 1 1

Figure 4.3. The function of Figure 2.15.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2 x3

x1 x2

0 0 0 m0 x3

00 01 11 10

0 0 1 m1

0 m0 m2 m6 m4

0 1 0 m2

0 1 1 m3 1 m1 m3 m7 m5

1 0 0 m4

1 0 1 m5 (b) Karnaugh map

1 1 0 m6

1 1 1 m7

(a) Truth table

Figure 4.4. Location of three-variable minterms.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1x2

x3

00 01 11 10

0 0 0 1 1

f = x1x3 + x2x3

1 1 0 0 1

(a) The function of Figure 2.18

x1x2

x3

00 01 11 10

0 1 1 1 1

f = x3 + x x2

1 0 0 0 1 1

(b) The function of Figure 4.1

Figure 4.5. Examples of three-variable Karnaugh maps.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

x1 x2

x3 x4

00 01 11 10

00 m0 m4 m 12 m8

01 m1 m5 m 13 m9

x4

11 m3 m7 m 15 m 11

x3

10 m2 m6 m 14 m 10

x2

Figure 4.6. A four-variable Karnaugh map.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2 x1x2

x3x4 x3 x4

00 01 11 10 00 01 11 10

00 0 0 0 0 00 0 0 0 0

01 0 0 1 1 01 0 0 1 1

11 1 0 0 1 11 1 1 1 1

10 1 0 0 1 10 1 1 1 1

f 1 = x2x3 + x1 x3x4 f 2 = x3 + x1x4

x1 x2 x1x2

x3x4 x3 x4

00 01 11 10 00 01 11 10

00 1 0 0 1 00 1 1 1 0

01 0 0 0 0 01 1 1 1 0

11 1 1 1 0 11 0 0 1 1

10 1 1 0 1 10 0 0 1 1

x1x2

f 3 = x2x4 + x1x3 + x2x3x4 f 4 = x1 x3 + x1x3 + or

x2x3

Figure 4.7. Examples of four-variable Karnaugh maps.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2 x1 x2

x3 x4 x3 x4

00 01 11 10 00 01 11 10

00 00 1

01 1 1 01 1 1

11 1 1 11 1 1

10 1 1 10 1 1

x5 = 0 x5 = 1

f 1 = x1 x3 + x1 x3 x4 + x1 x2 x3 x5

Figure 4.8. A five-variable Karnaugh map.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2

x3

00 01 11 10

0 1 1 0 0

1 1 1 1 0

x x2 x3

1

Figure 4.9. Three-variable function f (x1, x2, x3) = m(0, 1, 2, 3, 7).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2

x3 x4

00 01 11 10

00 x1 x2 x4

01 1 1 x2 x3 x4

11 1 1 1

10 1 1 1 1 x x

3 4

x1 x3 x2 x3

Figure 4.10. Four-variable function f ( x1,, x4) =

m(2, 3, 5, 6, 7, 10, 11, 13, 14).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1x2

x3 x4

00 01 11 10

x3 x4

00 1 1 1 1

x1 x2 x3

01 1

x1 x2 x4

11 1 1 x1 x3 x4

10 1 x 1 x2 x3

x1 x2 x4

Figure 4.11. The function f ( x1,, x4) =

m(0, 4, 8, 10, 11, 12, 13, 15).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2

x3 x4

00 01 11 10

00 1 1 x 1 x 3 x4

01 1 1 x 2 x3 x4

11 1 1 x 1 x3 x4

10 1 1

x 2 x3 x4

x1 x2 x4 x1 x 2 x4

x1 x 2 x3 x 1 x2 x3

Figure 4.12. The function f ( x1,, x4) =

m(0, 2, 4, 5, 10, 11, 13, 15).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2

x3

00 01 11 10

0 1 1 0 0 ( x1 + x3)

1 1 1 1 0

( x1 + x2)

Figure 4.13. POS minimization of f (x1, x2, x3) = M(4, 5, 6).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2

x3x4

00 01 11 10

00 0 0 0 0 ( x3 + x4)

01 0 1 1 0

( x2 + x3)

11 1 1 0 1

10 1 1 1 1

( x1 + x2 + x3 + x4)

Figure 4.14. POS minimization of f ( x1,, x4) =

M(0, 1, 4, 8, 9, 12, 15).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1x2 x1x2

x3x4 x3x4

00 01 11 10 00 01 11 10

( x2 + x3)

00 0 1 d 0 00 0 1 d 0

x2 x3

01 0 1 d 0 01 0 1 d 0

11 0 0 d 0 11 0 0 d 0 ( x3 + x4)

10 1 1 d 1 x3 x4 10 1 1 d 1

(a) SOP implementation (b) POS implementation

Figure 4.15. Two implementations of the function f ( x1,, x4) =

m(2, 4, 5, 6, 10) + D(12, 13, 14, 15).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2

x3 x4

00 01 11 10

00 1 1

x2

01 1 1 1 x3

x4

11 1 1 f1

x1

10 1 1

x3

(a) Function f 1

x1

x1x2 x3

x3 x4 f2

00 01 11 10 x2

00 1 1 x3

x4

01 1 1

(c) Combined circuit for f 1 and f 2

11 1 1 1

10 1 1

(b) Function f 2

Figure 4.16. An example of multiple-output synthesis.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1x2 x1x2

x3x4 x3 x4

00 01 11 10 00 01 11 10

00 00

01 1 1 1 01 1 1 1

x1

11 1 1 1 11 1 1 1 x4

10 1 10 1 x1 f3

x2

(a) Optimal realization of f 3 (b) Optimal realization of f 4

x4

x1x2 x1x2

x3x4 x3 x4 x1

00 01 11 10 00 01 11 10

x2

00 00

x3

01 1 1 1 01 1 1 1 x4 f4

11 1 1 1 11 1 1 1 x2

x4

10 1 10 1

(c) Optimal realization of f 3 and f 4 together (d) Combined circuit for f 3 and f 4

Figure 4.17. Another example of multiple-output synthesis.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.18. Implementation in a CPLD.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x4 x5 x3 f

x1

x1 0 x4 0 x3 0

0 A 0 C 1 E

x6 x6 1 x5 0 1

0 1 C 1

x2

x2 0 A 0 D 0

0 B 1 D 0 f

x7 x7 0 1 0

1 B 1 E 1

Figure 4.19. Implementation in an FPGA.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

7 inputs

Figure 4.20. Using four-input AND gates to realize a

seven-input product term.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

x2 x4

x3 x6

x5

x2

x3

x5

Figure 4.21. A factored circuit.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

x2

f1

x3 f2

x4

Figure 4.22. Circuit for Example 4.5.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

x3

g

f

x2

x4

Figure 4.23. Logic circuit for Example 4.6.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

x3

g

f

x2

x4

x1

x2 g

x3 h f

x4

Figure 4.24. The structure of decomposition in Example 4.6.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2 x1 x2

x3 x4 x3 x4

00 01 11 10 00 01 11 10

00 1 00

01 1 1 1 01 1 1 1 1

11 1 11

10 1 1 1 10 1 1 1 1

x5 = 0 x5 = 1

Figure 4.25. Decomposition

(a) Karnaugh map for the function f

for Example 4.7. x

1

g

x2

x5

x3 f

x4

Fundamentals of Digital Logic Brown-Vranesic

(b) Circuit obtained using decomposition

i oh C842 NE CE

U M & A saxeT

x1

x1 x2

x1

x2

(a) Sum-of-products implementation g x1 x2

x1

x2

(c) Optimal NAND gate implementation

x1 x2

x2

(b) NAND gate implementation

Fundamentals of Digital Logic Brown-Vranesic

Figure 4.26. Implementation of XOR.

i oh C842 NE CE

x1 x1 U M & A saxeT

x2 x2

x3 x3

x4 f x4 f

x5 x5

x6 x6

x7 x7

(a) Circuit with AND and OR gates (b) Inversions needed to convert to NANDs

x1

x2

x3

x4 f

x5

x6

x7

(c) NAND-gate circuit

Figure 4.27. Conversion to a NAND-gate circuit.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

x1 U M & A saxeT

x2

x3

x4 f

x5

x6

x7

(a) Inversions needed to convert to NORs

x1

x2

Figure 4.28. Conversion

to a NOR-gate circuit. x3

f

x4

x5

x6

x7

(b) NOR-gate circuit

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

P3

x2

x3 P1

x4 f

P4

x5

P5

x6 P2

x7

Figure 4.29. Circuit for Example 4.10.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

P1

x2 P9

x5

x3 P4 f

P7

P2

P3 P10

P6 P8

x4

P5

Figure 4.30. Circuit for Example 4.11.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 P1

x2 P2

x3 P3

x4

f

x5

(a) NAND-gate circuit

x1

x2

x3

x4

f

x5

(b) Moving bubbles to convert to ANDs and ORs

x1

x2

x3

x4

f

x5

(c) Circuit with AND and OR gates

Figure 4.31. Circuit for Example 4.12.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1

P2

P1

x 22 P4

x3

f

P3

x4

x5

Figure 4.32. Circuit for Example 4.13.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

01 x1 11 x1 x2 f

0 0 0

x2 0 1 1

1x

1 0 1

1 1 1

x1

00 10

Figure 4.33. Representation of f (x1, x2) = m(1, 2, 3).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.34. Representation of f (x1, x2, x3) = m(0, 2, 4, 5, 6).

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.35. Representation of f 3 from Figure 4.7.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

List 1 List 2 List 3

0 0 0 0 0 0,4 0 x 0 0 0,4,8,12 x x 0 0

0,8 x 0 0 0

4 0 1 0 0

8 1 0 0 0 8,10 1 0 x 0

4,12 x 1 0 0

10 1 0 1 0 8,12 1 x 0 0

12 1 1 0 0

10,11 1 0 1 x

11 1 0 1 1 12,13 1 1 0 x

13 1 1 0 1

11,15 1 x 1 1

15 1 1 1 1 13,15 1 1 x 1

Figure 4.36. Generation of prime implicants for the function

in Figure 4.11.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Prime Minterm

implicant 0 4 8 10 11 12 13 15

p1 1 0 x 0

p2 1 0 1 x

p3 1 1 0 x

p4 1 x 1 1

p5 1 1 x 1

p6 x x 0 0 Prime Minterm

implicant 10 11 13 15

(a) Initial prime implicant cover table p2

p4

p5

Prime Minterm

implicant 10 11 13 15

p1 (c) After the removal of dominated rows

p2

p3

p4

p5

(b) After the removal of essential prime implicants

Figure 4.37. Selection of a cover for the function in Figure 4.11.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

List 1 List 2 List 3

0 0 0 0 0 0,1 0 0 0 x 0,1,8,9 x 0 0 x

0,2 0 0 x 0

1 0 0 0 1 0,8 x 0 0 0 1,5,9,13 x x 0 1

2 0 0 1 0 8,9,12,13 1 x 0 x

8 1 0 0 0 1,5 0 x 0 1

2,6 0 x 1 0 5,7,13,15 x 1 x 1

5 0 1 0 1 1,9 x 0 0 1

6 0 1 1 0 8,9 1 0 0 x

9 1 0 0 1 8,12 1 x 0 0

12 1 1 0 0

5,7 0 1 x 1

7 0 1 1 1 6,7 0 1 1 x

13 1 1 0 1 5,13 x 1 0 1

15 1 1 1 1 9,13 1 x 0 1

12,13 1 1 0 x

7,15 x 1 1 1

13,15 1 1 x 1

Figure 4.38. Generation of prime implicants for the function

in Example 4.14.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Prime Minterm

implicant 0 2 5 6 7 8 9 13

p1 0 0 x 0

p2 0 x 1 0

p3 0 1 1 x

p4 x 0 0 x

p5 x x 0 1

p6 1 x 0 x

p7 x 1 x 1 Prime Minterm

implicant 0 2 5 6 7 8 Prime Minterm

(a) Initial prime implicant cover table p1 implicant 2 6

p2 p1

p3 p2

Prime Minterm

implicant 0 2 5 6 7 8 p4 p3

p7

p1 0 0 x 0

p2 0 x 1 0 (d) After including p4 and p7

(c) After the removal of rows p5 and p6

p3 0 1 1 x

p4 x 0 0 x

p5 x x 0 1

p6 1 x 0 x

p7 x 1 x 1

(b) After the removal of columns 9 and 13

Figure 4.39. Selection of a cover for the function in Example 4.14.

Fundamentals of Digital Logic Brown-Vranesic in the cover

i oh C842 NE CE

U M & A saxeT

Prime Minterm

implicant 0 3 10 15

p1 0 0 x x

p2 x 0 x 0

p3 x 0 1 x Prime Minterm

p4 x x 1 1 implicant 0 3 10 15

p5 1 x 1 x p1

p2

(a) Initial prime implicant cover table p4

p5

Prime Minterm

implicant 0 15 (c) After excluding p3 from the cover

p1

p2

p4

p5

(b) After including p3 in the cover

Figure 4.40. Selection of a cover for the function in Example 4.15.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Bi

Ai 0 1 x

0 0 o 0 Ai * Bi

1 o 1 1

x 0 1 x

Figure 4.41. The coordinate *-operation.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Bi

Ai 0 1 x

0 o Ai # Bi

1 o

x 1 0

Figure 4.42. The coordinate #-operation.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2 x1 x2

x3 x4 x3 x4

00 01 11 10 00 01 11 10

00 1 1 d 00 1

01 d 1 01

11 11 1 1 1

10 1 d 1 10 d 1 1

x5 = 0 x5 = 1

Figure 4.43. The function for Example 4.20.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

module example4_21 (x1, x2, x3, f);

input x1, x2, x3;

output f;

assign f = (~x1 & ~x2 & ~x3) | (~x1 & x2 & ~x3) |

(x1 & ~x2 & ~x3) | (x1 & ~x2 & x3) |

(x1 & x2 & ~x3);

endmodule

Figure 4.44. Verilog code for the function in Figure 4.1.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.45. Implementation of the Verilog code in Figure 4.44.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

i1 i2 i3 i4 f

d 0 0 0 1

0 i1 d 0 0 1 0

x1 i2 d 0 1 0 1

x2 d 0 1 1 0 f

i3

x3 i4 d 1 0 0 1

d 1 0 1 1

d 1 1 0 1

d 1 1 1 0

LUT

Figure 4.46. The Verilog code in Figure 4.44 implemented in a LUT.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

module example4_22 (x1, x2, x3, x4, f);

input x1, x2, x3, x4;

output f;

assign f = (~x1 & ~x2 & x3 & ~x4) | (~x1 & ~x2 & x3 & x4) |

(x1 & ~x2 & ~x3 & x4) | (x1 & ~x2 & x3 & ~x4) |

(x1 & ~x2 & x3 & x4) | (x1 & x2 & ~x3 & x4) ;

endmodule

Figure 4.47. Verilog code for f1 in Figure 4.7.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

module example4_23 (x1, x2, x3, x4, x5, x6, x7, f);

input x1, x2, x3, x4, x5, x6, x7;

output f;

assign f = (x1 & x3 & ~x6) | (x1 & x4 & x5 & ~x6) |

(x2 & x3 & x7) | (x2 & x4 & x5 & x7) ;

endmodule

Figure 4.48. Verilog code for the function of section 4.6.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

0

x1 x1 x3 x6

x3

x6

x1

x1 x2 x1 x6 + x2 x7

x4 x1 x4 x5 x6 x6

x5 x7

x6

f x3

0 x4 f

x2 x2 x3 x7 x5

x3

x7

x2 (b) Factored realization

x4 x2 x4 x5 x7

x5

x7

(a) Sum-of-products realization

Figure 4.49. Implementation of the Verilog code in Figure 4.48.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.50. Karnaugh maps for

Example 4.24.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.51. Karnaugh maps

for Example 4.25.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.52. Generation of prime implicants for the function in Example 4.26.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.53. Selection of a cover for the function in Example 4.26.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.54. Circuit for Example 4.29.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

Figure 4.55. A possible format for truth tables of seven-variable

functions.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

U M & A saxeT

x1 x2x3

x2 x3 x1x3 x1x2

x3 x2 x3 x1 x2 x1

NO NO NO NO

Figure P4.1. Expansion of implicant x1x2x3.

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

x1 U M & A saxeT

x3

x4

x1

x3

x4

x1

x2 f

x3

x1

Figure P4.2. Circuit x2

for problem 4.33. x3

x4

x2

x4

x3

g

x1

x4

x1

x4

Fundamentals of Digital Logic Brown-Vranesic

i oh C842 NE CE

x1 U M & A saxeT

x2

x1

x2

f

x3

x2

Figure P4.3. Circuit for x4

problem 4.34.

x1

x2

g

x1

x3

x2

x3

Fundamentals of Digital Logic Brown-Vranesic

You might also like

- Chapter 3 Parallel and Pipelined Processing: 1 ECE734 VLSI Arrays For Digital Signal ProcessingDocument13 pagesChapter 3 Parallel and Pipelined Processing: 1 ECE734 VLSI Arrays For Digital Signal ProcessingM Madan GopalNo ratings yet

- Course SyllabusDocument1 pageCourse SyllabusM Madan GopalNo ratings yet

- Registration FormDocument1 pageRegistration FormM Madan GopalNo ratings yet

- 1 CE102 Conducted EmissionsDocument9 pages1 CE102 Conducted EmissionsM Madan GopalNo ratings yet

- Mark XIIA Identification Friend or Foe (IFF) Mode 5: Navy ProgramsDocument2 pagesMark XIIA Identification Friend or Foe (IFF) Mode 5: Navy ProgramsM Madan GopalNo ratings yet

- Unit 4 - Mean Risk PDFDocument19 pagesUnit 4 - Mean Risk PDFM Madan GopalNo ratings yet

- Unit-5 Index Tracking Complete PDFDocument11 pagesUnit-5 Index Tracking Complete PDFM Madan GopalNo ratings yet

- Unit-7 Dyn MV PDFDocument34 pagesUnit-7 Dyn MV PDFM Madan GopalNo ratings yet

- Unit 2 - Mean Variance PDFDocument29 pagesUnit 2 - Mean Variance PDFM Madan GopalNo ratings yet

- Digital Design With Fpgas: by Neeraj KulkarniDocument24 pagesDigital Design With Fpgas: by Neeraj KulkarniM Madan GopalNo ratings yet

- Diode ReviewDocument34 pagesDiode ReviewM Madan GopalNo ratings yet

- Robotics With RobotCDocument6 pagesRobotics With RobotCM Madan GopalNo ratings yet

- Virtex 5Document1 pageVirtex 5M Madan GopalNo ratings yet

- ANURAG GROUP OF INSTITUTIONS, Venktapur (V), Ghatkesar (M), Ranga Reddy (Dist.), A.P, INDIADocument8 pagesANURAG GROUP OF INSTITUTIONS, Venktapur (V), Ghatkesar (M), Ranga Reddy (Dist.), A.P, INDIAM Madan GopalNo ratings yet

- Mosfets Tutorial: (A) (B) (C) (D)Document2 pagesMosfets Tutorial: (A) (B) (C) (D)M Madan GopalNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Fortigate Fortiwifi 80F Series: Data SheetDocument12 pagesFortigate Fortiwifi 80F Series: Data SheetMonNo ratings yet

- SRT259 Construction Projects - Assignment 1 Guide Individual Report On Regulatory RequirementsDocument4 pagesSRT259 Construction Projects - Assignment 1 Guide Individual Report On Regulatory Requirementssikandar abbasNo ratings yet

- A Review On Cleaning Mechanism of Solar Photovoltaic Panel: Patil P.A., Bagi J.S., Wagh M. MDocument7 pagesA Review On Cleaning Mechanism of Solar Photovoltaic Panel: Patil P.A., Bagi J.S., Wagh M. MSumant MalganNo ratings yet

- Fintechinternshipdefenseslides2000 180511165636 PDFDocument40 pagesFintechinternshipdefenseslides2000 180511165636 PDFSadman Abrar RaiyanNo ratings yet

- 2011 Oregon State Mars Rover Design ReportDocument31 pages2011 Oregon State Mars Rover Design ReportHarini MNo ratings yet

- TP03 Software ManualDocument338 pagesTP03 Software ManualAjith KumarNo ratings yet

- eTB Register FinalDocument43 pageseTB Register FinalRaNa MBNo ratings yet

- BoyceODEch2s2p27 PDFDocument3 pagesBoyceODEch2s2p27 PDFHelalNo ratings yet

- Srinivas NarlaDocument8 pagesSrinivas NarlaRAJINIKNTH REDDYNo ratings yet

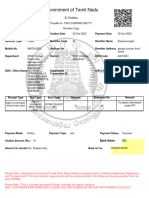

- Government of Tamil Nadu: E-ChallanDocument1 pageGovernment of Tamil Nadu: E-ChallanGopal AeroNo ratings yet

- Argus Flanged Ball Valve Fk76m Technical Data Sheet AhgDocument4 pagesArgus Flanged Ball Valve Fk76m Technical Data Sheet Ahgfahmi1987No ratings yet

- AB MaintenanceDocument46 pagesAB Maintenanceagung_wpNo ratings yet

- Joseph Carreon: 3Mt0Ssuof Pomaansoernch Rehf2U0A2God0FDocument2 pagesJoseph Carreon: 3Mt0Ssuof Pomaansoernch Rehf2U0A2God0FBergonsolutions Aingel100% (1)

- Amit Kumar Das (Iiest Shibpur)Document28 pagesAmit Kumar Das (Iiest Shibpur)In SaneNo ratings yet

- MAWOP CalculationDocument28 pagesMAWOP Calculationsigit praNo ratings yet

- Application Security ArchitectureDocument20 pagesApplication Security ArchitectureManish WaliaNo ratings yet

- Embossing and Debossing PresentationDocument13 pagesEmbossing and Debossing PresentationKeerthanaNo ratings yet

- HPE Pointnext Tech Care Brochure-A00118675enwDocument8 pagesHPE Pointnext Tech Care Brochure-A00118675enwViniloNo ratings yet

- Python ProgrammingDocument4 pagesPython ProgrammingLucifer MorningstarNo ratings yet

- CCNP Encor Course OutlineDocument2 pagesCCNP Encor Course OutlinePartha Sarathi NandiNo ratings yet

- Big Data AnalysisDocument30 pagesBig Data AnalysisAdithya GutthaNo ratings yet

- Adobe Forms - Create Table (Using Subform)Document6 pagesAdobe Forms - Create Table (Using Subform)Naresh VepuriNo ratings yet

- ADA Lec 001-005Document86 pagesADA Lec 001-005Hikmatullah SaqibNo ratings yet

- Jotatemp 250: Technical Data SheetDocument5 pagesJotatemp 250: Technical Data SheetMedhat Merzek100% (1)

- Pull Out Testing Methodology Ultimate Load Tests For Rebar DowelsDocument3 pagesPull Out Testing Methodology Ultimate Load Tests For Rebar DowelsHenry FlorendoNo ratings yet

- Progresssive Cavity PumpDocument5 pagesProgresssive Cavity PumpSACHIN PATELNo ratings yet

- BV242Document1 pageBV242FAIYAZ AHMEDNo ratings yet

- Godox XProS, XPro-S Manual v2018-01-24Document15 pagesGodox XProS, XPro-S Manual v2018-01-24deejjjaaaa100% (2)

- Restart Class 4 Term 2Document2 pagesRestart Class 4 Term 2sebastinNo ratings yet