Professional Documents

Culture Documents

Estructural y Generate PDF

Uploaded by

Daniel Andrés CrespoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Estructural y Generate PDF

Uploaded by

Daniel Andrés CrespoCopyright:

Available Formats

Chapter 8 Outline

Structural Modeling z Basic Example

z Component Declaration

z Component Instantiation

z Resolving Signal Value

z Generate Statement

VHDL

VHDL - Flaxer Eli Ch 8 - 1 VHDL - Flaxer Eli Ch 8 - 2

Structural Modeling Structural Modeling

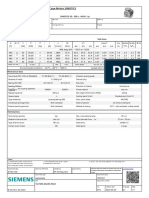

Structural Modeling Basic Example

z This chapter describes the structural style of modeling. An entity is

MR

modeled as a set of components connected by signals, that is, as a netlist.

z The behavior of the entity is not explicitly apparent from its model. The S1 RDY

Data D Q

component instantiation statement is the primary mechanism used for

describing such a model of an entity. S2

CK CLK QB

CTRL

z COMPONENT & PORT MAP statements are used to implement

structural modeling. Din

z The component instantiation statements are concurrent statements, and

their order of appearance in the architecture body is therefore not

z Three components and2, nor2, and dff are used.

important.

z The components are instantiated in the architecture body via three

z A component can, in general, be instantiated any number of times. component instantiation statements - PORT MAP, and the instantiated

z Each instantiation must have a unique component label. components are connected to each other via signals S1 and S2.

VHDL - Flaxer Eli Ch 8 - 3 VHDL - Flaxer Eli Ch 8 - 4

Structural Modeling Structural Modeling

Basic Example (VHDL Code) Component Declaration

ENTITY Gating IS

PORT (data, ck, mr, din: IN bit; rdy, ctrl: OUT bit); z A component in a structural description must first be declared using

END Gating; a component declaration.

ARCHITECTURE Structure_View OF Gating IS z A component declaration declares the name and the interface of a

COMPONENT and2

PORT (x, y: IN bit; z: OUT bit); component (similar to the entity).

END COMPONENT;

z The interface specifies the mode and the type of ports.

COMPONENT nor2

PORT (x, y: IN bit; z: OUT bit); z The syntax of a simple form of component declaration is:

END COMPONENT;

COMPONENT dff

PORT (d, clk: IN bit; q, qb: OUT bit); COMPONENT Component-Name [IS]

END COMPONENT; [PORT(List-of-Interface-Ports);]

END COMPONENT [Component-Name ];

SIGNAL s1, s2: bit; MR

BEGIN

S1 RDY

d1: dff PORT MAP (data, ck, s1, s2); Data D Q

a1: and2 PORT MAP (s2, din, ctrl); CK CLK QB

S2

CTRL

n1: nor2 PORT MAP (s1, mr, rdy);

END Structure_View ; Din

VHDL - Flaxer Eli Ch 8 - 5 VHDL - Flaxer Eli Ch 8 - 6

Structural Modeling Structural Modeling

Component Declaration (notes) Component & Package

z Component declarations appear in the declarations part of an architecture

z The component-name may or may not refer to the name of an entity

body.

already existing in a library. If it does not, it must be explicitly bound to

an entity. z Alternately, they may also appear in a package declaration. Items declared in

this package can then be made visible within any architecture body by using

z The binding information can be specified using a configuration.

the library and use clauses.

z The List-Of-Interface-Ports specifies the name, mode, and type for each

z For example, consider the entity GATING described in the basic example. A

port of the component in a manner similar to that specified in an entity

package such as shown may be created to hold the component declarations.

declaration.

z The names of the ports may also be different from the names of the ports PACKAGE MyCOMP IS

in the entity to which it may be bound (different port names can be COMPONENT and2

PORT (x, y: IN bit; z: OUT bit);

mapped in a configuration). For while, we will assume that an entity of END COMPONENT;

the same name as that of the component already exists and that the name, COMPONENT nor2

PORT (x, y: IN bit; z: OUT bit);

mode, and type of each port matches the corresponding ones in the END COMPONENT;

component. COMPONENT dff

PORT (d, clk: IN bit; q, qb: OUT bit);

z Configurations are discussed in the next chapter. END COMPONENT;

END MyCOMP;

VHDL - Flaxer Eli Ch 8 - 7 VHDL - Flaxer Eli Ch 8 - 8

Structural Modeling Structural Modeling

Component & Package Library Component Instantiation

z If the package MyPackage has been compiled into library MyLib, the z A component instantiation statement defines a sub-component of the entity in

architecture body can be as: which it appears. It associates the signals in the entity with the ports of that

sub-component.

LIBRARY MyLib; z A format of a component instantiation statement:

USE MyLib.MyPackage.All;

ARCHITECTURE Structure_View OF Gating IS Component-Label: Component-Name PORT MAP (association-list);

SIGNAL s1, s2: bit;

BEGIN z The Component-Label can be any legal identifier and can be considered as

d1: dff PORT MAP (data, ck, s1, s2); the name of the instance.

a1: and2 PORT MAP (s2, din, ctrl);

n1: nor2 PORT MAP (s1, mr, rdy); z The Component-Name must be the name of a component declared earlier

END Structure_View ; using a component declaration.

z The association-list, associates signals in the entity, called actuals, with the

ports of a component, called formals.

z More on Library and Package in the next chapters.

VHDL - Flaxer Eli Ch 8 - 9 VHDL - Flaxer Eli Ch 8 - 10

Structural Modeling Structural Modeling

Actuals and Formals Actuals and Formals

z An actual may be a signal. An actual for an input port may also be an z If a port in a component instantiation is not connected to any signal, the

expression. keyword OPEN can be used to signify that the port is not connected.

z An actual may also be the keyword open to indicate a port that is not z For example:

connected.

z There are two ways to perform the association of formals with actuals: COMPONENT dff

PORT (d, clk: IN bit:=0; q, qb: OUT bit);

1. Positional association END COMPONENT;

2. Named association -----------------------------------------

d1: dff PORT MAP (OPEN, ck, s1, OPEN);

z In positional association, each actual in the component instantiation is

mapped by position with each port in the component declaration. That is, z The second input port of the dff component is not connected to any signal.

the first port in the component declaration corresponds to the first actual in An input port may be left open only if its declaration specifies an initial

the component instantiation, the second with the second, and so on. value. For the previous component instantiation statement to be legal, port d

of the component declaration for dff must have an initial value expression,

COMPONENT dff while the output port qb not.

PORT (d, clk: IN bit; q, qb: OUT bit);

END COMPONENT; z A port of any other mode may be left unconnected as long as it is not an

-----------------------------------------

d1: dff PORT MAP (data, ck, s1, s2);

unconstrained array.

VHDL - Flaxer Eli Ch 8 - 11 VHDL - Flaxer Eli Ch 8 - 12

Structural Modeling Structural Modeling

Actuals and Formals Actuals / Formals Type and Mode

z In named association, an association-list is of the form: z The types of the formal and actual being associated must be the same.

formal1 => actual1, formal2 => actual2, formaln => actualn z The modes of the ports must conform to the rule that if the formal is

z For example: readable, so must the actual be; and if the formal is writable, so must the

actual be.

COMPONENT dff z Locally declared signal is considered to be both readable and writable, such

PORT (d, clk: IN bit; q, qb: OUT bit); a signal may be associated with a formal of any mode.

END COMPONENT;

----------------------------------------- z If an actual is a port of mode in, it may not be associated with a formal of

d1: dff PORT MAP (clk => ck, d => data, qb => s2, q => s1); mode out or inout; if the actual is a port of mode out, it may not be

associated with a formal of mode in or inout; if the actual is a port of mode

inout, it may be associated with a formal of mode in, out, or inout.

z In named association, the ordering of the associations is not important since

z It is important to note that an actual of mode out or inout indicates the

the mapping between the actuals and formals is explicitly specified. presence of a source for that signal, and therefore, it must be resolved if that

z An important point to note is that the scope of the formals is restricted to be signal is multiply driven.

within the port map part of the instantiation for that component. z A buffer port can never have more than one source; therefore, the only kind

of actual that can be associated with a buffer port is another buffer port or a

signal that has at most one source.

VHDL - Flaxer Eli Ch 8 - 13 VHDL - Flaxer Eli Ch 8 - 14

Structural Modeling Structural Modeling

Component Model Component Example (Package)

z Structural models can be simulated and synthesize only after the entities that

the components represent are modeled and placed in a design library.

z The lowest-level entities must be behavioral models (or dataflow).

z Consider the components instantiation A1, N1, and D1 in the basic example.

Assume that those instance is bound to an entity with the same name and

identical port names.

z The library must include the model of those components.

z More on Library and Package in the next chapters.

VHDL - Flaxer Eli Ch 8 - 15 VHDL - Flaxer Eli Ch 8 - 16

Structural Modeling Structural Modeling

Component Example (Entity & Arc) Component Example (Main)

VHDL - Flaxer Eli Ch 8 - 17 VHDL - Flaxer Eli Ch 8 - 18

Structural Modeling Structural Modeling

Component Example (Simulation) Resolving Signal Value

z If outputs of two components drive a common signal, the value of the signal

must be resolved using a resolution function. This is similar to the case of a

signal being assigned using more than one concurrent signal assignment

statement.

z For example, consider the circuit shown below, which shows two and gates

driving a common signal RS1, which is drive to produce the result in Z.

z The RS1 signal must be of resolved type (std_logic for example).

A

B Z

RS1

C

D

VHDL - Flaxer Eli Ch 8 - 19 VHDL - Flaxer Eli Ch 8 - 20

Structural Modeling Structural Modeling

Generate Statement For Generate Scheme

z The format of a generate statement using the for-generation scheme is:

z Generate statement is concurrent.

z Concurrent statements can be conditionally selected or replicated Generate-Label: FOR index IN range GENERATE

during the elaboration phase using the generate statement. [block-declarations

z There are two forms of the generate statement: BEGIN]

1. for-generation - concurrent statements replicated a predetermined concurrent-statements;

number of times. END GENERATE [Generate-Label];

2. if-generation - concurrent statements conditionally elaborated.

z The generate statement is interpreted during elaboration, and z The values in the discrete range must be globally static, that is, they

must be computable at elaboration time.

therefore has no simulation semantics. It resembles a macro

expansion. z During elaboration, the set of concurrent statements are replicated once

for each value in the discrete range.

z The generate statement provides for a compact description of

z The statements can use the generate index in their expressions, and its

regular structures such as memories, registers, and counters.

value would be substituted during elaboration for each replication.

VHDL - Flaxer Eli Ch 8 - 21 VHDL - Flaxer Eli Ch 8 - 22

Structural Modeling Structural Modeling

For Generate Scheme (notes) For Generate (example)

z Consider the following representation of a 4 - bit full-adder:

z There is an implicit declaration for the generate index within the

generate statement.

z The type of the identifier is defined by the discrete range.

z Declarations, if present, declare items that are visible only within the

generate statement.

z The body of the generate statement can also include other concurrent CAR(0)

statement (as we will see later).

z For-Generate statements may be nested.

CAR(4)

VHDL - Flaxer Eli Ch 8 - 23 VHDL - Flaxer Eli Ch 8 - 24

Structural Modeling Structural Modeling

For - Generate (example code) For - Generate (without Port-Map)

ENTITY full_add4 IS z The body of the generate statement can also have other concurrent

PORT (a, b: IN bit_vector(3 DOWNTO 0); cin: IN bit;

statement.

sum: OUT bit_vector(3 DOWNTO 0); cout: OUT bit;

END full_add4; z For example, in the previous architecture, the component instantiation

statement could be replace by concurrent signal assignment:

ARCHITECTURE for_generate OF full_add4 IS

COMPONENT fa

PORT (pa, pb, pc: IN bit; pcout, psum: OUT bit);

END COMPONENT; SIGNAL car: bit_vector(4 DOWNTO 0);

BEGIN

SIGNAL car: bit_vector(4 DOWNTO 0); car(0) <= cin;

BEGIN gk: FOR k IN 3 DOWNTO 0 GENERATE

car(0) <= cin; sum(k) <= a(k) XOR b(k) XOR car(k);

gk: FOR k IN 3 DOWNTO 0 GENERATE car(k+1) <= a(k) AND b(k) AND car(k);

f1: fa PORT MAP(car(k),a(k),b(k),car(k+1),sum(k)); END GENERATE gk;

END GENERATE gk; cout <= car(4);

cout <= car(4); END for_generate;

END for_generate;

VHDL - Flaxer Eli Ch 8 - 25 VHDL - Flaxer Eli Ch 8 - 26

Structural Modeling Structural Modeling

If Generate Scheme If Generate (example)

z The format of a generate statement using the if-generation scheme is: z Consider the following representation of a 4 - bit full-adder:

Generate-Label: IF expression GENERATE

[block-declarations

BEGIN]

concurrent-statements;

END GENERATE [Generate-Label];

z The if-generate statement allows for conditional selection of concurrent

statements based on the value of an expression.

z The expression must be a globally static expression, that is, the value

must be computable at elaboration time. z This time we use the port directly.

z Any declarations present are local to the generate statement.

z There is no else or elsif branch.

VHDL - Flaxer Eli Ch 8 - 27 VHDL - Flaxer Eli Ch 8 - 28

Structural Modeling Structural Modeling

If - Generate (example code)

ARCHITECTURE if_generate OF full_add4 IS

COMPONENT fa

PORT (pa, pb, pc: IN bit; pcout, psum: OUT bit);

END COMPONENT;

SIGNAL car: bit_vector(3 DOWNTO 1);

BEGIN

gk: FOR k IN 3 DOWNTO 0 GENERATE

ck0: IF k = 0 GENERATE

f1: fa PORT MAP(cin,a(k),b(k),car(k+1),sum(k));

END GENERATE ck0;

ck1: IF k > 0 AND k < 3 GENERATE

f1: fa PORT MAP(car(k),a(k),b(k),car(k+1),sum(k));

END GENERATE ck1;

ck3: IF k = 3 GENERATE

f1: fa PORT MAP(car(k),a(k),b(k),cout,sum(k));

END GENERATE ck3;

END GENERATE gk;

END if_generate;

VHDL - Flaxer Eli Ch 8 - 29

Structural Modeling

You might also like

- Conference #1Document1 pageConference #1Daniel Andrés CrespoNo ratings yet

- 1987 EngDocument2 pages1987 EngChhorvorn VannNo ratings yet

- Organize Your Research and Collaborate Online with MendeleyDocument4 pagesOrganize Your Research and Collaborate Online with MendeleyDaniel Andrés CrespoNo ratings yet

- Dusty Schmidt - Don't Listen To Phil HellmuthDocument370 pagesDusty Schmidt - Don't Listen To Phil HellmuthCeno Nedkov86% (7)

- Introduction to PCA and FA: Dimension Reduction ToolsDocument29 pagesIntroduction to PCA and FA: Dimension Reduction ToolsPushpaRasnayakeNo ratings yet

- (Asif Mahmood Mughal) Real Time Modeling, Simulati (B-Ok - Xyz)Document199 pages(Asif Mahmood Mughal) Real Time Modeling, Simulati (B-Ok - Xyz)Yousef SardahiNo ratings yet

- Efficient Hardware Realization of Advanced Encryption Standard Algorithm Using Virtex-5 FPGADocument5 pagesEfficient Hardware Realization of Advanced Encryption Standard Algorithm Using Virtex-5 FPGASyedshafiulhaqNo ratings yet

- FPGA implementation of 4D memristor chaotic system generates random numbers for encryptionDocument20 pagesFPGA implementation of 4D memristor chaotic system generates random numbers for encryptionDaniel Andrés CrespoNo ratings yet

- Cryptographic Accelerator in Reconfigurable HardwareDocument8 pagesCryptographic Accelerator in Reconfigurable HardwareDaniel Andrés CrespoNo ratings yet

- 2005 Book DesignOfEmbeddedControlSystems PDFDocument267 pages2005 Book DesignOfEmbeddedControlSystems PDFDaniel Andrés CrespoNo ratings yet

- Design and Implementation of Reconfigurable Rijndael Encryption Algorithms For Reconfigurable Mobile TerminalsDocument9 pagesDesign and Implementation of Reconfigurable Rijndael Encryption Algorithms For Reconfigurable Mobile TerminalsDaniel Andrés CrespoNo ratings yet

- Edward Winter - InterregnumDocument14 pagesEdward Winter - InterregnumDaniel Andrés CrespoNo ratings yet

- Hex NotesDocument10 pagesHex Notesramez1863No ratings yet

- Hotelling Simplified Calculation of Principal Components PDFDocument9 pagesHotelling Simplified Calculation of Principal Components PDFDaniel Andrés CrespoNo ratings yet

- AlphaGo Tutorial SlidesDocument16 pagesAlphaGo Tutorial SlidesDaniel Andrés CrespoNo ratings yet

- Miller PDFDocument25 pagesMiller PDFDaniel Andrés CrespoNo ratings yet

- Taller AlgebraDocument10 pagesTaller AlgebraDaniel Andrés CrespoNo ratings yet

- Edward Winter - Jaffe and His 'Primer'Document4 pagesEdward Winter - Jaffe and His 'Primer'Daniel Andrés CrespoNo ratings yet

- IMO BookDocument159 pagesIMO Bookmywol1931100% (9)

- Imc2010 Day1 SolutionsDocument4 pagesImc2010 Day1 SolutionsamrinalNo ratings yet

- Switching Power Supply 150W S-150-24: Output 24Vdc 6.25ADocument2 pagesSwitching Power Supply 150W S-150-24: Output 24Vdc 6.25ADaniel Andrés CrespoNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- CFEExam Prep CourseDocument28 pagesCFEExam Prep CourseM50% (4)

- Spouses Mariano Z. Velarde and Avelina D. VELARDE, Petitioners, vs. COURT OF Appeals, David A. RAYMUNDO and GEORGE RAYMUNDO, RespondentsDocument11 pagesSpouses Mariano Z. Velarde and Avelina D. VELARDE, Petitioners, vs. COURT OF Appeals, David A. RAYMUNDO and GEORGE RAYMUNDO, RespondentsRobyn JonesNo ratings yet

- Law of TortsDocument22 pagesLaw of TortsRadha KrishanNo ratings yet

- Dell 1000W UPS Spec SheetDocument1 pageDell 1000W UPS Spec SheetbobNo ratings yet

- 2020-05-14 County Times NewspaperDocument32 pages2020-05-14 County Times NewspaperSouthern Maryland OnlineNo ratings yet

- Yi-Lai Berhad - COMPANY PROFILE - ProjectDocument4 pagesYi-Lai Berhad - COMPANY PROFILE - ProjectTerry ChongNo ratings yet

- Meanwhile Elsewhere - Lizzie Le Blond.1pdfDocument1 pageMeanwhile Elsewhere - Lizzie Le Blond.1pdftheyomangamingNo ratings yet

- Novirost Sample TeaserDocument2 pagesNovirost Sample TeaserVlatko KotevskiNo ratings yet

- Expert Business Analyst Darryl Cropper Seeks New OpportunityDocument8 pagesExpert Business Analyst Darryl Cropper Seeks New OpportunityRajan GuptaNo ratings yet

- Sta A4187876 21425Document2 pagesSta A4187876 21425doud98No ratings yet

- ABBBADocument151 pagesABBBAJeremy MaraveNo ratings yet

- RAP Submission Form, OBIDocument3 pagesRAP Submission Form, OBIAhmed MustafaNo ratings yet

- Berry B Brey Part IDocument49 pagesBerry B Brey Part Ikalpesh_chandakNo ratings yet

- Case Study - Soren ChemicalDocument3 pagesCase Study - Soren ChemicalSallySakhvadzeNo ratings yet

- Usa Easa 145Document31 pagesUsa Easa 145Surya VenkatNo ratings yet

- 1LE1503-2AA43-4AA4 Datasheet enDocument1 page1LE1503-2AA43-4AA4 Datasheet enAndrei LupuNo ratings yet

- Code Description DSMCDocument35 pagesCode Description DSMCAnkit BansalNo ratings yet

- Royal Enfield Market PositioningDocument7 pagesRoyal Enfield Market PositioningApoorv Agrawal67% (3)

- Cib DC22692Document16 pagesCib DC22692Ashutosh SharmaNo ratings yet

- Indian Institute of Management KozhikodeDocument5 pagesIndian Institute of Management KozhikodepranaliNo ratings yet

- Bar Exam 2016 Suggested Answers in Political LawDocument15 pagesBar Exam 2016 Suggested Answers in Political LawYlnne Cahlion KiwalanNo ratings yet

- A320 Normal ProceduresDocument40 pagesA320 Normal ProceduresRajesh KumarNo ratings yet

- 5.0 A Throttle Control H-BridgeDocument26 pages5.0 A Throttle Control H-Bridgerumellemur59No ratings yet

- Gates em Ingles 2010Document76 pagesGates em Ingles 2010felipeintegraNo ratings yet

- 9IMJan 4477 1Document9 pages9IMJan 4477 1Upasana PadhiNo ratings yet

- Model S-20 High Performance Pressure Transmitter For General Industrial ApplicationsDocument15 pagesModel S-20 High Performance Pressure Transmitter For General Industrial ApplicationsIndra PutraNo ratings yet

- Module 5Document10 pagesModule 5kero keropiNo ratings yet

- OBHR Case StudyDocument8 pagesOBHR Case StudyYvonne TanNo ratings yet

- Dwnload Full International Monetary Financial Economics 1st Edition Daniels Solutions Manual PDFDocument36 pagesDwnload Full International Monetary Financial Economics 1st Edition Daniels Solutions Manual PDFelegiastepauleturc7u100% (16)

- Yamaha Nmax 155 - To Turn The Vehicle Power OffDocument1 pageYamaha Nmax 155 - To Turn The Vehicle Power Offmotley crewzNo ratings yet