Professional Documents

Culture Documents

Assignment 3

Uploaded by

Dhivya NCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Assignment 3

Uploaded by

Dhivya NCopyright:

Available Formats

Birla Institute of Technology and Science Pilani (Rajasthan)

Department of Electrical and Electronics Engineering

MEL G642, VLSI Architecture

Second Semester 2015-16

Assignment - 2

STATEMENT: Given that the sequence of instructions to be executed by the processor is

guaranteed to be free from data hazards, design a 4 stage (Instruction Fetch; Decode and

register operand read; execute; write back) pipelined RISC processor that can execute following

register to register instructions with a sustained throughput of one instruction per clock cycle:

AND, SUB, NAND, NOR

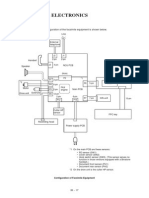

STEP 0: Draw the detailed architecture level diagram of the processor naming and depicting

the various architectural blocks (e.g. register file, instruction memory, ALU, pipeline registers,

PC and combinational functional blocks).

STEP 1: Create Verilog/ VHDL behavioural models for each of the architectural blocks.

(Register file, Instruction memory, ALU, Pipeline registers, PC)

STEP 2: Build the top level structural model of the processor by instantiating and

interconnecting the architectural blocks created in step 1.

STEP 3: Initialize the instruction memory with a program consisting of 4 instructions:

0000 ADD reg3, reg2, reg1

0004 SUB reg6, reg5, reg4

0008 NAND reg9, reg8, reg7

0012 NOR reg13, reg11, reg10

Initialize the register file with the following data

reg2 = 60 reg1 = 40

reg5 = 40 reg4 = 60

reg7 = FFFF856D reg8 = EEEE3721

reg10 = 1FFF756F reg11 = FFFF765E

Initialize PC by 0000 address.

The instruction format is:

31 14 9 4 0

OPCODE Dest. Reg Source Reg.1 Source Reg.2

Opcode ADD 0 - - - - -001

SUB 0 - - - - -010

NAND 0 - - - - -011

NOR 0 - - - - -100

The register file has 32 number of 32 bit registers. The data in registers is stored as integers in

2s complement binary representation. Assume that register file has two 32-bit read ports: A and

B for data reading and one 32 bit write port: C for data writing. At the rising edge of the clock

the read ports A and B output the data from the registers whose addresses are present at port A

address and port B address respectively if the enable read port A and enable read port B signals

are true. At the falling edge of a clock data is written to the register whose address is present at

Port C address if write enable Port C is true. Design the pipeline registers such that they are

latched at the rising edge of the clock. Specify the size and format of all pipeline registers

including the fields holding the decoded control signals as well as data.

The instruction memory is of size 64 bytes. A read operation from the memory outputs 4

consecutive bytes of information (starting from the byte address provided to the memory) at the

negative edge of clock if the read enable instruction memory signal is true. Byte addresses to be

provided to memory must be either 0 or multiples of 4.

You might also like

- Embedded Sysytem FileDocument52 pagesEmbedded Sysytem FileGagan MaggoNo ratings yet

- Ec6711 Emb Lab PDFDocument92 pagesEc6711 Emb Lab PDFAnonymous LXQnmsD100% (1)

- 8 Bit Risc Processor PresentationDocument36 pages8 Bit Risc Processor PresentationSantanu KumarNo ratings yet

- ITCE362: Computer Architecture Experiment No. 2 Register File DesignDocument9 pagesITCE362: Computer Architecture Experiment No. 2 Register File DesignHALIMANo ratings yet

- 1.0 The Design of Datapath Decoder: Ece 522/computer OrganizationDocument36 pages1.0 The Design of Datapath Decoder: Ece 522/computer OrganizationacapNo ratings yet

- Doc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardDocument48 pagesDoc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardRockson Kwame AgyemanNo ratings yet

- RiSC PipelineDocument9 pagesRiSC Pipelinekb_lu232No ratings yet

- Experiment No. 3Document6 pagesExperiment No. 3John FarandisNo ratings yet

- MP8085 Lab ManualDocument179 pagesMP8085 Lab ManualEvan3333No ratings yet

- Pipelined RISC Processor With Interrupt Handling: ECGR 5146 - Introduction To VHDL Fall 2013 ProjectDocument13 pagesPipelined RISC Processor With Interrupt Handling: ECGR 5146 - Introduction To VHDL Fall 2013 ProjectDon_TurboNo ratings yet

- 19ecs431 - Embedded SystemsDocument18 pages19ecs431 - Embedded SystemsNaresh KumarNo ratings yet

- Pic ReportDocument46 pagesPic ReportknlkohliNo ratings yet

- FPGA Lab#1Document8 pagesFPGA Lab#1حساب ويندوزNo ratings yet

- II BSC Computer ArchitectureDocument76 pagesII BSC Computer ArchitectureSukanyaNo ratings yet

- EE8681 Lab ManualDocument110 pagesEE8681 Lab ManualVasunthara DNo ratings yet

- 15EE305J Microcontroller LabDocument82 pages15EE305J Microcontroller LabEngr. Muhammad Shahid Laiq Research Associate NCAINo ratings yet

- Vss Paper MicroprocessorDocument4 pagesVss Paper MicroprocessorAnil JhaNo ratings yet

- EC8711 Embedded Lab Manual FinalDocument258 pagesEC8711 Embedded Lab Manual FinalbloomeceNo ratings yet

- Implementation of A 16-Bit RISC Processor Using FPGA ProgrammingDocument25 pagesImplementation of A 16-Bit RISC Processor Using FPGA ProgrammingTejashree100% (3)

- Unit 4Document108 pagesUnit 4Rasool NayabNo ratings yet

- Unit-2 Part-1: Basic Computer Organization and Design: ContentsDocument20 pagesUnit-2 Part-1: Basic Computer Organization and Design: ContentsSeid DeguNo ratings yet

- Manufacturing Processes Report (Thapar University)Document10 pagesManufacturing Processes Report (Thapar University)Nishant SainiNo ratings yet

- Laborator 1 Scriere in MemorieDocument8 pagesLaborator 1 Scriere in MemorieMadalin SandaNo ratings yet

- ARM New Manual 2018Document58 pagesARM New Manual 2018Shubham RajNo ratings yet

- Test2 Aplicatii CID Seriaf V4.ro - enDocument3 pagesTest2 Aplicatii CID Seriaf V4.ro - enAmmarArshadNo ratings yet

- Ec6232 Lab-ManualDocument74 pagesEc6232 Lab-ManualSuyash MishraNo ratings yet

- Write The Features of PIC16F8XX Flash Microcontrollers?: Unit-ViDocument6 pagesWrite The Features of PIC16F8XX Flash Microcontrollers?: Unit-ViashokNo ratings yet

- 445 April 2695Document7 pages445 April 2695Prateek Kumar PandeyNo ratings yet

- DSP Lab ManualDocument26 pagesDSP Lab ManualMadhan ReddyNo ratings yet

- Embed Lab9Document10 pagesEmbed Lab9amitpanvekarNo ratings yet

- 16-Bit RISCDocument6 pages16-Bit RISCnevdullNo ratings yet

- SsDocument60 pagesSsponns100% (1)

- CEA Lab ReportDocument8 pagesCEA Lab ReportIbrahim MehmoodNo ratings yet

- Microprocessors and Programming: Fall: 2021Document41 pagesMicroprocessors and Programming: Fall: 2021Emirhan AlmaNo ratings yet

- Milestone 2-UpdatedDocument13 pagesMilestone 2-UpdatedHưng Nguyễn ThànhNo ratings yet

- Milestone2 Ee3043Document14 pagesMilestone2 Ee3043teoNo ratings yet

- BoxDocument20 pagesBoxu2006262918No ratings yet

- CH341A DatasheetDocument22 pagesCH341A Datasheetflav100050% (2)

- Assembler Pass1bDocument3 pagesAssembler Pass1bshravan kumbharNo ratings yet

- University Institute of EnggDocument28 pagesUniversity Institute of EnggMeghna ChatterjeeNo ratings yet

- Lecture12-Using PIC Micro Controller 16F877ADocument57 pagesLecture12-Using PIC Micro Controller 16F877ADoodee Mohammed100% (4)

- FPGA Altera DE2 RS232 PDFDocument5 pagesFPGA Altera DE2 RS232 PDFidiot930902No ratings yet

- Reduced Instruction Set Computer (Risc) 32bit Processor On Field Programmable Gate Arrays (Fpgas) ImplementationDocument5 pagesReduced Instruction Set Computer (Risc) 32bit Processor On Field Programmable Gate Arrays (Fpgas) ImplementationDr. Krishna N. SharmaNo ratings yet

- PIC1Document183 pagesPIC1Gokul GocoolNo ratings yet

- Solved Tutorial With Tiny Bugs27-8-12Document24 pagesSolved Tutorial With Tiny Bugs27-8-12WondosenEshetieNo ratings yet

- ES Lab FileDocument37 pagesES Lab FileMøhït JáñgírNo ratings yet

- Lab ManualDocument78 pagesLab Manualgurusandhya11No ratings yet

- Lab # 03 I2C WriteDocument4 pagesLab # 03 I2C WriteSOBAN KHANNo ratings yet

- IT18302 - Computer Organization and Architecture Lecture Notes Unit 1-Basic Computer Organization and DesignDocument17 pagesIT18302 - Computer Organization and Architecture Lecture Notes Unit 1-Basic Computer Organization and DesignNAVINRAJ RSNo ratings yet

- Basic Computer OrganizationDocument23 pagesBasic Computer OrganizationKibrom HaftuNo ratings yet

- Laboratory Manual Rec 451 - Microprocessors & Microcontrollers LabDocument28 pagesLaboratory Manual Rec 451 - Microprocessors & Microcontrollers Lababhishek singhNo ratings yet

- 8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash Attiny22 Attiny22L PreliminaryDocument11 pages8-Bit Microcontroller With 2K Bytes of In-System Programmable Flash Attiny22 Attiny22L Preliminarymike_helplineNo ratings yet

- 1.1 Introduction To PIC Microcontroller: Embedded System DesignDocument33 pages1.1 Introduction To PIC Microcontroller: Embedded System DesignMinh HoangNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- ARM Microcontrollers Programming for Embedded SystemsFrom EverandARM Microcontrollers Programming for Embedded SystemsRating: 5 out of 5 stars5/5 (1)

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- Description Features: PT6967 LED Driver ICDocument22 pagesDescription Features: PT6967 LED Driver ICDhivya NNo ratings yet

- Description: Technical DataDocument17 pagesDescription: Technical DataDhivya NNo ratings yet

- RX Family: User's Manual: Software Renesas 32-Bit Mcu RX FamilyDocument278 pagesRX Family: User's Manual: Software Renesas 32-Bit Mcu RX FamilyDhivya NNo ratings yet

- Description Features: PT6961 LED Driver ICDocument18 pagesDescription Features: PT6961 LED Driver ICDhivya NNo ratings yet

- Description Features: PT6964 LED Driver ICDocument15 pagesDescription Features: PT6964 LED Driver ICDhivya NNo ratings yet

- The MOS TransistorDocument49 pagesThe MOS TransistorLauraPiccinnoNo ratings yet

- 2013 Arduino PID Lab 0Document7 pages2013 Arduino PID Lab 0Uma MageshwariNo ratings yet

- LCD-TFT Display Controller (LTDC) On STM32 MCUsDocument91 pagesLCD-TFT Display Controller (LTDC) On STM32 MCUsamirmoh1992100% (1)

- Main Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDocument25 pagesMain Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDhivya NNo ratings yet

- Ps Ex 1Document2 pagesPs Ex 1Dhivya NNo ratings yet

- LCD-TFT Display Controller (LTDC) On STM32 MCUsDocument91 pagesLCD-TFT Display Controller (LTDC) On STM32 MCUsamirmoh1992100% (1)

- L01 ComputerSystemAnatomyDocument14 pagesL01 ComputerSystemAnatomyDhivya NNo ratings yet

- STLED316S: Serial-Interfaced 6-Digit LED Controller With KeyscanDocument33 pagesSTLED316S: Serial-Interfaced 6-Digit LED Controller With KeyscanDhivya NNo ratings yet

- Design and Implementation of Single-Phase Hybrid Active Power Filter Controller-LibreDocument5 pagesDesign and Implementation of Single-Phase Hybrid Active Power Filter Controller-LibreDhivya NNo ratings yet

- Indian Electricity Act 2003Document67 pagesIndian Electricity Act 2003Dhivya NNo ratings yet

- Daq Ni Usb 6009Document30 pagesDaq Ni Usb 6009ramiro_vicente_6No ratings yet

- Harmonics in Power Quality IssuesDocument19 pagesHarmonics in Power Quality IssuesthomaswynnNo ratings yet

- Sorting AlgorithmsDocument17 pagesSorting AlgorithmsBilo BiloNo ratings yet

- Stacks and QueuesDocument21 pagesStacks and QueuesDhivya NNo ratings yet

- StringsDocument6 pagesStringsDhivya NNo ratings yet

- Design of Active Harmonic Filter For A 3Document10 pagesDesign of Active Harmonic Filter For A 3Dhivya NNo ratings yet

- Resume Preparation Do's and Don'ts: Amrita Vishwa Vidyapeetham 2014Document6 pagesResume Preparation Do's and Don'ts: Amrita Vishwa Vidyapeetham 2014Dhivya NNo ratings yet

- Core Architecture:: Container BasedDocument3 pagesCore Architecture:: Container BasedDhivya NNo ratings yet

- B.E. (Hons.) Electrical & Electronics: List of Discipline Core Courses: S. No. Course No. Course Title L P UDocument4 pagesB.E. (Hons.) Electrical & Electronics: List of Discipline Core Courses: S. No. Course No. Course Title L P UDhivya NNo ratings yet

- Electrical EngineeringDocument2 pagesElectrical EngineeringSantosh SandyNo ratings yet

- Core Architecture:: Container BasedDocument3 pagesCore Architecture:: Container BasedDhivya NNo ratings yet

- Theoretical Study On Active FiltersDocument2 pagesTheoretical Study On Active FiltersDhivya NNo ratings yet

- 9.speed Control of DC Motor Using Chopper DriveDocument8 pages9.speed Control of DC Motor Using Chopper DriveDhivya N100% (2)

- Soil AnalysisDocument13 pagesSoil AnalysisDhivya NNo ratings yet

- B&R PackMLDocument20 pagesB&R PackMLgo4viewNo ratings yet

- Fire c166Document108 pagesFire c166carver_uaNo ratings yet

- Fast BeamDocument2 pagesFast BeamSimila Razzak RahmanNo ratings yet

- (Entrance-Exam - Net) - Birlasoft Placement Exam Sample Paper 5Document4 pages(Entrance-Exam - Net) - Birlasoft Placement Exam Sample Paper 5Chayan UpadhyayNo ratings yet

- E85001-0646 - Intelligent Smoke DetectorDocument4 pagesE85001-0646 - Intelligent Smoke DetectorDauXuan HuynhNo ratings yet

- Philips SDK ManualDocument16 pagesPhilips SDK ManualMartin HríbikNo ratings yet

- XBOX 360 Jtag and Modifying TutorialDocument31 pagesXBOX 360 Jtag and Modifying TutorialNumair Imran100% (2)

- Bipolar Junction (BJT) Parameters: Circuit Small Signal TransistorsDocument4 pagesBipolar Junction (BJT) Parameters: Circuit Small Signal TransistorsPradyumna YambarNo ratings yet

- An6668 PDFDocument18 pagesAn6668 PDFCarlos OtzoyNo ratings yet

- Abbreviations (Updated)Document18 pagesAbbreviations (Updated)muhammad.wbaigNo ratings yet

- Design Verification With e 0131413090 9780131413092 CompressDocument410 pagesDesign Verification With e 0131413090 9780131413092 CompressQUÂN LÊ HỒNGNo ratings yet

- Speed Control of 3 Phase Induction MotorDocument10 pagesSpeed Control of 3 Phase Induction MotorK.R.RaguramNo ratings yet

- IBM Pure Flex PDFDocument512 pagesIBM Pure Flex PDFDhanuka PathinayakeNo ratings yet

- On Chip Variation and CRPRDocument12 pagesOn Chip Variation and CRPRnizam_shaik100% (6)

- PCH Install Guide Extras PackDocument2 pagesPCH Install Guide Extras PackThiago HaksNo ratings yet

- RC10PRD 10 11 AwrDocument52 pagesRC10PRD 10 11 AwrAnonymous URVO3VDKNo ratings yet

- Módulos SIGA CC1 e CC2Document6 pagesMódulos SIGA CC1 e CC2leomsilveiraNo ratings yet

- 5620 SAM Part Number ListingDocument109 pages5620 SAM Part Number ListingSa VahidiNo ratings yet

- Question Bank - CC LAQDocument6 pagesQuestion Bank - CC LAQFazalUrRahmanNo ratings yet

- Network OrchestrationDocument2 pagesNetwork OrchestrationMo ElNo ratings yet

- Online Ups: ME-1000-FTU ME-2000-FTU ME-3000-FTU ME-6000-FTUDocument2 pagesOnline Ups: ME-1000-FTU ME-2000-FTU ME-3000-FTU ME-6000-FTUtrdNo ratings yet

- BASIC: Beginner's All-Purpose Symbolic Instruction Code: What Does BASIC Look Like A Larger Program: Animal - BASDocument6 pagesBASIC: Beginner's All-Purpose Symbolic Instruction Code: What Does BASIC Look Like A Larger Program: Animal - BASAtanu DasNo ratings yet

- CA7 NotesDocument27 pagesCA7 Noteshprasad13100% (1)

- Brother 190 SM 04Document19 pagesBrother 190 SM 04Sunny SinghNo ratings yet

- Syllabus of DataStage CourseDocument8 pagesSyllabus of DataStage CourseDinesh SanodiyaNo ratings yet

- Setup Hold TimeDocument28 pagesSetup Hold Timeavneesh_singh100% (1)

- 9A04701 Embedded Real Time Operating SystemsDocument4 pages9A04701 Embedded Real Time Operating SystemssivabharathamurthyNo ratings yet

- Sales Force Apex Language ReferenceDocument520 pagesSales Force Apex Language ReferenceCharan TejaNo ratings yet

- Emerson Automated Patch Management ServiceDocument8 pagesEmerson Automated Patch Management ServicebioNo ratings yet

- Drawbot Using Arduino UnoDocument17 pagesDrawbot Using Arduino UnoAnukriti LeeNo ratings yet