Professional Documents

Culture Documents

22 Field Induced Charged Device Model

Uploaded by

MirnaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

22 Field Induced Charged Device Model

Uploaded by

MirnaCopyright:

Available Formats

JEDEC

STANDARD

Field-Induced Charged-Device Model

Test Method for Electrostatic-

Discharge-Withstand Thresholds of

Microelectronic Components

JESD22-C101F

(Revision of JESD22-C101E, December 2009)

OCTOBER 2013

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and

approved through the JEDEC Board of Directors level and subsequently reviewed and approved

by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating

misunderstandings between manufacturers and purchasers, facilitating interchangeability and

improvement of products, and assisting the purchaser in selecting and obtaining with minimum

delay the proper product for use by those other than JEDEC members, whether the standard is to

be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption

may involve patents or articles, materials, or processes. By such action JEDEC does not assume

any liability to any patent owner, nor does it assume any obligation whatever to parties adopting

the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to

product specification and application, principally from the solid state device manufacturer

viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or

publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in

the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or

publication should be addressed to JEDEC at the address below, or refer to www.jedec.org under

Standards and Documents for alternative contact information.

Published by

JEDEC Solid State Technology Association 2013

3103 North 10th Street

Suite 240 South

Arlington, VA 22201-2107

This document may be downloaded free of charge; however JEDEC retains the

copyright on this material. By downloading this file the individual agrees not to

charge for or resell the resulting material.

PRICE: Contact JEDEC

Printed in the U.S.A.

All rights reserved

PLEASE!

DONT VIOLATE

THE

LAW!

This document is copyrighted by JEDEC and may not be

reproduced without permission.

For information, contact:

JEDEC Solid State Technology Association

3103 North 10th Street

Suite 240 South

Arlington, VA 22201-2107

or refer to www.jedec.org under Standards-Documents/Copyright Information.

JEDEC Standard No. 22-C101F

TEST METHOD C101F

FIELD-INDUCED CHARGED-DEVICE MODEL TEST METHOD FOR

ELECTROSTATIC-DISCHARGE-WITHSTAND THRESHOLDS OF

MICROELECTRONIC COMPONENTS

Introduction

This standard describes a uniform method for establishing charged device model (CDM) electrostatic

discharge (ESD) withstand thresholds. The update allows tests to be partitioned across multiple

samples.

This revision enables testing to be done to limit cumulative related failures, and also aligns the

testing of CDM to HBM in terms of testing flexibility.

-i- Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Test Method C101F -ii-

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 1

TEST METHOD C101F

FIELD-INDUCED CHARGED-DEVICE MODEL TEST METHOD FOR

ELECTROSTATIC-DISCHARGE-WITHSTAND THRESHOLDS OF

MICROELECTRONIC COMPONENTS

(From JEDEC Board Ballot JCB-04-102, JCB-08-60, JCB-09-87, and JCB-13-53 formulated under the

cognizance of the JC-14.1 Committee on Reliability Test Methods for Packaged Devices.)

1 Scope

All packaged semiconductor components, thin film circuits, surface acoustic wave (SAW) components,

opto-electronic components, hybrid integrated circuits (HICs), and multi-chip modules (MCMs)

containing any of these components are to be evaluated according to this standard. The test methods

described in this standard may also be used to evaluate components that are shipped as wafers or bare

chips. To perform the tests, the components must be assembled into a package similar to that expected in

the final application. The package used shall be recorded.

2 Reference document

JESD625, Requirements for Handling Electrostatic Discharge-Sensitive (ESDS) Devices.

3 Terms and definitions

Charged device model (CDM): A specified circuit characterizing an ESD event that occurs when a

device acquires charge through some triboelectric (frictional) or electrostatic induction processes and then

abruptly touches a grounded object or surface.

Electrostatic discharge (ESD): A sudden transfer of electrostatic charge between bodies or surfaces at

different electrostatic potentials.

NOTE The terms discharge, pulse, ESD event and CDM stresses are equivalent for the purposes of this

document.

Field-induced charging: A charging method using electrostatic induction.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 2

4 Circuit schematic for the CDM simulator

4.1 The waveforms produced by the simulator shall meet the specifications of 5.1 through 8.

4.2 A schematic for the CDM test circuit is shown in Figure 1. (Other equivalent circuits are allowed if

the generated waveform meets the requirements of 5.1 through 8.) A detachable discharge head (see

Figure 1), consisting of the pogo probe, radial resistor, top ground plane, semi-rigid coaxial cable, and the

support arm, is used to initiate the discharge. The top ground plane shall be a square conductive plate with

edge length of 63.5 mm 6.35 mm (2.5 in 0.25 in). The discharge path includes a 1 ohm resistive

current probe of at least 3 GHz bandwidth for waveform monitoring. The cable from the 1 ohm resistor to

the oscilloscope should also have a bandwidth of at least 3 GHz. The thickness of the FR-4 dielectric shall

be 0.381 mm 0.038 mm (0.015 in 0.0015 in). The dielectric constant of the dielectric shall be

specified at 4.7(5%) at 1 MHz. The charging resistor shown in figure 1 shall be nominally 100 M or

greater.

Resistor values higher than 100 M may be used, but this may not allow large devices (greater than 25

mm by 25 mm) to fully saturate before being discharged by the probe assembly. This effect can be

overcome by adding a delay between discharges in the CDM tester programming software. If using a

resistor greater than 100 M, it is recommended that the tester or the device itself be characterized to

determine if a delay is needed for discharging large devices. A procedure for this large device delay

characterization is given in 6.2.1.

100 M

CHARGING

RESISTOR

Figure 1 Field induced CDM simulator

4.3 The Field-Induced Method shall be used to raise the component potential for a subsequent CDM

discharge. The component potential is raised by applying the test voltage to the field charging electrode

shown in Figure 1. The size of the charging electrode shall be larger than the size of the component and

the waveform generated shall meet the requirements in Table 3. The area of the dielectric should be the

same as or larger than the charge plate.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 3

5 Measurement instrumentation

5.1 Waveform verification requires the following instrumentation:

a) Oscilloscope with single shot bandwidth of 1 GHz with nominal 50 ohm input impedance and a real

time sample rate of 5 gigasamples per second. The bandwidth and sampling rate affect the observed

waveform. Use of oscilloscopes with differing bandwidth and sampling rate are permitted only if

appropriate hardware or software filtering is used to produce a bandwidth and sampling equivalent to

that specified here.

b) Ohmmeter capable of measuring a resistance of 1.0 0.01 ohm.

c) A capacitance meter with a resolution of 0.20 pF, a measurement accuracy of 3% and a measurement

frequency of at least 1 MHz.

d) Standard Test modules - One small and one large with the dimensions listed in Table 2.

Table 1 Test modules

Disk Small Large

Diameter mm (inches) 8.89 0.127 (0.350 0.005) 25.4 0.127 (1.000 0.005)

Thickness mm (inches) 1.27 0.05 (0.050 0.002) 1.27 0.05 (0.050 0.002)

Capacitance at 1 MHz 6.8 pF 5% 55 pF 5%

5.2 The disks shall be made of brass plated with nickel or gold/nickel and may optionally have a gold

flash coating over the nickel. They shall be manufactured to the dimensions specified in Table 1 and shall

be verified once before the initial use.

NOTE CAUTION shall be exercised during the manufacture of the disks so that they are free from burrs. If the

perimeter of the disk has burrs then arcing may occur altering the results.

5.3 The standard test modules for the CDM simulator can be cleaned in an ultrasonic bath using

isopropanol for about 20 seconds and dried in a moderate air stream to prevent charge leakage during test

operation.

5.4 The capacitance of the small and large disks shall be measured while sitting on the dielectric/charge

plate, and shall conform to the values specified in Table 1.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 4

6 Simulator waveform verification

6.1 The three levels of CDM simulator verification tests are:

CDM Equipment Manufacturer Qualification

User Verification

Routine Verification

The tests are described in Table 2.

Table 2 Waveform verification tests

Manufacturer Qualification

Routine Verification

and User Verification

Record of waveforms required Yes Yes

Check (see 7.1) No Yes

Tests (see Table 3) #1 #1, #2, #3, #4

6.2 CDM Equipment Manufacturer Qualification - must be done by the CDM equipment manufacturer

when the simulator is installed. High-speed instrumentation must be used, including an oscilloscope that

meets the requirements in 5.1. All three qualification tests in clause 8 are required, and the test waveforms

must be permanently recorded with copies supplied to the user when requested.

6.2.1 Charging Resistor / Charging Delay Characterization Procedure - Using the large test module disk

(see Table 1), measure the average of 10 pulses of the peak current magnitude (Ip) using a +500V plate

voltage.

Take one set of measurements with the pre- and post- charge delay setting set to 0 ms. Take another set of

measurements with the pre-charge delay set at 500 ms. If the Ip is the same for both measurements, a

delay does not need to be added to test large devices. If a delay is needed, 500 ms is long enough for

most devices. Alternatively, the tester hardware can be modified by adding a lower valued charging

resistor and then re-verified with this procedure. The same procedure can be used on a ground pin of a

device to determine the optimum amount of delay needed for a specific device.

6.3 User Verification - done during initial acceptance testing, whenever the equipment is serviced, and on

a regular basis at least once per month. The same tests are done as in the manufacturer's qualification.

Waveforms must be recorded and stored for comparison with the manufacturer's waveforms and the

weekly verification waveforms.

6.4 Routine Verification - Performed at the beginning of each shift the simulator is used. Only test #1 in

clause 8 is required. The user shall observe the waveforms and compare them with the previously

recorded waveforms.

6.5 If the waveforms do not meet the requirement in clause 8, reject any data obtained after the last

successful verification.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 5

7 Measurement procedure

7.1 With the ohmmeter, verify that the resistance of the current sensing resistors in all discharge heads to

be used is 1 +/- 0.1 ohm and record the value for use in computing the peak current.

7.2 With the capacitance meter, verify that the capacitance (at 1 MHz) of the small and large disks when

placed on the dielectric/charge plate meet the requirements in Table 1.

7.3 With the use of the standard modules in 5.1, perform the four tests in clause 8. For each test,

1) Raise the potential of the standard test module to the voltage indicated in Table 3.

2) Discharge the standard test module at least three times at both positive and negative polarities.

NOTE With the Field-Induced CDM technique, both discharge polarities are obtained on alternate discharges with

a single power supply setting. Therefore the power supply voltage may be set to either polarity. The peak currents

should have the same magnitude but opposite sign for the two discharge polarities.

3) Record the waveforms using the oscilloscope and take the average values of the parameters specified

in Table 3.

4) Repeat the step 1 through step 3 for additional discharge heads as needed.

5) If the waveform characteristics do not meet the requirements in Table 3, clean the test modules

(see 6.3) and repeat step 1 through step 3.

6) If the waveform still can not meet the requirements in Table 3, any data obtained since the last

verification shall be invalidated and the simulator shall be serviced.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 6

8 Waveform characteristics

The waveforms shall appear as shown in Figure 2 for the positive polarity and its reverse for the negative

polarity. The average values specified in 7.3 shall meet the specifications in Table 3.

Table 3 CDM waveform characteristics

Test Number

#1 #2 #3 #4

Standard test module Small Small Large Large

Test voltage (V) 500 ( 5%) 1000 ( 5%) 200 ( 5%) 500 ( 5%)

Peak current magnitude (A) Ip 5.75 ( 15%) 11.5 ( 15%) 4.5 ( 15%) 11.5 ( 15%)

Rise time (ps) tr <400 <400 - -

Full width at half height (ns) Td 1.0 0.5 1.0 0.5 - -

Undershoot (A, max.) U- <50% Ip <50% Ip <50% Ip <50% Ip

Overshoot U+ <25% Ip <25% Ip <25% Ip <25% Ip

Figure 2 CDM current waveform

9 Voltage levels

9.1 The recommended voltage levels for CDM ESD testing are:

125 V 500 V

250 V 1000 V

Testing above 1000 volts is not recommended.

NOTE Recommended voltage levels from previous revisions of this standard may also be used (100 V, 200 V,

500 V and 1000 V).

9.2 To determine the threshold more accurately, it is permitted to test at any voltage level >= 100 V and

<=1000 V in addition to those recommended above.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 7

10 Test procedures

10.1 The test shall be carried out at room temperature. Ambient humidity shall not exceed 60% RH.

10.2 Testing may begin at any convenient voltage level listed in 9.1.

10.3 Unless otherwise specified, obtain three samples that have been verified to meet their data

specifications. For component qualification sample size see JESD47.

10.4 For each component, apply at least one positive and at least one negative discharge to each pin (For

Field Induced CDM simulators, a negative pulse automatically follows a positive pulse or vice-versa).

Allow enough time (>200 ms) between discharges for the component to reach the full test voltage level.

Verify a discharge pulse occurs for each polarity by monitoring the discharge event detector output or

connecting an oscilloscope to the current monitoring resistor.

NOTE If there are concerns about the repeatability of current pulses, it is recommended to monitor and record the

peak current with an oscilloscope that meets or exceeds the requirements in 5.1.

Stresses may be partitioned by polarity, using a sample size of at least three units per polarity. Pins may

also be partitioned into one or more sets of samples, provided that each pin of the device is a member of

at least one set. Each set should have a minimum of three units.

Different devices may be used for each polarity as long as at least three devices are used for each polarity;

i.e., 3 units for positive discharge and 3 units for negative discharge. Separate devices may also be used

for different pin groups as long as each group is tested on 3 devices.

10.5 Test each of the components, using the failure criteria in 11.

10.6 Components that pass the test may be reused at other voltage levels. Components that fail may not

be used in tests at other levels. It is permitted to use new components for every voltage level. That is,

step-stressing is not required.

10.7 The component passes a voltage level if all three samples stressed at this level pass. The component

code fails at the voltage level if one or more samples fail at this level.

10.8 The CDM WITHSTAND THRESHOLD of the COMPONENT is the highest level for which the

specified number of stressed samples (usually three out of three) pass. If the component does not pass any

level, its threshold is 0 V. In addition, no sample failure shall occur at any test voltage level lower than

the withstand threshold.

10.9 CDM stressing and reporting of products shipped and assembled onto printed wiring boards as bare

die: Standardized CDM stressing of bare die is currently not defined due to equipment limitations.

Products shipped as bare die shall be placed in a package for purposes of performing CDM stressing, as

determined by package test limitations. CDM pass/fail voltages shall be reported with the package type(s)

used for CDM testing clearly noted. If more than one package type is used for CDM stressing, either all

package type data, or worst case data shall be reported.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 8

11 Failure criteria

A component will be defined as a failure if, after exposure to ESD, it no longer meets its data sheet

specifications.

NOTE 1 It is suggested that electrical testing be performed within 96 hours of ESD testing. Parametric and

functional testing shall be performed at room temperature and, if applicable, at high temperature.

NOTE 2 A failure at a given voltage level may be discounted if proven by failure analysis that is not CDMESD

related. If the failure analysis is inconclusive a second tightened sample of six devices shall be pulled and stressed at

the same voltage level. If no CDM-related failures are observed among these six devices then the part is considered

to have passed at that level and the device may be tested at the next voltage level in the stressing regimen.

12 Classification criteria

All samples must meet the test requirements of this document up to a particular voltage level in order for

the part to be classified as meeting a particular sensitivity classification.

Devices shall be classified as follows:

CLASS C0A <125 V

CLASS C0B 125 to <250 V

CLASS C1 250 to <500 V

CLASS C2 500 to <1000 V

CLASS C3 1000 V or greater

13 Supplementary information

13.1 Components used for CDM test shall not be used for any prior or future qualification tests.

13.2 All operators shall wear grounding straps when handling the components. The test components shall

be handled with extreme care, using ESD preventive procedure outlined in JESD625.

13.3 Components should not be placed within 610 mm (24 inches) of the discharge head while the tester

is operating to avoid potential damage from the radiated transient signal.

13.4 Components shall be transported in appropriate ESD-protective packaging. If the CDM withstand

threshold is 200 V or less, shipping tubes or tape-and-reel packaging should not be used. Contact

customers for information on special packing materials.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 9

Annex A (informative) Differences between JESD22-C101F and JESD22-C101E

This annex briefly describes most of the changes made to entries that appear in this standard,

JESD22-C101F, compared to its predecessor, JESD22-C101E (December 2009) as well as changes

between earlier revisions. Some punctuation changes are not included.

Clause Description of Change

4.2 Specified the charging resistor to be nominally 100 M. Added a paragraph related to

the charging resistor.

6.2.1 Added a section related to charging resistor characterization. Measurements may be

made on a large verification module or packaged IC.

9.1 Modified the recommended stress voltage levels to align with Industry Council

recommendations. Limited CDM stress to 1000V or less.

12 Updated Classification levels to align to the Industry Council recommendations and

better overall alignment to JS-001.

A.1 Changes to revision of JESD22-C101D (JESD22-C101E)

Clause Description of Change

10.4 replaced 1st paragraph with new paragraph and note.

A.2 Changes to revision of JESD22-C101C (JESD22-C101D)

Clause Description of Change

10.4 Modified and added text

A.3 Changes to revision of JESD22-C101B.01 (JESD22-C101C)

Clause Description of Change

5.1a Waveform capture bandwidth limited to 1GHz. Higher bandwidth equipment may be

used if filtered to produce effective 1GHz. Removed note.

7.1 Require use of actual monitoring resistor value rather than default 1 ohm. Added material

at end of sentence.

7.3 Changed number of pulses required for waveform verification from five to three to be

consistent with previous change in number of stressing pulses from five to three.

10 Added 10.9 to clarify language describing CDM characterization of die intended to be

shipped unpackaged. Such device must be evaluated using suitable package.

11 Clarified treatment of non-CDM test failures

ALL Corrected typographical and grammatical errors in several sections.

Test Method C101F

(Revision of Test Method C101E)

JEDEC Standard No. 22-C101F

Page 10

A.4 Changes to revision of JESD22-C101-B (JESD22-C101B.01)

Clause Description of Change

4.2 Corrected decimal point in the thickness of the FR-4.

Table 2 Clarified clause references in the first column

8 First paragraph, changed 7.2 to 7.3

A.5 Changes to revision of JESD22-C101-A (JESD22-C101-B)

Clause Description of Change

ALL Renumbered clauses, due to format issue. (All clauses and subclauses affected.)

3 Added NOTE to Electrostatic Discharge (ESD)

10.4 Changed five to three 2 times.

Test Method C101F

(Revision of Test Method C101E)

Standard Improvement Form JEDEC JESD22-C101F

The purpose of this form is to provide the Technical Committees of JEDEC with input from the industry

regarding usage of the subject standard. Individuals or companies are invited to submit comments to

JEDEC. All comments will be collected and dispersed to the appropriate committee(s).

If you can provide input, please complete this form and return to:

JEDEC Fax: 703.907.7583

Attn: Publications Department

3103 North 10th Street

Suite 240 South

Arlington, VA 22201-2107

1. I recommend changes to the following:

Requirement, clause number

Test method number Clause number

The referenced clause number has proven to be:

Unclear Too Rigid In Error

Other

2. Recommendations for correction:

3. Other suggestions for document improvement:

Submitted by

Name: Phone:

Company: E-mail:

Address:

City/State/Zip: Date:

You might also like

- Jedec StandardDocument22 pagesJedec StandardFrank ChenNo ratings yet

- JESD22 B110A Sub Assembly ShockDocument16 pagesJESD22 B110A Sub Assembly ShockTan Long BinNo ratings yet

- Temperature, Bias, and Operating LifeDocument14 pagesTemperature, Bias, and Operating LifeMirnaNo ratings yet

- JESD22-B103B Vibration, Variable FrequencyDocument16 pagesJESD22-B103B Vibration, Variable Frequencyyangmingliu0709No ratings yet

- JEDEC JESD22a101cDocument12 pagesJEDEC JESD22a101cAglieglie BrazorNo ratings yet

- Jesd51 13Document14 pagesJesd51 13truva_kissNo ratings yet

- Jedec 22a111Document18 pagesJedec 22a111Rafael Palhas DomingosNo ratings yet

- Mechanical Shock - Component andDocument14 pagesMechanical Shock - Component andMirna100% (1)

- Low Temperature Storage LifeDocument10 pagesLow Temperature Storage LifeMirna0% (1)

- Steady State Temperature HumidityDocument12 pagesSteady State Temperature HumidityMirnaNo ratings yet

- High Temperature Storage LifeDocument12 pagesHigh Temperature Storage LifeMirnaNo ratings yet

- Jedec Permanent MarkingDocument14 pagesJedec Permanent Markingbeach_lover_1970No ratings yet

- JEDEC - Mechanical Shock - 22b104cDocument12 pagesJEDEC - Mechanical Shock - 22b104cAglieglie BrazorNo ratings yet

- Temperature CyclingDocument18 pagesTemperature CyclingMirnaNo ratings yet

- Cycled Temperature Humidity BiasDocument12 pagesCycled Temperature Humidity BiasMirnaNo ratings yet

- JESD22-A100C Cycled Temp Humid Bias TestDocument12 pagesJESD22-A100C Cycled Temp Humid Bias Testtehky63No ratings yet

- Eia/Jedec Standard: Test Method A110-B Highly-Accelerated Temperature and Humidity Stress Test (HAST)Document11 pagesEia/Jedec Standard: Test Method A110-B Highly-Accelerated Temperature and Humidity Stress Test (HAST)Bruno SotoNo ratings yet

- Thermal Impedance Measurement ForDocument16 pagesThermal Impedance Measurement ForMirnaNo ratings yet

- Jesd22 A114dDocument20 pagesJesd22 A114dSathish Kumar YallampalliNo ratings yet

- 22A105CDocument12 pages22A105CDuram_Han_2546No ratings yet

- Jedec 22B112A 1Document30 pagesJedec 22B112A 1Shih Chien ChenNo ratings yet

- An Update On Revisions To: StandardsDocument6 pagesAn Update On Revisions To: StandardsStefano MologniNo ratings yet

- Jesd625 A PDFDocument30 pagesJesd625 A PDFCezaryCezas100% (1)

- Jedec Standard: N-Channel MOSFET Hot Carrier Data AnalysisDocument15 pagesJedec Standard: N-Channel MOSFET Hot Carrier Data AnalysisBenchNo ratings yet

- Jedec Standard: N-Channel MOSFET Hot Carrier Data AnalysisDocument15 pagesJedec Standard: N-Channel MOSFET Hot Carrier Data AnalysisBenchNo ratings yet

- Jesd51 12Document24 pagesJesd51 12liuxc111No ratings yet

- Aec Q101-004Document7 pagesAec Q101-004mathurashwaniNo ratings yet

- JESD22B113A Board Level Cyclic Bend Test Method For Interconnect ReliabilityDocument22 pagesJESD22B113A Board Level Cyclic Bend Test Method For Interconnect Reliabilityyangmingliu0709No ratings yet

- Jedec Standard: Electrically Erasable Programmable ROM (EEPROM) Program/Erase Endurance and Data Retention Stress TestDocument23 pagesJedec Standard: Electrically Erasable Programmable ROM (EEPROM) Program/Erase Endurance and Data Retention Stress TestsupNo ratings yet

- HERMETICITYDocument8 pagesHERMETICITYMirnaNo ratings yet

- JEDEC 22A122 - Power Cycling Test - PCTDocument18 pagesJEDEC 22A122 - Power Cycling Test - PCTDaus Villa Jr.No ratings yet

- ESD Mod FICDM Tesy Method JEDECDocument6 pagesESD Mod FICDM Tesy Method JEDECNilesh NarkhedeNo ratings yet

- Jedec Standard: Thermal Modeling OverviewDocument10 pagesJedec Standard: Thermal Modeling Overviewtruva_kissNo ratings yet

- Accelerated Moisture ResistanceDocument12 pagesAccelerated Moisture ResistanceMirnaNo ratings yet

- Edec Standard: CoretronicDocument14 pagesEdec Standard: Coretronic彭以和No ratings yet

- Test Method For The Measurement ofDocument16 pagesTest Method For The Measurement ofMirnaNo ratings yet

- Ball Shear Test Standard - Jedec - 22b117a - 20230810Document16 pagesBall Shear Test Standard - Jedec - 22b117a - 20230810đông bùi đứcNo ratings yet

- Jedec Standard: Information Requirements For The Qualification of Silicon DevicesDocument7 pagesJedec Standard: Information Requirements For The Qualification of Silicon DevicesMy HomeNo ratings yet

- Jedec Standard: Integrated Circuit Thermal Test Method Environmental Conditions - Junction-to-BoardDocument17 pagesJedec Standard: Integrated Circuit Thermal Test Method Environmental Conditions - Junction-to-BoardMarcio SilvaNo ratings yet

- Ipc 9592 Final Draft 0407 Normas LayoutDocument92 pagesIpc 9592 Final Draft 0407 Normas LayoutDomRuanNo ratings yet

- Jedec Standard: DELPHI Compact Thermal Model GuidelineDocument24 pagesJedec Standard: DELPHI Compact Thermal Model GuidelineAniketKulkarniNo ratings yet

- Jesd625 ADocument13 pagesJesd625 ACezaryCezasNo ratings yet

- Jedec Standard: Els ServiçosDocument18 pagesJedec Standard: Els ServiçosEverton LuizNo ratings yet

- Dielectric Breakdown Voltage of Insulating Liquids Using VDE ElectrodesDocument5 pagesDielectric Breakdown Voltage of Insulating Liquids Using VDE ElectrodesJavier NegretteNo ratings yet

- Zero Defect TestingDocument4 pagesZero Defect TestingNagamuthu PandianNo ratings yet

- Eia 364 21CDocument16 pagesEia 364 21CMetin100% (1)

- 32-'Msi-O3: Metal Clad Gas Insulated Medium Voltage Switchgear KV, 13.8 KV, 33 Kvor 34.5 KV)Document43 pages32-'Msi-O3: Metal Clad Gas Insulated Medium Voltage Switchgear KV, 13.8 KV, 33 Kvor 34.5 KV)Mahmoud MoezNo ratings yet

- General Specification For Electrical/Electronic Components and Subsystems, Electromagnetic CompatibilityDocument53 pagesGeneral Specification For Electrical/Electronic Components and Subsystems, Electromagnetic Compatibilityfghd100% (1)

- Jedec Standard: CoretronicDocument12 pagesJedec Standard: Coretronic彭以和No ratings yet

- SAE Standards Intro 2012 Rev IIDocument27 pagesSAE Standards Intro 2012 Rev IIEmily StewartNo ratings yet

- TP-22 Grounding SystemDocument8 pagesTP-22 Grounding SystemsathiyaseelanNo ratings yet

- 07IEC Member For IEC62271-200 MT14 PDFDocument15 pages07IEC Member For IEC62271-200 MT14 PDFedwinoriaNo ratings yet

- Emc 61000Document2 pagesEmc 61000tushar2.khandelwalNo ratings yet

- Jdec StandardDocument13 pagesJdec Standardswathi_efftronicsNo ratings yet

- Eia 364-21D 2008Document16 pagesEia 364-21D 2008hadiranji40% (1)

- Voltagetestingsystemfinal DriescherDocument12 pagesVoltagetestingsystemfinal DriescherMostafa MohmmedNo ratings yet

- Jdec 3 3VDocument16 pagesJdec 3 3VMohamedQassemNo ratings yet

- Ground TestingDocument31 pagesGround TestingabdulkadhirNo ratings yet

- Aec Q101-006Document14 pagesAec Q101-006MirnaNo ratings yet

- GBT 18333.2 - 2015 - Zinc-Air Batteries For Electric Road VehicleDocument17 pagesGBT 18333.2 - 2015 - Zinc-Air Batteries For Electric Road VehicleMirnaNo ratings yet

- New Marking GuidelinesDocument20 pagesNew Marking GuidelinesMirnaNo ratings yet

- R100 R 2 eDocument82 pagesR100 R 2 edesc82No ratings yet

- Functional Safety PDFDocument12 pagesFunctional Safety PDFGabriel BolatitoNo ratings yet

- Fluke 233 Certificate ConformityDocument2 pagesFluke 233 Certificate ConformityMirna100% (1)

- Solar BoatDocument1 pageSolar BoatMirnaNo ratings yet

- IPC Standards TreeDocument1 pageIPC Standards TreeMirnaNo ratings yet

- Blue Guide - 2014 - en PDFDocument134 pagesBlue Guide - 2014 - en PDFjasonNo ratings yet

- Iqrmx5 Manual enDocument44 pagesIqrmx5 Manual enMirnaNo ratings yet

- 5 ClanakDocument10 pages5 ClanakMirnaNo ratings yet

- Zener and Voltage Regulator DiodeDocument28 pagesZener and Voltage Regulator DiodeMirnaNo ratings yet

- Sigurnost EV U AmericiDocument30 pagesSigurnost EV U AmericiMirnaNo ratings yet

- 5 ClanakDocument10 pages5 ClanakMirnaNo ratings yet

- Power MOSFET Equivalent SeriesDocument10 pagesPower MOSFET Equivalent SeriesMirnaNo ratings yet

- Short Circuit Withstand Time TestDocument12 pagesShort Circuit Withstand Time TestMirnaNo ratings yet

- Large Animal Safety ChecklistDocument1 pageLarge Animal Safety ChecklistMirnaNo ratings yet

- Cycled Temperature Humidity BiasDocument12 pagesCycled Temperature Humidity BiasMirnaNo ratings yet

- Mechanical Shock - Component andDocument14 pagesMechanical Shock - Component andMirna100% (1)

- Method For Measurement of PowerDocument16 pagesMethod For Measurement of PowerMirnaNo ratings yet

- Thermal Impedance Measurement ForDocument16 pagesThermal Impedance Measurement ForMirnaNo ratings yet

- Procedure For Measuring N-ChannelDocument20 pagesProcedure For Measuring N-ChannelMirnaNo ratings yet

- Test Method For Measurement ofDocument12 pagesTest Method For Measurement ofMirnaNo ratings yet

- Gate Charge Test MethodDocument14 pagesGate Charge Test MethodMirnaNo ratings yet

- Solid-State Drive (SSD) RequirementsDocument36 pagesSolid-State Drive (SSD) RequirementsMirnaNo ratings yet

- Solid-State Drive (SSD) EnduranceDocument26 pagesSolid-State Drive (SSD) EnduranceMirnaNo ratings yet

- Procedure For Wafer-Level DCDocument32 pagesProcedure For Wafer-Level DCMirnaNo ratings yet

- Test Method For The Measurement ofDocument16 pagesTest Method For The Measurement ofMirnaNo ratings yet

- Jdec StandardDocument13 pagesJdec Standardswathi_efftronicsNo ratings yet

- SC Ua70Document118 pagesSC Ua70angel quintero100% (3)

- HARK Acuitus Service Manual Rev C PDFDocument162 pagesHARK Acuitus Service Manual Rev C PDFmarcelo ribeiroNo ratings yet

- ISO5451 High-CMTI 2.5-A and 5-A Isolated IGBT, MOSFET Gate Driver With Active Protection FeaturesDocument40 pagesISO5451 High-CMTI 2.5-A and 5-A Isolated IGBT, MOSFET Gate Driver With Active Protection FeaturesamitNo ratings yet

- Neca Bicsi 607-2011 PDFDocument34 pagesNeca Bicsi 607-2011 PDFJosé Manuel Gambino100% (1)

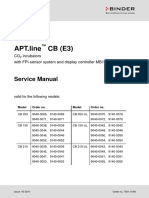

- APT - Line CB (E3) : Service ManualDocument100 pagesAPT - Line CB (E3) : Service ManualDavid EguezNo ratings yet

- CKT ProtectionDocument21 pagesCKT Protectionajay rNo ratings yet

- Philips MCD388-55 Sistema Reproductor DVD Manual de Servicio PDFDocument45 pagesPhilips MCD388-55 Sistema Reproductor DVD Manual de Servicio PDFMario Rodriguez JuradoNo ratings yet

- Datasheet Potenciometro DigitalDocument10 pagesDatasheet Potenciometro Digitalpsilva12No ratings yet

- TPS56320x 4.5-V To 17-V Input, 3-A Synchronous Step-Down Voltage Regulator in SOT-23Document27 pagesTPS56320x 4.5-V To 17-V Input, 3-A Synchronous Step-Down Voltage Regulator in SOT-23muneNo ratings yet

- Samsung DVD v5600 v6600 SMDocument239 pagesSamsung DVD v5600 v6600 SMchuftaNo ratings yet

- 150i-240i Heracell Service ManualDocument47 pages150i-240i Heracell Service Manualpham toan100% (13)

- Samsung Ua32d4003b Ua22d5003br Chassis U56h U57g PDFDocument55 pagesSamsung Ua32d4003b Ua22d5003br Chassis U56h U57g PDFShailesh VajaNo ratings yet

- Richard Wolf 2271Document39 pagesRichard Wolf 2271Akram AlwahibiNo ratings yet

- Service Manual MCD 3000Document54 pagesService Manual MCD 3000Anhell Salvador Loza100% (1)

- ULQ200xA-Q1 High-Voltage High-Current Darlington Transistor ArraysDocument26 pagesULQ200xA-Q1 High-Voltage High-Current Darlington Transistor ArraysDanny Alexander Bodegas pinedaNo ratings yet

- Powerflex 700sDocument214 pagesPowerflex 700sJuan Manuel GuerreroNo ratings yet

- Samsung MySono U5 Ultrasound - Service ManualDocument177 pagesSamsung MySono U5 Ultrasound - Service ManualEcomedical Pluss100% (1)

- Static Electricity: Test Yourself 16.1 (Page 309)Document5 pagesStatic Electricity: Test Yourself 16.1 (Page 309)Jack Kowman100% (2)

- Obsolete: Ultralow Noise 20-Bit Audio DAC AD1862Document12 pagesObsolete: Ultralow Noise 20-Bit Audio DAC AD1862Usval AnNo ratings yet

- 1993 Chevrolet Corvette SpecificationsDocument209 pages1993 Chevrolet Corvette Specificationsedosr100% (2)

- PGA305 Signal Conditioner and Transmitter For Pressure SensorsDocument81 pagesPGA305 Signal Conditioner and Transmitter For Pressure SensorsFaisalNo ratings yet

- 1500R Installation 10 09Document61 pages1500R Installation 10 09Marcos Valera100% (1)

- P4fl3.3a Au - Series 1866315Document7 pagesP4fl3.3a Au - Series 1866315Adam SchwemleinNo ratings yet

- MB Manual Ga z170x Gaming g1 eDocument136 pagesMB Manual Ga z170x Gaming g1 emanuelNo ratings yet

- Panasonic TX-l32c10b TX-l32c10e TX-l32c10es Chassis Glp24Document60 pagesPanasonic TX-l32c10b TX-l32c10e TX-l32c10es Chassis Glp24Toni Martin SebéNo ratings yet

- Tools in PC Hardware ServicingDocument20 pagesTools in PC Hardware ServicingPaula ChoiceNo ratings yet

- NewDocument16 pagesNewduong nguyen dai100% (1)

- Ceragon FibeAir IP-20C Installation Guide Rev D.01Document174 pagesCeragon FibeAir IP-20C Installation Guide Rev D.01Telworks RSNo ratings yet

- Delexi Cdi. eDocument266 pagesDelexi Cdi. eNouman Mughal100% (1)

- Manual - Service - PB560 - EnglishDocument260 pagesManual - Service - PB560 - EnglishAlejhandro navarroNo ratings yet