Professional Documents

Culture Documents

Funciones Booleanas 8

Uploaded by

Jeiner Rafael VasquezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Funciones Booleanas 8

Uploaded by

Jeiner Rafael VasquezCopyright:

Available Formats

UNDC Electrnica y Circuitos Digitales

RESUMEN DE SEMANA 8

8. FUNCIONES BOOLEANAS

8.1. LGEBRA DE BOOLE

El lgebra booleana difiere en gran medida del lgebra ordinaria, ya que a las constantes y

variables booleanas slo se les permite tener dos valores posibles: 0 y 1.

Por lo tanto, el 0 y el 1 booleanos no representan nmeros reales, sino el estado de una

variable de voltaje, o lo que se conoce como su nivel lgico.

8.2. TABLAS DE VERDAD

Una tabla de verdad es una herramienta para describir la forma en que la

salida de un circuito lgico depende de los niveles lgicos presentes en las

entradas del circuito. La tabla lista todas las posibles combinaciones de

niveles lgicos presentes en las entradas junto con los correspondientes

niveles en la salida.

8.3. FUNCIONES BSICAS

8.3.1. FUNCIN OR

=+

ENTRADA A ENTRADA B SALIDA F

0 0 0

0 1 1

1 0 1

1 1 1

8.3.2. FUNCIN AND

= .

ENTRADA A ENTRADA B SALIDA F

0 0 0

0 1 0

1 0 0

1 1 1

8.3.3. FUNCIN NOT

Mg. Joel Vilca 1

UNDC Electrnica y Circuitos Digitales

ENTRADA A SALIDA F

0 1

1 0

8.3.4. FUNCIN NOR

=

+

ENTRADA A ENTRADA B SALIDA F

0 0 1

0 1 0

1 0 0

1 1 0

8.3.5. FUNCIN NAND

=

.

ENTRADA A ENTRADA B SALIDA F

0 0 1

0 1 1

1 0 1

1 1 0

8.3.6. FUNCIN XOR (OR EXCLUSIVA)

ENTRADA A ENTRADA B SALIDA F

0 0 0

0 1 1

1 0 1

1 1 0

Mg. Joel Vilca 2

UNDC Electrnica y Circuitos Digitales

8.3.7. FUNCIN XNOR (NOR EXCLUSIVA)

ENTRADA A ENTRADA B SALIDA F

0 0 1

0 1 0

1 0 0

1 1 1

8.4. TEOREMAS DEL LGEBRA DE BOOLE

Sean x, y, z unas variables booleanas de entrada. Por lo tanto se cumple que:

1. x . 0 = 0

2. x . 1 = x

3. x . x = x

4. x . x = 0

5. x + 0 = x

6. x + 1 = 1

7. x + x = x

8. x + x = 1

9. x = x (Involucin)

10. x + y = y + x (Ley comunicativa)

11. x . y = y. x (Ley comunicativa)

12. x + (y + z) = (x + y) + z = x + y + z (Ley asociativa)

13. x(y. z) = (x. y). z = x. y. z (Ley asociativa)

14. (w + x)(y + z) = w. y + x. y + w. z + x. z (Ley distributiva)

15. x + x. y = x (Absorcin)

16. x + x. y = x + y

17. x + x. y = x + y

8.4.1. TEOREMAS DEMORGAN

Los teoremas de DeMorgan son extremadamente tiles para simplificar expresiones

en las cuales se invierte un producto o la suma de variables. Los dos teoremas son:

a)

(x + y) = x. y

b) (x.

)

y = x + y

Aunque estos teoremas estn declarados en trminos de las variables individuales x e

y, son tambin vlidos en situaciones en las que x y/o y son expresiones que

contienen ms de una variable.

Mg. Joel Vilca 3

UNDC Electrnica y Circuitos Digitales

8.5. REPRESENTACIN DE FUNCIONES BOOLEANAS

8.5.1. SUMA DE PRODUCTOS (SOP)

Cada una de las expresiones de suma de productos consiste de dos o ms trminos

AND (productos) a los que se les aplican la operacin OR. Cada trmino AND consiste

de una o ms variables que aparecen de manera individual, ya sea en forma

complementada o no complementada.

8.5.2. PRODUCTO DE SUMAS (POS)

Cada una de las expresiones de producto de las sumas consiste de dos o ms

trminos OR (sumas) a los que se les aplica una operacin AND. Cada trmino OR

consiste de una o ms variables en su forma complementada o no complementada.

8.6. MAPAS DE KARNAUGH

El mapa de Karnaugh es una herramienta grfica que se utiliza para simplificar una

ecuacin lgica o convertir una tabla de verdad en su correspondiente circuito lgico

mediante un proceso simple y ordenado. Aunque un mapa de Karnaugh puede usarse

para problemas en los que se involucre cualquier nmero de variables de entrada, su

utilidad prctica est limitada a cinco o seis variables.

8.6.1. FORMATO DEL MAPA DE KARNAUGH

Al igual que una tabla de verdad, el mapa de Karnaugh es un medio para mostrar la

relacin entre las entradas lgicas y la salida deseada.

Mg. Joel Vilca 4

UNDC Electrnica y Circuitos Digitales

8.6.2. AGRUPAMIENTO

La expresin para la salida "X" puede simplificarse mediante la combinacin apropiada

de las casillas en el mapa de Karnaugh que contengan 1s. Al proceso para combinar

estos 1s se le conoce como agrupamiento.

8.6.2.1. AGRUPAMIENTO DE PARES (GRUPOS DE DOS)

Al agrupar un par de 1s adyacentes en un mapa de Karnaugh se elimina la

variable que aparece tanto en forma no complementada como en forma

complementada.

8.6.2.1. AGRUPAMIENTO DE CUARTETOS (GRUPOS DE CUATRO)

Al agrupar un cuarteto de 1s adyacentes se eliminan las dos variables que

aparecen tanto en forma complementada como en forma no complementada.

8.6.2.1. AGRUPAMIENTO DE OCTETOS (GRUPOS DE OCHO)

Al agrupar un octeto de 1s adyacentes se eliminan las tres variables que aparecen

tanto en su forma complementada como en su forma no complementada.

Mg. Joel Vilca 5

UNDC Electrnica y Circuitos Digitales

8.6.3. PROCESO COMPLETO DE SIMPLIFICACIN

Los siguientes pasos son el procedimiento mediante el uso del mtodo del mapa de

Karnaugh, para simplificar una expresin booleana:

Paso 1: Construya el mapa de Karnaugh y coloque 1s en las casillas que

correspondan a los 1s en la tabla de verdad. Coloque 0s en las dems casillas.

Paso 2: Examine el mapa en busca de 1s adyacentes y marque los que no

sean adyacentes con cualquier otro 1. A stos se les conoce como 1s aislados.

Paso 3: A continuacin busque los 1s que sean adyacentes slo con otro 1.

Agrupe cualquier par que contenga este tipo de 1s.

Paso 4: Agrupe cualquier octeto, an y cuando contenga algunos 1s que ya se

hayan agrupado.

Paso 5: Agrupe cualquier cudruple que contenga uno o ms 1s que no se

hayan agrupado ya, asegurndose de utilizar el nmero mnimo de grupos.

Paso 6: Agrupe cualquier par necesario para incluir todos los 1 que no se

hayan agrupado todava, asegurndose de utilizar el nmero mnimo de

agrupamientos.

Paso 7: Forme la suma OR de todos los trminos generados, uno por cada

grupo.

8.6.4. CONDICIONES "NO IMPORTA"

Algunos circuitos lgicos pueden disearse de manera que haya ciertas condiciones

de entrada para las cuales no existan niveles de salida especificados. En otras

palabras, habr ciertas combinaciones de niveles de entrada en las que "no importa" si

la salida est en ALTO o en BAJO.

Mg. Joel Vilca 6

UNDC Electrnica y Circuitos Digitales

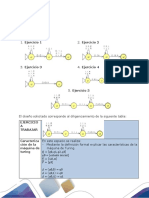

8.7. PROBLEMAS RESUELTOS

1. Simplifique las siguientes expresiones mediante el uso del lgebra booleana.

a) x = ABC + A C

Utilizando el teorema N15 (absorcin) del lgebra de Boole simplificamos y obtenemos:

x = (AB + A )C

Luego utilizando el teorema N16 del lgebra de Boole se reduce a:

x = (B + A )C

x = (A + B)C

b) q =

RST(R + S + T)

Utilizando el teorema N14 (Ley distributiva) del lgebra de Boole obtenemos:

q =

RSTR + RSTS + RSTT

Luego utilizando los teoremas N3 y N7 del lgebra de Boole simplificamos:

q = RST + RST + RST

q = RST

2. Reducir usando el lgebra booleana el circuito lgico combinacional de la

figura a una forma mnima.

La expresin para la salida del circuito es:

BC)C +

BC + D

X = (A A

Aplicando el teorema de DeMorgan y el lgebra booleana se tiene:

X = (A+B + C)C + A +B + C + D

X = AC + BC + CC + A + B + C + D

X = AC + BC + C + A + B + C + D

X = AC + BC + C + A + B + D

X = C(A + B + 1) + A + B + D

X=A+B+C+D

El circuito simplificado es una puerta OR de cuatro entradas, como se muestra en la siguiente

figura:

Mg. Joel Vilca 7

UNDC Electrnica y Circuitos Digitales

3. Use un mapa de Karnaugh para simplificar la expresin y = C(A

BD

+ D) + AB

C + D

.

Primero multiplique el primer trmino para tener la expresin como Suma de Productos (SOP):

y=A BCD

+ CD + ABC + D

Para escribir los 1s en el mapa de Karnaugh descomponemos la expresin como la Suma de

Productos completa en sus mnimos trminos:

y=A BCD B

+ (A +A B + AB + AB)CD + AB C(D + D) + (AB

C + A

BC + A BC + A

BC + ABC + ABC

+ ABC + ABC)D

y = ABCD + ABCD + ABCD + AB CD + ABCD + AB CD + ABCD + ABCD

+A BCD+A BCD

+A BCD

+ ABCD + ABCD + ABCD + ABCD

y=A BCD+A BCD + A BCD + ABCD + ABCD + AB CD + ABCD + ABCD+A BCD

+A BCD + ABCD

+ ABCD + ABCD

A partir de la expresin completa ubicamos en el mapa de Karnaugh cada trmino y lo ponemos

como 1s.

Agrupando mediante en octetos y cuartetos obtenemos del mapa de Karnaugh la expresin final

simplificada:

y = AB + C + D

Mg. Joel Vilca 8

You might also like

- Ecuaciones Diferenciales HomogéneasDocument14 pagesEcuaciones Diferenciales HomogéneasThe ShamanNo ratings yet

- Sistemas de Ecuaciones Diferenciales Lineales Parte 1Document6 pagesSistemas de Ecuaciones Diferenciales Lineales Parte 1Michael Martines IzquierdoNo ratings yet

- Ecuaciones Diferenciales Unidad 4Document28 pagesEcuaciones Diferenciales Unidad 4Jason Clemente0% (1)

- Proyecto Final E.D. Método Del AnuladorDocument27 pagesProyecto Final E.D. Método Del AnuladorEstefannya Carvajal Cruz50% (2)

- Ejercicios de Conversión de Bases (Metodos Numericos)Document1 pageEjercicios de Conversión de Bases (Metodos Numericos)Rafa Bautista0% (1)

- Aritmetica en Punto FlotanteDocument18 pagesAritmetica en Punto Flotantejorgekf13No ratings yet

- Teorema de La Función Implícita para Funciones de RM en RDocument7 pagesTeorema de La Función Implícita para Funciones de RM en RAnonymous tyXLCGZgNo ratings yet

- Ejercicios Independencia-Bondad de Ajuste - Regresion Lineal SimpleDocument2 pagesEjercicios Independencia-Bondad de Ajuste - Regresion Lineal SimpleDanny Medina MoncayoNo ratings yet

- Areas en Coordenadas Polares-ProblemasDocument3 pagesAreas en Coordenadas Polares-ProblemasMiguel Flores AndradeNo ratings yet

- g1 Cinematica PDFDocument5 pagesg1 Cinematica PDFFIMpeluchinNo ratings yet

- Diseño de circuitos secuenciales con MSIDocument9 pagesDiseño de circuitos secuenciales con MSIZaira GüzelNo ratings yet

- Representacion Por ModelosDocument3 pagesRepresentacion Por ModelosSebastian Sebastian0% (1)

- Árboles y GrafosDocument49 pagesÁrboles y Grafosomy2100% (2)

- Segunda Parte EJERCICIOSDocument1 pageSegunda Parte EJERCICIOShumbertoNo ratings yet

- Analisis AlgoritmosDocument33 pagesAnalisis AlgoritmosJose Dismar100% (1)

- Taller de REGRESIÓN LINEALDocument4 pagesTaller de REGRESIÓN LINEALConsueloSabogalNo ratings yet

- Foro Cuadratura Gaussiana A IPAC 2020Document2 pagesForo Cuadratura Gaussiana A IPAC 2020Daniel Mercado PadillaNo ratings yet

- RUTA OPTIMA - Implementar Métodos de Búsqueda para Encontrar La Ruta Mas Corta Entre Dos Ciudades Capitales de EcuadorDocument8 pagesRUTA OPTIMA - Implementar Métodos de Búsqueda para Encontrar La Ruta Mas Corta Entre Dos Ciudades Capitales de EcuadorChristian QuindeNo ratings yet

- Cholesky 2Document4 pagesCholesky 2Carlos Alberto CCdlcNo ratings yet

- Cuadratura GaussianaDocument33 pagesCuadratura GaussianaDiego ChávezNo ratings yet

- Algunas Distribuciones ContinuasDocument29 pagesAlgunas Distribuciones ContinuasJulieth BarriosNo ratings yet

- Programación lineal: Método simplexDocument26 pagesProgramación lineal: Método simplexLuis BurgosNo ratings yet

- CAPITULO 9. - Sistemas de Ecuaciones DiferencialesDocument23 pagesCAPITULO 9. - Sistemas de Ecuaciones DiferencialesAleNo ratings yet

- Valores y vectores característicos de una matrizDocument18 pagesValores y vectores característicos de una matrizdui123456789No ratings yet

- Automat AsDocument17 pagesAutomat AsDiego AceroNo ratings yet

- Aplicaciones de La Integral de RiemannDocument45 pagesAplicaciones de La Integral de RiemannEduardoLalo MamaniNo ratings yet

- Análisis Sintáctico y Matriz PredictivaDocument10 pagesAnálisis Sintáctico y Matriz PredictivaIrvin G. Contreras García0% (1)

- Complejidad espacial algoritmos 40Document7 pagesComplejidad espacial algoritmos 40Luciana Villanueva VasquezNo ratings yet

- NOTACION POLACA INVERSADocument11 pagesNOTACION POLACA INVERSAVictor Miguel LopezNo ratings yet

- Cuadraturas de GaussDocument4 pagesCuadraturas de GaussPedro RojasNo ratings yet

- Cambio de Variables en Integrales MúltiplesDocument6 pagesCambio de Variables en Integrales MúltiplesFernando LeonNo ratings yet

- Ensayo Ecuaciones DiferencialesDocument4 pagesEnsayo Ecuaciones DiferencialesjabondecalabazaNo ratings yet

- BaseDatosBecasDocument9 pagesBaseDatosBecasKevin Mejia0% (1)

- Proyecto Variable Compleja Copy PDFDocument13 pagesProyecto Variable Compleja Copy PDFAlejandro CalderonNo ratings yet

- MÉTODOS NUMÉRICOS PARA SISTEMAS DE ECUACIONESDocument2 pagesMÉTODOS NUMÉRICOS PARA SISTEMAS DE ECUACIONESNiko MartinezNo ratings yet

- Sistema LTIDocument3 pagesSistema LTIRicardo AqpNo ratings yet

- Campos VectorialesDocument28 pagesCampos VectorialesRodrigo Gutierrez Guadarrama100% (1)

- Funciones de Varias Variables (Recuperado 1) PDFDocument33 pagesFunciones de Varias Variables (Recuperado 1) PDFMicheNo ratings yet

- Informe AluDocument8 pagesInforme AluDanielSaniNo ratings yet

- Modelo SnaDocument8 pagesModelo SnaDamarisChambi100% (3)

- Aplicaciones de Notacion Polaca e InversaDocument6 pagesAplicaciones de Notacion Polaca e InversaAlejandra RomeroNo ratings yet

- Ciclos y condicionalesDocument7 pagesCiclos y condicionalesJohan SegoviaNo ratings yet

- Taller 1Document8 pagesTaller 1Anthony veraCNo ratings yet

- Señales y Su Clasificación Analógicas, Digitales, EléctricasDocument3 pagesSeñales y Su Clasificación Analógicas, Digitales, EléctricasNahum TorresNo ratings yet

- Algoritmos y Estructuras de DatosDocument192 pagesAlgoritmos y Estructuras de DatosAaronDaniel CarrilloTorrezNo ratings yet

- Lenguaje de Definición de Objetos (ODL)Document19 pagesLenguaje de Definición de Objetos (ODL)Adan_Enrique_J_4588No ratings yet

- 3.2 Variables Aleatorias ContinuasDocument27 pages3.2 Variables Aleatorias ContinuasBruno UnivazoNo ratings yet

- Diferenciación Numérica: Métodos NuméricosDocument18 pagesDiferenciación Numérica: Métodos NuméricosMaría Fernanda Suárez Gualteros100% (1)

- Análisis de grafos para determinar rutas en una redDocument3 pagesAnálisis de grafos para determinar rutas en una redhamilton giraldo vascoNo ratings yet

- Automata FinitoDocument12 pagesAutomata FinitoGerardo SandovalNo ratings yet

- Transformada de Laplace: Introducción, definición y propiedadesDocument8 pagesTransformada de Laplace: Introducción, definición y propiedadesgianco_x12No ratings yet

- Sistemas de Ecuaciones Lineales. EjerciciosDocument5 pagesSistemas de Ecuaciones Lineales. EjercicioscandelanibalNo ratings yet

- Backus Naur FormDocument15 pagesBackus Naur FormCarlos Noel Saracho EsquivelNo ratings yet

- Arboles B+Document22 pagesArboles B+s1a2n3d4r5a6100% (1)

- 2-.Relaciones de Orden ReticulosDocument19 pages2-.Relaciones de Orden ReticulosmicaelakorecNo ratings yet

- Informe 3Document4 pagesInforme 3Edison AlvearNo ratings yet

- Guía de Autoestudio - CombinacionalesDocument13 pagesGuía de Autoestudio - CombinacionalesFabrizio ArmoaNo ratings yet

- Sistemas de Procesos de ProducciónDocument44 pagesSistemas de Procesos de ProducciónJeiner Rafael VasquezNo ratings yet

- Sistemas de Procesos de ProducciónDocument32 pagesSistemas de Procesos de ProducciónJeiner Rafael VasquezNo ratings yet

- Sistemas de Procesos de ProducciónDocument32 pagesSistemas de Procesos de ProducciónJeiner Rafael VasquezNo ratings yet

- Nociones Geometría AnalíticaDocument128 pagesNociones Geometría AnalíticaJeiner Rafael VasquezNo ratings yet

- Matrices. Determinantes. Sistema de EcuacionesDocument48 pagesMatrices. Determinantes. Sistema de EcuacionesJeiner Rafael VasquezNo ratings yet

- Límite y ContinuidadDocument63 pagesLímite y ContinuidadJeiner Rafael VasquezNo ratings yet

- Examen Final de Dinamica de SistemasDocument1 pageExamen Final de Dinamica de SistemasJeiner Rafael VasquezNo ratings yet

- Ejercicios de programación lineal resueltosDocument2 pagesEjercicios de programación lineal resueltosJeiner Rafael VasquezNo ratings yet

- Circuito EléctricoDocument10 pagesCircuito EléctricoJeiner Rafael VasquezNo ratings yet

- Límite y ContinuidadDocument63 pagesLímite y ContinuidadJeiner Rafael VasquezNo ratings yet

- Aporte de Edgar MorinDocument13 pagesAporte de Edgar MorinJuan Carlos Amezquita100% (1)

- Catalogo Ball - Español Web 2021Document105 pagesCatalogo Ball - Español Web 2021sergio andres zamora auzzaNo ratings yet

- Unidades Funcionales PulmonaresDocument104 pagesUnidades Funcionales PulmonaresAndrea MartinezNo ratings yet

- Categorización Social y Construcción de Las Categorías SocialesDocument11 pagesCategorización Social y Construcción de Las Categorías SocialesFedeSGNo ratings yet

- La Tabla de La Esmeralda Hermes TrismegistusDocument9 pagesLa Tabla de La Esmeralda Hermes TrismegistusesperanzaNo ratings yet

- Qué Son Los ÉteresDocument13 pagesQué Son Los ÉteresAlexa Jane LiraNo ratings yet

- Evaluacion Inicial Gerencia de Mercadeo Sem 5Document4 pagesEvaluacion Inicial Gerencia de Mercadeo Sem 5YANAHIR0% (1)

- Libro Nexos - La Educacion Como Sistema PDFDocument114 pagesLibro Nexos - La Educacion Como Sistema PDFLuciana DacunaNo ratings yet

- Conceptos MuseografíaDocument3 pagesConceptos MuseografíaInternt EmanuelNo ratings yet

- Pap Solidario Corregido (1Document18 pagesPap Solidario Corregido (1Gustavo palacio garciaNo ratings yet

- Nuevos Activos AntioxidantesDocument24 pagesNuevos Activos AntioxidantesCRAULNo ratings yet

- En Nuestro Estudio Del Libro de Rut Veremos El Lado Amoroso de La RedenciónDocument50 pagesEn Nuestro Estudio Del Libro de Rut Veremos El Lado Amoroso de La RedenciónMarta Lorena Darce GarciaNo ratings yet

- El Cura de SaraguroDocument1 pageEl Cura de SaraguroCarlos Alberto Rodeiguez mesaNo ratings yet

- Programacion Anual Inglés 5° Grado 2023Document14 pagesProgramacion Anual Inglés 5° Grado 2023Julio MontoyaNo ratings yet

- Análisis de árbol de decisiones para caso de demanda por transgresión de patentesDocument9 pagesAnálisis de árbol de decisiones para caso de demanda por transgresión de patentesGisela OrozcoNo ratings yet

- Estructura proceso comunicación marketingDocument4 pagesEstructura proceso comunicación marketingSandry AmayaNo ratings yet

- Origen Del Laudo ArbitralDocument7 pagesOrigen Del Laudo ArbitralDIEGO CAÑARI TAFURNo ratings yet

- Conducción PersonalDocument11 pagesConducción PersonalMarco LeivaNo ratings yet

- Plan de Gobierno Juntos Por El Perú CarabaylloDocument9 pagesPlan de Gobierno Juntos Por El Perú CarabaylloClaudia OrtizNo ratings yet

- CNE2012 Conferencia Luis BretelDocument10 pagesCNE2012 Conferencia Luis BretelFernando Garcia LopezNo ratings yet

- Rituales de purificación en Campo de MontielDocument31 pagesRituales de purificación en Campo de MontielPríncipe del CrochetNo ratings yet

- Destrezas Bernice # 3Document74 pagesDestrezas Bernice # 3MarielaLeonMorenoNo ratings yet

- Extracto Planificación PedagógicaDocument2 pagesExtracto Planificación PedagógicaMiguel AtemporaliaNo ratings yet

- LUNALLENADocument2 pagesLUNALLENADiana Laura Ibarra BarrónNo ratings yet

- La Lectio DivinaDocument2 pagesLa Lectio DivinaYessica MoralesNo ratings yet

- Lamentaciones de Un Prepucio Shalom Auslander PDFDocument522 pagesLamentaciones de Un Prepucio Shalom Auslander PDFMarco Aurelio Castaño AriasNo ratings yet

- EXPERIENCIA DE APRENDIZAJE INTEGRAL DIVERSIFICADA N°05 - 1°y 2° INGLES Y ARTEDocument11 pagesEXPERIENCIA DE APRENDIZAJE INTEGRAL DIVERSIFICADA N°05 - 1°y 2° INGLES Y ARTEAntOny H. BarbozaNo ratings yet

- Unidad 1 El Consumidor Es El ReceptorDocument29 pagesUnidad 1 El Consumidor Es El Receptorpatricia martinez garcia100% (1)

- Solucion Del Fii Examen ParcialDocument6 pagesSolucion Del Fii Examen ParcialYacqui Adeli OblitasNo ratings yet

- Auditoría operativa para mejorar la eficiencia empresarialDocument1 pageAuditoría operativa para mejorar la eficiencia empresarialLuis DiazNo ratings yet