Professional Documents

Culture Documents

DC Manual Final

Uploaded by

srvsbondOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DC Manual Final

Uploaded by

srvsbondCopyright:

Available Formats

PCCOER, Ravet Department of E&TC

Experiment No. : 1

Experiment Name : Experimental Study of PCM and Companded PCM

Class & Batch : _________________________________________

Roll No : _________________________________________

Date of Performance : __________________________________________

Signature : __________________________________________

TE (E&TC) (SEMESTER I) 1 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 1

AIM: a) Experimental Study of Pulse Code Modulation & Demodulation

b) PCM Companding.

APPARATUS: PCM trainer kit, patch chords, CRO, CRO probes.

THEORY:

a) PCM Modulation & Demodulation:

By Nyquist theorem, if signal contains no frequency components for Fs >2fm, it is

completely described by instantaneous sample values uniformly spaced in time with period Ts. If a

signal has been sampled at the Nyquist rate or greater (Fs > 2fm) & the sample values are represented as

weighted impulses, the signal can be exactly reconstructed from its samples by an ideal LPF of

bandwidth B.W.

Pulse code Modulation is a digital transmission of samples of analog signal. In PCM

Generator we have sampler, Analog to digital converter & parallel to serial data converter & serial

transmission. In PCM Receiver there is serial reception of data, this serially received data is then

converted to parallel from & then fed to digital to analog converter. The output of DAC is fed to low

pass filter & we get transmitted analog signal. PCM performance as an analog communication system

depends primarily on the quantization noise introduced by ADC.

In our kit for PCM transmitter we have used ADC0809, Multiplexer IC74151, Latch

IC74373, Counter IC4040, IC7404, IC7432 & IC7408 for required Logic implementation.

The conversion time of ADC limits maximum sampling rate & therefore Bandwidth of

transmitter. All control signals are derived from basic clock. To derive control signals IC7408, 7432,

4017, are used. After analog to digital conversion signals fed to Multiplexer IC. Control for IC 74151 is

from IC4040. Every time IC4040 counter gives 8 combinations & transmits 8 bit data corresponding to

every sample.

In Receiver section we have used shift register IC 74198 in serial in & parallel out form.

For synchronization clock at Receiver must be same to clock at transmitter. After serial reception of data

TE (E&TC) (SEMESTER I) 2 Digital Communication

PCCOER, Ravet Department of E&TC

output of shift register is latched using 74373 & fed to DAC (R-2R Ladder). Output of DAC is fed to

filter.

To observe stable waveform on CRO the sampling frequency must be exactly integer

multiple of signal frequency. In our kit signal frequency is obtain by frequency divider & filter circuit.

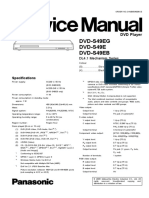

BLOCK DIAGRAM OF PULSE CODE MODULATION / DEMODULATION:

PCM MODULATOR:

PCM DEMODULATOR

TE (E&TC) (SEMESTER I) 3 Digital Communication

PCCOER, Ravet Department of E&TC

PROCEDURE:

Note: Pot provided at top left side corner is for varying dc bias at theI/p of A/D. We can measure DC

bias voltage at the test pt. 8 bit dip switch is provided for varying bit resolution of A/D. If Sw is ON

that means that bit is going to latch connected after A/D. If it is OFF it means gnd is connected to

respective pin of latch. If LSB bit is off (no. 1 of DIP switch) least count of A/D is now 38 mv instead of

19mv when all bits are connected.

1) Switch on Power on switch, red LED should glow.

2) Observe 1MHz clock O/p signal on panel.

3) Connect this 1MHz clock to ADC 0809 clock I/p.

4) Observe point A O/p from: 2 Network & connect it to point B i.e. I/p to 8 Network .

5) Observe O/p of both: 8 network & calculate their frequencies.

6) Connect O/p of 2nd: 8 network to start conversion I/p of ADC 0809 i.e. SC point on panel.

7) Observe SC point & EOC point on panel simultaneously on dual trace oscilloscope & find

out conversion period of A/D. Conversion period Time between falling edge of SC & rising

edge of EOC.

8) Observe EOC point & OE point i.e. O/p enable pin of 74373 latch simultaneously on dual

trace scope. Also observe RST point &Clk point of IC 4040 along with OE.

9) Observe PCM OUTPUT point & connect it to I/p to receiver. i e. serial I/p to shift register

74198.

10) Observe CLK of 74198 along with Clk of 4040 dual trace scope.

11) Observe LE i. e. latch enable pin of 74373 latches next to shift register, with CLK of 74198.

12) Now you can draw timing diagram of the system.

13) Ensure that all 8 bits are connected to latch i. e. that all DIP SWs are to on position.

14) Adjust biasing dc voltage to 2.5v with the pot.

15) By using pot provided above DAC adjust 2.5v at the O/p of DAC.

16) Now vary I/p biasing pot slightly & observe that accordingly DAC voltage varies linearly, on

CRO.

17) Now keep 3 LSB bits SWs to Off position & vary I/p biasing voltage, you will find DAC

voltage varies in steps.

18) By measuring I/p voltage & DAC voltage we can find out quantization noise.

TE (E&TC) (SEMESTER I) 4 Digital Communication

PCCOER, Ravet Department of E&TC

19) Now keep DC bias to 2.5v using nearby pot. & all DIP SWs to on position.

20) Two generators are provided on panel rightmost is fixed frequency Sine wave & the other is

variable frequency. (Sine, square & triangular wave generator) To vary its frequency pot is

provided on panel.

21) First Connect fixed frequency sine wave to I/p of ADC 0809.

22) Observe DAC O/p. Calculate its frequency & peak to peak amplitude. Observe this with I/p fixed

frequency sine wave.

23) Connect DAC O/p to I/p of filter & observe O/p of filter.

24) Repeat step 22-23 variable frequency sine, triangular & square wave a I/p to ADC.

25) First keep the frequency of sine wave minimum. Observe the DAC O/p along with I/p sine wave.

Now slowly increase the frequency of sine wave to verify Nyquist criteria and to observe

aliasing effect.

OBSERVATION TABLE:

Measurement of Quantization Error:

Sr. No. I/P O/P Quantization Error = O/P - I/P

TE (E&TC) (SEMESTER I) 5 Digital Communication

PCCOER, Ravet Department of E&TC

WAVEFORMS:

Draw the following waveforms:

1. I/p signal

2. Start of Conversion & End of Conversion

3. O/P enable & PCM

4. LE signal

5. DAC O/P signal

6. LPF o/p.

CONCLUSION:

TE (E&TC) (SEMESTER I) 6 Digital Communication

PCCOER, Ravet Department of E&TC

b) PCM Companding

AIM: To study PCM with Companding (A law and law).

APPARATUS: Experiment kit, DSO, DMM, Connecting Wires, Probes.

THEORY:

In linear PCM if Bit resolution is 8 Bit then there are 28 = 256 quantization Levels. Also if

signal amplitude it capable of swinging through all available quantization region without extending

beyond the outermost ranges. (e.g. if ADC 0809 is Used outermost range is OV & 5V & we can apply

maximum signal amplitude 5V p-p ). The O/p signal to quantization noise ratio is 6N dB. When N = 8

i. e. no of Bits. S/N ratio 48 dB.

If the signal is reduced in amplitude so that not all quantization ranges are used than S/Nq ratio

is also reduced. That means effective numbers of quantization levels are also reduced. To avoid this

problem a process called COMPANDING is used. COMPANDING means compressing of signal at

transmitter & expanding of a signal at receiver. To keep S/Nq ratio high we must use a signal which

swings through a range which is large in comparison with step size. This requirement is not satisfied

when the signal is small. Therefore signal is passed through a compressor. So that at the O/p of

compressor at low amplitude slope is large than at large amplitude. Due to this, a small amplitude

signal will range thro-ugh more quantization regions than would be the case in the absence of

compression. Compression produces signal distortion . To undo the distortion, at the receiver We pass

the recovered signal through an expander Network. An expander network has an I/p O/p

characteristic which is the inverse of the characteristic of the Compressor. The inverse distortion of

compressor & expander generate a final O/p signal without distortion.

A] Law Companding: In the U. S., Canada & Japan law is used.

y = + log ( 1 + IxI )

log (1 + )

= 255 = degree of compression & Range of allowable Voltage is V to +V. For our kit -V to + V = 5.

Therefore V = 2.5. For synthesis of law compander we have used log, Antilog, Adder , Subtractor

TE (E&TC) (SEMESTER I) 7 Digital Communication

PCCOER, Ravet Department of E&TC

Circuits using OPAMPs. Refer to block diagram for u law compander. Also Precision rectifier is used

to get absolute value.

OBSERVATION TABLE:

A) For law observations:

Sr. No. I/P of Compressor O/P of Compressor Sr. No. I/P of expander O/P of Expander

B] A law compander: Rest of the world uses A law Companding.

y =+ A [x] For IxI < 1/A

1+ log A

& y= + 1+log a[x] For 1/A < IxI < 1

1 + log A

To observe A & law curve directly on CRO, connect sine wave & companded O/P either of A law

or law to two channels of CRO & press XY mode switch you will observe curve on screen related

TE (E&TC) (SEMESTER I) 8 Digital Communication

PCCOER, Ravet Department of E&TC

to that law. You will observe that near zero, slope of curve is very sharp than higher values which is

desired. Also for A law we can observe break point near zero value due to two equations.

At PCM receiver DAC gain control pot has to be perfectly adjusted to get proper wave shape after

expander block.

b) For A Law Observations:

Sr. No. I/P of Compressor O/P of Compressor Sr. No. I/P of expander O/P of Expander

TE (E&TC) (SEMESTER I) 9 Digital Communication

PCCOER, Ravet Department of E&TC

PROCEDURE:

1) Switch on the power supply.

2) Connect O/p of Function Generator to I/p of COM Block. Keep Frequency of Function

generator minimum.

3) Vary I/p of COM Block from 0 to 1 Vpeak linearly & take Reading of O/p of COM Block.

Plot the graph of I/p Vs O/p & verify the u law.

4) Observe that sine wave is companded at the O/p of u COM Block.

5) Connect O/p of u COM Block to I/p of u Exp. Block & observe that Companding undo at the

O/p of u Exp. Block.

6) Repeat step to (2) to (5) for A COM & A Exp Block.

7) Now to study advantage of companding for small signals follow the following procedure.

A. Connect PCM O/p to I/p of 74198.

B. Adjust DAC O/p to exactly 0 Volts.

C. Connect Sine wave (100 mVp-p) as I/p to ADC 0809 & keep Frequency of function generator to

minimum position.

D. Observe DAC O/p

E. Now connect Sine wave (100 mVp-p) to I/p of u COM. Block Connect its O/p to I/p of

ADC0809. & observe DAC O/P. Observe there are more no of Quantization Levels for small

signal.

8) Repeat Step (7) for A COM & A Exp Block.

WAVEFORMS:

Waveforms to be observed-

1. I/P signal of the compressor

2. O/P signal of the compressor

3. PCM O/P

4. Reconstructed signal at the DAC o/p.

5. O/p signal of the Expander.

6. O/p of LPF.

7. I/O Vs O/P graph for compressor.

TE (E&TC) (SEMESTER I) 10 Digital Communication

PCCOER, Ravet Department of E&TC

CONCLUSION:

STUDY QUESTIONS:

1) Calculate sampling frequency of system.

2) What is the bit rate of system?

3) What is the bit resolution of the system?

4) What is quantization noise? Try to find out some practical procedure to find out quantization

noise.

5) When fixed frequency sine wave is connected I/p DAC O/p wave form is stable one & you can

observe it on CRO, but when variable frequency sine wave is connected DAC O/p is not stable,

why?

REFERENCES:

TE (E&TC) (SEMESTER I) 11 Digital Communication

PCCOER, Ravet Department of E&TC

Experiment No. : 2

Experiment Name : Experimental Study of DM and ADM.

Class & Batch : _________________________________________

Roll No : _________________________________________

Date of Performance : __________________________________________

Signature : __________________________________________

TE (E&TC) (SEMESTER I) 12 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 2

AIM: Experimental Study of delta modulation & adaptive delta modulation

APPARATUS: DM & ADM trainer kit, patch chords, CRO, CRO probes.

a) Delta Modulation and Demodulation:

THEORY:

Sample values of analog waveform derived from physical Process often exhibit predictability in

the sense that the average change from Sample to sample is small. Hence you can make a reasonable

guess of the next sample value based on previous values. The predicted values has some error off

course, but the range of the error should be much, less than the Peak - to peak signal Range Predictive

coded modulation scheme exploit this property by transmitting just the prediction errors. An identical

prediction circuit at the destination combines the incoming errors with its own predicted values to

reconstruct the waveform. Delta modulation employees prediction to simplify hardware in exchange

for increased signaling rate compared to Pulse code modulation.

At DM transmitter, every sample of message waveform is compared with previous sample. To

have previous sample available, dummy receiver is required at transmitter. If sample at any instant is

larger in magnitude than previous one, then one is transmitted. If sample at any instant is smaller than

previous value O is transmitted. Thus DM one bit per sample is transmitted.

In our kit we have provided IC8038 based function generator Sine triangular & Square wave is

provided. A fixed sampling (8 KHz) frequency is provided. By varying I/p signal frequency different

sampling rates & its effect on reconstructed message signal can be observed. Also variable step-size is

provided. For square wave slope-overload prominently occurs, it can reduce by increasing step-size or

increasing sampling rate.

At DM Receiver our aim is to reconstruct transmitted message signal from train of 1 & 0. In

our kit Receiver is built with complete hardware flip-flops ( IC4013 ), Decade counter ( IC4017),

Binary Adders ( IC 7483 ), Latches ( 74373 ), OR Gate ( IC7432 ), Not Gate ( IC7404), Digital to

analog converter (OP-AMP based R-2R Ladder) are used for this purpose. At receiver timing is very

critical. We have to perform different operation such as addition, subtraction, latching. Therefore

different control signals for sequential operation are derived by dividing Basic Clock using (IC4017).

TE (E&TC) (SEMESTER I) 13 Digital Communication

PCCOER, Ravet Department of E&TC

Before taking new I/p pulse, previous sample value is latched using (IC74373) & transfer to binary

adder & subtractor. Subtraction is carried out using binary adder (IC7483) using 2s complement

method. If received signal is One then 1 is added to previous value, else it is subtracted from

previous value. The result of addition/ subtraction is again latched & transfer to adder/ subtractor. So it

can used as previous sample for next sample. Result is fed to DAC. O/p of DAC is reconstructed

message signal.

BLOCK DIAGRAM:

Delta Modulation:

Demodulation:

TE (E&TC) (SEMESTER I) 14 Digital Communication

PCCOER, Ravet Department of E&TC

PROCEDURE:

1) Switch on Power on switch. Red led should glow.

2) Two signal generators are provided on panel. One is fixed frequency sine wave & the other is

variable frequency square, sine, triangular wave generator. First Connect O/p of fixed frequency

generator to non-inverting terminal of comparator.

3) O/p of 4013 i.e. point A on panel should be connected to point B on panel.

4) DAC O/p should be connected to inverting terminal of comparator & to input of LPF.

5) Observe O/p of CLOCK Measure its frequency.

6) Observe clock O/p terminal connected to 4013 IC. It is nothing but the sampling frequency.

Measure it.

7) Observe DM O/p for given fixed frequency sine wave. Measure frequency of this sine wave.

8) Observe fixed frequency sine wave & DAC O/p i. e. reconstructed signal simultaneously on

CRO & find out DM algorithm.

9) Observe point A of 4013 & DAC O/p simultaneously on dual trace CRO.

10) Observe OEs of 74373s in subtractor branch i. e. in which 7404 is connected & adder

branch simultaneously on dual trace CRO. They are complement to each other.

11) Observe effect of pot on step size. This pot is situated on top of DAC.

12) To find out bit resolution in DM algorithm procedure is as follows

a. Keep non-inverting terminal of comparator open.

b. Connect inverting terminal of comparator to ground other & Connections as it is.

c. Observe DAC O/p. stair case waveform is seen on CRO. Measure no. of step in that

waveform from this now calculate Bit resolution.

d. For this configuration rising stair case waveform is observed Reason for this is that non-

inverting terminal is internally dc biased for 2.5V, & we kept inverting terminal grounded.

So comparator O/p is permanently high, so increment command to DM receiver, so it goes

on Incrementing & due to overflow again starts from zero level.

e. If inverting terminal is connected to VCC i. e. 5V, falling stair-case waveform is observed.

13) To draw timing diagram of system, make connection as said earlier & instead of connecting

any signal to non-inverting terminal keep it open, internally 2.5V biasing is given. For this

DAC O/p wave form is sq. wave. For each sample either increment or decrement by one step

TE (E&TC) (SEMESTER I) 15 Digital Communication

PCCOER, Ravet Department of E&TC

size. Now observe sampling clock of IC 4013 with LE signal of previous data latch 74373

simultaneously on dual trace. Then observe any OE signal with LE signal,

simultaneously. Now draw timing diagram.

14) Now by connecting variable frequency sine wave & sq. wave to non-inverting terminal

observe DAC O/p. also see the effect of step size & sampling frequency when frequency is

varied.

15) Low pass filter is provided on panel. By giving variable sine wave to its I/p observe its O/p &

from that find out its cut off frequency. Also for fixed frequency sine wave connect DAC O/p

to I/p of LPF & observe its O/p.

WAVEFORMS:

Draw following waveforms:

1. Input signal

2. DAC output

3. DM output

4. OE of both the adder and subtractor block.

5. LPF output.

6. Output of DAC for triangular and square inputs for frequency of 1KHz.

CONCLUSION:

REFERENCES:

TE (E&TC) (SEMESTER I) 16 Digital Communication

PCCOER, Ravet Department of E&TC

b) ADAPTIVE DELTA MODULATION & DEMODULATION (ADM)

AIM: To study adaptive delta modulation & demodulation

APPARATUS: Experiment kit, DSO, Connecting Wires, Probes.

THEORY:

In case of Delta modulation we transmit 1 when instantaneous value of message waveform is

larger than previous sample & 0 when it is smaller than previous sample. But the step size is fixed. If

I/p (i. e. message waveform) is changing rapidly, it is not possible for DM to track the message

waveform. For example for square wave I/p, O/p of DM receiver is not square wave. This is called as

slope overload. To avoid this problem adaptive delta modulation technique is used. Adaptive delta

modulation (ADM) involves additional hardware designed to provide variable step size, thereby

reducing slope-overload effects without increasing the granular noise. In DM we observe that slope-

overload appears as a sequence of pulses having the same polarity. This sequence information can be

utilized to adopt the step size in accordance with the signals characteristics.

If instantaneous value of message waveform is larger than previous sampled then 1 is

transmitted and if smaller then 0 is transmitted. But the difference is that if 1 is transmitted two or

more times successively then step size is not same. If for first 1 it is 1D for second 1 it 2D, for 3 rd

3D and so on. Similarly if 0 is transmitted two or more times then step size is D for 1st 0, -2D for

second zero and so on.

In our ADM kit we have provided sine & square wave as a message waveform. The logic which

explained earlier is build using complete hardware. Up-Down counters, Latches, Binary adders,

Digital to analog converters, Comparators are used. Complete circuit diagram is as shown in figure.

Timing sequence is similar to that of DM kit. Only difference is that one CLK is fed during each

sampling to UP or DOWN counter depending on whether 1 is transmitted or 0 is transmitted.

Also up counter is reset if 0 is transmit & down counter is reset if 1 is transmit.

TE (E&TC) (SEMESTER I) 17 Digital Communication

PCCOER, Ravet Department of E&TC

BLOCK DIAGRAM:

Adaptive Delta Modulation:

Demodulation:

TE (E&TC) (SEMESTER I) 18 Digital Communication

PCCOER, Ravet Department of E&TC

PROCEDURE:

1. Switch on Power on switch. Red LED should glow.

2. Observe O/p from clock & measure its frequency.

3. Two signal generators are provided on panel. One is fixed frequency sine wave generator.

Observe its O/p on CRO. Measure its frequency & peak to peak amplitude. The other is

variable frequency sine & square wave generator. Pot is given to very its frequency. measure

i6ts frequency span.

4. Connect non inverting terminal of comparator to fixed sine wave.

5. Connect inverting terminal of comparator to DAC O/p.

6. O/ps from 4013 IC are shown as point A & C on panel. They are used for further control.

Connect point A to point B & connect point C to point D on panel.

7. Now observe DAC O/p along with I/p sine wave & by nearing hearby pot see variable step

size. Also observe that slope overload is less in ADM.

8. Observe ADM O/p with sine wave & then with digitally reconstructed DAC O/p. what is

your conclusion?

9. Also for particular step size if we observe ADM O/p & DAC O/p simultaneously on dual

trace CRO then we find 1 sample delay in decision making but if point A & DAC O/p is

observed simultaneously, no such delay is observed why ?

10. Observe sampling clock of IC 4013. Measure its frequency..

11. Connect DAC O/p to I/p of low pass filter & observe its O/p & measure its frequency

observe effects of step size variation on the filter O/p.

12. Observe point A & one by one, two RST pins of 74193 on dual trace. What is your

observation.?

TE (E&TC) (SEMESTER I) 19 Digital Communication

PCCOER, Ravet Department of E&TC

13. Measure Clock frequency given to both 74193 ICs.

14. Observe point A & two OEs on dual trace scope one by one. What is your conclusion ?

15. Observe LE point of previous latch 74373 situated at the bottom. Measure its frequency.

16. To draw timing diagram, keep non inverting terminal of comparator open, then in this case

DC is given due to internal DC biasing. Observe DAC O/p. adjust pot so that only one step

hunting is observed. Also see that here if step size is varied hunting is more than in DM. Now

when only one step size hunting is there, for every sample we get increment or decrement.

Then observe sampling clock & LE of latch simultaneously. Then observe RST &

sampling clock. Observe Clk to 74193 & LE of previous latch. Observe Clk to 74193 &

OEs of two latches i. e. 74373. From these observations draw timing diagram.

17. Now connect non inverting terminal of comparator to variable frequency sine wave & sq.

wave. Observe slope overload effect. For low frequency observe hunting.

18. Low pass filter is provided on panel. We have variable frequency signal generator. Measure

LPFs cut-off frequency.

WAVEFORMS:

Draw following waveforms:

1. Input Signal

2. DAC output

3. ADM o/p

4. OE of adder or subtractor section.

5. LE of main latch 74373 along with OE of adder or subtractor.

6. O/P of LPF with respect to input.

7. Observe the effect of variable step size on slope overload error

CONCLUSION:

TE (E&TC) (SEMESTER I) 20 Digital Communication

PCCOER, Ravet Department of E&TC

Experiment No. : 3

Experiment Name : Experimental Study of line codes (NRZ, RZ, POLAR RZ,

BIPOLAR (AMI), MANCHESTER) & their spectral analysis.

Class & Batch : _________________________________________

Roll No : _________________________________________

Date of Performance : __________________________________________

Signature : __________________________________________

TE (E&TC) (SEMESTER I) 21 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 3

AIM: Experimental Study of line codes (NRZ, RZ, POLAR RZ, BIPOLAR (AMI),

MANCHESTER) & their spectral analysis.

APPRATUS: Data formats trainer kit, patch chords, CRO, CRO probes.

THEORY:

The symbols `0 and `1 in digital system can be represented in various

formats with different levels and waveforms. The selection of particular format for

communication depends on the system bandwidth, systems ability to pass DC level

information, error checking facility, ease of clock regeneration & S ynchronization at

receiver, system complexity and cost etc.

In this kit we have provided two different bit patterns to study different data formats. [RZ,

NRZ, Bipolar RZ, Bipolar NRZ & Bi-phase or split phase]

1. RZ: In case of RZ i. e. return to zero formats, if bit is 1 then logic high level is transmitted

for first half bit period & then logic low level is transmitted.

2. NRZ: In case of NRZ i. e. not return to zero, if bit is 1 then logic high level is transmitted

for full bit period & if bit is 0 then logic low level is transmitted.

3. BIPOLAR RZ: If bit is 1 then high level is transmitted for first high bit period & then low

level for remaining half bit period. If bit is 0 then negative high level is transmitted for first

half bit period & then low level for remaining half bit period.

4. BIPOLAR NRZ: If bit is 1 then high level is transmitted for full bit period. If next bit (Not

necessary consecutive) is also 1 then negative high level is transmitted i. e. for every 1

sign of high level is altered. If bit is zero then logic low level is transmitted.

5. SPLIT PHASE (MANCHESTER): If bit is 1 , then logic high level is transmitted for first

half bit period followed by logic low level for next half bit period. If bit is 0 then logic low

level is transmitted for first half bit period followed by logic high level for next half bit

period.

TE (E&TC) (SEMESTER I) 22 Digital Communication

PCCOER, Ravet Department of E&TC

Line Coding Waveforms:

PSD of Line Codes:

TE (E&TC) (SEMESTER I) 23 Digital Communication

PCCOER, Ravet Department of E&TC

PROCEDURE:

1. Switch on the power supply.

2. Connect one of the bit patterns as I/p to data format section.

3. Observe bit pattern together with different data formats on dual scope CRO.

4. Repeat the procedure for other bit patterns.

CONCLUSION:

TE (E&TC) (SEMESTER I) 24 Digital Communication

PCCOER, Ravet Department of E&TC

STUDY QUESTIONS:

1) What is line coding?

2) Draw the various data formats for bit pattern i) 1010010100 ii) 1000010000

REFERENCES:

TE (E&TC) (SEMESTER I) 25 Digital Communication

PCCOER, Ravet Department of E&TC

Experiment No. : 4

Experiment Name : Experimental Study of Generation of PN Sequence and its

spectrum.

Class & Batch : _________________________________________

Roll No : _________________________________________

Date of Performance : __________________________________________

Signature : __________________________________________

TE (E&TC) (SEMESTER I) 26 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 4

AIM: Experimental Study of Generation of PN Sequence and its spectrum.

APPRATUS: PN Sequence trainer kit, patch chords, CRO, CRO probes.

THEORY:

PN sequence means Pseudo Random sequence. It is not exactly random but repeats after 2

n

1 clock cycles. So called as pseudo random. They may connect to D/A converters to produce

random noise used to test audio system. To generate PN sequence a clock generator, D flip/flops, ex-

or & not gates are used. In our kit we have given 4 bit, 8 bit, 12 bit PN sequence generator. Clock

generator is designed using IC555. For D flip/flop IC 74175 (4 D flip/flops) ,ex-or7486, Not 7404 are

used. For 4 bit, sequence repeats after 15 clock cycles. For 8 bit sequence repeats after 255 clock

cycles & for 12 bit sequence repeats after 4095 clock cycles.

CIRCUIT DIAGRAM:

i.e. Q0 & Q3 are Ex-ORed & given to I/P after inverting. Inverter is because after resetting all

O/Ps are zero & to start PN sequence I/P should be one. For 12 bit Q0 & Q11 are Ex-ORed.

For 4 Bit

Q0 To I/p

Q3 for max. Length

TE (E&TC) (SEMESTER I) 27 Digital Communication

PCCOER, Ravet Department of E&TC

Clock Q3 Q2 Q1 Q0 Feedback PN Sequence

0 0 0 0 0 1 0

1 0 0 0 1 0 1

2 0 0 1 0 1 0

3 0 1 0 1 0 1

4 1 0 1 0 0 1

5 0 1 0 0 1 0

6 1 0 0 1 1 0

7 0 0 1 1 0 1

8 0 1 1 0 1 0

9 1 1 0 1 1 0

10 1 0 1 1 1 0

11 0 1 1 1 0 1

12 1 1 1 0 0 1

13 1 1 0 0 0 1

14 1 0 0 0 0 1

15 0 0 0 0 1 0

16 0 0 0 1 0 1

TE (E&TC) (SEMESTER I) 28 Digital Communication

PCCOER, Ravet Department of E&TC

PROCEDURE:

For 4 & 8 bit PN sequence Gen. keep toggle S/w in right upper corner to 4-8 Bit position & for

12 bit PN sequence Gen. S/w to 12 Bit position.

1. Switch on the Power Supply.

2. Connect CLK O/p of CLK Generator to CLK I/p of F/F.

3. Now to study 4 bit PN sequence generator connect pt. F to pt E.

4. Press reset S/w on panel.

5. Observe PN sequence O/p on C. R. O. together with clock. It repeats after 15 clock

cycles.

6. Now to study 8 Bit PN sequence generator.

i) Disconnect pt F from pt E

ii) Connect pt F to pt C

iii) Connect pt D to pt E

iv) Press reset Switch

v) Observe O/p of PN sequence generator.

7. Now to study 12 Bit PN sequence generator.

i) Disconnect pt F from pt C

ii) Connect pt F to pt A

iii) Connect pt B to pt C

iv) Connect pt D to pt E

v) Press reset Switch & Observe O/p of PN sequence generator.

CONCLUSION:

REFERENCES:

TE (E&TC) (SEMESTER I) 29 Digital Communication

PCCOER, Ravet Department of E&TC

Experiment No. : 5

Experiment Name : Experimental Study of Pulse shaping, ISI and eye diagram.

Class & Batch : _________________________________________

Roll No : _________________________________________

Date of Performance : __________________________________________

Signature : __________________________________________

TE (E&TC) (SEMESTER I) 30 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 7

TITLE: Write a simulation program to implement PCM system.

AIM: To write a MATLAB program to implement Pulse code Modulation.

APPARATUS REQUIRED:

Sr.No. COMPONENTS SPECIFICATION QTY.

1. COMPUTER - 1

2. MATLAB R2010a - 1

ALGORITHM:

1. Generate a signal 8*sin(x) and plot it.

2. Sample that signal and plot sampled waveform.

3. Quantize the sampled signal and plot it.

4. Encode the quantized signal and display that encoded sequence.

5. Get back the index in decimal form.

6. Get back the quantized levels.

7. Plot demodulated signal.

MATLAB COMMANDS USED:

input( ), subplot( ), quantiz( ), length( ), de2bi( ), stairs( ), reshape( ).

CONCLUSION:

TE (E&TC) (SEMESTER I) 31 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 8

TITLE: Write a simulation program implementation of any digital communication system.

AIM: Write a MATLAB code for BPSK generation and detection.

APPARATUS REQUIRED:

Sr.No. COMPONENTS SPECIFICATION QTY.

1. COMPUTER - 1

2. MATLAB R2010a - 1

ALGORITHM:

1. Get the frequency of carrier sine wave from user.

2. Get the frequency of message signal from user.

3. Get the amplitude of carrier and message signal from user.

4. Generate message and carrier signal.

5. Modulate carrier using message signal and plot it.

6. Demodulate modulated signal to recover the message.

MATLAB Commands used:

square ( ), input( ), subplot( ), figure( ), title( ), xlabel( ), ylabel( ),

CONCLUSION:

TE (E&TC) (SEMESTER I) 32 Digital Communication

PCCOER, Ravet Department of E&TC

EXPERIMENT NO. 9

TITLE: Write a simulation program for Constellation diagram of any pass band modulation

technique (QPSK).

AIM: Write a MATLAB code for Constellation diagram of any pass band modulation technique

(QPSK).

APPARATUS REQUIRED:

Sr.No. COMPONENTS SPECIFICATION QTY.

1. COMPUTER - 1

2. MATLAB R2010a - 1

ALGORITHM:

1 Create random digital message.

2 Modulate it using QPSK technique.

3 Create a scatter plot and show constellation.

4 Transmit signal through an AWGN channel.

5 Create scatter plot from noisy data.

6 Compare these two plots.

MATLAB COMMANDS USED:

randi( ), modem.pskmod(M), commscope.ScatterPlot( ), modulate( ), awgn( ), update( ),

demodulate( ).

CONCLUSION:

TE (E&TC) (SEMESTER I) 33 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 34 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 35 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 36 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 37 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 38 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 39 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 40 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 41 Digital Communication

PCCOER, Ravet Department of E&TC

TE (E&TC) (SEMESTER I) 42 Digital Communication

You might also like

- DSP Programs Using Scilab PDFDocument205 pagesDSP Programs Using Scilab PDFsrvsbondNo ratings yet

- PCM Sampling and Demodulation Waveform AnalysisDocument37 pagesPCM Sampling and Demodulation Waveform Analysissouled oneNo ratings yet

- DCLabDocument31 pagesDCLabani rohiraNo ratings yet

- DC LAB MANUAL FinalDocument39 pagesDC LAB MANUAL FinalTushar MaruNo ratings yet

- Digital Communications Lab: List of ExperimentsDocument50 pagesDigital Communications Lab: List of ExperimentsNeel SarkarNo ratings yet

- A/D and D/A Converter FundamentalsDocument18 pagesA/D and D/A Converter FundamentalskarkeraNo ratings yet

- DPSK Modulation ExperimentDocument49 pagesDPSK Modulation ExperimentSnigdha SidduNo ratings yet

- New DC Lab ManualDocument53 pagesNew DC Lab Manualsriram128No ratings yet

- Communication Systems Lab Manual ExperimentsDocument37 pagesCommunication Systems Lab Manual Experimentsnidheeshlal10No ratings yet

- Digital StethoscopeDocument4 pagesDigital StethoscopeDhaval ShahNo ratings yet

- Experiment No. 6: Objective: ApparatusDocument4 pagesExperiment No. 6: Objective: ApparatusNioNo ratings yet

- EXP 9 - Pulse Code Modulation & DemodulationDocument5 pagesEXP 9 - Pulse Code Modulation & DemodulationsasankflyNo ratings yet

- MANUAL COMMUNICATION LAB-II, KEC-651,2020-21, Even SemDocument18 pagesMANUAL COMMUNICATION LAB-II, KEC-651,2020-21, Even SemPiyushNo ratings yet

- Digital Communications: Lab Manual (Student Copy)Document78 pagesDigital Communications: Lab Manual (Student Copy)dhileepan DilipNo ratings yet

- Data Conversion CCTSDocument5 pagesData Conversion CCTSDavis AllanNo ratings yet

- Comm 2Document53 pagesComm 2John Adam Cayanan DesuasidoNo ratings yet

- DC Lab ManualDocument24 pagesDC Lab Manualvidyae100% (2)

- Using A BJT As A Switch: An Example: BelowDocument10 pagesUsing A BJT As A Switch: An Example: BelowPrakhar BhatnagarNo ratings yet

- A/D and D/A Conversion Testing: V G 2 V VDocument7 pagesA/D and D/A Conversion Testing: V G 2 V VRichard NewbyNo ratings yet

- ECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S ObservationDocument12 pagesECE/EEE F311 Communication Systems - Laboratory. Lab Report: Steps Observation: Step S ObservationMohit DhayalNo ratings yet

- FM DemodulationDocument4 pagesFM DemodulationRudra Pratap SinghNo ratings yet

- Analog-To-Digital Conversion Btech IIIDocument50 pagesAnalog-To-Digital Conversion Btech IIILisa BhagatNo ratings yet

- Digital Coding of Signals: ClippingDocument15 pagesDigital Coding of Signals: ClippingGurkaranjot SinghNo ratings yet

- Lab 7Document5 pagesLab 7MELINDA BR GINTINGNo ratings yet

- Es1107 Assignment-01Document6 pagesEs1107 Assignment-01K. BHANU PRAKASH REDDYNo ratings yet

- Electronics & Communication EngineeringDocument41 pagesElectronics & Communication EngineeringKrishna Chaitanya TNo ratings yet

- berkes_interfacing exp arrangementDocument20 pagesberkes_interfacing exp arrangementAditya K NNo ratings yet

- Measuring Total Power of AM TransmitterDocument44 pagesMeasuring Total Power of AM TransmitterNikhil KolheNo ratings yet

- Measuring Distance Using Infrared SensorsDocument5 pagesMeasuring Distance Using Infrared SensorsRajkeen ChamanshaikhNo ratings yet

- ManualDocument61 pagesManualprembalanNo ratings yet

- DPCM and Delta ModulationDocument12 pagesDPCM and Delta ModulationHarikrishnan Manakara RadhakrishnanNo ratings yet

- Adc Lab Manual PDFDocument74 pagesAdc Lab Manual PDFJega Deesan75% (4)

- Model-Dpcm100: Differential Pulse Code Modulation/Demodulation TrainerDocument15 pagesModel-Dpcm100: Differential Pulse Code Modulation/Demodulation TrainerVăn Tấn ĐìnhNo ratings yet

- Mixed Signal Lecture Series - DSP-Based Testing Fundamentals 01Document8 pagesMixed Signal Lecture Series - DSP-Based Testing Fundamentals 01Tina HuangNo ratings yet

- Nnew - DC Lab ManualDocument106 pagesNnew - DC Lab ManualKalidindi TejasreeNo ratings yet

- Communication II Lab (EELE 4170)Document6 pagesCommunication II Lab (EELE 4170)Fahim MunawarNo ratings yet

- Tc320 Lab Manual - 2013Document68 pagesTc320 Lab Manual - 2013Guillermo Castillo MarmolNo ratings yet

- BC Lab Cycle Iii ExperimentsDocument15 pagesBC Lab Cycle Iii ExperimentsYaniNo ratings yet

- Bapatla Engineering College Digital Communications Lab EC-451Document30 pagesBapatla Engineering College Digital Communications Lab EC-451nithyamnvNo ratings yet

- Inverters SpecsDocument11 pagesInverters SpecsbhuwaneshtakNo ratings yet

- C. Instrumentation For Electrical Bioimpedance MeasurementsDocument32 pagesC. Instrumentation For Electrical Bioimpedance MeasurementsDmitriyNo ratings yet

- Elec4505 Exp0Document7 pagesElec4505 Exp0muafhanNo ratings yet

- Electronic Measurement & Instrumentation Lab Lab Manual: Vi SemesterDocument41 pagesElectronic Measurement & Instrumentation Lab Lab Manual: Vi SemesterMy JaanNo ratings yet

- Generation and Detection of DPSKDocument3 pagesGeneration and Detection of DPSKAmy OliverNo ratings yet

- Lab Design and Analysis of Active CS and Cascode AmplifierDocument3 pagesLab Design and Analysis of Active CS and Cascode AmplifierAzure HereNo ratings yet

- Plugin-LDICA LAB ManualDocument83 pagesPlugin-LDICA LAB Manualnainesh goteNo ratings yet

- Analog-To-digital Converter - Wikipedia, The Free EncyclopediaDocument6 pagesAnalog-To-digital Converter - Wikipedia, The Free EncyclopediaAziz SahatNo ratings yet

- Generation and Detection of DPSKDocument3 pagesGeneration and Detection of DPSKAmy OliverNo ratings yet

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDocument5 pagesLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Me 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesDocument13 pagesMe 365 Experiment 2 Introduction To Digital Data Acquisition ObjectivesSenthil KumarNo ratings yet

- EE LAB MANUAL EXPERIMENTS GUIDEDocument39 pagesEE LAB MANUAL EXPERIMENTS GUIDEMadhusudhanan RamaiahNo ratings yet

- An 477Document28 pagesAn 477radaresNo ratings yet

- Nama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCDocument4 pagesNama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCRifky Yoga PratamaNo ratings yet

- MTech (DCN) DEC-I ManualDocument34 pagesMTech (DCN) DEC-I ManualMallikarjun DeshmukhNo ratings yet

- Lab ManualDocument56 pagesLab ManualNarendra ReddyNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Digital Signal Processing: Instant AccessFrom EverandDigital Signal Processing: Instant AccessRating: 3.5 out of 5 stars3.5/5 (2)

- To Network LayerDocument130 pagesTo Network Layersrvsbond100% (1)

- Projectile Paper3 30Q 20 08 2018Document5 pagesProjectile Paper3 30Q 20 08 2018srvsbondNo ratings yet

- Solutions To Concepts: Chapter - 8Document16 pagesSolutions To Concepts: Chapter - 8rajpersonalNo ratings yet

- Oral Questions For DSPDocument38 pagesOral Questions For DSPsrvsbondNo ratings yet

- Maharashtra - Customer List For PCB LabsDocument3 pagesMaharashtra - Customer List For PCB LabssrvsbondNo ratings yet

- Scilab BeginnersDocument33 pagesScilab BeginnersCarlos Soza RossNo ratings yet

- GIS FUSE GTPDocument4 pagesGIS FUSE GTPAnand ShekharNo ratings yet

- ECA - II Lab 03, FA20-BEE-3C-146Document14 pagesECA - II Lab 03, FA20-BEE-3C-146Souban JavedNo ratings yet

- Panasonic dvd-s49 EgDocument65 pagesPanasonic dvd-s49 EgRobert PudziNo ratings yet

- Tibbo2 Tps Catalogue EngDocument4 pagesTibbo2 Tps Catalogue EngseacerNo ratings yet

- ELSAP01DDocument1 pageELSAP01DJhonny RinconesNo ratings yet

- M-Series: Contractor GuideDocument44 pagesM-Series: Contractor GuideStefy CarrascoNo ratings yet

- Commands of PDDocument18 pagesCommands of PDRA NDYNo ratings yet

- 600 W Tvs in SMB: FeaturesDocument13 pages600 W Tvs in SMB: Featuresعلي باعقيلNo ratings yet

- Brochure Solar Module - Suntech - EN - Ultra - S - STP455S - B72 - VNH (MC4 - 455 - 435) - 4G - S3Document2 pagesBrochure Solar Module - Suntech - EN - Ultra - S - STP455S - B72 - VNH (MC4 - 455 - 435) - 4G - S3Yudha Trias RusmanaNo ratings yet

- 4.1.2hoja de Datos Baterias SAFTDocument16 pages4.1.2hoja de Datos Baterias SAFTBSMD2309No ratings yet

- ESVB100: Operating ManualDocument18 pagesESVB100: Operating ManualMiloradNo ratings yet

- Controlled Rectifiers: DR Keshav PatidarDocument38 pagesControlled Rectifiers: DR Keshav PatidarManav JainNo ratings yet

- Lab#6a MeggerDocument7 pagesLab#6a MeggerRehman ButtNo ratings yet

- Compal Electronics Schematics Document for GLONASS BoardDocument29 pagesCompal Electronics Schematics Document for GLONASS BoardbobbiNo ratings yet

- Infunsion Pump 707 V Service ManualDocument28 pagesInfunsion Pump 707 V Service ManualJulio RojasNo ratings yet

- List of PSU (Very Important)Document2 pagesList of PSU (Very Important)api-3824629No ratings yet

- Ics Level 3Document2 pagesIcs Level 3bantalem da100% (1)

- Lg-Pdp-Training Plasma TV AlapokDocument67 pagesLg-Pdp-Training Plasma TV AlapokHamedKoneNo ratings yet

- Jitter Testing On 1G Ethernet Using An Automated Compliance ApplicationDocument7 pagesJitter Testing On 1G Ethernet Using An Automated Compliance ApplicationdarNo ratings yet

- Microwave Filter Design Chp. 5: End-Coupled, Half-Wavelength Resonator FiltersDocument37 pagesMicrowave Filter Design Chp. 5: End-Coupled, Half-Wavelength Resonator FiltersyyryNo ratings yet

- Connect Medium-Voltage TransformersDocument20 pagesConnect Medium-Voltage TransformersShiaTVfanNo ratings yet

- Zener Diode, Photo Diode, LEDDocument31 pagesZener Diode, Photo Diode, LEDsujithNo ratings yet

- 10 Aaa21700qDocument24 pages10 Aaa21700qasdfNo ratings yet

- 4010 SFIO Programmed IC Installation InstructionsDocument4 pages4010 SFIO Programmed IC Installation InstructionsRobel MTNo ratings yet

- Standard Features: Model GB-YM20Document4 pagesStandard Features: Model GB-YM20مہرؤآنہ آبہرآهہيہمہNo ratings yet

- Direct Online StarterDocument17 pagesDirect Online Starterදුප්පත් කොල්ලාNo ratings yet

- NEOS Parameter and Fault Code Overview EN 2946185800Document13 pagesNEOS Parameter and Fault Code Overview EN 2946185800jaypc10No ratings yet

- DOCUMENTATION HANDBOOK FOR PHONTECH SR 8200 SOUND RECEPTION SYSTEMDocument20 pagesDOCUMENTATION HANDBOOK FOR PHONTECH SR 8200 SOUND RECEPTION SYSTEMDamian MajewskiNo ratings yet

- Lab Iv. Silicon Diode Characteristics: 1. ObjectiveDocument9 pagesLab Iv. Silicon Diode Characteristics: 1. ObjectiveRaja MariyappanNo ratings yet

- Asco 3000 Series Static & Moveable Load BanksDocument3 pagesAsco 3000 Series Static & Moveable Load Bankshakera7536No ratings yet