Professional Documents

Culture Documents

A Low Power Vernier Time-To-Digital PDF

Uploaded by

Laxmi KumreOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Low Power Vernier Time-To-Digital PDF

Uploaded by

Laxmi KumreCopyright:

Available Formats

2017 International Conference on Networks & Advances in Computational Technologies (NetACT) |20-22 July 2017| Trivandrum

A LOW POWER VERNIER TIME-TO-DIGITAL

CONVERTER USING ADIABATIC LOGIC

*R.Mahima, Mr.D.Muralidharan,

M.Tech VLSI Design, School of Computing School of Computing

SASTRA UNIVERSITY, SASTRA UNIVERSITY

Thanjavur, Tamil Nadu, India. Thanjavur, Tamil Nadu, India.

mahi.rmc7@gmail.com murali@sastra.edu

AbstractIn this paper, an adiabatic based vernier time- Digital approaches using delay line methods. It can

to-digital converter (VTDC) is proposed. Generally, static provide the merit of lower power and also concept is

based vernier TDC consumes more power due to two delay simple. Due to the intrinsic gate delay of delayed

chain and D-flipflop. To avoid this issue an adiabatic based element in DLL, resolution is low. The difference

vernier TDC is proposed. This proposed TDC is constructed

between delay of gate helps to accomplish sub gate

by using adiabatic inverter and D-flipflop but in classical

TDC architecture consists of static based inverter and D-

delay resolution. VTDC belongs to sub-gate delay

flipflop. A high resolution with low power is achieved in technique. Due to this, vernier TDC provides high

proposed TDC. Here, 2 stages, 3 stages, 4 stages traditional resolution [4]. For achieving low power vernier TDC

and proposed vernier TDC are implemented and also adiabatic logic is used in this paper.

discussed about power consumption comparison of 2 stages,

3 stages, 4 stages conventional and proposed vernier TDC at This paper is organized into seven sections.

different supply voltages. This vernier TDC is simulated in Section I presents the introduction about TDC. Section II

180nm CMOS technology. Its operating frequency is conferred the theory of delay line based TDC. The concept

1.5KHZ. of cascadable adiabatic logic and its circuit diagram is

presented in section III. A detailed analysis of conventional

Keywords Time-to-Digital Converter (TDC); Vernier delay line vernier TDC is presented in section IV. In section

Time-to-Digital Converter (VTDC); All-Digital Phase V, a novel adiabatic based vernier delay line TDC concepts

Locked Loop (ADPLL); Digital Phase Locked Loop and its block diagram is presented. Section VI presents the

(DPLL), Delay Locked Loop (DLL). experimental results of conventional and proposed vernier

TDC. Section VII concludes the paper.

I. INTRODUCTION

To design an all-digital phase locked loop, TDC is II. OPERATION OF DELAY LINE BASED TDC

a basic building block [1]. TDC is a replacement of phase

comparator in digital pll (DPLL). All the blocks in DPLL Figure 1 displays the basic configuration of

like phase comparator, analog based loop filter and charge delay line based TDC. It comprises of delayed

pump is replaced by TDC, digital control loop and digital

elements and flip-flops. Also, it consists of stop and

filter. After this replacement, digital PLL become all digital

PLL because all the components in this PLL is digital [2]. start signals. Here, start signal is delayed by either

TDC is utilized in equivalent-time sampling in oscilloscope, inverter or buffer element [4] [5]. Similarly stop

particle life time detection in physics, time-interval signal also delayed by delay element. At the rising

analyser, on-chip jitter measurement, laser range finder and edge of another input stop signal, sampling process

frequency counter applications [3]. Because of the fast takes place which means flip-flops provide the level

advancement in VLSI innovation, the vast majority of the of delay line. Finally output will be generated in the

TDCs are incorporated into the target systems in order to form of 0s and 1s. This delay line concept is simple

decrease the power and cost while accomplishing high to understand.

resolutions.

978-1-5090-6590-5/17/$31.00 2017 IEEE 90

2017 International Conference on Networks & Advances in Computational Technologies (NetACT) |20-22 July 2017| Trivandrum

IV. CONVENTIONAL DELAY LINE

VERNIER TDC (VTDC)

The basic configuration of vernier delay line is

shown in figure 3. Its main task is to quantize the time

interim between start and stop signals [11] [12]. Here,

start and stop are the two input signals. These input

signals travel through two delay chains. The delay

chain is made up of a series of buffers with different

delay. Delay1 is the delay of top chain and delay2 is the

delay of bottom chain. Delay of top chain is greater

than the bottom chain [13]. Sampling process is done

by D-flipflop. Sampling of input start signal takes place

when the rising edge of other input stop signal.

Fig.1. Principle of delay line based TDC

TLSB=Delay1-Delay2 (1)

III. CASCADABLE ADIABATIC LOGIC

Currently, there is developing hobby in TLSB is the time resolution of vernier TDC as shown in

adiabatic approach for designing circuits in low power (1). In this static CMOS based vernier TDC, the power

VLSI [6]. In digital circuits power dissipation is more. consumption and area is increased due to two delay

To avoid this adiabatic approach provides better chain and register.

solution without circuit complexity. The word

adiabatic means no exchange of heat with the

environment. Adiabatic circuits work on the principle

of adiabatic charging and discharging [7]. In

conventional CMOS circuits, the energy from the

output capacitance is discharging to the ground. In

adiabatic logic, recycle back to the power supply [8].

The amount of saving energy is more in adiabatic logic

rather than conventional one. Adiabatic technique is

also named as Energy Recovery logic [9] [10].

Figure 2 shows the circuit diagram of cascadable

adiabatic logic. This circuit consists of basic CMOS

logic along with two MOS diodes which is D1 and D2.

D1 is NMOS transistor and D2 is PMOS transistor. D1

is charging path and D2 is discharging path.

Fig.3. Traditional vernier delay line based TDC

V. PROPOSED VERNIER TDC

Generally, the traditional vernier TDC improves the

time resolution by utilizing two delay lines. Here, stop signal

is applied as clock signal to D-flipflop. At the rising edge of

stop signal, the current state of start input signal is sampled

by the D-flipflop. These chains are made up of delayed

element buffer with different delay. Difference between the

gate delays of two chains is nothing but the effective time

resolution of vernier TDC. This static CMOS based vernier

TDC consumes more power due to two delay chains and flip-

flops. The delay chain can be formed by using delayed

Fig.2. Circuit diagram of cascadable adiabatic logic

element buffer. To overcome this power consumption issue,

a cascadable adiabatic logic based vernier TDC is proposed

as displayed in fig4.

978-1-5090-6590-5/17/$31.00 2017 IEEE

91

2017 International Conference on Networks & Advances in Computational Technologies (NetACT) |20-22 July 2017| Trivandrum

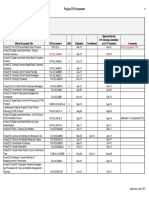

TABLE I. 2 STAGE CONVENTIONAL AND

PROPOSED VERNIER TDC SIMULATION

RESULTS AT 1.8V

Fig.4. Block diagram of proposed vernier TDC

Here, single time varying supply voltage is used instead of

constant supply voltage. Using this adiabatic technique, low

power can be achieved by the charge stored in load

capacitance is discharged to the power supply instead of

discharging the capacitor charge to ground [14]. It helps to

save some amount of power. The most attractive feature of

this cascadable adiabatic technique is that there is no need of

complementary inputs [15]. So, the cascadable adiabatic

logic circuit consumes less area. It helps to minimize power

consumption. This adiabatic logic has been implemented by

adding charging and discharging paths in the existing

standard CMOS logic, using diodes and capacitors. In this

proposed vernier TDC, high dynamic range is possible with

loop structure and also sub gate delay resolution is achieved. TABLE II. 3 STAGE CONVENTIONAL AND

PROPOSED VERNIER TDC SIMULATION

RESULTS AT 1.8V

VI. EXPERIMENTAL RESULTS

Here, both the classical and adiabatic based

vernier TDC circuits are analysed and simulated in

cadence 180nm technology. An adiabatic based

proposed vernier TDC consumes less power because

adiabatic logic uses time varying supply voltage but in

classical vernier TDC a constant supply voltage is used.

vpulse is used for time varying supply voltage. For

constant supply voltage vdc is used. Also in adiabatic

logic, the energy stored in load capacitance is recycle

back to power supply rather than discharging to

ground. Both the conventional and proposed vernier

TDC circuit is analyzed for different supply voltage.

Table I shows the simulation results for both 2 stage

conventional and proposed vernier TDC at 1.8V. Table

II shows the simulation results for both 3 stage

conventional and proposed vernier TDC at 1.8V.

Similarly, Table III shows the simulation results for

both 4 stage conventional and proposed vernier TDC at

1.8V. Table IV shows the power consumption

comparison of 2 stages, 3 stages, 4 stages conventional

and proposed vernier TDC with different supply

voltage.

978-1-5090-6590-5/17/$31.00 2017 IEEE 92

2017 International Conference on Networks & Advances in Computational Technologies (NetACT) |20-22 July 2017| Trivandrum

TABLE III. 4 STAGE CONVENTIONAL AND VII. CONCLUSION

PROPOSED VERNIER TDC SIMULATION

A novel design of adiabatic based vernier delay

RESULTS AT 1.8V

line TDC is presented. In this paper, a detailed analysis

of both conventional and adiabatic based vernier TDC

also takes place. This proposed vernier TDC consumes

less power compared with conventional TDC. Here,

both the TDCs are implemented in cadence 180nm

technology. The schematic diagram, output waveform

and its power consumption output of both TDCs for 2

stages, 3 stages, and 4 stages at 1.8V supply voltage is

shown here. Similarly, the power consumption

comparison of both conventional and proposed vernier

TDC for 2 stages, 3 stages, and 4 stages with different

supply voltage is presented. This power consumption

comparison of 2 stages, 3 stages, and 4 stages of both

conventional and proposed VTDC with different

supply voltage shows that if stages increases means

obviously the power consumption is increased as well

as high resolution can be achieved. Based on user

application need the number of stages can be fixed. If

resolution plays a major role means then the number of

stages should be increased and need to sacrifice power

which means power consumption should be high.

When compared with 2, 3, and 4 stages proposed

vernier TDC, 3 stages TDC consumes moderate power

and moderate resolution. Finally, this proposed vernier

TDC achieves sub gate delay resolution with low

TABLE IV. COMPARISON OF POWER

CONSUMPTION WITH DIFFERENT SUPPLY

power.

VOLTAGE

REFERENCES

[1] Effendrik, Popong, Time-to-Digital Converter

(TDC) for wimax ADPLL in State-of- The-Art 40-

nm CMOS Diss. Msc Thesis, Apr. 18, 2011.

[2] Yao, Chen. "Time to Digital Converter used in

ALL digital PLL", 2011.

[3] Naraghi, Shahrzad. "Time-based analog to digital

converters." PhD diss., The University of Michigan,

2009.

[4] R.Mahima, D.Muralidharan,A survey paper on

Time-to-Digital Converter (TDC) Research Journal

of Pharmaceutical, Biological and Chemical Sciences

(RJPBCS), Vol. 8 | Issue No.1 | Page No. 739- 746,

ISSN: 0975-8585, January February 2017.

[5] Li, Guansheng, et al. "Delay-line-based analog-to-

digital converters." IEEE Transactions on Circuits and

Systems II: Express Briefs 56.6 (2009): 464-468.

[6] Teichmann, Philip Adiabatic Logic, Future Trend

and System Level Perspective, Springer, - Springer

series in advanced microelectronics, XVII, 166p., 2012

978-1-5090-6590-5/17/$31.00 2017 IEEE 93

2017 International Conference on Networks & Advances in Computational Technologies (NetACT) |20-22 July 2017| Trivandrum

[7] Patel, Durgesh, S. R. P. Sinha, and Meenakshi

Shree. "Adiabatic Logic Circuits for Low Power VLSI

Applications.", Volume 5 Issue 4, April 2016.

[8] Himanshu Saxena, Akansha, Vikrant Chaudhary,

Low power adiabatic logic circuits analysis,

International Journal of Advance Research in Science

and Engineering IJARSE, Vol. No.2, Issue No.5, May,

2013.

[9] Sanadhya, Minakshi, and M. Vinoth Kumar.

"Recent Development in Efficient Adiabatic logic

Circuits and Power Analysis with CMOS Logic."

Procedia Computer Science 57, 2015:1299-1307.

[10] Nikunj R Patel, Sarman K Hadia, Adiabatic Logic

for Low Power Application Using Design 180nm

Technology, International Journal of Computer Trends

and Technology (IJCTT) - vol4, issue4 april 2013.

[11] S. Henzler, Time-to-Digital Converters, Series:

Springer Series in Advanced Microelectronics, Vol. 29,

124 p, 2010.

[12] Jianjun Yu, Fa Foster Dai, Richard C. Jaeger, A

12-Bit Vernier Ring Time-to-Digital Converter in 0.13

um CMOS Technology, IEEE journal of solid-state

circuits, vol. 45, no. 4, april 2010.

[13] Niklas Andersson and Mark Vesterbacka, A

Vernier Time-to-Digital Converter With delay Latch

Chain Architecture, 2014, IEEE Transactions on

Circuits and Systems - II Express Briefs, (61), 10,

773-777.

[14] S.S. Reddy, M. Satyam, K.L. Kishore: Cascadable

adiabatic logic circuits for low-power applications.

IET Circuits Devices Syst., 2008, Vol. 2, No. 6, pp.

518526.

[15] Shelly Garg and Vandana Niranjan, A new

cascadable adiabatic logic technique, Department of

Electrical and Electronics Engineering: An

International Journal (ELELIJ) vol 5, No 1, February

2016.

94

978-1-5090-6590-5/17/$31.00 2017 IEEE

You might also like

- A Fast-Lock Mixed-Mode DLL With Wide-Range Operation and Multiphase OutputsDocument4 pagesA Fast-Lock Mixed-Mode DLL With Wide-Range Operation and Multiphase OutputsAbhishek MinniNo ratings yet

- 180.5Mbps-8Gbps DLL-based Clock and Data Recovery Circuit With Low Jitter PerformanceDocument4 pages180.5Mbps-8Gbps DLL-based Clock and Data Recovery Circuit With Low Jitter PerformanceMinh KhangNo ratings yet

- Vernier Delay Line 1Document8 pagesVernier Delay Line 1Shibnath BhattacharjeeNo ratings yet

- Yin 2011Document11 pagesYin 2011Lâm Trần ThànhNo ratings yet

- Time-to-Digital Converter: Guided ByDocument5 pagesTime-to-Digital Converter: Guided ByVineet SharmaNo ratings yet

- A Fast-Locking Digital Delay-Locked Loop With Multiphase Outputs Using Mixed-Mode-Controlled Delay LineDocument8 pagesA Fast-Locking Digital Delay-Locked Loop With Multiphase Outputs Using Mixed-Mode-Controlled Delay LineMeshcheryakov SlavaNo ratings yet

- An Adaptive Voltage Scaling Circuit Based On Dominate Pole CompensationDocument4 pagesAn Adaptive Voltage Scaling Circuit Based On Dominate Pole CompensationNguyen Van ToanNo ratings yet

- Advanced TDK Techniques: Application Note 62-3 May 1990Document24 pagesAdvanced TDK Techniques: Application Note 62-3 May 1990Alércio RosaNo ratings yet

- A Wide-Range, High-Resolution, Compact, CMOS Time To Digital ConverterDocument6 pagesA Wide-Range, High-Resolution, Compact, CMOS Time To Digital ConverterShruti KalraNo ratings yet

- A Variation and Noise Tolerant Wide Fan-In OR-Logic Domino CircuitDocument6 pagesA Variation and Noise Tolerant Wide Fan-In OR-Logic Domino Circuitkanha gargNo ratings yet

- Chapter 1b: Circuit Switching: ETM 7012 Transmission & Switching: SwitchingDocument45 pagesChapter 1b: Circuit Switching: ETM 7012 Transmission & Switching: Switchingkhaled loteesNo ratings yet

- A CMOS Based Low Power Digitally Controlled OscillDocument12 pagesA CMOS Based Low Power Digitally Controlled OscillDEEPAK PRAJAPATINo ratings yet

- Delay Lock LoopDocument19 pagesDelay Lock LoopjameelahmadNo ratings yet

- TDC VerifiedDocument8 pagesTDC VerifiedeejlnyNo ratings yet

- Minimizing The Delay of C2mos D Flip Flop Using Logical Effort TheoryDocument3 pagesMinimizing The Delay of C2mos D Flip Flop Using Logical Effort TheorySavio SNo ratings yet

- Power-Delay Efficient Overlap-Based Charge-Sharing Free Pseudo-Dynamic D Flip-FlopsDocument4 pagesPower-Delay Efficient Overlap-Based Charge-Sharing Free Pseudo-Dynamic D Flip-FlopsGopi PremalaNo ratings yet

- MDC Project RepoDocument18 pagesMDC Project RepoRihNo ratings yet

- TDA PaperDocument20 pagesTDA PaperwarabegaiNo ratings yet

- Designs of All Digital Phase Locked Loop: A ReviewDocument5 pagesDesigns of All Digital Phase Locked Loop: A ReviewKoldodeRostovNo ratings yet

- 2016 Ieee Pes HVDC STFTDocument5 pages2016 Ieee Pes HVDC STFTAtiqMarwatNo ratings yet

- Low Power Clock-Synchronizer For SOC With Delay Line Controller (DLC) in 45nm CMOS TechnologyDocument6 pagesLow Power Clock-Synchronizer For SOC With Delay Line Controller (DLC) in 45nm CMOS TechnologysrivathsavaNo ratings yet

- A Low-Power Programmable DLL-based Clock Generator With Wide-Range Anti-Harmonic LockDocument4 pagesA Low-Power Programmable DLL-based Clock Generator With Wide-Range Anti-Harmonic LockKushwanth PokapudiNo ratings yet

- Limit Cycle OscillationsDocument7 pagesLimit Cycle OscillationsAsish DuttaNo ratings yet

- A 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSDocument13 pagesA 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSnayakadarsh2000No ratings yet

- ICCSP IEEE Published Paper - ManikanthDocument4 pagesICCSP IEEE Published Paper - ManikanthRamesh NairNo ratings yet

- Design of A Low Power Dynamic Comparator in 180nm CMOS TechnologyDocument6 pagesDesign of A Low Power Dynamic Comparator in 180nm CMOS TechnologyVishnu VardhanNo ratings yet

- A 1.6-To-3.0-GHz Fractional-N MDLL With A Digital-To-Time Converter Range-Reduction Technique Achieving 397fs Jitter at 2.5-MW PowerDocument4 pagesA 1.6-To-3.0-GHz Fractional-N MDLL With A Digital-To-Time Converter Range-Reduction Technique Achieving 397fs Jitter at 2.5-MW PowerSuyog DhakneNo ratings yet

- A Novel Low Power Digitally Controlled Oscillator With Improved Linear Operating RangeDocument6 pagesA Novel Low Power Digitally Controlled Oscillator With Improved Linear Operating RangeNandhini IlangovanNo ratings yet

- Design of All Digital Phase Locked Loop For WireleDocument5 pagesDesign of All Digital Phase Locked Loop For WireleKiran SomayajiNo ratings yet

- High Resolution Time To Digital ConverterDocument5 pagesHigh Resolution Time To Digital ConverterInnybtzNo ratings yet

- Design of High Frequency D Ip Op Circuit For Phase Detector ApplicationDocument6 pagesDesign of High Frequency D Ip Op Circuit For Phase Detector Applicationmohan sardarNo ratings yet

- A Brief Introduction To Time-to-Digital and Digital-to-Time ConvertersDocument5 pagesA Brief Introduction To Time-to-Digital and Digital-to-Time Convertersjulio perezNo ratings yet

- A 0.5-To-2.5 Gbs Reference-Less Half-Rate Digital CDR With Unlimited Frequency Acquisition Range and Improved Input Duty-Cycle Error ToleranceDocument13 pagesA 0.5-To-2.5 Gbs Reference-Less Half-Rate Digital CDR With Unlimited Frequency Acquisition Range and Improved Input Duty-Cycle Error ToleranceMinh KhangNo ratings yet

- A 5-Gbs Adaptive Digital CDR Circuit With SSC Capability and Enhanced High-Frequency Jitter Tolerance PDFDocument5 pagesA 5-Gbs Adaptive Digital CDR Circuit With SSC Capability and Enhanced High-Frequency Jitter Tolerance PDFMinh KhangNo ratings yet

- An Efficient Differential Conditional Capturing Energy Recovery Flip-Flop DesignDocument6 pagesAn Efficient Differential Conditional Capturing Energy Recovery Flip-Flop DesignRaghul RamasamyNo ratings yet

- Kundu Et Al - 2019 - A Fully Integrated Digital LDO With Built-In Adaptive Sampling and ActiveDocument12 pagesKundu Et Al - 2019 - A Fully Integrated Digital LDO With Built-In Adaptive Sampling and Active马晓飞No ratings yet

- The Analog Behavior of Pseudo Digital Ring Oscillators Used in VCO ADCsDocument14 pagesThe Analog Behavior of Pseudo Digital Ring Oscillators Used in VCO ADCszhaohhhengNo ratings yet

- 31 141 146 PDFDocument6 pages31 141 146 PDFlambanaveenNo ratings yet

- DSP Engine For Ultra-Low-Power Audio Applications: Slink4 (32Document4 pagesDSP Engine For Ultra-Low-Power Audio Applications: Slink4 (32kamelNo ratings yet

- DCDL - Noise and JitterDocument4 pagesDCDL - Noise and JitterDavidNo ratings yet

- TDC SSCL FinalDocument4 pagesTDC SSCL FinalRohish Kumar Reddy mittaNo ratings yet

- It's About Time: How TDR Enables Predictive Maintenance For Industrial EthernetDocument6 pagesIt's About Time: How TDR Enables Predictive Maintenance For Industrial EthernetMohsen KhabirNo ratings yet

- A 6.25-MHz 3.4-mW Single Clock DPWM Technique Using Matrix Shift ArrayDocument5 pagesA 6.25-MHz 3.4-mW Single Clock DPWM Technique Using Matrix Shift ArraywarabegaiNo ratings yet

- Digital Phase Lock LoopsDocument17 pagesDigital Phase Lock LoopsArfaaNaseemNo ratings yet

- Cntfet Technology Based Precision Full-Wave Rectifier Using DDCCDocument8 pagesCntfet Technology Based Precision Full-Wave Rectifier Using DDCCresearchinventyNo ratings yet

- Anti-Interference Low-Power Double-Edge Triggered Flip-Flop Based On C-ElementsDocument12 pagesAnti-Interference Low-Power Double-Edge Triggered Flip-Flop Based On C-ElementsVani YamaniNo ratings yet

- A Simulink Model For All-Digital-Phase-Locked-LoopDocument4 pagesA Simulink Model For All-Digital-Phase-Locked-LoopManiNo ratings yet

- IJME Vol 7 Iss 1 Paper 6 1085 1089Document5 pagesIJME Vol 7 Iss 1 Paper 6 1085 1089shravanNo ratings yet

- Lu Et Al - 2019 - PID Control Considerations For Analog-Digital Hybrid Low-Dropout RegulatorsDocument3 pagesLu Et Al - 2019 - PID Control Considerations For Analog-Digital Hybrid Low-Dropout Regulators马晓飞No ratings yet

- Frustaci 2009 BBNKKDocument5 pagesFrustaci 2009 BBNKKHemanthNo ratings yet

- Behavioral Model of Pipeline Adc by Using SimulinkrDocument5 pagesBehavioral Model of Pipeline Adc by Using SimulinkrSounakDuttaNo ratings yet

- Module 3Document25 pagesModule 3Sushanth M100% (3)

- Dual Loop DLLDocument11 pagesDual Loop DLLKiran KNo ratings yet

- Packet Transform Differential Protection For Power TransformersDocument10 pagesPacket Transform Differential Protection For Power TransformersMartins Dario Goncalves GalindoNo ratings yet

- All-Digital Calibration of Timing Mismatch Error in Time-Interleaved Analog-to-Digital ConvertersDocument9 pagesAll-Digital Calibration of Timing Mismatch Error in Time-Interleaved Analog-to-Digital ConvertersHitechNo ratings yet

- A Sub-Mw Fractional-N Adpll With Fom Of: 246 DB For Iot ApplicationsDocument13 pagesA Sub-Mw Fractional-N Adpll With Fom Of: 246 DB For Iot ApplicationsSAMNo ratings yet

- A New ADPLLDocument4 pagesA New ADPLLTruegodman FangNo ratings yet

- Digital Mobile Communications and the TETRA SystemFrom EverandDigital Mobile Communications and the TETRA SystemRating: 5 out of 5 stars5/5 (1)

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Letter For Implementation of Anomaly Committee Faculty Recommendations-1-1Document3 pagesLetter For Implementation of Anomaly Committee Faculty Recommendations-1-1Laxmi KumreNo ratings yet

- STTP On Advances in Optical Communication and Technologies-2016Document2 pagesSTTP On Advances in Optical Communication and Technologies-2016Laxmi KumreNo ratings yet

- MANIT Workshop On Empyrean S ZENI EDA PDFDocument2 pagesMANIT Workshop On Empyrean S ZENI EDA PDFLaxmi KumreNo ratings yet

- 7th CPC Order CFTIs PDFDocument7 pages7th CPC Order CFTIs PDFknighthood4allNo ratings yet

- A Novel Power Analysis Attack Resilient AdiabaticDocument4 pagesA Novel Power Analysis Attack Resilient AdiabaticLaxmi KumreNo ratings yet

- A Low Power Vernier Time-To-digitalDocument5 pagesA Low Power Vernier Time-To-digitalLaxmi KumreNo ratings yet

- Lab BoardsDocument9 pagesLab BoardsLaxmi KumreNo ratings yet

- Innovative Teaching Methodology ScheduleDocument1 pageInnovative Teaching Methodology ScheduleLaxmi KumreNo ratings yet

- Eliminating Oscillation Between Parallel MnosfetsDocument6 pagesEliminating Oscillation Between Parallel MnosfetsCiprian BirisNo ratings yet

- Sheet Metal Manufacturing Companies NoidaDocument9 pagesSheet Metal Manufacturing Companies NoidaAmanda HoldenNo ratings yet

- Quarter 4 English As Grade 4Document28 pagesQuarter 4 English As Grade 4rubyneil cabuangNo ratings yet

- Kwasaki ZX10R 16Document101 pagesKwasaki ZX10R 16OliverNo ratings yet

- All Pop SongsDocument53 pagesAll Pop SongsMadeleneQuiogueNo ratings yet

- Tran-Effects of Assisted JumpingDocument5 pagesTran-Effects of Assisted JumpingyoungjessNo ratings yet

- Generative Shape DesignDocument195 pagesGenerative Shape DesignAdi Fiera100% (1)

- Marketing Management 4th Edition Winer Test BankDocument35 pagesMarketing Management 4th Edition Winer Test Bankapneaocheryzxs3ua100% (24)

- Typical Section SC 10: Kerajaan MalaysiaDocument1 pageTypical Section SC 10: Kerajaan MalaysiaAisyah Atiqah KhalidNo ratings yet

- Approved Project 25 StandardsDocument5 pagesApproved Project 25 StandardsepidavriosNo ratings yet

- ChipmunkDocument19 pagesChipmunkema.nemec13No ratings yet

- 4 5803133100506483687Document245 pages4 5803133100506483687Malik HamidNo ratings yet

- LPG GasDocument39 pagesLPG Gasv prasanthNo ratings yet

- Modern Myth and Magical Face Shifting Technology in Girish Karnad Hayavadana and NagamandalaDocument2 pagesModern Myth and Magical Face Shifting Technology in Girish Karnad Hayavadana and NagamandalaKumar KumarNo ratings yet

- AR BuildingDocument819 pagesAR BuildingShithin KrishnanNo ratings yet

- Book BindingDocument14 pagesBook Bindingpesticu100% (2)

- Salapare Et Al 2015 ZambalesDocument12 pagesSalapare Et Al 2015 ZambalesTiqfar AhmadjayadiNo ratings yet

- Manufacuring EngineeringDocument3 pagesManufacuring Engineeringapi-79207659No ratings yet

- Hazard Assessment For PPE - XX-DRAFTDocument4 pagesHazard Assessment For PPE - XX-DRAFTWayne VanderhoofNo ratings yet

- Ge Fairchild Brochure PDFDocument2 pagesGe Fairchild Brochure PDFDharmesh patelNo ratings yet

- CE Review GEOMETRY 2Document6 pagesCE Review GEOMETRY 2Paul Gerard AguilarNo ratings yet

- Bolt Action Italian Painting GuideDocument7 pagesBolt Action Italian Painting GuideTirmcdhol100% (2)

- Complete Processing Lines For Extruded Pet FoodDocument13 pagesComplete Processing Lines For Extruded Pet FoodденисNo ratings yet

- Resumen C37 010 Aplicacion de Breaker Disenados IC Simetrica PDFDocument9 pagesResumen C37 010 Aplicacion de Breaker Disenados IC Simetrica PDFglendathais100% (1)

- Hot Topic 02 Good Light Magazine 56smDocument24 pagesHot Topic 02 Good Light Magazine 56smForos IscNo ratings yet

- Manual 35S EnglishDocument41 pagesManual 35S EnglishgugiNo ratings yet

- Smoldering Combustion: Guillermo ReinDocument20 pagesSmoldering Combustion: Guillermo ReinAhmed HussainNo ratings yet

- Recycling Mind MapDocument2 pagesRecycling Mind Mapmsole124100% (1)

- Zest O CorporationDocument21 pagesZest O CorporationJhamane Chan53% (15)

- ReviewerDocument3 pagesReviewerKristine SantominNo ratings yet