Professional Documents

Culture Documents

Efficient VLSI Signal Processing Architectures

Uploaded by

Raja PirianOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Efficient VLSI Signal Processing Architectures

Uploaded by

Raja PirianCopyright:

Available Formats

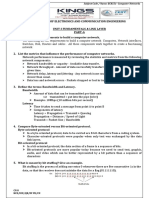

FORMAT : QP09 KCE/DEPT.

OF ECE

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

ME VLSI DESIGN

SUBJECT : VLSI SIGNAL PROCESSING

SEMESTER : II

COURSE PLAN (VL 5291)

(Version : 1)

PREPARED BY

Mr. P.RAJA PIRIAN, AP/ECE

VLSI SP 1 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

VL5291 VLSI SIGNAL PROCESSING LTPC

3003

UNIT I PIPELINING AND PARALLEL PROCESSING OF DIGITAL FILTERS 9

Introduction to DSP systems Typical DSP algorithms, Data flow and Dependence grap hs critical

path, Loop bound, iteration bound, Longest path matrix algorithm, Pipelining and Parallel processing

of FIR filters, Pipelining and Parallel processing for low power.

UNIT II ALGORITHMIC STRENGTH REDUCTION TECHNIQUE I 9

Retiming definitions and properties, Unfolding an algorithm for unfolding, properties of

unfolding, sample period reduction and parallel processing application, Algorithmic strength

reduction in filters and transforms 2 - parallel FIR filter, 2-parallel fast FIR filter, DCT architecture,

rank-order filters, Odd - Even merge - sort architecture, parallel rank - order filters.

UNIT III ALGORITHIMIC STRENGTH REDUCTION II 9

Fast convolution Cook - Toom algorithm, modified Cook Toom algorithm, Pipelined and parallel

recursive filters Look - Ahead pipelining in first - order IIR filters, Look

Ahead pipelining with power of - 2 decomposition, Clustered look - ahead pipelining, Parallel

processing of IIR filters, combined pipelining and parallel processing of IIR filters.

UNIT IV BIT - LEVEL ARITHMETIC ARCHITECTURES 9

Bit - level arithmetic architectures parallel multipliers with sign extension, parallel carry - ripple

and carry - save multipliers, Design of Lyons bit - serial multipliers using Horners rule, bit - serial

FIR filter, CSD representation, CSD multiplication using Horners rule for precision improvement,

Distributed Arithmetic fundamentals and FIR filters

UNIT V NUMERICAL STRENGTH REDUCTION, WAVE AND

ASYNCHRONOUS PIPELINING 9

Numerical strength reduction sub expression elimination, multiple constant multiplication,

iterative matching, synchronous pipelining and clocking styles, clock skew in edge - triggered single

phase clocking, two phase clocking, wave pipelining. Asynchronous pipelining bundled data versus

dual rail protocol.

TOTAL: 45 PERIODS

SIGNATUR OF STAFF INCHARGE HOD/ECE

( P.RAJA PIRIAN )

VLSI SP 2 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

COURSE PLAN

Sub. Code : VL 5291 Branch / Year / Sem : M.E VLSI/ I / II

Sub.Name : VLSI SIGNAL PROCESSING Batch : 2017 -2019

Staff Name : Mr. P.Raja Pirian Academic Year : 2017-18 (EVEN)

COURSE OBJECTIVE

To introduce techniques for altering the existing DSP structures to suit VLSI

implementations.

To introduce efficient design of DSP architectures suitable for VLSI

REFERENCES:

R1. Keshab K. Parhi, VLSI Digital Signal Processing Systems, Design and implementation,

Wiley, Interscience, 2007.

WEB RESOURCES

W1. http://galia.fc.uaslp.mx/~rmariela/RTDSP/ch4.pdf. (Topic : 07)

W2. http://www.iro.umontreal.ca/~dift6221/demicheli4/retiming.4.ps.pdf. (Topic : 09)

W3. http://web.cecs.pdx.edu/~mperkows/CAPSTONES/DSP1/parapipe.ppt. (Topic : 24)

W4. http://www.win.tue.nl/~cberkel/2IN35/Parhi/chap13.pdf. (Topic : 26)

W5. http://ics.kaist.ac.kr/ee877_2015s/A4_Numerical_Strength_Reduction.pdf. (Topic : 34)

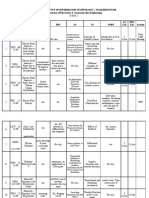

Topic Topic Books for Page No. Teaching No. of Cumulative

VLSI SP 3 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

Hours No. of

No Reference Methodology

Required periods

UNIT I PIPELINING AND PARALLEL PROCESSING OF DIGITAL FILTERS (09)

Introduction to DSP

01. R1 1 BB 1 1

systems

Typical DSP

02. R1 2-26 BB 1 2

algorithms

Data flow and

03. R1 36-40 BB 1 3

Dependence graphs

04. Critical path R1 45 BB 1 4

Loop bound,

05. R1 45-47 BB 1 5

Iteration bound

Longest path

06. R1 47-50 BB 1 6

matrix algorithm

Pipelining and

R1 63-76 BB

07. Parallel processing 2 8

W1 1-46 PPT

of FIR filters

Pipelining and

08. Parallel processing R1 76-83 BB 1 9

for low power

LEARNING OUTCOME

At the end of unit, students should be able to

Understand the concepts of different dataflow algorithm.

Describe the behaviors of digital filters.

Acquire knowledge about Parallel Processing.

UNIT II ALGORITHMIC STRENGTH REDUCTION TECHNIQUE I (09)

Retiming

R1 91-112 BB

09. definitions and 1 10

W2 1-9 PPT

properties

Unfolding an

10. algorithm for R1 119-126 BB 1 11

unfolding

Properties of

11. R1 127-128 BB 1 12

unfolding

Sample period

reduction and

12. R1 128-140 BB 1 13

parallel processing

application

Algorithmic

strength reduction

13. R1 255-256 BB 1 14

in filters and

transforms.

No. of Cumulative

Topic Books for Teaching

Topic Page No. Hours No. of

No Reference Methodology

Required periods

VLSI SP 4 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

Parallel FIR filter,

14. parallel fast FIR R1 256-275 BB 1 15

filter,

DCT architecture,

15. rank Order filters R1 275-296 BB 1 16

Odd - Even merge -

16. sort architecture R1 286-288 BB 1 17

Parallel rank -

17. order filters. R1 289-293 BB 1 18

LEARNING OUTCOME

At the end of unit, students should be able to

Understand the concepts retiming.

Describe about the reduction methods.

Acquire knowledge about different DCT architectures.

UNIT III ALGORITHIMIC STRENGTH REDUCTION II (09)

Fast convolution

18. Cook - Toom R1 227-234 BB 1 19

algorithm

Modified Cook

19. R1 234-242 BB 2 21

Toom algorithm,

Pipelined and

20. parallel recursive R1 313-320 BB 1 22

filters

Look - Ahead

21. pipelining in first - R1 320-321 BB 1 23

order IIR filters

Look Ahead

pipelining with

22. R1 321-324 BB 1 24

power of - 2

decomposition

Clustered look -

23. R1 327-328 BB 1 25

ahead pipelining

Parallel processing R1 339-345 BB

24. 1 26

of IIR filters W3 1-13 PPT

Combined

pipelining and

25. R1 345-348 BB 1 27

parallel processing

of IIR filters.

No. of Cumulative

Topic Books for Teaching

Topic Page No. Hours No. of

No Reference Methodology

Required periods

VLSI SP 5 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

LEARNING OUTCOME

At the end of unit, students should be able to

Understand the concept of fast convolution algorithm.

Describe the pipelining algorithms used for FIR and IIR filter.

Acquire knowledge about pipelining and parallel processing of IIR filters..

UNIT IV BIT - LEVEL ARITHMETIC ARCHITECTURES (09)

Bit - level arithmetic R1 477-478 BB

26. architectures 1 28

W4 1-38 PPT

Parallel multipliers

27. R1 478-481 BB 1 29

with sign extension

Parallel carry - ripple

28. and carry - save R1 481-483 BB 1 30

multipliers

Design of Lyons bit -

29. serial multipliers R1 490-495 BB 1 31

using Horners rule

30. Bit - serial FIR filter R1 499-501 BB 1 32

31. CSD representation R1 505-507 BB 1 33

CSD multiplication

using Horners rule

32. R1 507-511 BB 1 34

for precision

improvement

Distributed

Arithmetic

33. R1 511-518 BB 2 36

fundamentals and

FIR filters

LEARNING OUTCOME

At the end of unit, students should be able to

Understand the concepts of various Bit level arithmetic architectures.

Describe Horners rule for Lyons bit serial multipliers.

Acquire knowledge about the arithmetic fundamentals used in FIR filter.

UNIT V NUMERICAL STRENGTH REDUCTION, WAVE AND ASYNCHRONOUS

PIPELINING (09)

Numerical strength R1 BB

34. 559 1 37

reduction W5 PPT

Sub expression

35. R1 560 BB 1 38

elimination

Multiple constant

36. R1 560-566 BB 1 39

multiplication

37. Iterative matching R1 561-562 BB 1 40

No. of Cumulative

Topic Books for Teaching

Topic Page No. Hours No. of

No Reference Methodology

Required periods

VLSI SP 6 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

Synchronous

38 pipelining and R1 593-600 BB 1 41

clocking styles

39. Clock skew in edge R1 601-602 BB 1 42

Triggered single

40. phase clocking, R1 602-603 BB 1 43

Two phase

604

41. Clocking, R1 BB 1 44

606-611

wave pipelining.

Asynchronous

pipelining bundled

42. R1 619-621 BB 1 45

data versus dual

rail protocol.

LEARNING OUTCOME

At the end of unit, students should be able to

Understand the concepts numerical reduction in pipelining.

Describe effectiveness of clock signals in the pipelining.

Acquire knowledge about asynchronous pipelining and dual rail protocol.

COURSE OUTCOME

At the end of the course, the students will be able to

Know about Pipelining in parallel processing of digital filters.

Get an idea about algorithmic reduction techniques.

Understand the concept of BIT level arithmetic algorithms in Pipelining.

Get familiar with various reduction technique and also know about clock signal operations

in pipeline.

CONTENT BEYOND THE SYLLABUS

1. Signal Processing in Neural Network Using VLSI Implementation.

INTERNAL ASSESSMENT DETAILS

TEST NO. I II MODEL

Topic Nos. 1-17 18-33 1-42

Date

Prepared by Verified By

Mr.P.Raja Pirian HOD/ECE

Approved by

PRINCIPAL

REVIEW SHEET

VLSI SP 7 KCE/I M.E VLSI / VLSI SP

FORMAT : QP09 KCE/DEPT. OF ECE

After Completion of syllabus

Faculty experience in handling / covering syllabus

Unit I :

Unit II :

Unit III :

Unit IV :

Unit V :

Difficulties (if any)

Feedback on University Question Paper

SIGNATURE OF STAFF HOD/ECE

VLSI SP 8 KCE/I M.E VLSI / VLSI SP

You might also like

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsFrom EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNo ratings yet

- Radio-Frequency Digital-to-Analog Converters: Implementation in Nanoscale CMOSFrom EverandRadio-Frequency Digital-to-Analog Converters: Implementation in Nanoscale CMOSRating: 4 out of 5 stars4/5 (1)

- Satellite Communication Orbital Parameters and PerturbationsDocument30 pagesSatellite Communication Orbital Parameters and PerturbationsRaja Pirian57% (7)

- P1 - 16 and Quantization... DCDocument8 pagesP1 - 16 and Quantization... DCsana aminNo ratings yet

- Digital Electronics Question BankDocument10 pagesDigital Electronics Question BankponniNo ratings yet

- PX5004 - MR & RCDocument5 pagesPX5004 - MR & RCNarasimman DonNo ratings yet

- MEL G623 Advanced VLSI Design Course Handout: SECOND SEMESTER 2021-2022Document7 pagesMEL G623 Advanced VLSI Design Course Handout: SECOND SEMESTER 2021-2022SARITA GAJANAN BIJAWENo ratings yet

- Department of Electronics and Communication Engineering: Prepared byDocument6 pagesDepartment of Electronics and Communication Engineering: Prepared byheraldNo ratings yet

- Subject: Communication Theory: Department of Electronics and Communication EngineeringDocument12 pagesSubject: Communication Theory: Department of Electronics and Communication EngineeringponniNo ratings yet

- Subject: Ec8501 Digital Communication: Department of Electronics and Communication EngineeringDocument6 pagesSubject: Ec8501 Digital Communication: Department of Electronics and Communication EngineeringheraldNo ratings yet

- COURSE - DATA - SHEET2020-21@EM-I UpdatedDocument2 pagesCOURSE - DATA - SHEET2020-21@EM-I UpdatedMohammad Rafee ShaikNo ratings yet

- Ec8651 Unit 2Document54 pagesEc8651 Unit 2santhoshiniNo ratings yet

- Mel ZG625 Course HandoutDocument5 pagesMel ZG625 Course HandoutanbuNo ratings yet

- Digital Electronics Course OutlineDocument15 pagesDigital Electronics Course OutlineYash KuncolienkerNo ratings yet

- Microprocessors and Microcontrollers Question BankDocument11 pagesMicroprocessors and Microcontrollers Question BankheraldNo ratings yet

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- MPMC CP FinalDocument9 pagesMPMC CP Finalsimman8371029No ratings yet

- Subject: Electronic Devices: Department of Electronics and Communication EngineeringDocument9 pagesSubject: Electronic Devices: Department of Electronics and Communication EngineeringAnonymous 9WJ7YeGNo ratings yet

- Ldica Course Info Sheet and Question BankDocument28 pagesLdica Course Info Sheet and Question BankDr.B.Krishna KumarNo ratings yet

- Lesson Plan CEDocument4 pagesLesson Plan CEsureshvkumarNo ratings yet

- Ec8651 Unit 4Document47 pagesEc8651 Unit 4santhoshiniNo ratings yet

- Ec8651 Unit 1Document52 pagesEc8651 Unit 1santhoshiniNo ratings yet

- 07GSSDocument15 pages07GSSMokbelNo ratings yet

- Course Detail Format - LICDocument48 pagesCourse Detail Format - LICSamadhan ThokalNo ratings yet

- Ec8094 Unit 3 Satellite Communication Rmkec NotesDocument81 pagesEc8094 Unit 3 Satellite Communication Rmkec NotesAkNo ratings yet

- RAN KPI Analysis: 3G Network KPI Customised SeminarDocument152 pagesRAN KPI Analysis: 3G Network KPI Customised SeminarJoseph OgundiranNo ratings yet

- Junior Engineer CourseDocument101 pagesJunior Engineer CourseAjay ShankarNo ratings yet

- Communication Lab Course Plan Ec8561Document4 pagesCommunication Lab Course Plan Ec8561heraldNo ratings yet

- Vlsi DesignDocument22 pagesVlsi Designkoushikpallanti7No ratings yet

- Design of Radix-4 Signed Digit Encoding for Pre-Encoded MultipliersDocument6 pagesDesign of Radix-4 Signed Digit Encoding for Pre-Encoded MultipliersKanak KujurNo ratings yet

- DPSD CS8351 U1 PDFDocument182 pagesDPSD CS8351 U1 PDFPragna SidhireddyNo ratings yet

- 117276Document8 pages117276RamKumarNo ratings yet

- EC8691 Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesEC8691 Lesson Plan Microprocessor and Micro COntrollerlauro eugin brittoNo ratings yet

- DPSD Unit 3Document175 pagesDPSD Unit 3Pragna SidhireddyNo ratings yet

- An 8-Bit 120-MS/s Interleaved CMOS Pipeline ADC Based On MOS Parametric AmplificationDocument5 pagesAn 8-Bit 120-MS/s Interleaved CMOS Pipeline ADC Based On MOS Parametric Amplificationjulio perezNo ratings yet

- Lesson Plan PPEDocument6 pagesLesson Plan PPEGajendran A MECH KIOTNo ratings yet

- EDGE_OPT_Delhi_VAS_MeetingDocument44 pagesEDGE_OPT_Delhi_VAS_Meetingdangdoan2008No ratings yet

- Lesson Plan ECIDocument4 pagesLesson Plan ECIsureshvkumarNo ratings yet

- Vlsi Lab1 Lesson PlanDocument5 pagesVlsi Lab1 Lesson PlanRaja PirianNo ratings yet

- WC Lesson PlanDocument7 pagesWC Lesson PlanParanthaman GNo ratings yet

- NBA Modified RF&MW LPDocument4 pagesNBA Modified RF&MW LPshankarNo ratings yet

- Analog & Digital VLSI Design Course HandoutDocument3 pagesAnalog & Digital VLSI Design Course HandoutB Naresh Kumar ReddyNo ratings yet

- Syllabus Computer Science (3rd-8th) SemDocument57 pagesSyllabus Computer Science (3rd-8th) SemAsim Arunava Sahoo100% (2)

- Channel Estimation With MatlabDocument34 pagesChannel Estimation With Matlabsaeedmap95% (19)

- De&mp Unit - 3Document29 pagesDe&mp Unit - 3Mahesh BabuNo ratings yet

- Training Modules For Group B Officers & Group C Supervisors of S&T DepartmentDocument59 pagesTraining Modules For Group B Officers & Group C Supervisors of S&T DepartmentMayank TripathiNo ratings yet

- Pulse and Switching Circuits Course HandoutDocument5 pagesPulse and Switching Circuits Course HandoutSunny BNo ratings yet

- CMOS-controlled Inverting CDBA With A New All-PassDocument10 pagesCMOS-controlled Inverting CDBA With A New All-Passسعيد عبدالله فرحانNo ratings yet

- 21ec401 Unit IiiDocument71 pages21ec401 Unit IiisanthoshiniNo ratings yet

- Final Report 1Document61 pagesFinal Report 1Ashwin ThiyagarajanNo ratings yet

- My Top Skills:-: Short BioDocument7 pagesMy Top Skills:-: Short BiosanchayanNo ratings yet

- Low Power and Delay Efficient 32 - Bit Hybrid Carry Skip Adder Implementation Using HDLDocument4 pagesLow Power and Delay Efficient 32 - Bit Hybrid Carry Skip Adder Implementation Using HDLRahul SharmaNo ratings yet

- A Course Material On DIGITAL ELECTRONICS PDFDocument208 pagesA Course Material On DIGITAL ELECTRONICS PDFdasari_reddyNo ratings yet

- A Course Material On Digital ElectronicsDocument208 pagesA Course Material On Digital Electronicssritama royNo ratings yet

- Pipelined Adc-Final Version-20160606Document12 pagesPipelined Adc-Final Version-20160606Kasi BandlaNo ratings yet

- Electronic Devices and Circuits.Document8 pagesElectronic Devices and Circuits.Raja PirianNo ratings yet

- Vignan'S Institute of Information Technology:: Visakhapatnam Department of Electronics & Communication EngineeringDocument94 pagesVignan'S Institute of Information Technology:: Visakhapatnam Department of Electronics & Communication Engineeringsonyprasanna416No ratings yet

- 21ec401 Unit IDocument81 pages21ec401 Unit IsanthoshiniNo ratings yet

- Enabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksFrom EverandEnabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksNo ratings yet

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...From EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...No ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- ECE Microprocessor & Microcontroller Lab Course PlanDocument2 pagesECE Microprocessor & Microcontroller Lab Course PlanRaja PirianNo ratings yet

- Quiz For The Subject Microprocessors and Microcontrollers EC8691Document2 pagesQuiz For The Subject Microprocessors and Microcontrollers EC8691Raja PirianNo ratings yet

- Communication Network EC8551Document43 pagesCommunication Network EC8551Raja Pirian100% (3)

- Digital Logic CircuitsDocument3 pagesDigital Logic CircuitsRaja PirianNo ratings yet

- EC8551 Revision QuestionDocument3 pagesEC8551 Revision QuestionRaja PirianNo ratings yet

- Satellite Communication Lesson Plan 2018Document11 pagesSatellite Communication Lesson Plan 2018Raja PirianNo ratings yet

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- EC8553 Electron Devices and Circuits Question BankDocument24 pagesEC8553 Electron Devices and Circuits Question BankRaja PirianNo ratings yet

- EC8551 CN Question BankDocument43 pagesEC8551 CN Question BankRaja Pirian100% (3)

- Electronic Devices and Circuits.Document8 pagesElectronic Devices and Circuits.Raja PirianNo ratings yet

- Electronic Devices and Circuits.Document8 pagesElectronic Devices and Circuits.Raja PirianNo ratings yet

- Renewable Energy Sources Course PlanDocument8 pagesRenewable Energy Sources Course PlanRaja PirianNo ratings yet

- I C Bus: Inter-Integrated Circuit BusDocument12 pagesI C Bus: Inter-Integrated Circuit BusRaja PirianNo ratings yet

- CanbusDocument19 pagesCanbushakmanNo ratings yet

- VL7002 - Security Solutions in VlsiDocument10 pagesVL7002 - Security Solutions in VlsiRaja PirianNo ratings yet

- Vlsi Lab1 Lesson PlanDocument5 pagesVlsi Lab1 Lesson PlanRaja PirianNo ratings yet

- Mutiple Choice Question For Satellite CommunicationDocument4 pagesMutiple Choice Question For Satellite CommunicationRaja Pirian67% (3)

- Efficient VLSI Signal Processing ArchitecturesDocument8 pagesEfficient VLSI Signal Processing ArchitecturesRaja PirianNo ratings yet

- Attitude and Orbit ControlDocument28 pagesAttitude and Orbit ControlRaja PirianNo ratings yet

- FFTDocument15 pagesFFTRaja PirianNo ratings yet

- EC6004 Satellite Communication LTPCDocument2 pagesEC6004 Satellite Communication LTPCRaja Pirian50% (2)

- FFT and Spectral LeakageDocument2 pagesFFT and Spectral LeakageRaja PirianNo ratings yet

- Mobile Ad Hoc Networks Question Bank (MANET QBDocument31 pagesMobile Ad Hoc Networks Question Bank (MANET QBRaja Pirian100% (3)

- Question Bank Computer NetworkDocument23 pagesQuestion Bank Computer NetworkRaja PirianNo ratings yet

- EngDocument166 pagesEngEzequiel AnayaNo ratings yet

- Adhoc Lesson Plan EC2050Document10 pagesAdhoc Lesson Plan EC2050Raja PirianNo ratings yet

- Format For Student Project ProposalDocument1 pageFormat For Student Project ProposalRaja PirianNo ratings yet

- EC2205 EC1 - 2marksDocument25 pagesEC2205 EC1 - 2marksRaja PirianNo ratings yet

- Statement of Purpose - EeeDocument1 pageStatement of Purpose - EeeRakesh Mitra100% (1)

- Whats NewDocument18 pagesWhats NewKeadaan BisaNo ratings yet

- Fir Filter Matlab Design PracticalDocument3 pagesFir Filter Matlab Design PracticalKola OladapoNo ratings yet

- DSP Architecture PDFDocument353 pagesDSP Architecture PDFNhật TrungNo ratings yet

- VHF FM Repeater: S-14425XZ-C1 Jun. 2008Document44 pagesVHF FM Repeater: S-14425XZ-C1 Jun. 2008Jorge Enrique Anzola CarrilloNo ratings yet

- Signals and SystemsDocument27 pagesSignals and SystemsEdward Amoyen AbellaNo ratings yet

- Conv2d IntroDocument32 pagesConv2d IntroTín NguyễnNo ratings yet

- Final Smart Traffic Management System PPT Using DipDocument44 pagesFinal Smart Traffic Management System PPT Using DipSaloni SinghNo ratings yet

- QuestionDocument3 pagesQuestionSatish PaswanNo ratings yet

- HST.582J / 6.555J / 16.456J Biomedical Signal and Image ProcessingDocument23 pagesHST.582J / 6.555J / 16.456J Biomedical Signal and Image ProcessingEduardo AlvarezNo ratings yet

- Develop Board - DSP2812 ..Document7 pagesDevelop Board - DSP2812 ..iman145No ratings yet

- An Introduction To Digital Signal Processing: Dr. René Cumplido CCC InaoeDocument13 pagesAn Introduction To Digital Signal Processing: Dr. René Cumplido CCC InaoeAlexander Fabros SolivenNo ratings yet

- 5 Discrete Processing of Analog SignalsDocument21 pages5 Discrete Processing of Analog SignalsCHARLES MATHEWNo ratings yet

- FIR FilterDocument32 pagesFIR FilterWan TingNo ratings yet

- JPEG Compressor Using MATLABDocument6 pagesJPEG Compressor Using MATLABاحمد ابراهيمNo ratings yet

- Matlab Code For Gaussian Filter in Digital Image ProcessingDocument1 pageMatlab Code For Gaussian Filter in Digital Image Processinggeonav_had100% (4)

- Ec3354signals and Systemsl T P C 3 1 0 4Document3 pagesEc3354signals and Systemsl T P C 3 1 0 4fathimabashaNo ratings yet

- TS 2000Document4 pagesTS 2000Firdaus AriefatosaNo ratings yet

- Yamaha RX v573 HTR 5065Document134 pagesYamaha RX v573 HTR 5065jiktorNo ratings yet

- Chapter 3 Routes & Transfers: Operations Manual: DSP Logger MX 300 & DSP Data ManagementDocument14 pagesChapter 3 Routes & Transfers: Operations Manual: DSP Logger MX 300 & DSP Data ManagementEduardo_77No ratings yet

- Jntua B.tech 4-2 Ece R15Document10 pagesJntua B.tech 4-2 Ece R15turimerla swathiNo ratings yet

- Laboratory Manual 2021-2022: Digital Signal Processing LaboratoryDocument77 pagesLaboratory Manual 2021-2022: Digital Signal Processing LaboratorySanket AmbadagattiNo ratings yet

- Contrast Enhancement of Mammograms For Rapid Detection of Microcalcification ClustersDocument10 pagesContrast Enhancement of Mammograms For Rapid Detection of Microcalcification ClustersmarkNo ratings yet

- EC2306 DSP LAB RECORD - Final PDFDocument90 pagesEC2306 DSP LAB RECORD - Final PDFJayamani Krishnan100% (1)

- CS2403 DSP 2 Marks Important QuestionsDocument6 pagesCS2403 DSP 2 Marks Important QuestionsSakthiRJNo ratings yet

- Digital Signal Processing A Practical Guide For Engineers and ScientistsDocument26 pagesDigital Signal Processing A Practical Guide For Engineers and ScientistsissayedNo ratings yet

- Adc Dac ReportDocument6 pagesAdc Dac ReportatgNo ratings yet

- BR-101D Technical and Applications Literature Selector Guide and Cross ReferencesDocument132 pagesBR-101D Technical and Applications Literature Selector Guide and Cross ReferencesEdward YanezNo ratings yet

- Multirate Signal Processing Tutorial Using MATLAB : I. II. IiiDocument24 pagesMultirate Signal Processing Tutorial Using MATLAB : I. II. IiiSaravana KumarNo ratings yet