Professional Documents

Culture Documents

ESSSIETK3

Uploaded by

Chaitanya ThejaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ESSSIETK3

Uploaded by

Chaitanya ThejaCopyright:

Available Formats

1.

(B)PSPICE SIMULATION OF BJT CHARACTERISTICS

Expt No:

Date:

AIM:

To simulate BJT IV-Characteristics and verify the output

waveforms using Pspice.

APPARATUS REQUIRED:

PSPICE software

PC

ALGORITHMS:

Step1: Click on the Orcad release icon on the desktop.

Step2: Click file, new, text file.

Step3: Type the coding.

Step4: Save the file with .cir extension.

Step5: Close and open the application.

Step6: Find file in the text box over the top.

Step7: Go to simulation and Run the coding.

Step8: Plot and plot to the window.

Step9: Trace and add trace to choose the parameter to be

drawn as waveform.

Step10: Verify the O/P with the waveforms.

PROCEDURE:

1. Draw the BJT 2N6546 model circuit .

2. Place the nodes in the circuit.

3. Write the Pspice coding to the circuit.

Electrical system Simulation Lab(PED) SIETK-PUTTUR

4. Simulate the coding using Pspice No.

5. Trace the O/P waveform.

BJT CIRCUIT SPICE MODEL:

GRAPH:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

BJT SPICE CODEING:

*SOURCE

VS 1 0 DC 12V

VY 1 2 DC 0V

VG 7 3 PULSE 0V 30V 0.1NS 0/Ins 16.7US 4OUS)

*CIRCUIT

RB 7 6 250 ; Transistor base resistance

R505

L 3 4 145.8UH

C 5 0 200UF IC=3V

VX 4 5 DC 0V

DM 0 3 DMOD

.MODEL DMOD D(IS=2.22E-15 BV=1200V TT=0)

Q1 2 6 3 3 2N6546

.MODEL 2N6546 NPN (IS=6.83E-14 BF=13 CJE=1PF CJC=607.3PF

TF=26.5NS)

*ANALYSIS

.TRAN 2US 2.1MS 2MS UIC; Transient analysis

.PROBE

.OPTIONS ABSTOL=1.OON RELTOL=0.01 VNTOL=0.1 ITL5=40000

.FOUR 25KHZ I(VY)

.END

Electrical system Simulation Lab(PED) SIETK-PUTTUR

SIMULATION OUTPUT:

RESULT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

1.(C)PSPICE SIMULATION OF RLC–CIRCUIT PARAMETER

Expt No:

Date:

AIM:

To simulate RLC-Circuit parameter and verify the output

waveforms using Pspice.

APPARATUS REQUIRED:

PSPICE software

PC

ALGORITHMS:

Step1: Click on the Orcad release icon on the desktop.

Step2: Click file, new, text file.

Step3: Type the coding.

Step4: Save the file with .cir extension.

Step5: Close and open the application.

Step6: Find file in the text box over the top.

Step7: Go to simulation and Run the coding.

Step8: Plot and plot to the window.

Step9: Trace and add trace to choose the parameter to be

drawn as waveform.

Step10: Verify the O/P with the waveforms.

PROCEDURE:

1. Draw the RLC-Circuit parameter model circuit .

2. Place the nodes in the circuit.

3. Write the Pspice coding to the circuit.

Electrical system Simulation Lab(PED) SIETK-PUTTUR

4. Simulate the coding using Pspice No.

5. Trace the O/P waveform.

RLC-Circuit diagram:

EXPECTED GRAPH:

PSPICE RLC-CIRCUIT CODE :

RLC-CIRCUIT:

* PULSE (-VS +VS TD TR TF PW PER)

VIN 1 0 PULSE(-220V 220V 0 1NS 1NS 100US 200US)

R1 1 2 2OHMS

L1 2 3 50UH

Electrical system Simulation Lab(PED) SIETK-PUTTUR

C1 3 0 10UF

*TRAN TSTEP TSTOP

.TRAN 1US 400US

*. TRAN V(R1) V(L1) V(C1)

*.PLOT TRAN V(3) I(R1)

.PROBE

.END

SIMULATION OUTPUT:

RESULT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

1.(C)PSPICE SIMULATION OF DIODE PARAMETER

Expt No:

Date:

AIM:

To simulate diode parameter and verify the output

waveforms using Pspice.

APPARATUS REQUIRED:

PSPICE software

PC

ALGORITHMS:

Step1: Click on the Orcad release icon on the desktop.

Step2: Click file, new, text file.

Step3: Type the coding.

Step4: Save the file with .cir extension.

Step5: Close and open the application.

Step6: Find file in the text box over the top.

Step7: Go to simulation and Run the coding.

Step8: Plot and plot to the window.

Step9: Trace and add trace to choose the parameter to be

drawn as waveform.

Step10: Verify the O/P with the waveforms.

PROCEDURE:

1. Draw the diode parameter model circuit .

2. Place the nodes in the circuit.

3. Write the Pspice coding to the circuit.

Electrical system Simulation Lab(PED) SIETK-PUTTUR

4. Simulate the coding using Pspice No.

5. Trace the O/P waveform.

CIRCUIT DIAGRAM FOR DIODE MODEL:

INPUT VOLTAGE GRAPH:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

PSPICE CIRCUIT CODEING:

%RLC CIRCUIT WITH DIODE

.PARAM VALUE = 160

.STEP PARAM VALU LIST 50 160 320

VS 1 0 PWL(0 0 INS 220V 1MS 220V)

R 2 3 (VALU)

L 3 4 2MH

C 4 0 0.05UF

D1 1 2 DMOD

.MODEL DMOD D(IS=2.22E-15 BV=1800V)

.TRAN 0.1US 60US

.PROBE

.END

SIMULATION OUTPUT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

Electrical system Simulation Lab(PED) SIETK-PUTTUR

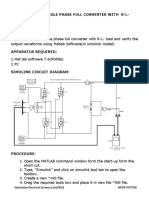

(A)SIMULATION OF THE RESISTIVITY VERSUS DOPING

CONCENTRATION

(B) SATURATION CURRENT

Expt No:

Date:

AIM: To simulate the resistivity versus doping concentration

and Saturation current verify the output waveforms using

Matlab Software(in script model)

APPARATUS REQUIRED:

1.Mat lab software 7.6(R008a)

2.PC

PROCEDURE:

1.Open the MATLAB command window form the start-up form

the short cut.

2.Type, “Simulink” and click on simulink tool bar to open the

toolbox.

3.Create a new *.mfile

4.Save with the extension of .M file.

5.Simulate the mdl design and verify the output with the

theoretical values.

Use MATLAB to plot the resistivity versus doping concentration

(cm-3 ).

MATLAB SCRIPT:

% nc is doping concentration

% rn - resistivity of n-type

% rp - resistivity of p-type

nc = logspace(14,20);

rn = (3.75e15 + nc.^0.91)./(1.47e-17*nc.^1.91 +

8.15e-1*nc);

rp = (5.86e12 + nc.^0.76)./(7.63e-18*nc.^1.76 +

4.64e-4*nc);

semilogx(nc,rn,'w',nc,rp,'w')

axis([1.0e14, 1.0e17,0,140])

Electrical system Simulation Lab(PED) SIETK-PUTTUR

title('Resistivity versus Doping')

ylabel('Resistivity (ohm-cm)')

xlabel('Doping Concentration cm-3')

text(1.1e14,12,'N-type')

text(3.0e14,50,'P-type')

MATLAB OUTPUT:

RESULT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

(B) SATURATION CURRENT

A silicon diode has IS = 10-15 A at 25o C and assuming IS

increases by 15% per oC rise in temperature, find and plot the

value of IS from 25 oC to 125oC.

MATLAB SCRIPT:

t = 25:5:125;

is = 1.0e-15*(1.15).^(t-25);

plot(t,is)

title('Reverse Saturation Current vs. Temperature')

xlabel('Temperature, C')

ylabel('Current, A')

MATLAB OUTPUT:

RESULT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

(A)SIMULATION OF AN N-CHANNEL ENHANCEMENT-

TYPE MOSFET.

(B) BREAKDOWN REGION (Si&Ge)

Expt No:

Date:

AIM: To simulate of an n-channel enhancement-type MOSFET

and breakdown region(Si&Ge) verify the output waveforms

using Matlab Software(in script model)

APPARATUS REQUIRED:

1.Mat lab software 7.6(R008a)

2.PC

PROCEDURE:

1.Open the MATLAB command window form the start-up form

the short cut.

2.Type, “Simulink” and click on simulink tool bar to open the

toolbox.

3.Create a new *.mfile

4.Save with the extension of .M file.

5. Simulate the mdl design and verify the output with the

Theoretical values.

Electrical system Simulation Lab(PED) SIETK-PUTTUR

Problem 1:

For an n-channel enhancement-type MOSFET with kn = 1 mA

/V 2 and V = 1.5V, use MATLAB to sketch the I-Characteristics

for VGS = 4, 6, 8 and for VDS between 0 and 12V.

MATLAB SCRIPT:

% I-V characteristics of mosfet%

kn=1e-3;

vt=1.5;

vds=0:0.5:12;

vgs=4:2:8;

m=length(vds);

n=length(vgs);

for i=1:n

for j=1:m

if vgs(i) < vt

cur(i,j)=0;

elseif vds(j) >= (vgs(i) - vt)

cur(i,j)=kn * (vgs(i) - vt)^2;

elseif vds(j) < (vgs(i) - vt)

cur(i,j)= kn*(2*(vgs(i)-vt)*vds(j) - vds(j)^2);

end

end

end

plot(vds,cur(1,:),'w',vds,cur(2,:),'w',vds,cur(3,:),'

w')

xlabel('Vds, V')

ylabel('Drain Current,A')

title('I-V Characteristics of a MOSFET')

text(6, 0.009, 'Vgs = 4 V')

text(6, 0.023, 'Vgs = 6 V')

text(6, 0.045, 'Vgs = 8 V')

Electrical system Simulation Lab(PED) SIETK-PUTTUR

SIMULATION RESULT:

RESULT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

(B) BREAKDOWN REGION (Si&Ge)

PROBLEM 2:

Use MATLAB to plot the breakdown voltage versus doping

concentration for a one-sided step junction for silicon and

germanium, and using doping concentration from 1014 to 1019

cm-3.

MATLAB SCRIPT:

% Breakdown voltage

k1 = 25;

k2 = 60;

nb = logspace(14,19);

n = length(nb);

for i = 1:n

vbr1(i) = k1*(nb(i)/1.0e16)^(-0.75); % Ge breakdown

voltage

vbr2(i) = k2*(nb(i)/1.0e16)^(-0.75); % Si breakdown

voltage

end

semilogx(nb,vbr1,'w', nb,vbr2,'w')

xlabel('Impurity Concentration, cm-3')

ylabel('Breakdown Voltage,V')

title('Breakdown Voltage vs. Impurity Concentration')

axis([1.0e14,1.0e17,0,2000])

text(2.0e14,270,'Ge')

text(3.0e14,1000,'Si')

Electrical system Simulation Lab(PED) SIETK-PUTTUR

SIMULATION OUTPUT:

RESULT:

Electrical system Simulation Lab(PED) SIETK-PUTTUR

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- GATE 2019 EE Answer Key & SolutionsDocument16 pagesGATE 2019 EE Answer Key & SolutionsChaitanya ThejaNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- PS Lab ManualDocument25 pagesPS Lab ManualPhani PhaniNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Electrical Machines IDocument16 pagesElectrical Machines Isuryaprakash001No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- GATE 2019 EE Answer Key & Solutions PDFDocument28 pagesGATE 2019 EE Answer Key & Solutions PDFSatyam SinghNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Ch10-Faraday's Law of InductionDocument32 pagesCh10-Faraday's Law of Inductionmehdii.heidary1366100% (3)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Vijaya Bank RecruitmentDocument22 pagesVijaya Bank RecruitmentTopRankersNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Advanced Digital Signal ProcessingDocument1 pageAdvanced Digital Signal ProcessingIbmWasuserNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Adhoc and Sensor NetworksDocument1 pageAdhoc and Sensor NetworksIbmWasuserNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Pesslabsietk PDFDocument30 pagesPesslabsietk PDFChaitanya ThejaNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Peesslabsietk2 PDFDocument29 pagesPeesslabsietk2 PDFChaitanya ThejaNo ratings yet

- Pesslabsietk PDFDocument30 pagesPesslabsietk PDFChaitanya ThejaNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Electrical Systems Simulation Laboratory Record: Department of Electrical & Electronics EngineeringDocument1 pageElectrical Systems Simulation Laboratory Record: Department of Electrical & Electronics EngineeringChaitanya ThejaNo ratings yet

- Instrument Operation ProcedureDocument2 pagesInstrument Operation ProcedureChaitanya ThejaNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- ResumeDocument2 pagesResumeChaitanya ThejaNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Homework Sheet 1Document2 pagesHomework Sheet 1Kjell adamsNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Fujitsu - ASIC/COT - 180nm CMOS Technology CS86 SeriesDocument2 pagesFujitsu - ASIC/COT - 180nm CMOS Technology CS86 SeriesFujitsu Semiconductor EuropeNo ratings yet

- Digital Integrated Circuits - A Design Perspective 2/e: Reference Chapter: 11Document3 pagesDigital Integrated Circuits - A Design Perspective 2/e: Reference Chapter: 11DarwinNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- 1988 Altera Data BookDocument260 pages1988 Altera Data Bookro100% (1)

- DLD Lab 1Document5 pagesDLD Lab 1tm tigerNo ratings yet

- Asynchronous CounterDocument5 pagesAsynchronous CounterJose GarciaNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Ht48r30a 1 PDFDocument43 pagesHt48r30a 1 PDFJohn GarnetNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Asayuki's Logic Comparator: WarningDocument9 pagesAsayuki's Logic Comparator: WarningindustronicaNo ratings yet

- Library Preparation LEF, DEF, GDSDocument51 pagesLibrary Preparation LEF, DEF, GDSROBI PAULNo ratings yet

- Assignment AsicDocument2 pagesAssignment AsicVijay Dhar MauryaNo ratings yet

- Digital MCQDocument19 pagesDigital MCQthesovereignmoonloveNo ratings yet

- Microprocessors and MicrocontrollersDocument22 pagesMicroprocessors and Microcontrollers6012 ANILNo ratings yet

- Am29BL162C: Data SheetDocument50 pagesAm29BL162C: Data SheetAndrey OliveiraNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Introduction To Flip-Flops: Experiment No. 12Document10 pagesIntroduction To Flip-Flops: Experiment No. 12Ramiz IqbalNo ratings yet

- Optical Disk Memory Storage DevicesDocument74 pagesOptical Disk Memory Storage DevicesM.WASEEM YOUSAF100% (2)

- Digital Design: Register-Transfer Level (RTL) DesignDocument88 pagesDigital Design: Register-Transfer Level (RTL) DesignmasrinaNo ratings yet

- BLX14 AdvancedSemiconductorDocument1 pageBLX14 AdvancedSemiconductorTeyfik koyuncuNo ratings yet

- Experiment 2 FinalDocument9 pagesExperiment 2 Finalliddleme33No ratings yet

- Computer AssignmentDocument4 pagesComputer AssignmentRichid1234No ratings yet

- 25LQ080B 016B 032BDocument74 pages25LQ080B 016B 032BAlfredo Valencia RodriguezNo ratings yet

- Lect28 2dff TFF JKFFDocument9 pagesLect28 2dff TFF JKFFpurwant10168No ratings yet

- 8255Document28 pages8255satyanarayana12No ratings yet

- 半導體製成Document2,148 pages半導體製成北科大-石秉宸No ratings yet

- M68 HC 05Document332 pagesM68 HC 05rullitoNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hamacher Ch7 MicroarchitectureDocument47 pagesHamacher Ch7 MicroarchitectureMILIND ADHAULYANo ratings yet

- Jif 316-PaDocument6 pagesJif 316-PaNur Hafizah RazaliNo ratings yet

- Eceg3202 - Computer Architecture and OrganizationDocument41 pagesEceg3202 - Computer Architecture and OrganizationAnonymous AFFiZnNo ratings yet

- STLD BitsDocument18 pagesSTLD BitsKornepati SureshNo ratings yet

- System Verilog For VHDL UsersDocument4 pagesSystem Verilog For VHDL UsersZakzouk ZakzoukNo ratings yet

- NGSPICE-Usage and Examples: Debapratim Ghosh Mohamed JabirDocument20 pagesNGSPICE-Usage and Examples: Debapratim Ghosh Mohamed JabirHARSH GARGNo ratings yet