Professional Documents

Culture Documents

Design Entry and Simulation of Sequential Circuits

Uploaded by

SriramCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design Entry and Simulation of Sequential Circuits

Uploaded by

SriramCopyright:

Available Formats

Expt No: Date:

DESIGN ENTRY AND SIMULATION OF SEQUENTIAL CIRCUITS

AIM:

To design and implement the following sequential circuits using Verilog HDL

and verify using the testbench

1. Counters

2. Finite State Machine

APPARATUS REQUIRED:

PC with Windows XP.

Xilinx 14.3

THEORY:

Counters

Synchronous counters are distinguished from asynchronous counters in that

clock pulses are applied to the CP inputs of all flip-flops. The common pulse triggers

all the flip-flops simultaneously, rather than one at a time in succession as in

asynchronous counter. The decision whether a flip-flop is to be complemented or not

is determined from the values of the J and K inputs at the time of the pulse. If J = K =

0, the flip-flop remains unchanged. If J = K = 1, the flip-flop complements. In a

synchronous binary ripple counter, the flip-flop in the lowest-order position is

complemented with very pulse. This means that it’s J and K inputs must be

maintained at logic-1. A flip-flop in any other position is complemented with a pulse

provided all the bits in the lower-order positions are equal to 1, because the lower-

order bits (when all 1’s) will change to 0’s on the next count pulse. The binary count

dictates the next higher-order bit is complemented. Synchronous binary counters

have a regular pattern and can easily be constructed with complementing flip-flops (

J K or T Type) and gates.

Finite State Machine

Designing a synchronous finite state machine (FSM) is a common task for a

digital logic engineer. A finite state machine can be divided in to two types: Moore

and Mealy state machines. The current state of the machine is stored in the state

memory, a set of n flip-flops clocked by a single clock signal (hence “synchronous”

state machine). The state vector (also current state, or just state) is the value currently

Page 1

stored by the state memory. The next state of the machine is a function of the state

vector in Moore; function of state vector and the inputs in Mealy.

PROCEDURE:

1. Start Xilinx ISE 14.3, click on “CREATE A NEW PROJECT” and then click on

Next.

2. Select your working directory, give the name of the project, then click on

“NEXT”.

3. Select the device family (Spartan 3E), Device (XC3S250E), package (PQ208),

Speed grade (4), Synthesis tool (XST [VHDL/VERILOG]), simulator (ISim) and

preferred language (Verilog) from the available device list, and then click

“NEXT” and click FINISH.

4. Write the HDL code and be careful to give the entity name the same as project

name.

5. In the design window change into simulation and double click behavioral

check syntax.

6. If the HDL code is error free a green check mark will be shown on the

behavioral check syntax.

7. Select simulation then double click on “Simulate Behavioral Model” (here we

can change the level of abstraction. i.e. structural/behavioral/dataflow/switch

level)

8. If there is zero error a new window will be shown. Apply the desired input as

1’s and 0’s and check whether the outputs are correct or not in the output

waveform.

9. Create a new verilog test fixture and give the various input constraints and

save the file and check if any errors are present.

10. Simulate the testbench and analyze the output waveform.

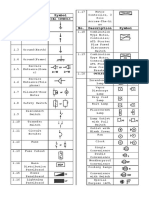

COUNTER

Logic Diagram:

CARE GROUP OF INSTITUTIONS

Page 2

Finite State Machine

State Diagram

Up Counter Design using Behavioral Down Counter Design using

Modelling Behavioral Modelling

module counter_up(out,clk,reset); module

output [3:0]out; counter_up_down(out,clk,reset);

input clk, reset; output [3:0]out;

reg [3:0] out; input clk, reset;

always @(negedge clk or posedge reset) reg [3:0] out;

if(reset) always @(negedge clk or posedge

out <=4'b0000; reset)

else if(reset)

out<=out+1; out <=4'b0000;

endmodule else

out<=out-1;

endmodule

Up/Down Counter Design using Mod-10 Counter Design

Behavioral Modelling module counter_ten(out,clk,reset);

module output [3:0]out;

counter_up_down(out,clk,reset,control); input clk, reset;

output [3:0]out; reg [3:0] out;

input clk, reset,control; always @(posedge clk or posedge

reg [3:0] out; reset)

always @(negedge clk or posedge reset) begin

if(reset) if(clk)

out <=4'b0000; if(reset)

CARE GROUP OF INSTITUTIONS

Page 3

else out <=4'b0000;

if (control) else

out<=out+1; if (out==4'b1001)

else out<=0;

out<=out-1; else

endmodule out<=out+1;

end

endmodule

Counter Design using Structural JK Flip-Flop Design using Behavioral

Modelling Modelling

module module jkff (q,qbar,j,k,clk,reset);

counter_strutural(q,qbar,clk,reset); output q,qbar;

output [3 : 0] q; input j,k,clk,reset;

output [3 : 0] qbar; reg q,qbar;

input clk,reset; always @ (negedge clk or reset)

wire [0 : 1] temp; if (~reset)

reg high; begin

initial q = 1'b0;

high = 1'b1; qbar = 1'b1;

jkff ff1 (q[0],qbar[0],high,high,clk,reset); end

jkff ff2 else if (reset)

(q[1],qbar[1],high,high,q[0],reset); begin

jkff ff3 if (j==0 && k ==0)

(q[2],qbar[2],high,high,q[1],reset); begin

jkff ff4 q = q;

(q[3],qbar[3],high,high,q[2],reset); qbar = qbar;

endmodule end

else if ( j== 0 && k ==1)

Counter Design using Behavioral begin

Modelling q = 1'b0;

qbar = 1'b1;

module counter(clk, reset,result); //,ena end

input clk, reset; else if (j==1 && k == 0)

output [3:0]result; begin

reg [3:0] result; q = 1'b1;

qbar = 1'b0;

always @(negedge clk or posedge end

reset) else if (j ==1 && k ==1)

begin begin

if (reset) q = ~q;

CARE GROUP OF INSTITUTIONS

Page 4

result = 0; qbar = ~qbar;

end

else else

result = result + 1; begin

end q = 1'bz;

endmodule qbar = 1'bz;

end

end

endmodule

FSM Design using Behavioral Modelling

module m1011( clk, rst, inp, outp);

input clk, rst, inp;

output outp;

reg [1:0] state;

reg outp;

always @( posedge clk, rst )

begin

if( rst )

state <= 2'b00;

else

begin

case( {state,inp} )

3'b000: begin

state <= 2'b00;

outp <= 0;

end

3'b001: begin

state <= 2'b01;

outp <= 0;

end

3'b010: begin

state <= 2'b10;

outp <= 0;

end

3'b011: begin

state <= 2'b01;

CARE GROUP OF INSTITUTIONS

Page 5

outp <= 0;

end

3'b100: begin

state <= 2'b00;

outp <= 0;

end

3'b101: begin

state <= 2'b11;

outp <= 0;

end

3'b110: begin

state <= 2'b10;

outp <= 0;

end

3'b111: begin

state <= 2'b01;

outp <= 1;

end

endcase

end

end

endmodule

RESULT:

The Sequential circuits were designed and, HDL codes were written and verified

using Testbench circuits

CARE GROUP OF INSTITUTIONS

Page 6

CARE GROUP OF INSTITUTIONS

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Timing issues in digital ASIC designDocument101 pagesTiming issues in digital ASIC designnsai_vs1513No ratings yet

- DFTC1 2007.12 StudentGuideDocument624 pagesDFTC1 2007.12 StudentGuideThi NguyenNo ratings yet

- DFT Interview QuestionsDocument3 pagesDFT Interview QuestionsJayesh PopatNo ratings yet

- Circuit Theory 2014 - Apr MayDocument6 pagesCircuit Theory 2014 - Apr MaySriramNo ratings yet

- MeasurementsDocument12 pagesMeasurementsSriramNo ratings yet

- 2014 - Apr May PDFDocument4 pages2014 - Apr May PDFSriramNo ratings yet

- EC8661 VLSI Design LaboratoryDocument53 pagesEC8661 VLSI Design LaboratorySriram100% (4)

- EC6612 - VLSI Design Laboratory ManualDocument39 pagesEC6612 - VLSI Design Laboratory ManualSriramNo ratings yet

- Sensors: SL - N o Application Sensor Example PriceDocument6 pagesSensors: SL - N o Application Sensor Example PriceSriramNo ratings yet

- Principles of Management: Lesson PlanDocument23 pagesPrinciples of Management: Lesson PlanSriram100% (1)

- Data Path Circuits - EC6601Document10 pagesData Path Circuits - EC6601SriramNo ratings yet

- Ec 6501Document1 pageEc 6501SriramNo ratings yet

- VLSI Design Lab EC-6612-nDocument58 pagesVLSI Design Lab EC-6612-nSriramNo ratings yet

- EC6702Document2 pagesEC6702SriramNo ratings yet

- What Determines The Color of An LED?: SemiconductingDocument1 pageWhat Determines The Color of An LED?: SemiconductingSriramNo ratings yet

- DSP WorkshopDocument2 pagesDSP WorkshopSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- ECE Department Course DetailsDocument151 pagesECE Department Course DetailsSriramNo ratings yet

- Analog DesignDocument4 pagesAnalog DesignSriramNo ratings yet

- Wireless Communication - EC 2401 - I - Answer KeyDocument9 pagesWireless Communication - EC 2401 - I - Answer KeySriramNo ratings yet

- Ec2357 - Vlsi Design LaboratoryDocument45 pagesEc2357 - Vlsi Design LaboratorySriramNo ratings yet

- Verilog Course ManualDocument60 pagesVerilog Course ManualSriramNo ratings yet

- Concept MapDocument18 pagesConcept MapSriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Kalasalingam University ECE302 Analog Communication Question BankDocument6 pagesKalasalingam University ECE302 Analog Communication Question BankSriramNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- SEMESTER Requirements Lab EquipmentDocument29 pagesSEMESTER Requirements Lab EquipmentSriramNo ratings yet

- Ece 2008Document27 pagesEce 2008SriramNo ratings yet

- Ece 2013Document14 pagesEce 2013SriramNo ratings yet

- Verilog Lab ProgramsDocument25 pagesVerilog Lab ProgramsSriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- PDFDocument38 pagesPDFप्रमोद म्हसेNo ratings yet

- Microchip PIC16F PIC16F882 Learning Centre MCU Application Notes Microchip - Application - Notes - 2Document16 pagesMicrochip PIC16F PIC16F882 Learning Centre MCU Application Notes Microchip - Application - Notes - 2tiago-macedoNo ratings yet

- Electrical network protection configuration for 2000KVA DG-1 generatorDocument30 pagesElectrical network protection configuration for 2000KVA DG-1 generatorKaruppasamy MariyappanNo ratings yet

- Digital Electronics 1-Sequential Circuit CountersDocument20 pagesDigital Electronics 1-Sequential Circuit CountersSatyam GuptaNo ratings yet

- 93L34 8-Bit Addressable Latch: General Description FeaturesDocument9 pages93L34 8-Bit Addressable Latch: General Description Featuresparvalhao_No ratings yet

- Waveshare Electronics: Technical SpecificationDocument20 pagesWaveshare Electronics: Technical SpecificationfirsttenorNo ratings yet

- KSZ8061 PDFDocument64 pagesKSZ8061 PDFsaberNo ratings yet

- Synchronous Sequential CircuitsDocument92 pagesSynchronous Sequential CircuitsDelphin ShibinNo ratings yet

- Rockwell Automation Library of Process Objects: Interlocks With First Out and Bypass (P - Intlk)Document34 pagesRockwell Automation Library of Process Objects: Interlocks With First Out and Bypass (P - Intlk)Brian McReynoldsNo ratings yet

- FC 62 - Remote Control Memory - ABB SolutionsBankDocument6 pagesFC 62 - Remote Control Memory - ABB SolutionsBankmohdthasthakirNo ratings yet

- CSC 204 - Final Study GuideDocument12 pagesCSC 204 - Final Study GuideFVCproductionsNo ratings yet

- MM53200 Encoder Decoder Application GuideDocument6 pagesMM53200 Encoder Decoder Application Guidekurtm22100% (1)

- C Mps 375 Class Notes Chap 03Document28 pagesC Mps 375 Class Notes Chap 03Mengistu KetemaNo ratings yet

- Digital ElectronicsDocument8 pagesDigital ElectronicsKali HungaNo ratings yet

- Ade Final Manual PDFDocument59 pagesAde Final Manual PDFRam Krishna JhaNo ratings yet

- Course Plan DLD-2020Document16 pagesCourse Plan DLD-2020Muhammad AsadNo ratings yet

- What Are The Various Registers in 8085Document9 pagesWhat Are The Various Registers in 8085kunalsekhri123100% (1)

- Electrical SymbolsDocument7 pagesElectrical SymbolsGia GalesNo ratings yet

- EE El 213 Digital Circuits and Systems Assignment 4Document3 pagesEE El 213 Digital Circuits and Systems Assignment 4Dhruv Paul100% (1)

- S.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021Document1 pageS.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021A.K. GamingNo ratings yet

- 888 Manual Ver1.06Document0 pages888 Manual Ver1.06Dota NgNo ratings yet

- PLTD Kairatu Incoming #2Document9 pagesPLTD Kairatu Incoming #2Densy Ojosh PattiasinaNo ratings yet

- Last Time Buy: 16-Bit Serial Input, Constant-Current Latched LED DriverDocument13 pagesLast Time Buy: 16-Bit Serial Input, Constant-Current Latched LED DriverDario Ochoa CoronelNo ratings yet

- Syllabus B.Sc-IT-3 Computer System Architecture and LabDocument3 pagesSyllabus B.Sc-IT-3 Computer System Architecture and LabArshpreet KaurNo ratings yet

- Gate CSE What To StudyDocument27 pagesGate CSE What To StudyNaveed TawargeriNo ratings yet

- DLD Chapter 6 Shifte Registers and CountersDocument82 pagesDLD Chapter 6 Shifte Registers and CountersLalisa RegassaNo ratings yet

- 8051 Beginners GuideDocument74 pages8051 Beginners GuideStorm LordNo ratings yet