Professional Documents

Culture Documents

PTFA181001E

Uploaded by

Dwp BhaskaranCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PTFA181001E

Uploaded by

Dwp BhaskaranCopyright:

Available Formats

PTFA181001E

PTFA181001F

Thermally-Enhanced High Power RF LDMOS FETs

100 W, 1805 – 1880 MHz

Description

The PTFA181001E and PTFA181001F are 100-watt LDMOS FETs PTFA181001E

designed for EDGE and WCDMA power amplifier applications in the Package H-36248-2

DCS band. Features include input and output matching, and

thermally-enhanced packages with slotted or earless flanges.

Manufactured with Infineon's advanced LDMOS process, these

devices provide excellent thermal performance and superior PTFA181001F

reliability. Package H-37248-2

Features

2-Carrier WCDMA Drive-up

VDD = 28 V, IDQ = 750 mA, ƒ = 1880 MHz, 3GPP WCDMA • Thermally-enhanced packages

signal, P/A R = 8 dB, 10 MHz carrier spacing • Broadband internal matching

• Typical EDGE performance at 1879.8 MHz, 28 V

-23 35

- Average output power = 45 W

Efficiency - Linear Gain = 16.5 dB

-28 30

IM3 (dBc), ACPR (dBc)

- Efficiency = 36%

Drain Efficiency (%)

- EVM RMS = 1.8%

-33 25

IM3 • Typical CW performance, 1880 MHz, 28 V

-38 20 - Output power at P–1dB = 120 W

- Gain 15.5 dB

-43 15 - Efficiency = 52%

• Integrated ESD protection: Human Body Model,

-48 10 Class 2 (minimum)

ACPR

• Excellent thermal stability, low HCI drift

-53 5

34 36 38 40 42 44 46 • Capable of handling 10:1 VSWR @ 28 V,

100 W (CW) output power

Average Output Power (dBm)

• Pb-free and RoHS compliant

RF Characteristics

EDGE Measurements (not subject to production test—verified by design/characterization in Infineon test fixture)

VDD = 28 V, IDQ = 750 mA, POUT = 45 W, ƒ = 1879.8 MHz

Characteristic Symbol Min Typ Max Unit

Error Vector Magnitude RMS EVM — 1.8 — %

Modulation Spectrum @ 400 KHz ACPR — –61 — dBc

Modulation Spectrum @ 600 KHz ACPR — –73 — dBc

Gain Gps — 16.5 — dB

Drain Efficiency ηD — 36 — %

All published data at TCASE = 25°C unless otherwise indicated *See Infineon distributor for future availability.

ESD: Electrostatic discharge sensitive device—observe handling precautions!

Data Sheet 1 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

RF Characteristics (cont.)

Two-tone Measurements (tested in Infineon test fixture)

VDD = 28 V, IDQ = 750 mA, POUT = 100 W PEP, ƒ = 1850 MHz, tone spacing = 1 MHz

Characteristic Symbol Min Typ Max Unit

Gain Gps 16 16.5 — dB

Drain Efficiency ηD 39 41 — %

Intermodulation Distortion IMD — –30 –28 dBc

DC Characteristics

Characteristic Conditions Symbol Min Typ Max Unit

Drain-Source Breakdown Voltage VGS = 0 V, IDS = 10 mA V(BR)DSS 65 — — V

Drain Leakage Current VDS = 28 V, V GS = 0 V IDSS — — 1.0 µA

VDS = 63 V, V GS = 0 V IDSS — — 10.0 µA

On-State Resistance VGS = 10 V, V DS = 0.1 V RDS(on) — 0.85 — Ω

Operating Gate Voltage VDS = 28 V, ID = 750 mA VGS 2.0 2.5 3.0 V

Gate Leakage Current VGS = 10 V, V DS = 0 V IGSS — — 1.0 µA

Maximum Ratings

Parameter Symbol Value Unit

Drain-Source Voltage VDSS 65 V

Gate-Source Voltage VGS –0.5 to +12 V

Junction Temperature TJ 200 °C

Total Device Dissipation PD 407 W

Above 25°C derate by 2.33 W/°C

Storage Temperature Range TSTG –40 to +150 °C

Thermal Resistance (TCASE = 70°C, 100 W CW) RθJC 0.43 °C/W

Ordering Information

Type and Version Package Type Package Description Marking

PTFA181001E V4 H-36248-2 Thermally-enhanced slotted flange, single-ended PTFA181001E

PTFA181001F V4 H-37248-2 Thermally-enhanced earless flange, single-ended PTFA181001F

*See Infineon distributor for future availability.

Data Sheet 2 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Typical Performance (data taken in a production test fixture)

Edge EVM and Modulation Spectrum EDGE Modulation Spectrum Performance

vs. Quiescent Current VDD = 28 V, IDQ = 750 mA, ƒ = 1879.8 MHz

VDD = 28 V, ƒ = 1879.8 MHz, POUT = 46.5 dBm

2.6 -10 -20 45

Efficiency

Modulation Spectrum (dBc)

2.4 -20

Modulation Spectrum (dBc)

EVM -40 35

Drain Efficiency (%)

EVM RMS (avg. %) .

2.2 -30

2.0 -40

400 kHz

1.8 -50 -60 25

1.6 -60

400 kHz

1.4 -70 -80 600 kHz 15

1.2 600 kHz -80

1.0 -90 -100 5

0.65 0.70 0.75 0.80 0.85 0.90 37 39 41 43 45 47 49

Quiescent Current (A) Output Power (dBm)

EDGE EVM Performance Intermodulation Distortion vs. Output Power

VDD = 28 V, IDQ = 750 mA, ƒ = 1879.8 MHz (as measured in a broadband circuit)

VDD = 28 V, IDQ = 750 mA, ƒ1 = 1879 MHz, ƒ2 = 1880 MHz

8 45 -20

3rd Order

Efficiency -25

-30

EVM RMS (avg. %) .

Drain Efficiency (%)

6 35

-35

IMD (dBc)

-40 5th

4 25

-45

-50

2 15 7th

-55

EVM

-60

0 5 -65

37 39 41 43 45 47 49 37 39 41 43 45 47 49

Output Power (dBm) Output Power, Avg. (dBm)

Data Sheet 3 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Typical Performance (cont.)

Broadband CW Performance (at P-1dB)

IM3 vs. Output Power at Selected Biases

VDD = 28 V, IDQ = 750 mA

VDD = 28 V, ƒ1 = 1879, ƒ2 = 1880 MHz

19 60 -20

Efficiency (%), Output Power (dBm)

-25

18 Efficiency 55

-30 IDQ = 375 mA

-35

IMD (dBc)

17 50

Gain (dB)

Output Power

-40 IDQ = 1125 mA

16 45

-45

Gain

-50

15 40

-55 IDQ = 750 mA

14 35 -60

1805 1818 1831 1844 1857 1870 1883 37 39 41 43 45 47 49

Frequency (MHz)

Output Power, Avg. (dBm)

Linear Broadband Performance Power Sweep

VDD = 28 V, IDQ = 750 mA, POUT Avg = 47 dBm VDD = 28 V, ƒ = 1880 MHz

55 40 17.5

IDQ = 1125 mA

50 30 17.0

Gain, Return Loss (dB)

Gain

16.5

Power Gain (dB)

45 20 IDQ = 750 mA

Efficiency (%)

40 10 16.0

Efficiency

35 0 15.5

Return Loss

30 -10 15.0

IDQ = 375 mA

25 -20 14.5

20 -30 14.0

1805 1818 1831 1844 1857 1870 1883 36 38 40 42 44 46 48 50 52

Frequency (MHz) Output Power (dBm)

Data Sheet 4 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Typical Performance (cont.)

Gain & Efficiency vs. Output Power Output Power (P–1dB) vs. Drain Voltage

VDD = 28 V, IDQ = 750 mA, ƒ = 1880 MHz IDQ = 750 mA, ƒ = 1880 MHz

18 65 52

17 55

Gain

Drain Efficiency (%)

Output Power (dBm)

16 45 51

Gain (dB)

15 35

14 25 50

Efficiency

13 15

12 5 49

36 38 40 42 44 46 48 50 52 24 26 28 30 32

Drain Voltage (V)

Output Power (dBm)

IS-95 CDMA Performance Bias Voltage vs. Temperature

VDD = 28 V, IDQ = 750 mA, ƒ = 1880 MHz Voltage normalized to typical gate voltage,

series show current

TCASE = 25°C

35 -10 1.03 0.15 A

TCASE = 90°C

Efficiency

Normalized Bias Voltage (V)

30 -20 1.02 0.44 A

Adj. Ch. Power Ratio (dBc)

1.01 0.73 A

Drain Efficiency (%)

25 -30

1.10 A

ACP FC – 0.75 MHz 1.00

20 -40 2.20 A

0.99

15 -50 3.30 A

0.98 4.41 A

10 -60

0.97 5.51 A

5 ACPR FC + 1.98 MHz -70 0.96

0 -80 0.95

33 35 37 39 41 43 45 47 -20 0 20 40 60 80 100

Output Power, Avg. (dBm) Case Temperature (°C)

Data Sheet 5 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Typical Performance (cont.)

Three-Carrier CDMA2000 Performance

VDD = 28 V, IDQ = 750 mA, ƒ = 1880 MHz

40 -35

35 -40

Adj. Ch. Power Ratio (dBc)

Drain Efficiency (%)

30 -45

25 Efficiency -50

20 -55

ACP Up

15 -60

10 ALT Up -65

5 -70

ACP Low

0 -75

33 35 37 39 41 43 45 47

Output Power, Avg. (dBm)

Broadband Circuit Impedance

R

E NE

Z0 = 50 Ω

RD G

D

Z Source Z Load

A

S T OW

0 .1

Z Load

1880 MHz

- WAV E LE NGT H

G 1805 MHz

S

0.0

0.1

D-

TOW ARD LOA

Frequency Z Source Ω Z Load Ω

Z Source

MHz R jX R jX

1805 MHz

1805 4.62 –6.23 1.71 2.79

GTHS

1830 4.18 –6.10 1.41 2.92 0. 1

1880 MHz

E N

1850 4.20 –6.13 1.47 3.05

VE L

1860 4.58 –6.20 1.99 3.13

WA

1880 4.42 –6.36 1.91 3.16

<---

Data Sheet 6 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

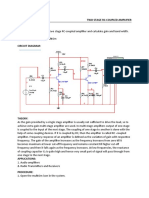

Reference Circuit

C1

0.001µF

R2 R1

1.3K V 1.2K V

QQ1

LM7805

Q1 VDD

BCP56

C2

C3

0.001µF

0.001µF

R3 R4

2K V 2K V

R5

10 V R6 R8 L1

5.1K V 2K V

V DD

C4 C5 R7 C6 C7 C8 C11 C12 C13 C14 C15

10µF 0.1µF 5.1K V 1µF 0.01µF 10pF l5 1µF 10pF 1µF 10µF 10µF

35V 50V 50V

R9

10 V

l8

l4

C9 C21 C24

10pF DUT 1.5pF 10pF

R F_IN l1 l2 l3 l6 l7 l10 l11 l12 l13 l14 l15 RF_OUT

C10 C22 C23

0.6pF 1.5pF 0.6pF

l9

L2

a181001ef_sch_06-04-18

C19

C16 C17 C18 10µF C20

1µF 10pF 1µF 50V 10µF

50V

Reference circuit schematic for ƒ = 1880 MHz

Circuit Assembly Information

DUT PTFA181001E or PTFA181001F LDMOS Transistor

PCB 0.76 mm [.030"] thick, εr = 4.5 Rogers TMM4 2 oz. copper

Microstrip Electrical Characteristics at 1880 MHz1 Dimensions: L x W (mm) Dimensions: L x W (in.)

l1 0.314 λ, 50.0 Ω 27.43 x 1.37 1.080 x 0.054

l2 0.172 λ, 38.0 Ω 14.73 x 2.16 0.580 x 0.085

l3 0.016 λ, 11.4 Ω 1.27 x 10.16 0.050 x 0.400

l4 0.024 λ, 60.0 Ω 2.24 x 0.99 0.088 x 0.039

l5 0.218 λ, 60.0 Ω 19.33 x 0.99 0.761 x 0.039

l6 0.019 λ, 6.9 Ω 1.52 x 17.78 0.060 x 0.700

l7 0.044 λ, 6.9 Ω 3.43 x 17.78 0.135 x 0.700

l8, l9 0.233 λ, 53.0 Ω 20.45 x 1.24 0.805 x 0.049

l10 0.039 λ, 4.9 Ω 3.10 x 25.65 0.122 x 1.010

l11 (taper) 0.037 λ, 4.9 Ω / 10.3 Ω 2.92 x 25.65 / 11.43 0.115 x 1.010 / 0.450

l12 (taper) 0.033 λ, 10.3 Ω / 41.0 Ω 2.79 x 11.43 / 1.91 0.110 x 0.450 / 0.075

l13 0.069 λ, 41.0 Ω 6.35 x 1.91 0.250 x 0.075

l14 0.038 λ, 41.0 Ω 3.25 x 1.91 0.128 x 0.075

l15 0.331 λ, 50.0 Ω 28.98 x 1.37 1.141 x 0.054

1Electrical characteristics are rounded.

Data Sheet 7 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Reference Circuit (cont.)

QQ1

R3 C1 VDD

R5 R4 C3

R3 QQ1 VDD C5

R5

C1

C4 R1 C2

R4 C3 R6 R2

C5 C2

C4 R1

R6 R2

VDD

Q1

L1

Q1

C6 C6

R7 C10 C11

C12 R7

C8

C7 C13 C8

C21 C14 C15 C7

R8 R9 C23

C9 a181001ef_dtl

R8

C24

C22 C19 C20

C18

C16

C17

VDD

A181001_01

L2

a181001ef_assy

Reference circuit assembly diagram (not to scale)

Component Description Suggested Manufacturer P/N or Comment

C1, C2, C3 Capacitor, 0.001 µF Digi-Key PCC1772CT-ND

C4 Tantalum capacitor, 10 µF, 35 V Digi-Key 399-1655-2-ND

C5 Capacitor, 0.1 µF Digi-Key PCC104BCT-ND

C6, C11, C13, C16, C18 Capacitor, 1.0 µF ATC 920C105

C7 Capacitor, 0.01 µF ATC 200B 103

C8, C9, C12, C17, C24 Ceramic capacitor, 10 pF ATC 100B 100

C10, C23 Ceramic capacitor, 0.6 pF ATC 100B 0R6

C14, C15, C19, C20 Tantalum capacitor, 10 µF, 50 V Garrett Electronics TPSE106K050R0400

C21, C22 Ceramic capacitor, 1.5 pF ATC 100B 1R5

L1, L2 Ferrite, 8.9 mm Elna Magnetics BDS 4.6/3/8.9-4S2

Q1 Transistor Infineon Technologies BCP56

QQ1 Voltage regulator National Semiconductor LM7805

R1 Chip Resistor 1.2 k-ohms Digi-Key P1.2KGCT-ND

R2 Chip Resistor 1.3 k-ohms Digi-Key P1.3KGCT-ND

R3, R8 Chip Resistor 2 k-ohms Digi-Key P2KECT-ND

R4 Potentiometer 2 k-ohms Digi-Key 3224W-202ETR-ND

R5, R9 Chip Resistor 10 ohms Digi-Key P10ECT-ND

R6, R7 Chip Resistor 5.1 k-ohms Digi-Key P5.1KECT-ND

Gerber files for this circuit available on request

Data Sheet 8 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Package Outline Specifications

Package H-36248-2

(45° X 2.72

CL

[.107])

4.83±0.51

D [.190±.020]

S

FLANGE 9.78

[.385] LID 9.40 +0.10 C

L

–0.15

19.43 ±0.51 [.370 +.004

–.006 ]

[.765±.020]

2X R1.63

G [R.064]

4X R1.52

[R.060]

2X 12.70

[.500]

27.94

[1.100]

19.81±0.20

[.780±.008] SPH 1.57

1.02 C

L [.062]

[.040]

3.61±0.38

[.142±.015]

0.0381 [.0015] -A-

34.04

0 7 1 1 1 7 _ h -3 6 2 4 8 -2 _ p o

[1.340]

Diagram Notes—unless otherwise specified:

1. Lead thickness: 0.10 +0.051/–0.025 [.004 +.002/–.001].

2. All tolerances ± 0.127 [.005] unless specified otherwise.

3. Pins: D = drain, S = source, G = gate.

4. Interpret dimensions and tolerances per ASME Y14.5M-1994.

5. Primary dimensions are mm. Alternate dimensions are inches.

6. Gold plating thickness:

S, D, G - flange & leads: 1.14 ± 0.38 micron [45 ± 15 microinch]

Find the latest and most complete information about products and packaging at the Infineon Internet page

http://www.infineon.com/products

Data Sheet 9 of 11 Rev. 02.1, 2009-02-20

PTFA181001E

PTFA181001F

Package Outline Specifications (cont.)

Package H-37248-2

( 45° X 2.72 CL

[.107])

4.83±0.51

[.190±.020] D

+0.10

LID 9.40 –0.15 19.43±0.51

[.765±.020]

[.370+.004

–.006 ] C

L

FLANGE 9.78

[.385]

G

4X R0.508+0.381

–0.127

[R.020+.015

– .005]

2X 12.70

[.500]

19.81±0.20

[.780±.008]

C

L

SPH 1.57

[.062] 1.02

[.040]

0.0381 [.0015] -A-

S

0 7 1 1 1 7 _ h -3 7 2 4 8 -2 _ p o

3.61±0.38 20.57

[.142±.015] [.810]

Diagram Notes—unless otherwise specified:

1. Lead thickness: 0.10 +0.051/–0.025 [.004 +.002/–.001].

2. All tolerances ± 0.127 [.005] unless specified otherwise.

3. Pins: D = drain, S = source, G = gate.

4. Interpret dimensions and tolerances per ASME Y14.5M-1994.

5. Primary dimensions are mm. Alternate dimensions are inches.

6. Gold plating thickness:

S, D, G - flange & leads: 1.14 ± 0.38 micron [45 ± 15 microinch]

Find the latest and most complete information about products and packaging at the Infineon Internet page

http://www.infineon.com/products

Data Sheet 10 of 11 Rev. 02.1, 2009-02-20

PTFA181001E/F

Confidential, Limited Internal Distribution

Revision History: 2009-02-20 Data Sheet

Previous Version: 2006-04-14, Data Sheet

Page Subjects (major changes since last revision)

1, 2, 9, 10 Update to product V4, with new package technologies. Update package outline diagrams.

8 Fixed typing error

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

highpowerRF@infineon.com

To request other information, contact us at:

+1 877 465 3667 (1-877-GO-LDMOS) USA

or +1 408 776 0600 International

GOLDMOS® is a registered trademark of Infineon Technologies AG.

Edition 2009-02-20

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2009 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of

any third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest

Infineon Technologies Office (www.infineon.com/rfpower).

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in

question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of

that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices

or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect

human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Data Sheet 11 of 11 Rev. 02.1, 2009-02-20

You might also like

- PSMN165-200K: 1. DescriptionDocument13 pagesPSMN165-200K: 1. DescriptionDwp BhaskaranNo ratings yet

- Mpc8323eec PDFDocument82 pagesMpc8323eec PDFDwp BhaskaranNo ratings yet

- MAX923 (Dual-Supply Comparators) PDFDocument17 pagesMAX923 (Dual-Supply Comparators) PDFDwp BhaskaranNo ratings yet

- Max 5051Document22 pagesMax 5051Dwp BhaskaranNo ratings yet

- MAX682ESADocument12 pagesMAX682ESADwp BhaskaranNo ratings yet

- MAX942ESADocument12 pagesMAX942ESADwp BhaskaranNo ratings yet

- Adrk (Max8515a)Document10 pagesAdrk (Max8515a)Dwp BhaskaranNo ratings yet

- Max5048aaut (Abwf)Document11 pagesMax5048aaut (Abwf)Dwp BhaskaranNo ratings yet

- AGQ100 Series: 100 WattsDocument4 pagesAGQ100 Series: 100 WattsDwp BhaskaranNo ratings yet

- Max 5051Document22 pagesMax 5051Dwp BhaskaranNo ratings yet

- Il207a PDFDocument8 pagesIl207a PDFDwp BhaskaranNo ratings yet

- Hmc349lp4c (h349 Ic - FRGB)Document6 pagesHmc349lp4c (h349 Ic - FRGB)Dwp BhaskaranNo ratings yet

- Tps40057 Data SheetDocument41 pagesTps40057 Data SheetDwp BhaskaranNo ratings yet

- LCX257 - 2 Input MultiplexerDocument8 pagesLCX257 - 2 Input MultiplexerDwp BhaskaranNo ratings yet

- Adrk (Max8515a)Document10 pagesAdrk (Max8515a)Dwp BhaskaranNo ratings yet

- Max5048aaut (Abwf)Document11 pagesMax5048aaut (Abwf)Dwp BhaskaranNo ratings yet

- LP2996Document21 pagesLP2996Dwp BhaskaranNo ratings yet

- Atmel 2486 8 Bit Avr Microcontroller Atmega8 L DatasheetDocument331 pagesAtmel 2486 8 Bit Avr Microcontroller Atmega8 L DatasheetRolando IrrazabalNo ratings yet

- 24C02BN Su18Document26 pages24C02BN Su18Dwp BhaskaranNo ratings yet

- MAX923 (Dual-Supply Comparators) PDFDocument17 pagesMAX923 (Dual-Supply Comparators) PDFDwp BhaskaranNo ratings yet

- Cdcvf25081 (Ck081 Ic) - IfxDocument18 pagesCdcvf25081 (Ck081 Ic) - IfxDwp BhaskaranNo ratings yet

- 3.3V Octal Buffer/line Driver With 30 Series Termination Resistors (3-State)Document11 pages3.3V Octal Buffer/line Driver With 30 Series Termination Resistors (3-State)Dwp BhaskaranNo ratings yet

- cdcvf2310 (CKV2310)Document23 pagescdcvf2310 (CKV2310)Dwp BhaskaranNo ratings yet

- B78417A1698A003 - EPCOS 1698 CoilDocument3 pagesB78417A1698A003 - EPCOS 1698 CoilDwp BhaskaranNo ratings yet

- Dm74als244awm - Bus DriverDocument6 pagesDm74als244awm - Bus DriverDwp BhaskaranNo ratings yet

- 8751 ProgrammingDocument16 pages8751 ProgrammingDwp BhaskaranNo ratings yet

- Datasheet 80C85 (Oki)Document29 pagesDatasheet 80C85 (Oki)José AdelinoNo ratings yet

- 74lvc1g08w (Ve-5pin Ic)Document15 pages74lvc1g08w (Ve-5pin Ic)Dwp BhaskaranNo ratings yet

- MSM81C55 5JSDocument20 pagesMSM81C55 5JSThanhha NguyenNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- EEE-354: Telecommunication Systems EngineeringDocument35 pagesEEE-354: Telecommunication Systems EngineeringBilal HabibNo ratings yet

- Ch12 BluetoothDocument30 pagesCh12 BluetoothTruong van TruongNo ratings yet

- Zte Lte FDD DL Mimo Feature GuideDocument63 pagesZte Lte FDD DL Mimo Feature GuideMuhammad Asim Arshad100% (2)

- IC-9700 AdvancedManual ENG 0Document173 pagesIC-9700 AdvancedManual ENG 0Lori McConnellNo ratings yet

- HCIP-LTE-RNP - RNO V1.0 Exam OutlineDocument6 pagesHCIP-LTE-RNP - RNO V1.0 Exam OutlineSemirNo ratings yet

- CDMA Overview & BSNL PlansDocument39 pagesCDMA Overview & BSNL PlansAkash AnjanNo ratings yet

- Handoff ManagementDocument11 pagesHandoff ManagementsabitavabiNo ratings yet

- Chapter 3 Solutions: Network+ Guide To Networks, 4 EditionDocument3 pagesChapter 3 Solutions: Network+ Guide To Networks, 4 EditionEmperorBaconNo ratings yet

- CODA - LINUS DSP & Amplification FINALDocument18 pagesCODA - LINUS DSP & Amplification FINALJaime Cataño GarciaNo ratings yet

- DigiMax 96k (OM)Document22 pagesDigiMax 96k (OM)Carlos SantamaríaNo ratings yet

- Datasheet Flatpack S 48V Rectifiers PDFDocument2 pagesDatasheet Flatpack S 48V Rectifiers PDFMalkiel Callisthenes DarjaNo ratings yet

- Addis Ababa Science AND Technology University: College of Electrical & Mechanical EngineeringDocument9 pagesAddis Ababa Science AND Technology University: College of Electrical & Mechanical EngineeringHuluNo ratings yet

- Career FileDocument2 pagesCareer FileSuriani SallehNo ratings yet

- Scala Rider Q1 Owner ManualDocument16 pagesScala Rider Q1 Owner ManualFabio GalloNo ratings yet

- TCP in Wireless DomainDocument30 pagesTCP in Wireless DomainMurugan Antham RNo ratings yet

- Public Switched Telephone Network (PSTN)Document4 pagesPublic Switched Telephone Network (PSTN)Syed Zulfiqar Haider BukhariNo ratings yet

- Annex 4 - Delivery Format - Task 3Document14 pagesAnnex 4 - Delivery Format - Task 3carlosNo ratings yet

- Antenna and Wave Propagation - G. S. N. Raju PDFDocument95 pagesAntenna and Wave Propagation - G. S. N. Raju PDFY Shak KmNo ratings yet

- Introduction To Cellular Mobile Radio SystemsDocument83 pagesIntroduction To Cellular Mobile Radio SystemsBhavana GayatriNo ratings yet

- Minilink CN R2 SpesificationsDocument2 pagesMinilink CN R2 SpesificationsAjun Wicaksono0% (1)

- SX20CDocument1 pageSX20Cyu3zaNo ratings yet

- Application Note: Docsis 3.1Document24 pagesApplication Note: Docsis 3.1Bernard Mkumbwa Jr.No ratings yet

- ATSC 8-VSB Demodulator and Decoder TDA8960: Philips Semiconductors Preliminary SpecificationDocument2 pagesATSC 8-VSB Demodulator and Decoder TDA8960: Philips Semiconductors Preliminary SpecificationabbasdfNo ratings yet

- BDA C3000 (5018375) - PRINT - PDF Release 1.0: Downloaded From Manuals Search EngineDocument8 pagesBDA C3000 (5018375) - PRINT - PDF Release 1.0: Downloaded From Manuals Search EngineAbdalhakeem Al turkyNo ratings yet

- Lucent Cdma ViewDocument192 pagesLucent Cdma ViewkumarvivekguptaNo ratings yet

- PX10 / PX8 / PX5 / PX3: Power AmplifierDocument2 pagesPX10 / PX8 / PX5 / PX3: Power AmplifierRajuNo ratings yet

- TWO STAGE RC Coupled AmplifierDocument3 pagesTWO STAGE RC Coupled Amplifierfarzana kousar100% (1)

- Microgrid Communications - Protocols and Standards: July 2019Document37 pagesMicrogrid Communications - Protocols and Standards: July 2019Daniel Felipe Losada RamosNo ratings yet

- v1 Block CalibrationDocument57 pagesv1 Block Calibrationravindra_jivani100% (3)

- Signals and System MCQDocument5 pagesSignals and System MCQVvek0% (1)