Professional Documents

Culture Documents

EC6612 - VLSI Design Laboratory Manual

Uploaded by

SriramCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EC6612 - VLSI Design Laboratory Manual

Uploaded by

SriramCopyright:

Available Formats

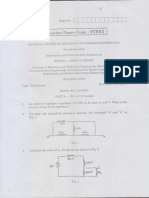

CARE GROUP OF INSTITUTIONS

EC6612

VLSI DESIGN LABORATORY

Page 1

EC6612 VLSI Design Laboratory

LIST OF EXPERIMENTS

1. Design of Adder (8-bit) and Multiplier (4-bit) and Simulate.

2. Design of simple counter and FSM and Simulate.

3. To Synthesis, P&R and post P&R simulation of the components simulation of

counter and find Critical paths and static timing analysis results to be

identified

4. Implementation of the Hardware device by using Chip Scope Pro

IC Design Experiments – CADENCE tool

5. Design of simple Differential amplifier, calculate gain and CMRR

6. Layout generation, parasitic Extraction and post layout Simulation

7. Synthesis and Simulate the counter and find Identification of critical

paths, power consumption.

8. Floor plan, Power plan, routing, placement, Static timing analysis(STA) and

Critical path for counter

CARE GROUP OF INSTITUTIONS

Page 2

Expt. No: Date:

STUDY OF VERILOG HDL AND SPARTAN-3E FPGA BOARD

AIM:

To study Verilog HDL, Spartan-3E FPGA board and the related software.

SOFTWARE USED:

Xilinx 14.3

DEVICE USED:

Spartan-3E FPGA 250S

THEORY:

INTRODUCTION TO VERILOG HDL:

Verilog HDL is one of the Hardware Description Languages (HDL) used to

describe a digital system. VHDL is the other one. Verilog HDL allows a hardware

designer to describe designs at a high level of abstraction such as an the architectural

or behavioral level as a set of modules. Modules can either be specified behaviorally

or structurally (for a combination of two). A behavioral specification defines the

behavior of a digital system (module) using traditional programming language

constructs. E.g. if assignment statements. A structural specification expresses the

behavior of a digital system (module) as a hierarchical interconnection of sub

modules. At the bottom of the hierarchy the components must be primitives or

specified behaviorally. Verilog provides the following gate level primitives:

And/nand - logical AND/NAND

or/nor - logical OR/NOR

xor/xnor - logical XOR/XNOR

buf/not - buffer/inverter

bufif0/notif0 - tristate with low enable

bufif1/notif1 - tristate with high enable

The structure of a module is the following:

Module <module name> (<port list>);

<(declares)>

<module items>

End module.

CARE GROUP OF INSTITUTIONS

Page 3

The <module name> is an identifier that uniquely names the module. The <port list>

is a list of input, in-out and output ports which are used to connect to other modules.

The <declares> section specifies data objects as registers, memories and wires as well

as procedural constructs such as functions and tasks. The <module items> may be

initial constructs, always constructs, continuous assignments or instances of

modules.

OPERATORS:

Bitwise operators: ~(not), &(and), |(or) and ^(xor)

Arithmetic: +, -, *, /

Unary reduction: &, &&, |, ~|, ^, ~ ^

Logical: !, &&, ||

Equality: ==, != (0,1)

Identity: ===, !== (0,1,x,z)

Relational: <,>,<=,>=

Logical shift : <<, >>

Conditional: ?:

Concatenate: {}

Replicate: {{}}

DESIGN FLOW:

DESIGN ENTRY: The designed circuit is specified either by means of a schematic

diagram or by using a hardware description language, such as Verilog or VHDL.

SYNTHESIS: The entered design is synthesized into a circuit that consists of the

logic elements (LE’s) provided in the FPGA board.

FUNCTIONAL SIMULATION: The synthesized circuit is tested to verify it’s

functional correctness. This simulation does not take into account any timing issues.

A test bench is HDL code that allows you to provide a repeatable set of stimuli with

clock and input dat for

error checking, file input and output and conditional testing.

FITTING: The CAD filter told determines the placement of LE’s defined in the

netlist into the LE’s in the actual FPGA chip. It also chooses routing wires in the chip

to make the required connections between specific LE’s.

TIMING ANALYSIS: Propagation delays along the various paths in the fitted

circuit are analyzed to provide an indication of the expected performance of the

circuit.

CARE GROUP OF INSTITUTIONS

Page 4

TIMING SIMULATION: The fitted circuit is tested to verify both its functional

correctness and timing.

PROGRAMMING AND CONFIGURATION: The designed circuit is implemented

in a physical FPGA chip by programming the configuration switches that configure

the LE’s and established the required wiring connections.

Fig. Flow chart of VLSI design flow

PROCEDURE OF XILINX 14.3 SOFTWARE:

1. Start Xilinx ISE 13.1, click on “CREATE A NEW PROJECT” and then click on

Next.

2. Select you’re working directory, give the name of the project, then click on

“NEXT”.

3. Select the device family (Spartan 3E), Device (XC3S250E), package (PQ208),

Speed grade (4), Synthesis tool (XST [VHDL/VERILOG]), simulator (ISim) and

preferred language (Verilog) from the available device list, and then click

“NEXT” and click FINISH.

CARE GROUP OF INSTITUTIONS

Page 5

4. Write the HDL code and be careful to give the entity name the same as project

name. After writing the code save the file and click on “Synthesis XST”.

5. If the HDL code is error free a green check mark will be shown on the

synthesis XST.

6. Select simulation then double click on “Simulate Behavioral Model” (here we

can change the level of abstraction. i.e. structural/behavioral/dataflow/switch

level)

7. If there is zero error a new window will be shown. Apply the desired input as

1’s and 0’s and check whether the outputs are correct or not in the output

waveform.

8. Expand the user constraints n the processes for source window and double

click “Assign package pins” (with ISE 13.1 web pack is called I/O floor plan

presynthesis). This is where you tell Xilinx which pins on Spartan 3E will be

used.

9. In the “Design object list I/O pins window type the pin numbers in the

following pin assignments under the heading LOC”. This action will create a

.UCF file for the top_level_struct file and will contain the pin assignments for

the Spartan-3E.

10. Make sure that the top_level_struct file is selected in the sources window.

11. Expand the Synthesis-XST in the Processes window and then double click it.

This action will check the syntax of the source code for top_level_struct and

convert the source code into a netlist of gates. A synthesis report will also be

produced. When the synthesis is finished, green check marks should be

displayed indicating that top_level_struct has compiled successfully.

12. Expand the “Implement design” process and double click on it. This is where

the netlist is translated, mapped, placed and routed for the logic circuits of the

Spartan-3E FPGA. After this process has been run, green check mark should

be displayed.

13. Expand the “Generate Programming file” process and double click it. This

process creates

A bit file that is used to program the Spartan-3E chip. Again, after this process

is finished, green check mark should be shown.

14. Expand the “Implement design” and double click on “Generate programming

file”.

15. Right click on the depiction of the Spartan-3E chip and select program. If the

download was successful, the message “Program succeeded” will be

displayed.

RESULT:

The verilog modelling methodology and Spartan 3E FPGA board were studied.

CARE GROUP OF INSTITUTIONS

Page 6

Expt. No: Date:

DESIGN ENTRY AND SIMULATION OF COMBINATIONAL CIRCUITS

AIM:

To design and implement the following combinational circuits using Verilog HDL

and simulate,

1. 8 bit adders,

2. 4 bit multipliers,

APPARATUS REQUIRED:

PC with Windows XP.

XILINX 14.3.

THEORY:

8-Bit Addition (Ripple Carry Adder)

The n-bit adder built from n one –bit full adders is known as ripple carry

adder because of the carry is computed. The addition is not complete until n-1th

adder has computed its Sn-1 output; that results depends upon ci input, n and so on

down the line, so the critical delay path goes from the 0-bit inputs up through ci’s to

the n-1 bit.(We can find the critical path through the n-bit adder without knowing

the exact logic in the full adder because the delay through the n-bit adder without

knowing the exact logic in the full adder because the delay through the n-bit carry

chain is so much longer than the delay from a and b to s). The ripple-carry adder is

area efficient and easy to design but it is when n is large. It can also be called as

cascaded full adder.

4-Bit Multiplier

Binary multiplication can be accomplished by several approaches. The

approach presented here is realized entirely with combinational circuits. Such a

circuit is called an array multiplier. The term array is used to describe the multiplier

because the multiplier is organized as an array structure. Each row, called a partial

product, is formed by a bit-by-bit multiplication of each operand.

For example, a partial product is formed when each bit of operand ‘a’ is

multiplied by b0, resulting in a3b0, a2b0,a1b0, a0b0. The binary multiplication table

is identical to the AND truth table.

CARE GROUP OF INSTITUTIONS

Page 7

Each product bit {o(x)}, is formed by adding partial product columns. The

product equations, including the carry-in {c(x)}, from column c(x-1), are (the plus

sign indicates addition not OR). Each product term, p(x), is formed by AND gates

and collection of product terms needed for the multiplier. By adding appropriate p

term outputs, the multiplier output equations are realized, as shown in figure.

PROCEDURE:

1. Start Xilinx ISE 14.3, click on “CREATE A NEW PROJECT” and then click on

Next.

2. Select your working directory, give the name of the project, then click on

“NEXT”.

3. Select the device family (Spartan 3E), Device (XC3S250E), package (PQ208),

Speed grade (4), Synthesis tool (XST [VHDL/VERILOG]), simulator (ISim) and

preferred language (Verilog) from the available device list, and then click

“NEXT” and click FINISH.

4. Write the HDL code and be careful to give the entity name the same as project

name.

5. In the design window change into simulation and double click behavioral

check syntax.

6. If the HDL code is error free a green check mark will be shown on the

behavioral check syntax.

7. Select simulation then double click on “Simulate Behavioral Model” (here we

can change the level of abstraction. i.e. structural/behavioral/dataflow/switch

level)

8. If there is zero error a new window will be shown. Apply the desired input as

1’s and 0’s and check whether the outputs are correct or not in the output

waveform.

9. Create a new verilog test fixture and give the various input constraints and

save the file and check if any errors are present.

10. Simulate the testbench and analyze the output waveform.

CARE GROUP OF INSTITUTIONS

Page 8

8-Bit Addition (Ripple Carry Adder)

Logic Diagram:

4-Bit Multiplier

4 X 4 Array Multiplier:

a3 a2 a1 a0

b3 b2 b1 b0

a3b0 a2b0 a1b0 a0b0

a3b1 a2b1 a1b1 a0b1

a3b2 a2b2 a1b2 a0b2

a3b3 a2b3 a1b3 a0b3

o7 o6 o5 o4 o3 o2 o1

a0b0 = p0 a1b2 = p8

a1b0 = p1 a0b3 = p9

a0b1 = p2 a3b1 = p10

a2b0 = p3 a2b2 = p11

a1b1 = p4 a1b3 = p12

a0b2 = p5 a3b2 = p13

a3b0 = p6 a2b3 = p14

a2b1 = p7 a3b3 = p15

CARE GROUP OF INSTITUTIONS

Page 9

Logic Diagram:

P14 P13 P11,P10 P7 P6 P4 P3 P2 P1 P0

P15

FA FA HA HA HA

P12 P8

FA FA FA

P9

FA FA FA HA

O7 O6 O5 O4 O3 O2 O1 O0

Programs:

Addition using Dataflow modeling

module addition8bit(a,b,oup);

input [7:0] a;

input [7:0] b;

output [8:0] oup;

assign oup = a + b;

endmodule

CARE GROUP OF INSTITUTIONS

Page 10

Ripple Carry Adder using Full Adder using Dataflow Modelling

Structural Modelling module fulladder(cout,sum, in1,in2,cin);

module ripplecarry_adder(a,b,oup); output cout;

input [7:0] a,b; output sum;

output [8:0] oup; input in1,in2,cin;

assign {cout,sum}= in1 + in2 + cin;

wire [6:0]c; endmodule

parameter cin=1'b0;

// instantiating 1b-ti full adders

fulladder f1(c[0],oup[0], a[0],b[0],cin);

fulladder f2(c[1],oup[1], a[1],b[1],c[0]);

fulladder f3(c[2],oup[2], a[2],b[2],c[1]);

fulladder f4(c[3],oup[3], a[3],b[3],c[2]);

fulladder f5(c[4],oup[4], a[4],b[4],c[3]);

fulladder f6(c[5],oup[5], a[5],b[5],c[4]);

fulladder f7(c[6],oup[6], a[6],b[6],c[5]);

fulladder f8(oup[8],oup[7],

a[7],b[7],c[6]);

endmodule

Multiplier using Dataflow Modelling

module mult4bit(a,b,op);

input [3:0] a;

input [3:0] b;

output [7:0]op;

assign op= a * b;

endmodule

RESULT:

The 8-bit Adder and 4-bit Multiplier were designed and, HDL codes were written

and verified.

CARE GROUP OF INSTITUTIONS

Page 11

Expt No: Date:

DESIGN ENTRY AND SIMULATION OF SEQUENTIAL CIRCUITS

AIM:

To design and implement the following sequential circuits using Verilog HDL

and verify using the testbench

1. Counters

2. Finite State Machine

APPARATUS REQUIRED:

PC with Windows XP.

Xilinx 14.3

THEORY:

Counters

Synchronous counters are distinguished from asynchronous counters in that

clock pulses are applied to the CP inputs of all flip-flops. The common pulse triggers

all the flip-flops simultaneously, rather than one at a time in succession as in

asynchronous counter. The decision whether a flip-flop is to be complemented or not

is determined from the values of the J and K inputs at the time of the pulse. If J = K =

0, the flip-flop remains unchanged. If J = K = 1, the flip-flop complements. In a

synchronous binary ripple counter, the flip-flop in the lowest-order position is

complemented with very pulse. This means that it’s J and K inputs must be

maintained at logic-1. A flip-flop in any other position is complemented with a pulse

provided all the bits in the lower-order positions are equal to 1, because the lower-

order bits (when all 1’s) will change to 0’s on the next count pulse. The binary count

dictates the next higher-order bit is complemented. Synchronous binary counters

have a regular pattern and can easily be constructed with complementing flip-flops (

J K or T Type) and gates.

Finite State Machine

Designing a synchronous finite state machine (FSM) is a common task for a

digital logic engineer. A finite state machine can be divided in to two types: Moore

and Mealy state machines. The current state of the machine is stored in the state

memory, a set of n flip-flops clocked by a single clock signal (hence “synchronous”

state machine). The state vector (also current state, or just state) is the value currently

CARE GROUP OF INSTITUTIONS

Page 12

stored by the state memory. The next state of the machine is a function of the state

vector in Moore; function of state vector and the inputs in Mealy.

PROCEDURE:

1. Start Xilinx ISE 14.3, click on “CREATE A NEW PROJECT” and then click on

Next.

2. Select your working directory, give the name of the project, then click on

“NEXT”.

3. Select the device family (Spartan 3E), Device (XC3S250E), package (PQ208),

Speed grade (4), Synthesis tool (XST [VHDL/VERILOG]), simulator (ISim) and

preferred language (Verilog) from the available device list, and then click

“NEXT” and click FINISH.

4. Write the HDL code and be careful to give the entity name the same as project

name.

5. In the design window change into simulation and double click behavioral

check syntax.

6. If the HDL code is error free a green check mark will be shown on the

behavioral check syntax.

7. Select simulation then double click on “Simulate Behavioral Model” (here we

can change the level of abstraction. i.e. structural/behavioral/dataflow/switch

level)

8. If there is zero error a new window will be shown. Apply the desired input as

1’s and 0’s and check whether the outputs are correct or not in the output

waveform.

9. Create a new verilog test fixture and give the various input constraints and

save the file and check if any errors are present.

10. Simulate the testbench and analyze the output waveform.

COUNTER

Logic Diagram:

CARE GROUP OF INSTITUTIONS

Page 13

Finite State Machine

State Diagram

Up Counter Design using Behavioral Down Counter Design using

Modelling Behavioral Modelling

module counter_up(out,clk,reset); module

output [3:0]out; counter_up_down(out,clk,reset);

input clk, reset; output [3:0]out;

reg [3:0] out; input clk, reset;

always @(negedge clk or posedge reset) reg [3:0] out;

if(reset) always @(negedge clk or posedge

out <=4'b0000; reset)

else if(reset)

out<=out+1; out <=4'b0000;

endmodule else

out<=out-1;

endmodule

Up/Down Counter Design using Mod-10 Counter Design

Behavioral Modelling module counter_ten(out,clk,reset);

module output [3:0]out;

counter_up_down(out,clk,reset,control); input clk, reset;

output [3:0]out; reg [3:0] out;

input clk, reset,control; always @(posedge clk or posedge

reg [3:0] out; reset)

always @(negedge clk or posedge reset) begin

if(reset) if(clk)

out <=4'b0000; if(reset)

CARE GROUP OF INSTITUTIONS

Page 14

else out <=4'b0000;

if (control) else

out<=out+1; if (out==4'b1001)

else out<=0;

out<=out-1; else

endmodule out<=out+1;

end

endmodule

Counter Design using Structural JK Flip-Flop Design using Behavioral

Modelling Modelling

module module jkff (q,qbar,j,k,clk,reset);

counter_strutural(q,qbar,clk,reset); output q,qbar;

output [3 : 0] q; input j,k,clk,reset;

output [3 : 0] qbar; reg q,qbar;

input clk,reset; always @ (negedge clk or reset)

wire [0 : 1] temp; if (~reset)

reg high; begin

initial q = 1'b0;

high = 1'b1; qbar = 1'b1;

jkff ff1 (q[0],qbar[0],high,high,clk,reset); end

jkff ff2 else if (reset)

(q[1],qbar[1],high,high,q[0],reset); begin

jkff ff3 if (j==0 && k ==0)

(q[2],qbar[2],high,high,q[1],reset); begin

jkff ff4 q = q;

(q[3],qbar[3],high,high,q[2],reset); qbar = qbar;

endmodule end

else if ( j== 0 && k ==1)

Counter Design using Behavioral begin

Modelling q = 1'b0;

qbar = 1'b1;

module counter(clk, reset,result); //,ena end

input clk, reset; else if (j==1 && k == 0)

output [3:0]result; begin

reg [3:0] result; q = 1'b1;

qbar = 1'b0;

always @(negedge clk or posedge end

reset) else if (j ==1 && k ==1)

begin begin

if (reset) q = ~q;

CARE GROUP OF INSTITUTIONS

Page 15

result = 0; qbar = ~qbar;

end

else else

result = result + 1; begin

end q = 1'bz;

endmodule qbar = 1'bz;

end

end

endmodule

FSM Design using Behavioral Modelling

module m1011( clk, rst, inp, outp);

input clk, rst, inp;

output outp;

reg [1:0] state;

reg outp;

always @( posedge clk, rst )

begin

if( rst )

state <= 2'b00;

else

begin

case( {state,inp} )

3'b000: begin

state <= 2'b00;

outp <= 0;

end

3'b001: begin

state <= 2'b01;

outp <= 0;

end

3'b010: begin

state <= 2'b10;

outp <= 0;

end

3'b011: begin

state <= 2'b01;

CARE GROUP OF INSTITUTIONS

Page 16

outp <= 0;

end

3'b100: begin

state <= 2'b00;

outp <= 0;

end

3'b101: begin

state <= 2'b11;

outp <= 0;

end

3'b110: begin

state <= 2'b10;

outp <= 0;

end

3'b111: begin

state <= 2'b01;

outp <= 1;

end

endcase

end

end

endmodule

RESULT:

The Sequential circuits were designed and, HDL codes were written and verified

using Testbench circuits

CARE GROUP OF INSTITUTIONS

Page 17

Expt No: Date:

SYNTHESIZE AND PLACE & ROUTE SIMULATIONS OF COMBINATIONAL

AND SEQUENTIAL CIRCUITS

AIM:

To synthesize and post place and route simulations the following combinational and

sequential circuits using Verilog HDL

1. 8 bit adders,

2. 4 bit multipliers,

3. Counters,

APPARATUS REQUIRED:

PC with Windows XP.

XILINX 14.3.

PROCEDURE:

1. Start Xilinx ISE 14.3, click on “CREATE A NEW PROJECT” and then click on

Next.

2. Select your working directory, give the name of the project, then click on

“NEXT”.

3. Select the device family (Spartan 3E), Device (XC3S250E), package (PQ208),

Speed grade (4), Synthesis tool (XST [VHDL/VERILOG]), simulator (ISim) and

preferred language (Verilog) from the available device list, and then click

“NEXT” and click FINISH.

4. Write the HDL code and be careful to give the entity name the same as project

name.

5. In the design window change into simulation and double click behavioral

check syntax.

6. If the HDL code is error free a green check mark will be shown on the

behavioral check syntax.

7. In the design window change into implementation and click on “Synthesis

XST”. If the HDL code is error free a green check mark will be shown on the

Synthesize –XST.

8. Note down the Device Utilization Summary (Number of Slices , Number of

LUTs and Number of bonded IOBs)

9. Double Click the View RTL Schematic in the process window and RTL

Schematic view of your HDL code.

CARE GROUP OF INSTITUTIONS

Page 18

10. Double Click View Technology Schematic in the process window and View

the Technology Schematic view of your HDL code.

11. In User Constraints, double click I/O Pin Planning (PlanAhead) –Post

synthesize. PlanAhead window is opened.

12. Give the input ports and output port 9n the PlanAhead tool and save the

configuration and close the PlanAhead window.

13. Double Click the Implementation Design and green check mark will be shown

on the Implementation Icon.

14. In the Design window, change into Post – Route Simulation and by double

clicking the Post-Place & Route Check Syntax and if code is error free a green

check mark will be shown on the Post-Place & Route Check Syntax.

15. Double Click Simulate Post-Place & Route Model and analyze the output

waveform.

16. In the design window change into Implementation and process window

under implementation – Place & Route, double click the View/Edit Routed

Design (FPGA Editor), now we can see the routed design of our circuit.

Programs:

Combinational Circuits:

Ripple Carry Adder using Structural Full Adder using Dataflow Modelling

Modelling module fulladder(cout,sum, in1,in2,cin);

module ripplecarry_adder(a,b,oup); output cout;

input [7:0] a,b; output sum;

output [8:0] oup; input in1,in2,cin;

assign {cout,sum}= in1 + in2 + cin;

wire [6:0]c; endmodule

parameter cin=1'b0;

// instantiating 1b-ti full adders

fulladder f1(c[0],oup[0], a[0],b[0],cin);

fulladder f2(c[1],oup[1], a[1],b[1],c[0]);

fulladder f3(c[2],oup[2], a[2],b[2],c[1]);

fulladder f4(c[3],oup[3], a[3],b[3],c[2]);

fulladder f5(c[4],oup[4], a[4],b[4],c[3]);

fulladder f6(c[5],oup[5], a[5],b[5],c[4]);

fulladder f7(c[6],oup[6], a[5],b[5],c[5]);

fulladder f8(oup[8],oup[7],

a[5],b[5],c[6]);

endmodule

CARE GROUP OF INSTITUTIONS

Page 19

Sequential Circuits;

Counter Design using Structural JK Flip-Flop Design using Behavioral

Modelling Modelling

module module jkff (q,qbar,j,k,clk,reset);

counter_strutural(q,qbar,clk,reset); output q,qbar;

output [3 : 0] q; input j,k,clk,reset;

output [3 : 0] qbar; reg q,qbar;

input clk,reset; always @ (negedge clk or reset)

wire [0 : 1] temp; if (~reset)

reg high; begin

initial q = 1'b0;

high = 1'b1; qbar = 1'b1;

jkff ff1 (q[0],qbar[0],high,high,clk,reset); end

jkff ff2 else if (reset)

(q[1],qbar[1],high,high,q[0],reset); begin

jkff ff3 if (j==0 && k ==0)

(q[2],qbar[2],high,high,q[1],reset); begin

jkff ff4 q = q;

(q[3],qbar[3],high,high,q[2],reset); qbar = qbar;

endmodule end

else if ( j== 0 && k ==1)

Counter Design using Behavioral begin

Modelling q = 1'b0;

qbar = 1'b1;

module counter(clk, reset,result); //,ena end

input clk, reset; else if (j==1 && k == 0)

output [3:0]result; begin

reg [3:0] result; q = 1'b1;

qbar = 1'b0;

always @(negedge clk or posedge end

reset) else if (j ==1 && k ==1)

begin begin

if (reset) q = ~q;

result = 0; qbar = ~qbar;

end

else else

result = result + 1; begin

end q = 1'bz;

endmodule qbar = 1'bz;

end

end

endmodule

CARE GROUP OF INSTITUTIONS

Page 20

FSM Design using Behavioral Modelling

module m1011( clk, rst, inp, outp);

input clk, rst, inp;

output outp;

reg [1:0] state;

reg outp;

always @( posedge clk, rst )

begin

if( rst )

state <= 2'b00;

else

begin

case( {state,inp} )

3'b000: begin

state <= 2'b00;

outp <= 0;

end

3'b001: begin

state <= 2'b01;

outp <= 0;

end

3'b010: begin

state <= 2'b10;

outp <= 0;

end

3'b011: begin

state <= 2'b01;

outp <= 0;

end

3'b100: begin

state <= 2'b00;

outp <= 0;

end

3'b101: begin

state <= 2'b11;

outp <= 0;

end

3'b110: begin

state <= 2'b10;

outp <= 0;

CARE GROUP OF INSTITUTIONS

Page 21

end

3'b111: begin

state <= 2'b01;

outp <= 1;

end

endcase

end

end

endmodule

RESULT:

The Combinational and Sequential circuits were designed and Verilog HDL codes

were written and verified. The verilog codes are Synthesized and Post Place and

Route was done.

CARE GROUP OF INSTITUTIONS

Page 22

Expt No: Date:

HARDWARE IMPLEMENTATION OF COMBINATIONAL AND

SEQUENTIAL CIRCUITS

AIM:

To synthesize and post place and route simulations the following combinational and

sequential circuits using Verilog HDL

1. 8 bit adders

2. Counters

APPARATUS REQUIRED:

PC with Windows XP.

XILINX 14.3.

Spartan 3E FPGA Kit.

PROCEDURE:

Combinational and Sequential Circuits Hardware Implementation Procedure

1. Start Xilinx ISE 14.3, click on “CREATE A NEW PROJECT” and then click on

Next.

2. Select your working directory, give the name of the project, then click on “NEXT”.

3. Select the device family (Spartan 3E), Device (XC3S250E), package (PQ208), Speed

grade (4), Synthesis tool (XST [VHDL/VERILOG]), simulator (ISim) and preferred

language (Verilog) from the available device list, and then click “NEXT” and click

FINISH.

4. Write the HDL code and be careful to give the entity name the same as project name.

5. In the design window change into simulation and double click behavioral check

syntax.

6. If the HDL code is error free a green check mark will be shown on the behavioral

check syntax.

7. In the design window change into implementation and click on “Synthesis XST”. If

the HDL code is error free a green check mark will be shown on the Synthesize –

XST.

8. Note down the Device Utilization Summary (Number of Slices , Number of LUTs and

Number of bonded IOBs)

9. Double Click the View RTL Schematic in the process window and RTL Schematic

view of your HDL code.

10. Double Click View Technology Schematic in the process window and View the

Technology Schematic view of your HDL code.

11. In User Constraints, double click I/O Pin Planning (PlanAhead) –Post synthesize.

PlanAhead window is opened.

12. Give the input ports and output port 9n the PlanAhead tool and save the configuration

and close the PlanAhead window.

CARE GROUP OF INSTITUTIONS

Page 23

13. Double Click the Implementation Design and green check mark will be shown on the

Implementation Icon.

14. In the Design window, change into Post – Route Simulation and by double clicking

the Post-Place & Route Check Syntax and if code is error free a green check mark

will be shown on the Post-Place & Route Check Syntax.

15. Double Click Simulate Post-Place & Route Model and analyze the output waveform.

16. In the design window change into Implementation and process window under

implementation – Place & Route, double click the View/Edit Routed Design (FPGA

Editor), now we can see the routed design of our circuit.

17. A BIT file will be generate by double clicking the Generate Programming File.

18. The BIT file is loaded in the FPGA processor through JTAG or USB cable and the

output can be verified using the hardware kit.

19. MCS file is created and loaded into the PROM for verification.

20. By using ChipScope tool outputs waveforms in the PC can be controlled by Hardware

kit for Clock based circuits.

Procedure for ChipScope:

Sequential Circuits Hardware Implementation Procedure (Counter Circuit)

1. Click the project menu and then select new source.

2. Select Chip Scope Definition and Connection File and enter the file name, click Next

and click finish.

3. Double click your .cdc File.

4. Now your chip scope pro application will open, and then click next.

5. Mention the Number of Input Trigger Port and Mention the Trigger Width then Click

Next.

6. Click Modify Connections and Select your clk_BUFGP then click Make connections.

7. Mention your Trigger input then click Make connections, click OK.

8. Click Return to Project Navigator and then click YES.

9. Right click the Analyze Design Using Chip scope and Click Run.

10. Connect your board using JTAG or USB.

11. Open the Chip scope Pro Analyzer.

12. Click JTAG Chain and select Xilinx Parallel cable, Click Auto Detect Cable Type

then click OK.

13. Your IC has been detected then clicks OK. Now Select My Device and click

configure.

14. Click Select New File and Select your .bit file and click open.

15. Click Select New File Select your .cdc file and click open and then click OK.

16. Open the UNIT: 0 then Right click the Trigger setup and open the trigger setup.

17. Now the Trigger setup will be appear.

18. Right Click the Waveform and Open Waveform.

19. Right Click the Trigger setup => click trigger run mode =>click Repetitive, click

RUN.

20. You can change the input in your board the corresponding output is show in your PC.

CARE GROUP OF INSTITUTIONS

Page 24

Programs

Addition using Dataflow modeling

module addition8bit(a,b,oup);

input [7:0] a;

input [7:0] b;

output [8:0] oup;

assign oup = a + b;

endmodule

Multiplier using Dataflow Modelling

module mult4bit(a,b,op);

input [3:0] a;

input [3:0] b;

output [7:0]op;

assign op= a * b;

endmodule

Counter Design

module counter_up(out,clk,reset);

output [3:0]out;

input clk, reset;

reg [3:0] out;

always @(negedge clk or posedge reset)

if(reset)

out <=4'b0000;

else

out<=out+1;

endmodule

Input Pin Numbers:

Output Pin Numbers:

RESULT:

The Combinational and Sequential circuits were designed and Verilog HDL codes were

written and verified. The verilog codes are Synthesized and Post Place and Route was done.

Also the outputs were verified using the Spartan3E FPGA hardware kit.

CARE GROUP OF INSTITUTIONS

Page 25

Expt No: Date:

DESIGN AND AUTOMATIC LAYOUT GENEARTION FOR COUNTER

AIM:

To design, simulate and synthesize the counter circuit and generate the automatic

layout and simulate through post layout extraction using Cadence tool.

APPARATUS REQUIRED:

1. Personal Computer with Linux Operating System

2. Cadence tool

PROCEDURES:

1. Write a verilog program (filename.v) for counter circuit and save it and close.

2. Simulate through the ncsim command and give the inputs and check the output

through the simvision window.

3. Synthesize and elaborate the verilog program.

4. Create a constraint file (filename.g) and read the file.

5. Synthesize the circuit and note down the power, timing parameters.

6. Create a net file (filename_net.v) and the hdl net file.

7. Open the encounter tool for automatic layout genearation.

8. Import the filename_net.v and select the *.lef file.

9. Create the power and ground nets.

10. Create the *.view file

11. Specify the floorplan structure and define the core utilization area.

12. Create power rings and nets (VDD and VSS) and select the ring configuration for

metal layers.

13. Create the power stripes and specify the number of sets to be used.

14. Route the design and Place the standard cells.

15. Do the Pre-CTS, clock synthesize, post-CTS and extract RC operations.

16. Create the *.gds file.

CARE GROUP OF INSTITUTIONS

Page 26

PROGRAM:

Up Counter Design using Behavioral Modelling

module counter_up_down(out,clk,reset,control);

output [3:0]out;

input clk, reset,control;

reg [3:0] out;

always @(negedge clk or posedge reset)

if(reset)

out <=4'b0000;

else

out<=out+1;

endmodule

RESULT:

The counter circuit was designed, simulated and synthesized and generated the

automatic layout and simulate through post layout extraction using Cadence tool.

CARE GROUP OF INSTITUTIONS

Page 27

Expt No: Date:

CMOS INVERTER LAYOUT DESIGN

AIM:

To design and simulate the CMOS inverter and observe the DC and transient

responses and to create the layout of CMOS inverter and extract the parasitic values using

cadence tool.

APPARATUS REQUIRED:

1. Personal Computer with Linux Operating System

2. Cadence tool

PROCEDURES:

Schematic Entry:

Creating a new library:

1. In the library manager, execute File - New library. The new library form appears.

2. In the new library form, type ‘my design lib’ in the name section.

3. In the field of directory section, verify that the path to the library is set to ~/Database /

Cadence- analog – lab –bl3 and click ok.

4. In the next ‘technology file for new library form select option attach to an existing

tech file and click ok.

5. In the ‘attach design library to technology file’ form, select gpdk180 form the cyclic

field and click ok.

6. After creating a new library you can verify it from the library manager.

7. If you right click on the ‘my design lib’ and select properties, you wil find that

gpdk180 library is attached as techlib to ‘my design lib’.

Creating a schematic cell view:

8. In the CIW or library manager, execute file – new – cell view.

9. Setup the new file form as follows, Do not edit the library path file and the above

might be different from the path shown in your form.

10. Click ok when done the above setting. A black schematic window for the inverter

design appears.

Adding components to schematic:

11. In the inverter schematic window, click the instance fixed menu icon to display the

add instance form.

12. Click on the browse button. This opens up a library browser from which you can

select components and the symbol view.

13. After you complete the add instance form move your cursor to the schematic window

and click left to place a component.

14. This is a table of components for building the inverter schematic.

CARE GROUP OF INSTITUTIONS

Page 28

15. After entering components, click cancel in the add instance form or press ESC with

your cursor in the schematic window.

LIBRARY NAME CELL NAME PROPERTIES/COMMENTS

For M0 : model name PMOS1,

gpdk180 PMOS

W = wp, L =180n

For M1 : model name NMOS1,

gpdk180 NMOS

W = 2u, L =180n

Adding pins to schematic:

16. Click the pin fixed menu icon in the schematic window. You can execute create pin or

press ‘p’.

17. Add pin form appears. Type the following in the ADD pin form in the next order

leaving space between the pin.

PIN NAMES DIRECTION

Vin Input

Vout output

18. Select cancel and then the schematic window enter window file or press the f bind

key.

Adding wires to schematic:

19. Click the wire (narrow) icon in the schematic window.

20. In the schematic window click on a pin of one of your components as the first point

for your wiring. A diamond shape appears over the starting point of this wire.

21. Follow the prompts at the bottom of design window and click left on the destination

point for your wire. A wire is routed between the source and destination points.

22. Complete the wiring as shown in the figure and when done wiring press ECS key in

the schematic window to cancel wiring.

Saving the design:

Click the check and save icon in the schematic editor window observe CIW output for

any errors.

Building the inverter test design:

Creating the inverter test cell view:

23. In the CIW or library manager, execute file – new – cell view.

24. Setup the newfile as shown below.

25. Click ok when done. A blank schematic window for the inverter test design appears.

CARE GROUP OF INSTITUTIONS

Page 29

26. Using the components list and properties/ comments in this table build the inverter

test schematic.

LIBRARY NAME CELL VIEW NAME PROPERTIES/COMMENTS

My design lib Inverter Symbol

V1 = 0, v2 = 1, td = 0,

Analog lib Vpulse tr=tf=1ns, ton = 10ns, T=

20ns

Analog lib Vdc, gnd Vdc = 1.8v

27. Add the above components using create – instance or by pressing I.

28. Click the wire (narrow) icon and wire your schematic.

29. Click create wirename or press c to name the i/p (vin) and output wires as in below

schematic.

30. Click on the check and save icon to save the design.

Analog simulation with spectra:

Starting the simulation environment:

31. In the inverter-test schematic window execute launch – ADEL. The variable virtuoso

analog design environment (ADE) simulation window appears.

Choosing a simulator:

32. In the simulation window (ADE) execute setup – simulator / directory / host.

33. In the choosing simulator form, set the simulator field to specra and click ok.

34. In the simulation window (ADE) execute the setup model libraries.

To complete, move the cursor and click ok.

Choosing Analysis:

35. Click the choose- Analysis icon in the simulation window (ADE).

36. The choosing analysis form appears.

37. To Setup the transient analysis.

a. In the analysis section select tron.

b. Set the stoptime as 200ns

c. Click at the moderate or enabled button and the bottom and then click apply.

38. To set for DC analysis

a. In the analysis section select DC.

b. Turn on save DC operating point.

c. Turn on the component parameters.

d. Double click the select Vpulse source.

e. Select the DC voltage in the select window parameter and click in the form start

and stop voltages are 0 to 1.8.

f. Select the enable button and click apply and then click ok.

CARE GROUP OF INSTITUTIONS

Page 30

Setting deign variables:

39. Click on the edit variable icon and its corresponding form appears.

40. Click copy from at the bottom of the form. The design is scanned. All variables

formed in the design are listed.In the few moments the wp variable name wp and

enter.

Value (ixpr) 2u

41. Click change and notice the update and then click ok or cancel (in the editing design

variable window)

Selecting o/p’s for plotting:

42. Execute the o/p’s to be plotted -select on sschematic in the simulation window.

43. Follow the prompt at the bottom. Click on the o/p net vout input vin of the inverter.

Press esc with the cursor after selecting.

Running the simulation:

44. Execute the simulation Netlist and run in the simulation window to start the

simulation on the icon. This will create the netlist as well as run the simulation.

45. When the simulation finishes the transient DC plots automatically with the log file.

Creating layout view of inverter:

46. From the inverter schematic window menu execute Launch – lyout XL. A startup

option form appears.

47. Select create new option. This gives a new cell view form.

48. Check the cell name (inverter). Viewname (Layout).

49. Click ok from the newcell view form. LSW and a black layout window appears along

with schematic window.

Adding components to layout:

50. Execute connecting Generate – All from source or click the icon in the layout editor

window. Generate the layout form appears. Click ok which imports the schematic

components into the layout window automatically.

51. Rearrange the components with in PR – Boundary as shown.

52. To rotate a component select the component and execute Edit – Properties. Now

select the degree of rotation from the property edit form.

53. Move a component, select the component and execute edit – Move command.

Making connection:

54. Execute connectivity – Nets – show/hide selected incomplete Nets or click the icon in

the layout menu.

55. Move the mouse pointer over the device and click LMB to get the connectivity

information which shows the guide lines for the interconnections of the components.

CARE GROUP OF INSTITUTIONS

Page 31

56. From the layout window, execute create – shape – path / create wire or create – shape

– rectangle and select the appropriate layers from the LSW window and vias for

making the interconnections.

Creating contacts/vias:

Execute create-via to place different contacts.

Connection Contact Type

For metal 1 – Polyconnection Metal 1 –Poly

For metal 1 – psubstrate connection Metal 1 – psub

For metal 1 – nwell connection Metal 1 - nwell

Saving the design:

Save your design by selecting file – save to save the layout and layout appears.

Running a DRC:

57. Open the inverter layout form the CIW or library manager if you have closed that.

Press shift –f in the layout to display all the levels.

58. Select Assura – Run DRC from layout window. The DRC form appears. The library

and cellname are taken from the current design window, but rule file maybe missing.

59. Seelect the technology as gpdk180. This automatically loads the rule file.

60. Click ok to start DRC.

61. A progress form will appear. You can click on the watch log file to see the log file.

62. When DRC finishes a dialog box asking you if you want to view your DRC results,

and click yes to view results of the run.

63. If there any DRC results in the design view layer window (VLW) and error layer

window (ELW) appears. Also the errors highlight in the design itself.

64. Click view – summary in the ELW to find the details of error.

65. You can refer to the run file for info, correct all the DRC error and the Re-run the

DRC.

66. If there are no errors in the layout then a dialog bo appears with no DRC errors found

written in it, click on close to terminate the DRC run.

Running LVS:

67. Select Assura – Run LVS from the layout window. The Assura – Run – LVS form

appears. It will automatically load both the schematic and layout view of the cell and

click ok.

68. The LVS begins and a progress form appears.

69. If the schematic and layout matches completely, you will get form displaying

schematic and layout match.

70. If the schematic and layout do not matches, a form informs that the LVS completed

successfully and asks if you want to see the results of this sum.

71. Click yes in the form.

72. In the LVS dialog box you can find the details of mismatches and you need to correct

all those mismatches and Re-Run the LVS.

CARE GROUP OF INSTITUTIONS

Page 32

73. In the filtering tab of the form enter power nets as vdd! , vss! And enter ground nets

as gnd!

74. Click ok in the assura parasitic extraction form when done. The RCX progress form

appears, in the progress form click watch log file to see the output log file.

75. When RCX completes, a dialog box appears, informs you that Assura RCX run

completed successfully.

76. You can open the av-extracted view from the library manager and view the parasitic.

RESULT:

The CMOS inverter Schematic and symbol was created and DC and Transient analysis were

done. Manual layout was drawn and parasitic extraction was done.

CARE GROUP OF INSTITUTIONS

Page 33

Expt No: Date:

DIFFERENTIAL AMPLIFIER LAYOUT DESIGN

AIM:

To design and simulate the simple Differential amplifier and observe the DC and

transient responses, calculate CMRR and to create the layout of CMOS inverter and extract

the parasitic values using cadence tool.

APPARATUS REQUIRED:

1. Personal Computer with Linux Operating System

2. Cadence tool

Schematic Diagram

PROCEDURES:

Schematic Entry:

Creating a new library:

1. In the library manager, execute File - New library. The new library form appears.

2. In the new library form, type ‘my design lib’ in the name section.

3. In the field of directory section, verify that the path to the library is set to ~/Database /

Cadence- analog – lab –bl3 and click ok.

CARE GROUP OF INSTITUTIONS

Page 34

4. In the next ‘technology file for new library form select option attach to an existing

tech file and click ok.

5. In the ‘attach design library to technology file’ form, select gpdk180 form the cyclic

field and click ok.

6. After creating a new library you can verify it from the library manager.

7. If you right click on the ‘my design lib’ and select properties, you wil find that

gpdk180 library is attached as techlib to ‘my design lib’.

Creating a schematic cell view:

8. In the CIW or library manager, execute file – new – cell view.

9. Setup the new file form as follows, Do not edit the library path file and the above

might be different from the path shown in your form.

10. Click ok when done the above setting. A black schematic window for the inverter

design appears.

Adding components to schematic:

11. In the inverter schematic window, click the instance fixed menu icon to display the

add instance form.

12. Click on the browse button. This opens up a library browser from which you can

select components and the symbol view.

13. After you complete the add instance form move your cursor to the schematic window

and click left to place a component.

14. This is a table of components for building the inverter schematic.

15. After entering components, click cancel in the add instance form or press ESC with

your cursor in the schematic window.

Adding pins to schematic:

16. Click the pin fixed menu icon in the schematic window. You can execute create pin or

press ‘p’.

17. Add pin form appears. Type the following in the ADD pin form in the next order

leaving space between the pin.

PIN NAMES DIRECTION

Vin Input

Vout output

CARE GROUP OF INSTITUTIONS

Page 35

18. Select cancel and then the schematic window enter window file or press the f bind

key.

LIBRARY NAME CELL NAME PROPERTIES/COMMENTS

For M0 : model name PMOS1,

gpdk180 PMOS

W = wp, L =180n

For M1 : model name NMOS1,

gpdk180 NMOS

W = 2u, L =180n

Adding wires to schematic:

19. Click the wire (narrow) icon in the schematic window.

20. In the schematic window click on a pin of one of your components as the first point

for your wiring. A diamond shape appears over the starting point of this wire.

21. Follow the prompts at the bottom of design window and click left on the destination

point for your wire. A wire is routed between the source and destination points.

22. Complete the wiring as shown in the figure and when done wiring press ECS key in

the schematic window to cancel wiring.

Saving the design:

Click the check and save icon in the schematic editor window observe CIW output for

any errors.

Building the inverter test design:

Creating the inverter test cell view:

23. In the CIW or library manager, execute file – new – cell view.

24. Setup the newfile as shown below.

25. Click ok when done. A blank schematic window for the inverter test design appears.

26. Using the components list and properties/ comments in this table build the inverter

test schematic.

LIBRARY NAME CELL VIEW NAME PROPERTIES/COMMENTS

My design lib Inverter Symbol

V1 = 0, v2 = 1, td = 0,

Analog lib Vpulse tr=tf=1ns, ton = 10ns, T=

20ns

Analog lib Vdc, gnd Vdc = 1.8v

27. Add the above components using create – instance or by pressing I.

28. Click the wire (narrow) icon and wire your schematic.

29. Click create wirename or press c to name the i/p (vin) and output wires as in below

schematic.

30. Click on the check and save icon to save the design.

CARE GROUP OF INSTITUTIONS

Page 36

Analog simulation with spectra:

Starting the simulation environment:

31. In the inverter-test schematic window execute launch – ADEL. The variable virtuoso

analog design environment (ADE) simulation window appears.

Choosing a simulator:

32. In the simulation window (ADE) execute setup – simulator / directory / host.

33. In the choosing simulator form, set the simulator field to specra and click ok.

34. In the simulation window (ADE) execute the setup model libraries.

To complete, move the cursor and click ok.

Choosing Analysis:

35. Click the choose- Analysis icon in the simulation window (ADE).

36. The choosing analysis form appears.

37. To Setup the transient analysis.

d. In the analysis section select tron.

e. Set the stoptime as 200ns

f. Click at the moderate or enabled button and the bottom and then click apply.

38. To set for DC analysis

g. In the analysis section select DC.

h. Turn on save DC operating point.

i. Turn on the component parameters.

j. Double click the select Vpulse source.

k. Select the DC voltage in the select window parameter and click in the form start

and stop voltages are 0 to 1.8.

l. Select the enable button and click apply and then click ok.

Setting deign variables:

39. Click on the edit variable icon and its corresponding form appears.

40. Click copy from at the bottom of the form. The design is scanned. All variables

formed in the design are listed.In the few moments the wp variable name wp and

enter.

Value (ixpr) 2u

41. Click change and notice the update and then click ok or cancel (in the editing design

variable window)

Selecting o/p’s for plotting:

42. Execute the o/p’s to be plotted -select on sschematic in the simulation window.

43. Follow the prompt at the bottom. Click on the o/p net vout input vin of the inverter.

Press esc with the cursor after selecting.

CARE GROUP OF INSTITUTIONS

Page 37

Running the simulation:

44. Execute the simulation Netlist and run in the simulation window to start the

simulation on the icon. This will create the netlist as well as run the simulation.

45. When the simulation finishes the transient DC plots automatically with the log file.

Creating layout view of inverter:

46. From the inverter schematic window menu execute Launch – lyout XL. A startup

option form appears.

47. Select create new option. This gives a new cell view form.

48. Check the cell name (inverter). Viewname (Layout).

49. Click ok from the newcell view form. LSW and a black layout window appears along

with schematic window.

Adding components to layout:

50. Execute connecting Generate – All from source or click the icon in the layout editor

window. Generate the layout form appears. Click ok which imports the schematic

components into the layout window automatically.

51. Rearrange the components with in PR – Boundary as shown.

52. To rotate a component select the component and execute Edit – Properties. Now

select the degree of rotation from the property edit form.

53. Move a component, select the component and execute edit – Move command.

Making connection:

54. Execute connectivity – Nets – show/hide selected incomplete Nets or click the icon in

the layout menu.

55. Move the mouse pointer over the device and click LMB to get the connectivity

information which shows the guide lines for the interconnections of the components.

56. From the layout window, execute create – shape – path / create wire or create – shape

– rectangle and select the appropriate layers from the LSW window and vias for

making the interconnections.

Creating contacts/vias:

Execute create-via to place different contacts.

Connection Contact Type

For metal 1 – Polyconnection Metal 1 –Poly

For metal 1 – psubstrate connection Metal 1 – psub

For metal 1 – nwell connection Metal 1 - nwell

Saving the design:

Save your design by selecting file – save to save the layout and layout appears.

CARE GROUP OF INSTITUTIONS

Page 38

Running a DRC:

57. Open the inverter layout form the CIW or library manager if you have closed that.

Press shift –f in the layout to display all the levels.

58. Select Assura – Run DRC from layout window. The DRC form appears. The library

and cellname are taken from the current design window, but rule file maybe missing.

59. Seelect the technology as gpdk180. This automatically loads the rule file.

60. Click ok to start DRC.

61. A progress form will appear. You can click on the watch log file to see the log file.

62. When DRC finishes a dialog box asking you if you want to view your DRC results,

and click yes to view results of the run.

63. If there any DRC results in the design view layer window (VLW) and error layer

window (ELW) appears. Also the errors highlight in the design itself.

64. Click view – summary in the ELW to find the details of error.

65. You can refer to the run file for info, correct all the DRC error and the Re-run the

DRC.

66. If there are no errors in the layout then a dialog bo appears with no DRC errors found

written in it, click on close to terminate the DRC run.

Running LVS:

67. Select Assura – Run LVS from the layout window. The Assura – Run – LVS form

appears. It will automatically load both the schematic and layout view of the cell and

click ok.

68. The LVS begins and a progress form appears.

69. If the schematic and layout matches completely, you will get form displaying

schematic and layout match.

70. If the schematic and layout do not matches, a form informs that the LVS completed

successfully and asks if you want to see the results of this sum.

71. Click yes in the form.

72. In the LVS dialog box you can find the details of mismatches and you need to correct

all those mismatches and Re-Run the LVS.

73. In the filtering tab of the form enter power nets as vdd! , vss! And enter ground nets

as gnd!

74. Click ok in the assura parasitic extraction form when done. The RCX progress form

appears, in the progress form click watch log file to see the output log file.

75. When RCX completes, a dialog box appears, informs you that Assura RCX run

completed successfully.

76. You can open the av-extracted view from the library manager and view the parasitic.

RESULT:

The simple Differential Amplifier Schematic and symbol was created and DC and Transient

analysis were done. Manual layout was drawn and parasitic extraction was done.

CARE GROUP OF INSTITUTIONS

You might also like

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- EC8661 VLSI Design LaboratoryDocument53 pagesEC8661 VLSI Design LaboratorySriram100% (4)

- EC8661 VLSI Design Laboratory PDFDocument53 pagesEC8661 VLSI Design Laboratory PDFSINDHUNo ratings yet

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- Vlsi RecordDocument61 pagesVlsi RecordRaghul MNo ratings yet

- EC6612 VLSI Design LabDocument130 pagesEC6612 VLSI Design LabbalabaskerNo ratings yet

- Vlsi ManualDocument110 pagesVlsi ManualSam Joel.DNo ratings yet

- VlsilabDocument82 pagesVlsilabk poornimaNo ratings yet

- Arithmetic Logic Unit: Project Report OnDocument36 pagesArithmetic Logic Unit: Project Report OnYermakov Vadim IvanovichNo ratings yet

- Introduction To Xilinx ISE 8.2i: Digital Design LaboratoryDocument5 pagesIntroduction To Xilinx ISE 8.2i: Digital Design LaboratoryGanesh JayakumarNo ratings yet

- 8.programmable Asic Design SoftwareDocument21 pages8.programmable Asic Design Softwaresalinsweety50% (2)

- Lab - 06 - Timing Simulation & Design Implementation (Combinational Logic)Document11 pagesLab - 06 - Timing Simulation & Design Implementation (Combinational Logic)Muhammad SaudNo ratings yet

- Vlsi Design FlowDocument7 pagesVlsi Design FlowAster RevNo ratings yet

- EE-421 Digital System Design Laboratory Manual: Group MembersDocument34 pagesEE-421 Digital System Design Laboratory Manual: Group MembersMuhammad SohaibNo ratings yet

- EE326 Lab 2Document25 pagesEE326 Lab 2krishneelNo ratings yet

- HDL ManualDocument44 pagesHDL ManualNithish ManjuNo ratings yet

- Ec3561-Vlsi Design LabDocument144 pagesEc3561-Vlsi Design LabperiyasamyNo ratings yet

- 8 Bit ALU by XilinxDocument16 pages8 Bit ALU by XilinxDIPTANU MAJUMDERNo ratings yet

- Computer Logic LabsDocument75 pagesComputer Logic LabsІко Оджо Віктор ОдаудуNo ratings yet

- EC8661-VLSI DESIGN LAB-116516724-vlsi Lab Manual PDFDocument146 pagesEC8661-VLSI DESIGN LAB-116516724-vlsi Lab Manual PDFSathish Kumar G Assistant Professor ECE KingstonNo ratings yet

- University of Technology Michatronics Branch: Wasan Shakir Mahmood 4 - Stage Supervisor: Layla HattimDocument13 pagesUniversity of Technology Michatronics Branch: Wasan Shakir Mahmood 4 - Stage Supervisor: Layla HattimWasan ShakirNo ratings yet

- Notes7 Applying Synthesis ConstraintsDocument18 pagesNotes7 Applying Synthesis ConstraintsravishopingNo ratings yet

- Spartan3E FPGA User GuideDocument14 pagesSpartan3E FPGA User GuideAbdelbacet_MHAMDINo ratings yet

- Practical Workbook (DSD)Document33 pagesPractical Workbook (DSD)ayeshaNo ratings yet

- VHDL Modeling and Synthesis in The Laboratory: Session 2647Document12 pagesVHDL Modeling and Synthesis in The Laboratory: Session 2647Красимир КостадиновNo ratings yet

- BEC7L1 - Digital Cmos Vlsi-LabDocument66 pagesBEC7L1 - Digital Cmos Vlsi-LabRamkumardevendiranDevenNo ratings yet

- FPGA Lab#1Document8 pagesFPGA Lab#1حساب ويندوزNo ratings yet

- EC8661-VLSI DESIGN LAB-116516724-Vlsi Lab ManualDocument149 pagesEC8661-VLSI DESIGN LAB-116516724-Vlsi Lab ManualAngelin ArulNo ratings yet

- CSEE W4840 Embedded Lab 1 - Memory DisplayDocument12 pagesCSEE W4840 Embedded Lab 1 - Memory Displaymicrobotica126No ratings yet

- Comprehensive Study of Flow To Program FPGA Kit Using VHDLDocument4 pagesComprehensive Study of Flow To Program FPGA Kit Using VHDLIJRECENo ratings yet

- RTL Compiler PDFDocument49 pagesRTL Compiler PDFStudent100% (1)

- Summer Training Report On Vlsi and Fpga ImplementationDocument44 pagesSummer Training Report On Vlsi and Fpga ImplementationsaurabhNo ratings yet

- Fpga: Digital Designs: Team Name:Digital DreamersDocument8 pagesFpga: Digital Designs: Team Name:Digital DreamersRishabhNo ratings yet

- LAB04Document15 pagesLAB04زياد عبدالله عبدالحميدNo ratings yet

- VLSI Design LabDocument130 pagesVLSI Design LabRao UmarNo ratings yet

- final DDCOLab manual (1)Document31 pagesfinal DDCOLab manual (1)susheela NatarajuNo ratings yet

- DFT With Tetramax PDFDocument33 pagesDFT With Tetramax PDFdeepakk_alpineNo ratings yet

- Digital System Design using VHDL and the Spartan-3E FPGA BoardDocument22 pagesDigital System Design using VHDL and the Spartan-3E FPGA BoardhungfrdNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaNo ratings yet

- EECS150 Lab 2: Mapping Circuit Elements to FPGAsDocument15 pagesEECS150 Lab 2: Mapping Circuit Elements to FPGAsdarkdrone66No ratings yet

- EEE 304 - Exp2Document7 pagesEEE 304 - Exp2Aurongo NasirNo ratings yet

- Layout and Synthesis - VLSI - Design - LabDocument115 pagesLayout and Synthesis - VLSI - Design - LabShanthini SridharNo ratings yet

- Acknowledgement: "4 Bit Microprosessor by VHDL" Mrs. K.G.BhuvaDocument26 pagesAcknowledgement: "4 Bit Microprosessor by VHDL" Mrs. K.G.BhuvaPranav MehtaNo ratings yet

- Silvaco EDA DemoDocument11 pagesSilvaco EDA DemobhataviNo ratings yet

- Project 2012fallDocument5 pagesProject 2012fallATHIRA V RNo ratings yet

- VHDL TutorialDocument127 pagesVHDL TutorialDeepanker KumeriaNo ratings yet

- Traffic Control Using VHDLDocument18 pagesTraffic Control Using VHDLnikky234No ratings yet

- System On Chip Design and ModellingDocument131 pagesSystem On Chip Design and ModellingGurram KishoreNo ratings yet

- Vls I Lab Manual 2021Document58 pagesVls I Lab Manual 2021shilpakesavNo ratings yet

- RTL Simulation Lab ManualDocument78 pagesRTL Simulation Lab Manualswapna revuri100% (2)

- Digital System Design Using VHDL PDFDocument47 pagesDigital System Design Using VHDL PDFSneha S RevankarNo ratings yet

- Ug Vlsi Design LabDocument2 pagesUg Vlsi Design LabvlsijpNo ratings yet

- VLSI Lab Manual Student Copy 21-22 04.10.21Document76 pagesVLSI Lab Manual Student Copy 21-22 04.10.21RanjithNo ratings yet

- Verilog HDLDocument62 pagesVerilog HDLMohamedAlzarrugh100% (1)

- Tutorial 1 Introduction To VHDL, and ISE 10.1 On The Digilent Spartan-3E Starter Kit BoardDocument17 pagesTutorial 1 Introduction To VHDL, and ISE 10.1 On The Digilent Spartan-3E Starter Kit BoardpwjfjfjklfdsNo ratings yet

- VLSI Design ReportDocument25 pagesVLSI Design ReportLucy HeartfilliaNo ratings yet

- 8 Bit Risc Processor PresentationDocument36 pages8 Bit Risc Processor PresentationSantanu KumarNo ratings yet

- VHDL MaterialDocument33 pagesVHDL MaterialChutiyaNo ratings yet

- Circuit Theory 2014 - Apr MayDocument6 pagesCircuit Theory 2014 - Apr MaySriramNo ratings yet

- Wireless Communication - EC 2401 - I - Answer KeyDocument9 pagesWireless Communication - EC 2401 - I - Answer KeySriramNo ratings yet

- MeasurementsDocument12 pagesMeasurementsSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- EC6702Document2 pagesEC6702SriramNo ratings yet

- Data Path Circuits - EC6601Document10 pagesData Path Circuits - EC6601SriramNo ratings yet

- 2014 - Apr May PDFDocument4 pages2014 - Apr May PDFSriramNo ratings yet

- VLSI Design Lab EC-6612-nDocument58 pagesVLSI Design Lab EC-6612-nSriramNo ratings yet

- Sensors: SL - N o Application Sensor Example PriceDocument6 pagesSensors: SL - N o Application Sensor Example PriceSriramNo ratings yet

- Principles of Management: Lesson PlanDocument23 pagesPrinciples of Management: Lesson PlanSriram100% (1)

- ECE Department Course DetailsDocument151 pagesECE Department Course DetailsSriramNo ratings yet

- Design Entry and Simulation of Sequential CircuitsDocument7 pagesDesign Entry and Simulation of Sequential CircuitsSriramNo ratings yet

- What Determines The Color of An LED?: SemiconductingDocument1 pageWhat Determines The Color of An LED?: SemiconductingSriramNo ratings yet

- Ec 6501Document1 pageEc 6501SriramNo ratings yet

- DSP WorkshopDocument2 pagesDSP WorkshopSriramNo ratings yet

- Ec2357 - Vlsi Design LaboratoryDocument45 pagesEc2357 - Vlsi Design LaboratorySriramNo ratings yet

- Concept MapDocument18 pagesConcept MapSriramNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- SEMESTER Requirements Lab EquipmentDocument29 pagesSEMESTER Requirements Lab EquipmentSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Verilog Course ManualDocument60 pagesVerilog Course ManualSriramNo ratings yet

- Ece 2013Document14 pagesEce 2013SriramNo ratings yet

- Ece 2008Document27 pagesEce 2008SriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Analog DesignDocument4 pagesAnalog DesignSriramNo ratings yet

- Kalasalingam University ECE302 Analog Communication Question BankDocument6 pagesKalasalingam University ECE302 Analog Communication Question BankSriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Verilog Lab ProgramsDocument25 pagesVerilog Lab ProgramsSriramNo ratings yet

- Module - 4 Sub System Design and PLA Acsce: 1 Acsce DR - HBB Notes On VlsiDocument90 pagesModule - 4 Sub System Design and PLA Acsce: 1 Acsce DR - HBB Notes On VlsiGovind M RoddannavarNo ratings yet

- LB2 UCxx x1 Data Sheet EnUS 13828738699Document8 pagesLB2 UCxx x1 Data Sheet EnUS 13828738699PRaoNo ratings yet

- Description Description Table of Contents Description: 26 27 PTC 2 3 51 52 Mech 1Document53 pagesDescription Description Table of Contents Description: 26 27 PTC 2 3 51 52 Mech 1juan luis san miguelNo ratings yet

- Tipos de AntenasDocument7 pagesTipos de AntenasDaniel AtiNo ratings yet

- Department of Eee ProspectusDocument5 pagesDepartment of Eee ProspectusAnonymous 9lX3i3vNo ratings yet

- AM FM Digital RadioDocument29 pagesAM FM Digital RadioPartha SenguptaNo ratings yet

- VolkswagenDocument53 pagesVolkswagenandersonNo ratings yet

- Sup MotorolaDocument18 pagesSup MotorolaMario João MarioNo ratings yet

- Tps 51650Document51 pagesTps 51650Qomari Ali MustofaNo ratings yet

- 174 48037 PDFDocument18 pages174 48037 PDFJuan Steven Montenegro PenagosNo ratings yet

- SIEMENS SIMOVERT P Transistorised Voltage-Source DC-Link Inverters Series 6SE21Document110 pagesSIEMENS SIMOVERT P Transistorised Voltage-Source DC-Link Inverters Series 6SE21ndani10No ratings yet

- Digital Meters Unit: Data SheetDocument2 pagesDigital Meters Unit: Data SheetrummanhzNo ratings yet

- PT NEXWAVE 2012 DT AnalysisDocument58 pagesPT NEXWAVE 2012 DT AnalysisFulanNo ratings yet

- Automatic Switch Mode Battery Charger: Design FeaturesDocument1 pageAutomatic Switch Mode Battery Charger: Design FeaturesJavier VillanuevaNo ratings yet

- P8822-000-R SERIES Dual Axes Position ControllerDocument29 pagesP8822-000-R SERIES Dual Axes Position ControllerAliali SmieoNo ratings yet

- Reactive Voltage DroopDocument2 pagesReactive Voltage Droopwagner_guimarães_1No ratings yet

- Avr4306 C4320 Protocol 4.6Document26 pagesAvr4306 C4320 Protocol 4.6fatrhinoNo ratings yet

- Drive Test Problems (Part 2)Document25 pagesDrive Test Problems (Part 2)Abdelrahman.Mostafa100% (7)

- Naida CI Q70 Product GuideDocument12 pagesNaida CI Q70 Product GuideAmirul AsyrafNo ratings yet

- RadWin - RW 2049 B350 PDFDocument3 pagesRadWin - RW 2049 B350 PDFElfy PalmaNo ratings yet

- Understanding A Simple Operating System: Chapter 1: Starting Up SOS 3Document53 pagesUnderstanding A Simple Operating System: Chapter 1: Starting Up SOS 3mmxy_1No ratings yet

- Manual Book Panasonic t2375mx LDocument39 pagesManual Book Panasonic t2375mx LWawan KreatifNo ratings yet

- AMS1117ADJDocument5 pagesAMS1117ADJCharly FhNo ratings yet

- A-199 SPRV ManualDocument6 pagesA-199 SPRV ManualinformagicNo ratings yet

- SMP72x14445, SMP72x14445S SMP72x14445T, SMP72x14445ST SMP45S, SMP45ST SMP9645S SMP9645STDocument2 pagesSMP72x14445, SMP72x14445S SMP72x14445T, SMP72x14445ST SMP45S, SMP45ST SMP9645S SMP9645STnithulNo ratings yet

- Synopsis On Voice Controlled Home Automation by Vishnu Chaudhary EceDocument25 pagesSynopsis On Voice Controlled Home Automation by Vishnu Chaudhary EceVíshñú Tømàr0% (1)

- Hardware Laptop/notebook ComputersDocument15 pagesHardware Laptop/notebook ComputersCostasNo ratings yet

- Configuring SELCO Sigma S6500 UI ModuleDocument1 pageConfiguring SELCO Sigma S6500 UI ModuleZubair RajpootNo ratings yet

- Easy refrigeration controllers connection diagramsDocument1 pageEasy refrigeration controllers connection diagramskelvinNo ratings yet

- Potential TransformerDocument27 pagesPotential TransformerVijay Pandit100% (1)