Professional Documents

Culture Documents

Computer Architecture - CS252

Uploaded by

Asghar Hussain ShahCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Computer Architecture - CS252

Uploaded by

Asghar Hussain ShahCopyright:

Available Formats

Rev No 2

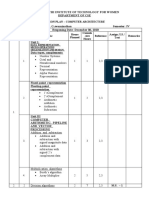

Course Outline CS 252 Credit Hours: 3 Page 1 of 2 pages

Dated: 01.06.05

Computer Architecture

Text Book:- M. Morris Mano, Computer System Architecture

Reference Books:-

Computer Architecture and Organization by John P. Hayes, McGraw Hill

International Edition

Advanced Computer Architecture- A design space approach by Dezso Sima,

Terence Fountain, Peter Kacsuk, Pearson Edition

Computer Organization and Architecture, by William Stallings, 6th Edition,

Prentice Hall Publishers.

Course Description:-

The objective of this course is to familiarize the students with the architecture

and organization of computer systems. It builds on the already acquired knowledge

of DLD and electronics. The major topics include: Data path design, ALUs,

pipelining, memory management, Internal devices and their architectural

requirements, control mechanism, and parallel processing.

Pre- requisite:-

Digital Logic Design

Grading Policy:-

In Semester Evaluations: 30%

End Semester Evaluation: 70%

Week-wise Breakdown

Week Topics/Activities Chapter

Control Memory, Address Sequencing

1 7.1 to 7.3

Micro program example

2 Design of Control Unit 7.4

Introduction, General Register Organization

3 8.1 to 8.3

Stack Organization

Instruction Formats, Addressing Modes

4 8.4 to 8.6

Data Transfer & Manipulation

Rev No 2

Course Outline CS 252 Credit Hours: 3 Page 2 of 2 pages

Dated: 01.06.05

Program Control, Reduced Instruction Set Computers (RISC),

5 8.7 to 8.8

Overlap Register Windows

Parallel Processing, Pipelining, Arithmetic Pipeline,

6 9.1 to 9.4

Instruction Pipeline

RISC Pipeline, Vector Processing

7 9.5 to 9.7

Array Processors

Introduction, Addition & Subtraction

8 10.1 to 10.4

Multiplication Algorithms, Division Algorithms

Floating Point Arithmetic Operations

9 Decimal Arithmetic Unit 10.5 to 10.7

Decimal Arithmetic Operations

Peripheral Devices, Input-Output Interface

10 11.1 to 11.4

Asynchronous Data Transfer, Modes of Transfer

Priority Interrupt

11 Direct Memory Access Input-Output Process 11.5 to 11.8

Serial Communication

Memory Hierarchy, Main Memory

12 12.1 12.4

Auxiliary Memory, Associative Memory

Cache Memory, Virtual Memory

13 12.5 to 12.7

Memory Management Hardware

Characteristics of Multiprocessors

Interconnection Structures, Interprocessor Arbitration,

14 13

Interprocessor Communication & Synchronization, Cache

Coherence.

15 Review

16 End Semester Exam

You might also like

- How To Program Python-Introducing XML-2002-Deitel (Pythonhtp1 Toc)Document13 pagesHow To Program Python-Introducing XML-2002-Deitel (Pythonhtp1 Toc)Rafael PLNo ratings yet

- Digital Logic Design and Computer OrganizationDocument227 pagesDigital Logic Design and Computer OrganizationRadhika Rani100% (2)

- Threads in Operating SystemDocument103 pagesThreads in Operating SystemMonika SahuNo ratings yet

- Multi Core Architectures and ProgrammingDocument10 pagesMulti Core Architectures and ProgrammingRIYA GUPTANo ratings yet

- ASTM Standards Catalog 2013Document22 pagesASTM Standards Catalog 2013dassoumennNo ratings yet

- Computer Science Ocr - j277Document18 pagesComputer Science Ocr - j277naseerNo ratings yet

- Coa CifDocument3 pagesCoa CifSamarth MathurNo ratings yet

- Programmig Ad Problem Solvig Through C': RatioaleDocument19 pagesProgrammig Ad Problem Solvig Through C': RatioaleCS and IT Department VBPCNo ratings yet

- Computer Organization Course Outline To Be Printed-1Document2 pagesComputer Organization Course Outline To Be Printed-1habtamu fentewNo ratings yet

- Computer Organization and ArchitectureDocument3 pagesComputer Organization and ArchitectureAnil MarsaniNo ratings yet

- Microprocessor Course OutlineDocument3 pagesMicroprocessor Course OutlineFrank JohnNo ratings yet

- Hawassa University Faculty of Informatics Department of Computer ScienceDocument3 pagesHawassa University Faculty of Informatics Department of Computer ScienceElijah IbsaNo ratings yet

- CSE216: Computer Organization and Architecture: Course Context and OverviewDocument3 pagesCSE216: Computer Organization and Architecture: Course Context and OverviewAman Agarwal AmanNo ratings yet

- NF) S ) JF Cfof) U G) KFN LJLJW ) JF, /fhkqflít T (Tlo ) 0Fl, Sdko'6/ Ol Hlgo/ KBSF) V'NF K - Ltof) Lutftds K/Liffsf) Kf7/Oqmd Låtlo KQDocument4 pagesNF) S ) JF Cfof) U G) KFN LJLJW ) JF, /fhkqflít T (Tlo ) 0Fl, Sdko'6/ Ol Hlgo/ KBSF) V'NF K - Ltof) Lutftds K/Liffsf) Kf7/Oqmd Låtlo KQNikesh NeupaneNo ratings yet

- CC ZG502 Course HandoutDocument10 pagesCC ZG502 Course HandoutpoonamNo ratings yet

- CIS775 Computer Architecture Chapter 1 FundamentalsDocument43 pagesCIS775 Computer Architecture Chapter 1 FundamentalsSwapnil Sunil ShendageNo ratings yet

- CS322 - Computer Architecture (CA) : Spring 2019 Section V3Document57 pagesCS322 - Computer Architecture (CA) : Spring 2019 Section V3TANZEELA SHAKEELNo ratings yet

- ICT Ed. 439 (Architecture) UpdatedDocument5 pagesICT Ed. 439 (Architecture) UpdatedMagneto Eric Apollyon ThornNo ratings yet

- Complement and R's Complement), Fixed Point RepresentationDocument7 pagesComplement and R's Complement), Fixed Point RepresentationBishal ShahiNo ratings yet

- Module - 1-1Document58 pagesModule - 1-1Praga PadmaNo ratings yet

- Parallel and Distributed SystemsDocument3 pagesParallel and Distributed Systemsarungupta652No ratings yet

- Embedded System (9168)Document5 pagesEmbedded System (9168)Victoria FrancoNo ratings yet

- Operating System Course OutlineDocument3 pagesOperating System Course OutlineKashif AsgharNo ratings yet

- Se 4Document15 pagesSe 4Nabin TimsinaNo ratings yet

- Computer Systems 5Th Edition Full ChapterDocument41 pagesComputer Systems 5Th Edition Full Chapterjoy.dial537100% (27)

- Computer Systems 5Th Edition PDF Full ChapterDocument41 pagesComputer Systems 5Th Edition PDF Full Chapterlawrence.graves202100% (20)

- Subject Code Subject Name Credits: Overview of Computer Architecture & OrganizationDocument4 pagesSubject Code Subject Name Credits: Overview of Computer Architecture & Organizationanon_71491248No ratings yet

- Lesson 4 Class NotesDocument5 pagesLesson 4 Class NotesgarangdedengNo ratings yet

- Birla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesDocument8 pagesBirla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesRaja KarthikNo ratings yet

- Co-So-Du-Lieu - Carlo-A.-Curino - Mit6 - 830f10 - Lec04-Introduction-To-Database-Internals - (CC) - (Cuuduongthancong - Com)Document7 pagesCo-So-Du-Lieu - Carlo-A.-Curino - Mit6 - 830f10 - Lec04-Introduction-To-Database-Internals - (CC) - (Cuuduongthancong - Com)aozNo ratings yet

- Paper Content 80% (Post Relate) 20% (General Knowledge) : Power SectorDocument7 pagesPaper Content 80% (Post Relate) 20% (General Knowledge) : Power Sectorjindal gulNo ratings yet

- Ce246: Database Management System: Sr. No. Title of The Unit Minimum Number of HoursDocument4 pagesCe246: Database Management System: Sr. No. Title of The Unit Minimum Number of HoursAnand BapodaraNo ratings yet

- COMPTIA IT FUNDAMENTALS Course Outline Final 2019Document8 pagesCOMPTIA IT FUNDAMENTALS Course Outline Final 2019liboireNo ratings yet

- Course Material Verilog ModuleDocument86 pagesCourse Material Verilog Modulevr46shreyasNo ratings yet

- Computer Science XIIDocument48 pagesComputer Science XIIPrem RajwanshiNo ratings yet

- Lesson Plan - Computer Architecture: Data Representation, Micro-Operations Organization and DesignDocument6 pagesLesson Plan - Computer Architecture: Data Representation, Micro-Operations Organization and DesignvijiiiisNo ratings yet

- 2cse402 Operating SystemDocument2 pages2cse402 Operating SystemHet TrivediNo ratings yet

- Lecture-Lab BreakdownDocument3 pagesLecture-Lab Breakdownmodyzombie82No ratings yet

- IT-205 (OS) Course OutlineDocument3 pagesIT-205 (OS) Course OutlineWaleed HussainNo ratings yet

- (Gatepsu - In) CS - GATE-2018 - Paper - 4-FEB-2018 Morning Session (1) - 1 PDFDocument9 pages(Gatepsu - In) CS - GATE-2018 - Paper - 4-FEB-2018 Morning Session (1) - 1 PDFkavithada9390No ratings yet

- Std11 CompSci EMDocument392 pagesStd11 CompSci EMnatarajNo ratings yet

- Computer Organisation - Morris ManoDocument178 pagesComputer Organisation - Morris ManoRamaSankar Molleti67% (3)

- COAL Theory Outline Fall 2022Document4 pagesCOAL Theory Outline Fall 2022Mohammad HumayunNo ratings yet

- CS - GATE-2018 - Paper - 4-FEB-2018 Morning SessionDocument11 pagesCS - GATE-2018 - Paper - 4-FEB-2018 Morning SessionsatishNo ratings yet

- BDA Techmax (Searchable)Document150 pagesBDA Techmax (Searchable)hell noNo ratings yet

- Third Semester SyllabusDocument10 pagesThird Semester SyllabusDil Prasad KunwarNo ratings yet

- Kadi Sarva Vishwavidyalaya: Fourth Year Bachelor of Engineering (Computer/IT)Document4 pagesKadi Sarva Vishwavidyalaya: Fourth Year Bachelor of Engineering (Computer/IT)DevanshNo ratings yet

- Distributed Systems Course OutlineDocument7 pagesDistributed Systems Course OutlineyekoyesewNo ratings yet

- CS - GATE-2018 - Paper - 4-FEB-2018 Morning SessionDocument34 pagesCS - GATE-2018 - Paper - 4-FEB-2018 Morning SessionAkshay MahajanNo ratings yet

- Cs Gate 2018 4 Feb Ms TgaDocument9 pagesCs Gate 2018 4 Feb Ms Tgaprabhu.swain3500No ratings yet

- Fundamentals of Operating Systems CompressDocument171 pagesFundamentals of Operating Systems CompresskowserNo ratings yet

- Digital Design Using HDL PDFDocument2 pagesDigital Design Using HDL PDFMarvin MayormenteNo ratings yet

- Computer TechnologyDocument192 pagesComputer TechnologyAmit PatelNo ratings yet

- SYLLABUSDocument2 pagesSYLLABUSHardik PandyaNo ratings yet

- Bca Major Syllabus - 2ND SemDocument7 pagesBca Major Syllabus - 2ND Sempradipta.sarkarNo ratings yet

- 6th Sem SyllabusDocument11 pages6th Sem SyllabusRahul SheikhNo ratings yet

- RNASeq Command Line 25march2021 0Document33 pagesRNASeq Command Line 25march2021 0prateek bhatiaNo ratings yet

- Birla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesDocument8 pagesBirla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesSunny KumarNo ratings yet

- Lec 2 AggregatesDocument8 pagesLec 2 AggregatesAsghar Hussain ShahNo ratings yet

- Lec 11 Bituminous MaterialsDocument6 pagesLec 11 Bituminous Materialsamjad aliNo ratings yet

- Lecture #01: BY Engineer Asghar Hussain ShahDocument9 pagesLecture #01: BY Engineer Asghar Hussain ShahAsghar Hussain ShahNo ratings yet

- Lecture#15: Sub Structure: Sub-Structure or Foundation Is The Lower Portion of The Building, UsuallyDocument3 pagesLecture#15: Sub Structure: Sub-Structure or Foundation Is The Lower Portion of The Building, UsuallyAsghar Hussain ShahNo ratings yet

- Lecture #01: BY Engineer Asghar Hussain ShahDocument9 pagesLecture #01: BY Engineer Asghar Hussain ShahAsghar Hussain ShahNo ratings yet

- EE150 Network Analysis-II Course OutlineDocument1 pageEE150 Network Analysis-II Course OutlineAsghar Hussain ShahNo ratings yet

- ACI The New Model Code Feb 2013Document87 pagesACI The New Model Code Feb 2013Asghar Hussain ShahNo ratings yet

- New Microsoft Office Word DocumentDocument5 pagesNew Microsoft Office Word DocumentAsghar Hussain ShahNo ratings yet

- Industrial Management MGT 427Document2 pagesIndustrial Management MGT 427Asghar Hussain ShahNo ratings yet

- Lecture #01: BY Engineer Asghar Hussain ShahDocument9 pagesLecture #01: BY Engineer Asghar Hussain ShahAsghar Hussain ShahNo ratings yet

- Chapter 03Document16 pagesChapter 03Iqbal HossainNo ratings yet

- High Voltage Technology - EE463Document1 pageHigh Voltage Technology - EE463Asghar Hussain ShahNo ratings yet

- Physics I - GS111Document2 pagesPhysics I - GS111Asghar Hussain ShahNo ratings yet

- High Voltage Technology - EE463Document1 pageHigh Voltage Technology - EE463Asghar Hussain ShahNo ratings yet

- Communications Skills - ENG 112Document1 pageCommunications Skills - ENG 112Asghar Hussain ShahNo ratings yet

- Abid 2 PDFDocument1 pageAbid 2 PDFAsghar Hussain ShahNo ratings yet

- Electromagnetic Feild Theory - EE315 - 14-07-2008Document2 pagesElectromagnetic Feild Theory - EE315 - 14-07-2008Asghar Hussain ShahNo ratings yet

- New Microsoft Office Word DocumentDocument5 pagesNew Microsoft Office Word DocumentAsghar Hussain ShahNo ratings yet

- Syllabus Class NurseryDocument1 pageSyllabus Class NurseryAsghar Hussain ShahNo ratings yet

- K.G Topics For DecorationDocument13 pagesK.G Topics For DecorationAsghar Hussain ShahNo ratings yet

- Large residential plot plan layout dimensionsDocument1 pageLarge residential plot plan layout dimensionsAsghar Hussain ShahNo ratings yet

- 2.final Structure25.07.2015-Model PDFDocument1 page2.final Structure25.07.2015-Model PDFAsghar Hussain ShahNo ratings yet

- Class 7thDocument15 pagesClass 7thAsghar Hussain ShahNo ratings yet

- Kaka G Tangarr-ModelDocument1 pageKaka G Tangarr-ModelAsghar Hussain ShahNo ratings yet

- Abid 1Document1 pageAbid 1Asghar Hussain ShahNo ratings yet

- Abid 1 PDFDocument1 pageAbid 1 PDFAsghar Hussain ShahNo ratings yet

- Lec 2 AggregatesDocument8 pagesLec 2 AggregatesAsghar Hussain ShahNo ratings yet

- Lec 3 CementsDocument7 pagesLec 3 CementsAsghar Hussain ShahNo ratings yet

- Master of Science Applied Computer Science and Society (Acs)Document4 pagesMaster of Science Applied Computer Science and Society (Acs)mostofa kalamNo ratings yet

- Cs403pc Operating Systems Unit 1Document13 pagesCs403pc Operating Systems Unit 1saiv36387No ratings yet

- Fuzzy Logic in Control DesignDocument10 pagesFuzzy Logic in Control DesignSonjoy SahaNo ratings yet

- Introduction To OpenMPDocument22 pagesIntroduction To OpenMPVariable 14No ratings yet

- IIT - CSC-109 - Chapter 1 & 2Document24 pagesIIT - CSC-109 - Chapter 1 & 2ArpoxonNo ratings yet

- Ku Cse SyllabusDocument75 pagesKu Cse SyllabusAshrith KaparaboinaNo ratings yet

- Parallelism in Technical WritingDocument17 pagesParallelism in Technical WritingMuhammad Hammad100% (1)

- Cuda 2dDocument8 pagesCuda 2dJose Angel Duarte MartinezNo ratings yet

- Slides 1Document28 pagesSlides 1YPSAPEXNo ratings yet

- ANSYS Fluent Getting Started GuideDocument56 pagesANSYS Fluent Getting Started GuideManoj KumarNo ratings yet

- Introduction To CUDA C 3Document67 pagesIntroduction To CUDA C 3Tarun RamNo ratings yet

- OpenMP Shared Memory ProgrammingDocument23 pagesOpenMP Shared Memory ProgrammingMonikaNo ratings yet

- Real-Time Star Identification Using Synthetic Radial Pattern and Its Hardware ImplementationDocument9 pagesReal-Time Star Identification Using Synthetic Radial Pattern and Its Hardware ImplementationYans PangerunganNo ratings yet

- MRSPTU B.Tech. Electronics Engg. 7th-8th Sem Scheme and Syllabus 2018 Batch OnwardsDocument24 pagesMRSPTU B.Tech. Electronics Engg. 7th-8th Sem Scheme and Syllabus 2018 Batch Onwardsraj raushanNo ratings yet

- Blue Gene AbstractDocument9 pagesBlue Gene AbstractBhanu Sai KolakaletiNo ratings yet

- Process ManagementDocument26 pagesProcess ManagementBright Alike ChiwevuNo ratings yet

- Nextflow in Bioinformatics Executors Performance - 2023 - Future Generation CoDocument12 pagesNextflow in Bioinformatics Executors Performance - 2023 - Future Generation CoRuchira SahaNo ratings yet

- Ds 42 Perf Opt enDocument202 pagesDs 42 Perf Opt enSamir Vergara PosadaNo ratings yet

- Big Data Analytics IntroductionDocument36 pagesBig Data Analytics IntroductionLikhith PNo ratings yet

- CS6303 Computer Architecture Two Marks QuestionsDocument56 pagesCS6303 Computer Architecture Two Marks QuestionsAngela KasekeNo ratings yet

- Computer GenerationDocument38 pagesComputer Generationaneesh_0111100% (1)

- Design of Low Voltage Low Power Neuromorphic Circuits Using CADENCEDocument83 pagesDesign of Low Voltage Low Power Neuromorphic Circuits Using CADENCEmuffassir100% (1)

- Scientific Writing Parallel Computing V2Document15 pagesScientific Writing Parallel Computing V2VD MirelaNo ratings yet

- Gpu IEEE PaperDocument14 pagesGpu IEEE PaperRahul SharmaNo ratings yet

- Ifs Documentation Cy47r3 Part 1 ObservationsDocument82 pagesIfs Documentation Cy47r3 Part 1 ObservationsNeeraj SharmaNo ratings yet

- EspDocument96 pagesEspzakyardo safalahNo ratings yet

- SD TimesDocument45 pagesSD TimesAftab AhmadNo ratings yet

- Artificial Intelligence and Parallel Processing: Knowledge ReasoningDocument2 pagesArtificial Intelligence and Parallel Processing: Knowledge Reasoningchriskathunkumi12No ratings yet