Professional Documents

Culture Documents

AVR585

Uploaded by

dibyo ariOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AVR585

Uploaded by

dibyo ariCopyright:

Available Formats

JED MICROPROCESSORS PTY LTD

173 Boronia Rd, Boronia, (PO Box 30), Victoria, 3155, Australia.

Phone: +61 3 9762 3588, Fax: +61 3 9762 5499.

Internet web site: http://www.jedmicro.com.au/ jed@jedmicro.com.au

AVR585 Single Board Computer (boxed as the

“Little Purple Computer”) AVR585, ATmega103

The AVR585 is a complement to the AVR580 “Little

Blue Computer”, but offers a different range of options in based single board

a similar physical format. It uses an ATmega103 CPU,

and has three serial ports and options of a much larger Xil-

inx gate array (downloaded FPGA rather than factory-

computer with three

loaded CPLD). It trades I/O for the serial ports, but still

has 16 bits of parallel I/O and four analog channels, and

has RS485, Dallas 1-Wire and an LCD/keyboard SPI con-

serial ports, 21 I/O lines

nector. A real-time clock and DataFLASH data- logging · Three UART interfaces, used for three RS232

memory are available as options. An “Upstairs” connec- to D9s, one RS485, or GPS (on add-on

tor allows expansion of memory and I/O functions, e.g. board);

adding megabytes of FLASH, analog outputs, or other

communications hardware. · Dallas 1-Wire interface to external sensors;

The board is designed to be compatible with the com- · Provision for I2C, SPI and CAN bus inter-

ing Atmel ATmega128 CPU, about which not much can faces;

be said because of nondisclosure agreements signed with · Cable connector for CPU FLASH program-

the manufacturer, other than it shares functions with other

ming, with automatic switching to pro-

new ATmega family devices such as the ATmega163, for

example, being able to reprogram its own program mem- gram mode from PC. Connector available

ory (allowing field upgrades of software remotely). Extra for LCD and keyboard scanning;

hardware features of the ATmega128 have connections · Programmed in C, with AVR RISC instruc-

on this board allowing them to be used in future. tion set especially designed for structured

CPU, program FLASH, DataFLASH languages, with several good, low-cost

compilers;

The ATmega103 is the most powerful CPU in the AVR

RISC architecture family, with 128K bytes of program · 16 I/O lines, and bus extension, all via Xilinx

FLASH memory, 4,000 bytes of internal RAM and 4K gate array, allowing extendible hardware,

bytes of byte accessible EEPROM.

The internal UART provides one of the three serial

ports (two other ports are provided by a separate dual Serial I/O

UART.) Using a 3.6864 Mhz crystal, the CPU runs at an The ATmega103 CPU has one full duplex serial port,

average 3.5 MIPS, and provides exact (zero error) baud and this is used for SER3 and the optional RS485 half-

rates from 2400 to 115,200 baud on all serial interfaces. duplex interface.

An EXAR ST16C2550 dual UART provides SER1

The hardware SPI serial port in the CPU is used to com-

and SER2 serial ports. This device has separate interrupts

municate with the DataFLASH memory and external

for the two channels, taken to separate interrupt inputs on

LCD/keyboard devices. The CPU FLASH memory is

the CPU. It also uses the 3.6864 Mhz crystal which runs

programmable via the same connector.

the CPU, and provides exact (zero error) baud rates from

The CPU provides eight analog channels from the in- 2400 to 115,200 baud on its serial interfaces as well.

ternal 10 bit Analog to Digital converter, four are brought

to screw terminals on this board, and the other four are ac-

cessible via the JTAG IDC connector.

DataFLASH memory in a range of chips from 128K

byte to 2M byte is connected to the SPI interface on the

CPU. Data is read and written byte by byte using internal Designed and manufactured

RAM buffers which is then transferred to FLASH while a in Australia by an Australian-

second buffer can then be used. More DataFLASH mem- owned company.

ory can be installed on the “Upstairs” connector.

JED AVR585 Single Board Computer (Release 18 March 2002) 1.

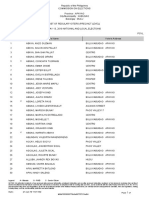

RS DTE/DCE DTE/DCE DTE, 8 lines (modem)

4 Analog In 1-Wire 485 SER3 SER2 SER1

D9F D9F D9F

Sw 5v or CAN Dual

UART MAX213

485 MAX1406

Analog

links CPU

ATmega Xilinx Xilinx

103/104 XCS05 expansion Vreg

to

XCS30 port

FETs

JED AVR585 DataFLASH

8 Optional FETs

ISP prog LEDs

LCD/Kbd 4 In/I2C 4 In/Out 4 In/Out 4 FET out 8-way Sw.Pwr

The CPU serial pins go into the Xilinx gate array so transceiver chip is moved between two overlapping sock-

they can be routed to additional serial devices upstairs, eted positions to change the port from DTE to DCE con-

e.g. a TTL-level GPS module. figuration. This uses one channel of the dual UART.

The serial ports use a combination of receiver/driver The DTR/DSR link can be jumpered to +9 RS232 level

chips: the SER1 DTE port uses a MAX213E with built-in if this is needed by external interfaces.

voltage generators, and the other two ports use a

MAX1406E passive device, stealing power from the SER3

MAX213E rails. The +/- inverter generated rail power can The SER3 RS232 port can be configured as either DTE

be closed down to conserve power in a sleeping system. or DCE, and supports TX and RX lines and loops back

All transceivers have full spec EMC suppression and DTR to DSR and CTS to RTS. The DTR/DSR link can be

15KV ESD ratings. jumpered to +9 RS232 level if this is needed by external

All three RS232 serial ports are provided with right- interfaces. The port DTE/DCE mode is reconfigured with

angled D-submin 9-pin female connectors with jack nuts a simple 4-way jumper. This port uses the CPU UART,

for cable locking. These are positioned along the top edge sharing it with the RS485 port.

of the card, allowing them to protrude through a panel. RS485/CAN

TCP/IP The CPU serial port is also used to communicate via a

Atmel has just released a TCP/IP toolkit for the half-duplex RS485 transceiver. This appears on a three-

ATmega103 to assist internet and networking applica- pin screw terminal connector on the card edge (A, B and

tions. JED will be seeking applications of this board into Gnd.). TX-ON function is facilitated by an end-of-

this type of applicaion. transmission interrupt in the CPU allowing correct timing

for TX turnoff at the end of a byte transmission. Steering

SER1 of the CPU serial port between SER3 RS232 and the

This port is always configured as a DTE port, and pro- RS485 port is controlled in the Xilinx gate array.

vides all eight standard lines to fully support connection to The UART in the CPU supports “9-bit mode”, a multi-

a modem (radio, GSM, Satellite terminal or POTS). This drop mode which uses a 9th bit in the data word to flag an

uses one channel of the dual UART. address byte. (This is sometimes called an “11-bit com-

SER2 munications system”, i.e. a START bit, 8 DATA bits, an

The SER2 RS232 port can be configured as either DTE address flag bit and a STOP bit.)

or DCE, and supports TX, RX, RTS/CTS and loops back The RS485 driver chip can be replaced with a header to

DTR to DSR. The port is reconfigured without links...the “Upstairs” where a CAN bus interface can use it to con-

JED AVR585 Single Board Computer (Release 1, June 2001) 2

nect to the three-pin screw terminal connector in place of LCD, external SPI and FLASH program

the RS485 interface. memory download connector

I2C (or Two Wire Serial Interface Bus) A fourteen-pin ribbon cable connector is provided on

This interface is an option on the board, and uses two the lower card edge to allow simple expansion to an exter-

pins (PD0, PD1) as SCL and SDA respectively, to imple- nal LCD display and keyboard scanner. This is imple-

ment a Master mode interface to a wide range of chips mented in a small CPLD gate array on the back of the

from a variety of manufacturers. Philips are the largest, LCD, and interface to the LCD and keyboard is via the SPI

but National, Microchip, Analog Devices and several oth- serial port.

ers make some nice devices, e.g. radio front ends, multi- This connector has SPI Clock. MOSI and MISO pins,

channel data acquisition systems (National, AD), and Vcc and multiple grounds, two address lines and two

LCD displays (Philips). other strobes (peripheral RD* and WR*).

This interface is well supported by the C Compiler (Using SPI rather than an asynchronous UART-driven

writers. serial interface is a much faster way to communicate with

a display, gives the CPU a more direct control of register

It is easily user-installed by placing of three (non-smt) access, and saves an RS232 serial interface.)

resistors onto the board to take over some pins on the Con-

nector 4 (Inputs) mentioned below, giving screw terminal The first 10 pins on this connector are compatible with

connections to this bus, including a 5volt line. The lines the 10-pin interface cable used for ISP programming in

are protected by clamp diodes and series resistors. the AVR community, and is that used on Kanda program-

mers, and the Atmel STK200/300/500 development kits.

Analog inputs JED also has an adapter for this interface, and it is com-

The ATmega103 has eight analog inputs to dedicated patible with downloaders in Atmel’s AVR-Studio suite

pins on the CPU, and these have their own ground and Vcc and all AVR C and BASIC compiler IDE (Integrated De-

connections to reduce noise. An external, accurate 4.096 velopment Environment) desktops.

volt reference to a reference pin on the CPU sets the full Switching of this interface to “download” mode is

scale range of the converter. automatic from the programming software, as the soft-

The CPU can go into “sleep” mode during conversion ware asserts a system RESET to the AVR585, which

to reduce noise. An interrupt occurs at the end of conver- automatically switches a multiplexer on the board to re-

sion to “wake” the CPU. route TX, RX and CLK lines to the programmer. No links

need be swapped, and it can be done with the board cover

Conversion speed is up to 14 ksamples per second, but in place.

trade-off of ADC speed and accuracy can be set up in a

control register. Dallas 1-Wire interface

On the board, analog inputs are split into two groups: This two-screw terminal connector (1-Wire and

Ground) allows the CPU to send and receive data using

Channels 1...4 go via a plug-in resistor block which al-

the Dallas Semiconductor 1-Wire protocol to

lows users to install user-selected pull-down resistors

communicate with memory containing identification and

(e.g. to convert a 4-20 mA loop to 0-4 volts), or a selected

portable data transfer devices. Several temperature

pull-up resistor (e.g. to power a sensor such as a thermis-

transducers and other simple line-powered contact

tor or resistive level sensor). A series protection resistor

closure sensors and I/O devices also use this protocol, and

also acts as the top resistor in a voltage divider network

devices have a unique 64 bit ROM code laser-etched into

which can extend the 0-4.092 volt range to, say, 0-10 or 0-

the chip at time of manufacture. A number of devices,

40 volts. (The extended voltage range is set by a second

(e.g. transducers) can share a common line, with devices

divider resistor.) An optional capacitor can be installed to

being addressed using this ROM code match. The

filter noise from the ADC input, and clamp diodes to

protocol is supported by drivers in a number of C and

ground and Vcc protect the inputs against over-voltage.

BASIC compilers for the AVR mega CPU.

These four channels connect to screw terminals on the

To be compatible with this software, a single, unbuff-

card edge, with an associated ground and a switched Vcc

ered CPU pin is used bi-directionally, and a 1.5K pullup

on a terminal to power external sensors, etc.

and a series protection resistor are used to feed the line.

Channels 5...8 go to a 10-pin internal connector (acces- Diode clamps protect the line against ESD hits. Note:

sible if the lid in not installed, and the board is used in a while Dallas claim very long distances and hundreds of

larger case). This connector also has grounds for all chan- devices possible on the line with the 1-Wire protocol, in

nels, and ground and switched Vcc to allow an external practice, it would seem from the consensus of users, don’t

analog processing board to pre-process analog data before count on more than 10 to 20 metres of low-capacitance ca-

feeding it via a 10-way ribbon cable to these extra four ble drive ability, and don’t plan to use more than 10 sen-

channels. sors on a line. The Dallas application notes show all sorts

If these channels are not needed, plug-in pullups to Vcc of line conditioning (active, threshold-sensitive pullups,

can be installed via a resistor array, and this connector can slew rate controlled pull-downs, etc) to get the perform-

act as a user-jumper input for four option-select jumpers. ance they claim. In our opinion, longer distances are better

JED AVR585 Single Board Computer (Release 1, June 2001) 3

served with distributed RS485 or CAN remotes using and clamp diodes on all lines protect the board from volt-

low-end AVR CPUs, and using impedance-matched ca- ages up to 40 volts. The output FETs have clamp diodes.

bles able to go out to 4,000 feet.

Real Time Clock

General purpose I/O via Xilinx gate array So that the board knows what time it is, there is a RTC

A Spartan XL gate array with a range of capacities is an (Real Time Clock) connected to the CPU. It is a small se-

option on this board. Four different devices ranging from rial device which uses a common I/O pin and a clock line.

the XCS05XL to the XCS30XL can be loaded onto the The Dallas DS1302S is backed up from a lithium 3 volt

TQ100 pads on the board. They provide 100 CLBs (Con- battery, and will run from many years without needing

figurable Logic Blocks) with 200 flip-flops up to 575 board power (Timekeeping current is under 1 microamp

CLBs with 1,150 flip-flops, providing possibilities of over full temperature range, so a 200 mAH Lithium bat-

simple counters to complex multi-channel stepper motor tery will run it for 22 years, assuming the battery self-

drivers or 12 channels of 32 bit counters, or 6, 32-bit coun- discharge does not flatten it first.)

ters with quadrature decoding. RAM (Random Access

Memory) can even be created in this device, e.g. FIFO The clock has eight, 8-bit registers accessible individu-

(First-In-First-Out) stacks or buffers. ally or in a continuous burst. Registers are:

Schematic or VHDL based software to support the Seconds, Minutes, Hours, Date, Month, Day, Year

Spartan XL family is available at low cost from Xilinx or

their distributors worldwide. JED supplies schematics of Thirty-one bytes of battery backed RAM is also in this

the Xilinx internals in PDF form with a system, and is pre- device, which can be used for holding pointers to FLASH

pared to license Xilinx source code for users to design “next address”, etc. between logging cycles.

their own modifictions. JED also offers a custom design It is supported with drivers by the C compilers.

service for Xilinx patterns fulfilling customer’s needs for

added functionality on the board. NOTE: This board can function in a limited way with-

out the Xilinx, offering a CPU with three RS232 serial

These Xilinx devices are RAM based, and are loaded ports, four analog inputs (which can also be used a digital

via the CPU SPI port from the CPU FLASH memory inputs), two other digital inputs (or I2C), the 1-wire input

(where they are loaded as part of the used program, as a and the 8-way switch input.

data file, between 7K byte and 31K byte long. The CPU

has 128K byte of FLASH, so there is plenty left for pro- “Upstairs” expansion system ... more

grams). ports, speech, CAN

Standard I/O provided in the Gate Array A connector from the gate array, with power and

There are four, five-screw terminal connectors and an grounds allows users to design custom additional hard-

8-way switch along the lower edge of the AVR585: ware. 18 lines from the Xilinx allow for very flexible up-

stairs logic.

Connector 1 has four MDT3055 power N-channel

FETs, driven directly from the gate array. CPU port The CPU UART connects to the Xilinx, and so to the

PB4..PB7 lines can be routed to these lines inside the Xil- upstairs board. This allows serial devices on the upstairs

inx ... these lines are general purpose I/O lines on the board to communicate with the CPU, e.g. a GPS receiver,

CPU, but have special, optional functions as PWM (Pulse an opto-isolated RS485 interface, or a specialised modem

Width Modulation) outputs from counters 0, 1 and 2 e.g. for the HART protocol.

(Counter 1 has two sets of compare registers, so it handles In a similar way, the SPI interface can go upstairs, so

two channels with the one counter. SPI devices such as Real Time Clocks with alarms, Da-

Connector 2 and Connector 3 have either 4 inputs or 4 taFLASH memories, motor controllers with SPI, etc can

more FET outputs each. These connect to the gate array, be used.

allowing for I/O built into the gate array to drive the FETs For example:

or use these as inputs. These connectors can also be driven · Several megabytes of battery-backed RAM in 512K

from the “Upstairs” board, allowing I/O originating there byte SRAM chips can be added upstairs;

to connect to the outside world. (This is used by a sound · Several megabytes of DataFLASH memory can be

generating system upstairs). added, using Xilinx pins as chip selects. This can be

Connectors 4 is always inputs. They go into the Xil- combined with sound generating logic, allowing long

inx. This can be taken over by the optional I2C (or Two messages to be stored and “spoken”;

Wire Serial Interface Bus). · Additional communications interfaces:

The 8-way DIP switch allows users to set options or

· More UARTs for conventional serial interfaces;

variables directly to the board, e.g. node address in a net-

work, calibration options, diagnostic or calibration mode · Infrared communications logic;

selection, baud rates and com options, etc. · A CAN bus controller can be added using a Philips

All inputs above can be configured with pull-up resis- SJA1000 and a bus transceiver. This would take over

tors for switch or opto-isolator inputs, or can have pull- the RS485 screw terminals;

downs to ground, to accept voltage inputs. Series resistors · Motor-controllers for stepper motors, etc.

JED AVR585 Single Board Computer (Release 1, June 2001) 4

· Wherever your imagination takes you ... The combina- chip), and to send and receive bytes and to turn the trans-

tion of a reprogrammable Xilinx gate array and an ex- mitter on and off under interrupt.

tension add-on board makes the AVR585 a very flexi-

ble, expandable system. A CAN interface (on an Upstairs board) provides the

hardware for the controller, and JED code would provide

Note on protocols low level hardware drivers. These are only the first two

While the board might provide a variety of interfaces, layers of the seven layer stack. There are numerous CAN

be warned that communications via the hardware inter- protocols for the next 5 layers. Examples are: CAL, CAN

faces provided on this card involves a lot more than just Open (a free license protocol, but you must still buy the

the hardware. At JED, we normally provide example code specifications), PCAL, DeviceNet (originally Allen

for interfacing to the hardware to enable JED to test that Bradly, now ODVA) and SDS (trademarked by

hardware. This code shows typically how to actually get a Honeywell) to name just a few. Some, e.g. DeviceNet, re-

byte in and out of the hardware. However, JED does NOT quire a licence to be purchased from the author or copy-

offer the higher levels of a protocol. The ISO model di- right owner, sometimes costing many thousands of dol-

vides a protocol stack into 7 levels, and the JED hardware lars US, and then you still have to write or buy the code!

and low-level drivers are only the lower 1 or 2 levels in

this stack. Standby mode and power up control

These comments apply to all interfaces: A number of devices on this board can be commanded

An RS232 interface to, for example, communicate via to enter low-power mode.

a modem or packet radio system, involves making a call,

The MAX213E RS232 serial driver has a power con-

establishing a link to the remote end, passing one or more

trol pin, and an auxiliary pin on the dual UART controls

messages, verifying their safe arrival (and possibly

this power. Two receivers are active in powerdown, and

resending), receiving new commands, and then closing

these are fed from a RI (Ring Input) and DSR (data Set

down the link in an orderly way, after setting a future time

Ready) to signal an incoming call. The other two serial

for further contact. JED provides test code to set up the

ports are powered from the power rails generated by the

UARTs and send and receive bytes, and the C and BASIC

MAX213E, so they also power down when the

compiler writers typically provide sample interrupt

MAX213E closes down.

driven buffered serial coms examples; this is a long way

from, for example, packet radio protocols. These could be There is no alarm provided from the RTC...automatic

quite expensive to implement. power-up on alarm is not provided. Rather, the board can

An IR interface needs to understand the whole mes- enter low power mode, and the CPU restart is controlled

sage structure for infra-red communications, and if used by the watch-dog timer, which can then examine the RTC

for data transfer from data gathering device, for example, time and other I/O at rates from milliseconds to 2 second

needs to understand message delimiters, file structures, intervals.

flagging completed data transfer, and then erasure of This would be sufficient to answer a phone call or ex-

memory, clearing it for more data. ternal RS232 access on the DTE port within 2 seconds (or

An RS485 interface is not just an asynchronous bus for whatever the watch-dog is set to before powerdown).

data bytes ... all RS485 systems, because of their multiple- A switched 5-volt output allows the CPU to control

address structure, MUST always implement a protocol, so power up and down on sensors or other external equip-

that all nodes understand where in the data byte stream the ment connected to the board.

message starts, which are address bytes, which are com-

mand bytes, which are data bytes (and how the length is Power supply

set or controlled) and which are CRC check bytes. Also An LM2931 five volt, low dropout linear regulator on

data can be in ASCII or binary, and can use 9 bit flags for board supplies all devices except the RTC backup and

address bytes. One popular RS485 protocol is Modbus, Xilinx (This runs from a 3.3 volt smt regulator.) This is an

and the specification for this is freely available, with a no- automotive-rated device, with -50 volt reverse protection

cost license. Even this has ASCII and RTU modes. JED and +60 volt load dump protection. Quiescent current of

normally supplies code to enable the interface (connect- the whole system is estimated to be under 5 mA in standby

ing the CPU UART in the gate array to the RS485 TX/RX and under 60mA in full speed mode.

JED AVR585 Single Board Computer (Release 1, June 2001) 5

You might also like

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Linux CommandsDocument6 pagesLinux Commandsajha_264415No ratings yet

- Techlog 2018-2 SynchronizationTool DeploymentGuideDocument20 pagesTechlog 2018-2 SynchronizationTool DeploymentGuidec_b_umashankarNo ratings yet

- Security+ Study Guide Better VersionDocument61 pagesSecurity+ Study Guide Better VersionalNo ratings yet

- Lab #8Document9 pagesLab #8Mitch FishbeinNo ratings yet

- LPI101Document6 pagesLPI101ammarkurdNo ratings yet

- Technology and Livelihood EducationDocument56 pagesTechnology and Livelihood EducationDerick B. PicardoNo ratings yet

- Movie Ticket Booking System Project ReportDocument22 pagesMovie Ticket Booking System Project Reportsrbehera2022No ratings yet

- Servinst 7703Document436 pagesServinst 7703Renato MarchesaniNo ratings yet

- WIBU protection knuth20 implementation analysisDocument7 pagesWIBU protection knuth20 implementation analysisgman444No ratings yet

- PriceDocument83 pagesPriceDiah PitalokaNo ratings yet

- Best Practices To Improve ASP - Net Web Application PerformanceDocument15 pagesBest Practices To Improve ASP - Net Web Application PerformanceNarendranNo ratings yet

- Rubrik For Oracle and Microsoft SQL Sever DSDocument2 pagesRubrik For Oracle and Microsoft SQL Sever DSPaul CondoNo ratings yet

- Xer Schedule Toolkit Manual PDFDocument33 pagesXer Schedule Toolkit Manual PDFringlove97No ratings yet

- EnggRoom Code Ad Hoc Wireless NetworkDocument39 pagesEnggRoom Code Ad Hoc Wireless Networkمعراج الرحمانNo ratings yet

- Archive Server Installation GuideDocument3 pagesArchive Server Installation GuideAdriel Ronald CaumbanNo ratings yet

- BLK MD BC04 B SpehhficationDocument11 pagesBLK MD BC04 B SpehhficationadelinatapuNo ratings yet

- Dash7 Alliance Mode Technical PresentationDocument23 pagesDash7 Alliance Mode Technical Presentationaj4fall086050No ratings yet

- 8086 MicroprocessorDocument48 pages8086 MicroprocessorRajaganapathi RajappanNo ratings yet

- BULUDocument14 pagesBULUCarol Fernandez Rivera AbellaNo ratings yet

- Active Directory, DNS, DHCP Q & AnsDocument53 pagesActive Directory, DNS, DHCP Q & AnsSudhir Maherwal100% (3)

- Oracle9i: Advanced PL/SQL: Student GuideDocument10 pagesOracle9i: Advanced PL/SQL: Student GuidevineetNo ratings yet

- DL-PN1 (IL) : User's ManualDocument36 pagesDL-PN1 (IL) : User's ManualSandu RaduNo ratings yet

- Jan p3Document16 pagesJan p3Kabir SinghNo ratings yet

- ePO 4.5 and 4.6 Server Backup and Disaster Recovery ProcedureDocument8 pagesePO 4.5 and 4.6 Server Backup and Disaster Recovery ProcedureRAJESHNo ratings yet

- Motherboard Manual 7vt600 RZ (C) eDocument40 pagesMotherboard Manual 7vt600 RZ (C) eАндрей КульковNo ratings yet

- Role Based Access Controls - How Cloud ERP Builds on EBS FoundationDocument34 pagesRole Based Access Controls - How Cloud ERP Builds on EBS FoundationManoj Sharma100% (1)

- CS 159 - Spring 2021 - Lab #9: Contact PriorDocument5 pagesCS 159 - Spring 2021 - Lab #9: Contact PriorKim Jong UnNo ratings yet

- Practice Problems for Bit-oriented Protocols LectureDocument39 pagesPractice Problems for Bit-oriented Protocols LectureRizwan Aslam ButtNo ratings yet

- Mobile Computing Lecture NotesDocument312 pagesMobile Computing Lecture Notessen19841No ratings yet

- Microprocessor Interfacing & Embedded System CSE 331/EEE 332/EEE 453/ETE 332 Summer 2020 Faculty: RSFDocument6 pagesMicroprocessor Interfacing & Embedded System CSE 331/EEE 332/EEE 453/ETE 332 Summer 2020 Faculty: RSFRifat HossainNo ratings yet