Professional Documents

Culture Documents

Department: Cse Subject Code & Subject: Cs6201 Digital Principles and System Design Year/Semester: I/II Name of The Faculty Member: Mr.S.MANIKANDAN

Uploaded by

ManiKandan Subbu0 ratings0% found this document useful (0 votes)

16 views2 pagesdigital electronics course plan

Original Title

Digital Cp

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentdigital electronics course plan

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

16 views2 pagesDepartment: Cse Subject Code & Subject: Cs6201 Digital Principles and System Design Year/Semester: I/II Name of The Faculty Member: Mr.S.MANIKANDAN

Uploaded by

ManiKandan Subbudigital electronics course plan

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 2

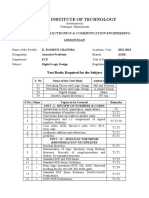

Pandian Saraswathi Yadav Engineering College

Arasanoor ,Sivagangai – 630561

Department of Electronics and Communication Engineering

Course Plan

Department : CSE

Subject Code & Subject : CS6201 DIGITAL PRINCIPLES AND SYSTEM DESIGN

Year/Semester : I/II

Name of the faculty Member: Mr.S.MANIKANDAN

Text and Reference Books

SI.No Title of the book Author(s) Publications

Morris Mano M. and IV Edition, Pearson

T1 Digital Design

Michael D. Ciletti Education, 2008.

Fourth Edition, Pearson

Digital Design Principles and Education,

R1 John F. Wakerly,

Practices

2007.

Fifth Edition – Jaico

R2 Fundamentals of Logic Design Charles H. Roth Jr Publishing House,

Mumbai, 2003.

R3 Digital Principles and Design Donald D. Givone Tata Mcgraw Hill, 2003.

Oxford University Press,

R4 Digital Electronics Kharate G. K.

2010

Lecture Page Numbers of

Topic to be taught

No Text book

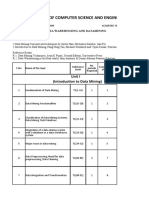

I - BOOLEAN ALGEBRA AND LOGIC GATES

1. Review of Number Systems T1(3-9)

2. Arithmetic Operations T1(13-24)

3. Binary Codes, Boolean Algebra andTheorems T1(35-41)

4. Boolean Functions T1(42-46)

5. Simplification of Boolean Functions using Karnaugh Map T1(46-50)

6. Tabulation Methods T1(51-55)

7. Logic Gates T1(55-60)

8. NAND Implementations T1(87-92)

9. NOR Implementations T1(92-94)

II-COMBINATIONAL LOGIC

10. Combinational Circuits T1(135-136)

11. Analysis and Design Procedures T1(136-142)

12. Circuits for Arithmetic Operations T1(143-154)

13. CodeConversion T1(17-24)

14. Decoders and Encoders T1(162-168)

15. Multiplexers and Demultiplexers T1(168-174)

16. Introduction to HDL T1(174-179)

17. HDL Models of Combinational circuits T1(180-185)

18. HDL Models of Combinational circuits T1(186-190)

III-SYNCHRONOUS SEQUENTIAL LOGIC

19. Sequential Circuits T1(197-199)

20. Latches T1(199-203)

21. Flip Flops T1(203-210)

22. Analysis and Design Procedures T1(210-221)

23. State Reductionand State Assignment T1(233-239)

24. Shift Registers T1(255-267)

25. Counters T1(268-293)

26. HDL for Sequential Logic Circuits T1(221-232)

27. HDL for Sequential Logic Circuits. T1(293-298)

IV-ASYNCHRONOUS SEQUENTIAL LOGIC

28. Analysis of Asynchronous Sequential Circuits T1(434-443)

29. Design of Asynchronous Sequential Circuits T1(443-446)

30. Analysis and Design of Asynchronous Sequential Circuits T1(446-453)

31. Reduction of State and Flow Tables T1(453-457)

32. Reduction of State and Flow Tables T1(457-460)

33. Reduction of State and Flow Tables T1(461-464)

34. Race-free State Assignment T1(464-469)

35. Hazards T1(469-473)

36. Hazards T1(473-474)

V-MEMORY AND PROGRAMMABLE LOGIC

37. RAM T1(308-314)

38. ROM T1(322-328)

39. Memory Decoding T1(314-319)

40. Error Detection and Correction T1(319-322)

41. Programmable Logic Array T1(328-332)

42. Programmable Array Logic T1(332-336)

43. Sequential Programmable Devices T1(336-339)

44. Sequential Programmable Devices T1(339-344)

45. Application Specific IntegratedCircuits T1(344-351)

Signature of faculty member Signature of HOD Signature of Principal

You might also like

- Basic Digital Signal Processing: Butterworths Basic SeriesFrom EverandBasic Digital Signal Processing: Butterworths Basic SeriesRating: 5 out of 5 stars5/5 (1)

- Digital Communication: Department of EceDocument4 pagesDigital Communication: Department of EceJefferson ThompsonNo ratings yet

- DLD LPDocument2 pagesDLD LPRameshchandra K ECENo ratings yet

- Lesson Plan Electrical Circuits 2Document3 pagesLesson Plan Electrical Circuits 2Sunny RoyalNo ratings yet

- School of Engineering and Technology (SET) : DEPARTMENT OF - Lesson PlanDocument3 pagesSchool of Engineering and Technology (SET) : DEPARTMENT OF - Lesson PlanSachin Kumar SinghNo ratings yet

- Anna University:: Chennai 600 025 Curriculum 2004 B.Tech. Information Technology Semester Iii Code No. Course Title L T P M TheoryDocument39 pagesAnna University:: Chennai 600 025 Curriculum 2004 B.Tech. Information Technology Semester Iii Code No. Course Title L T P M TheorySutha BalaNo ratings yet

- Vlsidt Syllabus Detailing - 2k15-CourseDocument2 pagesVlsidt Syllabus Detailing - 2k15-CoursevinodNo ratings yet

- Cs8251 Lesson PlanDocument2 pagesCs8251 Lesson Planshajitha120450% (2)

- EE227 - Course Outline v.00.00.00 - 2018-12-20Document2 pagesEE227 - Course Outline v.00.00.00 - 2018-12-20Muhammad Akif NaeemNo ratings yet

- NWS LP 23Document3 pagesNWS LP 23poornimaNo ratings yet

- Gujarat Technological University: Semester - III Subject Name: Digital ElectronicsDocument3 pagesGujarat Technological University: Semester - III Subject Name: Digital ElectronicsBhargavsinh ParmarNo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument26 pagesChhattisgarh Swami Vivekanand Technical University, BhilaiSK BeharNo ratings yet

- Btech Syllabus Copy2 LatestDocument152 pagesBtech Syllabus Copy2 LatestShivam VishwakarmaNo ratings yet

- Embedded Systems Session Plan DIV B 2019-20Document5 pagesEmbedded Systems Session Plan DIV B 2019-20JeyavelNo ratings yet

- 2020 BTech Syllabus Part IDocument24 pages2020 BTech Syllabus Part IVivekNo ratings yet

- BEC Curriculum Syllabus 2019-20 24-06-2020 NewDocument178 pagesBEC Curriculum Syllabus 2019-20 24-06-2020 NewadityavarmanNo ratings yet

- R2004 (3-8 Sem IT)Document81 pagesR2004 (3-8 Sem IT)yedandanakkaNo ratings yet

- Lecture Schedule CS6008 Human Computer InteractionDocument2 pagesLecture Schedule CS6008 Human Computer Interactionsubbulakshmi VNo ratings yet

- Department of Computer Science and Engineering: Unit I (Introduction To Data Mining)Document10 pagesDepartment of Computer Science and Engineering: Unit I (Introduction To Data Mining)K VENKATA SRAVANINo ratings yet

- Courseplan OoadDocument3 pagesCourseplan OoadbazilabanuNo ratings yet

- Data Structures Unit 2 NotesDocument51 pagesData Structures Unit 2 NotesSandeepNo ratings yet

- DICADocument2 pagesDICAak5775No ratings yet

- St. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanDocument11 pagesSt. Peter'Scollege of Engineeering and Technology Department of Eee Lesson PlanRaj Bharath Raju100% (1)

- 10 ICT - English Medium - FinalDocument10 pages10 ICT - English Medium - Finalthusharagomas18No ratings yet

- STLDDocument2 pagesSTLDPrasanth VarasalaNo ratings yet

- 2.digital ElectronicsDocument9 pages2.digital ElectronicsanupNo ratings yet

- Lec - A-01 - Number Systems and CodesDocument97 pagesLec - A-01 - Number Systems and Codescys96No ratings yet

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- Page 1 of 2: W.E.F. AY 2018-19Document2 pagesPage 1 of 2: W.E.F. AY 2018-19Jenny BhadouriyaNo ratings yet

- (Second Year) B.Tech (Computer Science & Engineering) : Proposed Curricula and Syllabi FORDocument12 pages(Second Year) B.Tech (Computer Science & Engineering) : Proposed Curricula and Syllabi FORSneheet MishraNo ratings yet

- Btech Cse 3 SEMDocument88 pagesBtech Cse 3 SEMDevil EvilNo ratings yet

- 4) Model Question Bank - SPDocument14 pages4) Model Question Bank - SPSanobar ShaikhNo ratings yet

- Dynamics of Linear Systems PDFDocument3 pagesDynamics of Linear Systems PDFBhautik Daxini100% (2)

- Mids MergedDocument420 pagesMids Mergedsourish.ambatiNo ratings yet

- Up & Uc - LessonPlanDocument2 pagesUp & Uc - LessonPlanKannan AlagumuthiahNo ratings yet

- BEC Curriculum Syllabus 2017-18 2018-19 24-06-2020 NewDocument169 pagesBEC Curriculum Syllabus 2017-18 2018-19 24-06-2020 NewswethaNo ratings yet

- EC 2012-2016 Course Structure and ContentsDocument20 pagesEC 2012-2016 Course Structure and ContentsHari Sankar SNo ratings yet

- Even Semester Syllabus-ICTDocument30 pagesEven Semester Syllabus-ICTemailidtofoolNo ratings yet

- 2.20RO2001 - DE & MicroprocessorsDocument5 pages2.20RO2001 - DE & MicroprocessorsRaj PNo ratings yet

- BTechCSE CurriculumDocument4 pagesBTechCSE CurriculumAnmol PawaNo ratings yet

- $warnandhira: Vlsi SimulationDocument3 pages$warnandhira: Vlsi SimulationRamarao BNo ratings yet

- CS 302 - Section A - IT - 3rd - 2nd - 2018-12-173313633 - 101100206 - PdfjoinerDocument6 pagesCS 302 - Section A - IT - 3rd - 2nd - 2018-12-173313633 - 101100206 - PdfjoinersrihariharalakshmiNo ratings yet

- Daa LPDocument3 pagesDaa LPrajaNo ratings yet

- SYLLABUS Ece PG Commn Sys2013 14Document49 pagesSYLLABUS Ece PG Commn Sys2013 14Ashwin RajaratnamNo ratings yet

- CSE 3rd Sem SyllabusDocument13 pagesCSE 3rd Sem SyllabusAryan RajNo ratings yet

- M. Tech - Communication Systems (Full Time) Curriculum & Syllabus (2015-2016 & Onwards)Document60 pagesM. Tech - Communication Systems (Full Time) Curriculum & Syllabus (2015-2016 & Onwards)Anonymous IjquQOmNo ratings yet

- 2.digital Electronics TheoryDocument15 pages2.digital Electronics TheoryYash KuncolienkerNo ratings yet

- Electronics & Communication EngineeringDocument6 pagesElectronics & Communication Engineeringvikram_bansal_5No ratings yet

- ECE 6th Sem SyllabusDocument7 pagesECE 6th Sem SyllabusHarsh KumarNo ratings yet

- G11 Eng MCQ 2023 T2Document6 pagesG11 Eng MCQ 2023 T2thamalieariyarathnaNo ratings yet

- Syllabi Special Computer Full 17E and Above Nov2020Document88 pagesSyllabi Special Computer Full 17E and Above Nov2020Vinodh LahiruNo ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- CENG250-Syllabus-Summer 2021Document3 pagesCENG250-Syllabus-Summer 2021medo.miso.2000No ratings yet

- BTech CSEDocument28 pagesBTech CSEKaushalPranavNo ratings yet

- 204184: Data Structures and Algorithms: SR - No Topic Reference Book UNIT I: Introduction To C and AlgorithmDocument3 pages204184: Data Structures and Algorithms: SR - No Topic Reference Book UNIT I: Introduction To C and Algorithmmadhuri nimseNo ratings yet

- DPCO Syllabus (Theory Cum Practical)Document2 pagesDPCO Syllabus (Theory Cum Practical)yogeshwaran.r2022lcseNo ratings yet

- 3rd Sem PDFDocument12 pages3rd Sem PDFHItesh PatreNo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument22 pagesChhattisgarh Swami Vivekanand Technical University, Bhilaibheshram janghelNo ratings yet

- CS 4th Semester SyllabusDocument13 pagesCS 4th Semester SyllabusManish KumarNo ratings yet

- Jul21 SemesterfeecircularDocument1 pageJul21 SemesterfeecircularManiKandan SubbuNo ratings yet

- Deep Learning For Image Analysis FDP BROCHURE Final - 20 07 2021Document2 pagesDeep Learning For Image Analysis FDP BROCHURE Final - 20 07 2021ManiKandan SubbuNo ratings yet

- EC 6702 Ocn Two MarksDocument24 pagesEC 6702 Ocn Two MarksManiKandan SubbuNo ratings yet

- Synchronization Techniques For Digital Receivers: Printed BookDocument1 pageSynchronization Techniques For Digital Receivers: Printed BookManiKandan SubbuNo ratings yet

- ZSpark F5 CE 201-203 PDFDocument6 pagesZSpark F5 CE 201-203 PDFmosabalintoNo ratings yet

- 5 HUAWEI BTS3012 Hardware StructureDocument138 pages5 HUAWEI BTS3012 Hardware Structuresharkae100% (1)

- Ep3050 SMDocument551 pagesEp3050 SMadjustmentNo ratings yet

- MHADA Investigation ReportDocument12 pagesMHADA Investigation Reportkuldip purohitNo ratings yet

- Os D201Document92 pagesOs D201jacmgmorgan100% (1)

- Problems 6 Circuit WileyDocument29 pagesProblems 6 Circuit WileyHelloWorldNo ratings yet

- Trunking Radio System TETRADocument21 pagesTrunking Radio System TETRAMihsah Exttreme50% (2)

- LSMV-M1000 e 161031Document40 pagesLSMV-M1000 e 161031Escalera EuropeaNo ratings yet

- Ups Part 2Document5 pagesUps Part 2NeztopNo ratings yet

- Paper - 062 - INTEGRATION OF SOLAR PHOTOVOLTAIC DISTRIBUTED GENERATION IN NIGERIAN POWER SYSTEM NETWORKDocument6 pagesPaper - 062 - INTEGRATION OF SOLAR PHOTOVOLTAIC DISTRIBUTED GENERATION IN NIGERIAN POWER SYSTEM NETWORKabera alemayehuNo ratings yet

- Training Progress Report - Comms (14May-29June)Document47 pagesTraining Progress Report - Comms (14May-29June)Tawanda Daniel DenguNo ratings yet

- Chapter 1: Basic Concepts: Today's ObjectivesDocument16 pagesChapter 1: Basic Concepts: Today's ObjectivesWan RodieNo ratings yet

- SINAMICS G150 Converter Cabinet Units en-USDocument770 pagesSINAMICS G150 Converter Cabinet Units en-USAncaOniscu100% (1)

- Apexi V-Afc II ManualDocument64 pagesApexi V-Afc II ManualsaM aS100% (4)

- PROANNOUNCE Software ManualDocument218 pagesPROANNOUNCE Software ManualViktor GrgurićNo ratings yet

- Impedance Spectroscopy and Experimental SetupDocument18 pagesImpedance Spectroscopy and Experimental SetupJako SibueaNo ratings yet

- ATO Voltage Sensor CatalogDocument9 pagesATO Voltage Sensor CatalogCrazyGamer SLNo ratings yet

- 3 DB Branch-Line Coupler With Improved Bandwidth Using PDMS and Zo Ex ConductorDocument5 pages3 DB Branch-Line Coupler With Improved Bandwidth Using PDMS and Zo Ex ConductorkamranishfaqNo ratings yet

- Application of Wavelet Transform For Fault Diagnosis in Rotating MachineryDocument6 pagesApplication of Wavelet Transform For Fault Diagnosis in Rotating MachinerySaeed JavdaniNo ratings yet

- TN-101 SER System ArchitecturesDocument6 pagesTN-101 SER System ArchitecturesTARAKESHWARIRNo ratings yet

- Service Manual: HCD-D90AV/GR10AV/ RX100AVDocument88 pagesService Manual: HCD-D90AV/GR10AV/ RX100AVConcret SlavaNo ratings yet

- Weidmuller PRO RTD Signal Isolators ConvertersDocument3 pagesWeidmuller PRO RTD Signal Isolators ConvertersFernando NunesNo ratings yet

- E 0 A 6Document4 pagesE 0 A 6EdNo ratings yet

- C&D KCR Manual PDFDocument6 pagesC&D KCR Manual PDFSteven MarksNo ratings yet

- Pressure SwitchDocument2 pagesPressure Switchayyaz123No ratings yet

- Module 3 - OscillatorsDocument36 pagesModule 3 - OscillatorsTanvi DeoreNo ratings yet

- Sport & Fitness User Manual MultiDocument185 pagesSport & Fitness User Manual MultibeoNo ratings yet

- MemristorsDocument26 pagesMemristorsLord_JoelNo ratings yet

- Ia Ha 2Document4 pagesIa Ha 2Er Shubham RaksheNo ratings yet

- Emotron Fdu2 0 - Manual - 01 5325 01r5.enDocument270 pagesEmotron Fdu2 0 - Manual - 01 5325 01r5.enImran Ullah KhanNo ratings yet