Professional Documents

Culture Documents

Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational Amplifier

Uploaded by

Alexandre CorreaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational Amplifier

Uploaded by

Alexandre CorreaCopyright:

Available Formats

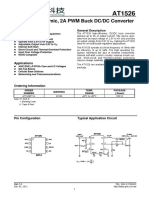

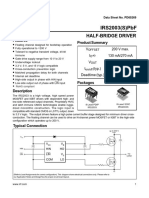

DATASHEET

CA3420 FN1320

0.5MHz, Low Supply Voltage, Low Input Current BiMOS Operational Amplifier Rev 9.00

Oct 4, 2005

The CA3420 is an integrated circuit operational amplifier that Features

combines PMOS transistors and bipolar transistors on a

single monolithic chip. The CA3420 BiMOS operational • 2V Supply at 300A Supply Current

amplifier features gate protected PMOS transistors in the • 1pA Input Current (Typ) (Essentially Constant to 85°C)

input circuit to provide very high input impedance, very low

• Rail-to-Rail Output Swing (Drive 2mA into 1k Load)

input currents (less than 1pA). The internal bootstrapping

network features a unique guardbanding technique for • Pin Compatible with 741 Operational Amplifiers

reducing the doubling of leakage current for every 10°C • Pb-Free Plus Anneal Available (RoHS Compliant)

increase in temperature. The CA3420 operates at total

supply voltages from 2V to 20V either single or dual supply. Applications

This operational amplifier is internally phase compensated to

achieve stable operation in the unity gain follower • pH Probe Amplifiers

configuration. Additionally, it has access terminals for a • Picoammeters

supplementary external capacitor if additional frequency roll-

• Electrometer (High Z) Instruments

off is desired. Terminals are also provided for use in

applications requiring input offset voltage nulling. The use of • Portable Equipment

PMOS in the input stage results in common mode input • Inaccessible Field Equipment

voltage capability down to 0.45V below the negative supply

terminal, an important attribute for single supply application. • Battery-Dependent Equipment (Medical and Military)

The output stage uses a feedback OTA type amplifier that

can swing essentially from rail-to-rail. The output driving

Functional Diagram

current of 1.5mA (Min) is provided by using nonlinear current

mirrors.

X1

Ordering Information

PART PART TEMP. PKG.

NUMBER MARKING RANGE (°C) PACKAGE DWG. # -

CA3420E CA3420E -55 to 125 8 Ld PDIP E8.3 MOS

BIPOLAR

CA3420EZ CA3420EZ -55 to 125 8 Ld PDIP* E8.3 MOS

+ BIPOLAR

(Note) (Pb-free)

*Pb-free PDIPs can be used for through hole wave solder

processing only. They are not intended for use in Reflow solder

processing applications. X1

NOTE: Intersil Pb-free plus anneal products employ special

Pb-free material sets; molding compounds/die attach materials and

100% matte tin plate termination finish, which are RoHS compliant BUFFER AMPS;

and compatible with both SnPb and Pb-free soldering operations. BOOTSTRAPPED HIGH GAIN OTA BUFFER

INPUT PROTECTION (50K) (X2)

Intersil Pb-free products are MSL classified at Pb-free peak reflow

NETWORK

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

Pinout

CA3420 (PDIP)

TOP VIEW

OFFSET NULL 1 8 STROBE

INV.

2 7 V+

INPUT -

NON-INV. +

3 6 OUTPUT

INPUT

V- 4 5 OFFSET NULL

FN1320 Rev 9.00 Page 1 of 5

Oct 4, 2005

CA3420

Absolute Maximum Ratings Thermal Information

Supply Voltage (V+ to V-). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22V Thermal Resistance (Typical, Note 2) JA (°C/W) JC (°C/W)

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15V PDIP Package* . . . . . . . . . . . . . . . . . . 105 N/A

DC Input Voltage . . . . . . . . . . . . . . . . . . . . . . (V+ + 8V) to (V- -0.5V) Maximum Junction Temperature (Plastic Package) . . . . . . . 150°C

Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1mA Maximum Storage Temperature Range . . . . . . . . . . -65°C to 150°C

Output Short Circuit Duration (Note 1). . . . . . . . . . . . . . . . Indefinite Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300°C

Operating Conditions *Pb-free PDIPs can be used for through hole wave solder processing

only. They are not intended for use in Reflow solder processing

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -55°C to 125°C

applications.

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Short circuit may be applied to ground or to either supply.

2. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications Typical Values Intended Only for Design Guidance, VSUPPLY = 10V, TA = 25°C

PARAMETER SYMBOL TEST CONDITIONS TYP UNITS

Input Resistance RI 150 T

Input Capacitance CI 4.9 pF

Output Resistance RO 300

Equivalent Input Noise Voltage eN f = 1kHz RS = 100 62 nV/Hz

f = 10kHz 38 nV/Hz

Short-Circuit Current Source IOM+ 2.6 mA

To Opposite Supply Sink IOM- 2.4 mA

Gain Bandwidth Product fT 0.5 MHz

Slew Rate SR 0.5 V/s

Transient Response Rise Time tR RL = 2k, CL = 100pF 0.7 s

Overshoot OS 15 %

Current from Terminal 8 To V- I8+ 20 A

To V+ I8- 2 mA

Electrical Specifications For Equipment Design, At VSUPPLY = 1V, TA = 25°C, Unless Otherwise Specified

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Input Offset Voltage |VIO| - 5 10 mV

Input Offset Current (Note 3) |IIO| - 0.01 4 pA

Input Current (Note 3) |II| - 1 5 pA

Large Signal Voltage Gain AOL RL = 10k 10 100 - kV/V

80 100 - dB

Common Mode Rejection Ratio CMRR - 560 1800 V/V

55 65 - dB

Common Mode Input Voltage Range VlCR+ 0.2 0.5 - V

VlCR- - -1.3 - V

Power Supply Rejection Ratio PSRR VIO/V - 100 1000 V/V

60 80 - dB

Max Output Voltage VOM+ RL = 0.90 0.95 - V

VOM- -0.85 -0.91 - V

Supply Current I+ - 350 650 A

Device Dissipation PD - 0.7 1.1 mW

Input Offset Voltage Temperature Drift VlO/T - 4 - V/°C

NOTE:

3. The maximum limit represents the levels obtainable on high speed automatic test equipment. Typical values are obtained under laboratory conditions.

FN1320 Rev 9.00 Page 2 of 5

Oct 4, 2005

CA3420

Electrical Specifications For Equipment Design, at VSUPPLY = 10V, TA = 25°C, Unless Otherwise Specified

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Input Offset Voltage |VIO| - 5 10 mV

Input Offset Current (Note 4) |IIO| - 0.03 4 pA

Input Current (Note 4) |II| - 0.05 5 pA

Large Signal Voltage Gain AOL RL = 10k 10 100 - kV/V

80 100 - dB

Common Mode Rejection Ratio CMRR - 100 320 V/V

70 80 - dB

Common Mode Input Voltage Range VlCR+ 8.5 9.3 - V

VlCR- -10 -10.3 - V

Power Supply Rejection Ratio PSRR VIO/V - 32 320 V/V

70 90 - dB

Max Output Voltage VOM+ RL = 9.7 9.9 - V

VOM- -9.7 -9.85 - V

Supply Current I+ - 450 1000 A

Device Dissipation PD - 9 14 mW

Input Offset Voltage Temperature Drift VlO/T - 4 - V/°C

NOTE:

4. The maximum limit represents the levels obtainable on high speed automatic test equipment. Typical values are obtained under laboratory conditions.

Typical Applications

10G 10pF

+1.5V

Picoammeter Circuit

500-0-500

2 - 7

The exceptionally low input current (typically 0.2pA) makes 1M 10M

A

the CA3420 highly suited for use in a picoammeter circuit. CA3420 6 M

With only a single 10G resistor, this circuit covers the range 3 + 4 50pA

1.5k

from 1.5pA. Higher current ranges are possible with suitable 5

BATTERY

1 1.5k, 1%

switching techniques and current scaling resistors. Input RETURNS 15pA

10k 1k

transient protection is provided by the 1M resistor in series

430, 1%

with the input. Higher current ranges require that this resistor 5pA

be reduced. The 10M resistor connected to pin 2 of the

-1.5V 150, 1%

CA3420 decouples the potentially high input capacitance 1.5pA

often associated with lower current circuits and reduces the

tendency for the circuit to oscillate under these conditions. 11k 68

1%

High Input Resistance Voltmeter

FIGURE 1. PICOAMMETER CIRCUIT

Advantage is taken of the high input impedance of the CA3420

in a high input resistance DC voltmeter. Only two 1.5V “AA” +1.5V

type penlite batteries power this exceedingly high-input 500-0-500

3 + 7

A

resistance (>1,000,000M) DC voltmeter. Full-scale deflection 22M 10M

CA3420 6 M

is 500mV, 150mV, and 15mV. Higher voltage ranges are 100pF

2 - 4 500mV 1.5k

easily added with external input voltage attenuator networks. 5

1 BATTERY

The meter is placed in series with the gain network, thus RETURNS 1.5k, 1%

10k 150mV

eliminating the meter temperature coefficient error term. 1k

Supply current in the standby position with the meter 430, 1%

50mV

undeflected is 300A. At full-scale deflection this current -1.5V

rises to 800A. Carbon-zinc battery life should be in excess 150, 1%

15mV

of 1,000 hours.

68

1.1k 1%

FIGURE 2. HIGH INPUT RESISTANCE VOLTMETER

FN1320 Rev 9.00 Page 3 of 5

Oct 4, 2005

CA3420

Typical Performance Curves

10

INPUT & OUTPUT VOLTAGE EXCURSIONS FROM THE

OUTPUT STAGE TRANSISTOR SATURATION

1.0 TA = 25°C

POSITIVE AND NEGATIVE SUPPLY VOLTAGE (V)

TA = 25°C V- = 0V

0.8 RL = 100k

V+ = 2V

0.6

V+ = 5V

VOLTAGE, Q19 (mV)

0.4 V+ = 10V

V+ = 20V

0.2 V O-

100

0

VO+

-0.2

-0.4 VICR-

-0.6

VICR+

-0.8

1000

-1.0 0.01 0.1 1 10

0 1 5 10 15

LOAD (SOURCING) CURRENT (mA)

SUPPLY VOLTAGE (V)

FIGURE 3. OUTPUT VOLTAGE SWING AND COMMON MODE FIGURE 4. OUTPUT VOLTAGE vs LOAD SOURCING CURRENT

INPUT VOLTAGE RANGE vs SUPPLY VOLTAGE

1000 1000

EQUIVALENT INPUT NOISE VOLTAGE (nV/Hz)

TA = 25°C

OUTPUT STAGE TRANSISTOR SATURATION

TA = 25°C

V+ = 0V VS = 10V

VS = 5V

VS = 1V

VOLTAGE, Q17 (mV)

100

V- = -20V

V- = -10V

100 V- = -5V

V- = -2V

10

10 1

0.01 0.1 1 10

101 102 103 104 105 106

LOAD (SINKING) CURRENT (mA) FREQUENCY (Hz)

FIGURE 5. OUTPUT VOLTAGE vs LOAD SINKING CURRENT FIGURE 6. INPUT NOISE VOLTAGE vs FREQUENCY

TA = 25°C

OPEN LOOP PHASE (DEGREES)

VS = 5V

100 RL = 10k

CL = 0pF

0

OPEN LOOP VOLTAGE GAIN (dB)

80 -45

-90

60 -135

-180

40

20

0

1 101 102 103 104 105 106

FREQUENCY (Hz)

FIGURE 7. OPEN LOOP GAIN AND PHASE SHIFT RESPONSE

FN1320 Rev 9.00 Page 4 of 5

Oct 4, 2005

CA3420

Dual-In-Line Plastic Packages (PDIP)

N

E8.3 (JEDEC MS-001-BA ISSUE D)

8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

E1

INDEX INCHES MILLIMETERS

AREA 1 2 3 N/2

SYMBOL MIN MAX MIN MAX NOTES

-B-

A - 0.210 - 5.33 4

-A-

D E A1 0.015 - 0.39 - 4

BASE A2 0.115 0.195 2.93 4.95 -

PLANE A2

-C- A

SEATING

B 0.014 0.022 0.356 0.558 -

PLANE L C B1 0.045 0.070 1.15 1.77 8, 10

L

D1 A1 eA C 0.008 0.014 0.204 0.355 -

D1

B1 e D 0.355 0.400 9.01 10.16 5

eC C

B

eB D1 0.005 - 0.13 - 5

0.010 (0.25) M C A B S

E 0.300 0.325 7.62 8.25 6

NOTES: E1 0.240 0.280 6.10 7.11 5

1. Controlling Dimensions: INCH. In case of conflict between

e 0.100 BSC 2.54 BSC -

English and Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982. eA 0.300 BSC 7.62 BSC 6

3. Symbols are defined in the “MO Series Symbol List” in Section eB - 0.430 - 10.92 7

2.2 of Publication No. 95. L 0.115 0.150 2.93 3.81 4

4. Dimensions A, A1 and L are measured with the package seated

N 8 8 9

in JEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protru- Rev. 0 12/93

sions. Mold flash or protrusions shall not exceed 0.010 inch

(0.25mm).

6. E and eA are measured with the leads constrained to be per-

pendicular to datum -C- .

7. eB and eC are measured at the lead tips with the leads uncon-

strained. eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions.

Dambar protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3,

E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch

(0.76 - 1.14mm).

© Copyright Intersil Americas LLC 2000-2005. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN1320 Rev 9.00 Page 5 of 5

Oct 4, 2005

You might also like

- Ca 3260Document4 pagesCa 3260Carlos TibussiNo ratings yet

- Icl 7667Document11 pagesIcl 7667De JeanNo ratings yet

- Features: Dual, Low Power CMOS Operational AmplifiersDocument9 pagesFeatures: Dual, Low Power CMOS Operational AmplifiersDibya DeyNo ratings yet

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Document8 pagesINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNo ratings yet

- GS358 GlobaltechDocument9 pagesGS358 GlobaltechFlaviano Costa SilvaNo ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- CA5260, CA5260A: FeaturesDocument7 pagesCA5260, CA5260A: FeaturesCharbel TadrosNo ratings yet

- AT1526 GlobalMixed ModetechnologyDocument2 pagesAT1526 GlobalMixed ModetechnologyFafa MangstabNo ratings yet

- 2.5A Switch Step Down Switching Regulator: DescriptionDocument10 pages2.5A Switch Step Down Switching Regulator: DescriptionVictor CuaicalNo ratings yet

- Ca3290, Ca3290A: Bimos Dual Voltage Comparators With Mosfet Input, Bipolar OutputDocument8 pagesCa3290, Ca3290A: Bimos Dual Voltage Comparators With Mosfet Input, Bipolar OutputMultiAbderrahmaneNo ratings yet

- Jameco Part Number 1762453: Distributed byDocument7 pagesJameco Part Number 1762453: Distributed byIkram BalochNo ratings yet

- 1.5A Switch Step Down Switching Regulator: 1 General FeaturesDocument11 pages1.5A Switch Step Down Switching Regulator: 1 General FeaturesRene gNo ratings yet

- 2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesDocument14 pages2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesMaxNo ratings yet

- IRS4427Document19 pagesIRS4427ali ülküNo ratings yet

- Sy8008A/Sy8008B/Sy8008C: High Efficiency 1.5Mhz, 0.6A/1A/1.2A Synchronous Step Down RegulatorDocument5 pagesSy8008A/Sy8008B/Sy8008C: High Efficiency 1.5Mhz, 0.6A/1A/1.2A Synchronous Step Down RegulatorAnil BpsNo ratings yet

- Operacional de Alto GanhoDocument11 pagesOperacional de Alto Ganhorogerio pessanha dos santosNo ratings yet

- Ha 2542Document12 pagesHa 2542Charbel TadrosNo ratings yet

- Tv/Linear Applications RF & Microwave Transistors: Pin ConnectionDocument5 pagesTv/Linear Applications RF & Microwave Transistors: Pin ConnectionGabriel RacovskyNo ratings yet

- 12-Bit, Multiplying D/A Converter Features: Obso Lete Prod UCT Ible S Ubst Itute Prod UCT AD752 1Document8 pages12-Bit, Multiplying D/A Converter Features: Obso Lete Prod UCT Ible S Ubst Itute Prod UCT AD752 1sirosNo ratings yet

- Features: 12Mhz Rail-To-Rail Input-Output BufferDocument13 pagesFeatures: 12Mhz Rail-To-Rail Input-Output BufferЕвгений ИвановNo ratings yet

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 pagesRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNo ratings yet

- Unisonic Technologies Co., LTD: Vertical Deflection Output CircuitDocument5 pagesUnisonic Technologies Co., LTD: Vertical Deflection Output CircuitVinod kumarNo ratings yet

- TB67H451FNG: PWM Chopper Type DC Brushed Motor DriverDocument21 pagesTB67H451FNG: PWM Chopper Type DC Brushed Motor Drivermalak na3eemNo ratings yet

- Dual Operational Amplifiers: Product Description FeaturesDocument9 pagesDual Operational Amplifiers: Product Description FeaturesMendez VeronicaNo ratings yet

- TEA2025D: Unisonic Technologies Co., LTDDocument8 pagesTEA2025D: Unisonic Technologies Co., LTDFrank FullerNo ratings yet

- VHC32Document7 pagesVHC32quangNo ratings yet

- Features: CMOS Voltage ConvertersDocument12 pagesFeatures: CMOS Voltage ConvertersAlexNo ratings yet

- Wide Bandwidth Single J-Fet Operational Amplifier: LF151 LF251 - LF351Document9 pagesWide Bandwidth Single J-Fet Operational Amplifier: LF151 LF251 - LF351Charbel TadrosNo ratings yet

- Description Features: Ait Semiconductor IncDocument8 pagesDescription Features: Ait Semiconductor Incteranet tbtNo ratings yet

- 4 / Digit, BCD Output, A/D Converter Features: Data Sheet August 28, 2007Document15 pages4 / Digit, BCD Output, A/D Converter Features: Data Sheet August 28, 2007Erasmo Franco SNo ratings yet

- Irs2003 (S) PBF: Half-Bridge DriverDocument14 pagesIrs2003 (S) PBF: Half-Bridge DriverSundar RajanNo ratings yet

- Icl7667 1528911Document12 pagesIcl7667 1528911Trung Nguyên VõNo ratings yet

- Last Time Buy: 16-Bit Serial Input, Constant-Current Latched LED DriverDocument13 pagesLast Time Buy: 16-Bit Serial Input, Constant-Current Latched LED DriverDario Ochoa CoronelNo ratings yet

- MM58274CDocument16 pagesMM58274CThomasNo ratings yet

- TC5565Document9 pagesTC5565MiniLabNo ratings yet

- CA3140 DataSheetDocument23 pagesCA3140 DataSheetluisjeNo ratings yet

- LF153 LF253 - LF353: Wide Bandwidth Dual J-Fet Operational AmplifiersDocument2 pagesLF153 LF253 - LF353: Wide Bandwidth Dual J-Fet Operational AmplifiersKSNo ratings yet

- Integrated CircuitsDocument17 pagesIntegrated CircuitsmatbdyNo ratings yet

- TDA8359JDocument21 pagesTDA8359JCesar HernandezNo ratings yet

- Features: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifierDocument13 pagesFeatures: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifiersdasfaNo ratings yet

- STB 75 NF 75Document11 pagesSTB 75 NF 75costas1182No ratings yet

- TBD62304AFNG Datasheet en 20170324-1313625Document11 pagesTBD62304AFNG Datasheet en 20170324-1313625basheer almetwakelNo ratings yet

- BA6208Document4 pagesBA6208jcsg2007No ratings yet

- ISL6269 Data SheetDocument14 pagesISL6269 Data SheetSummer SpringNo ratings yet

- TS1117BDocument8 pagesTS1117BImonkNo ratings yet

- A4950 DatasheetDocument9 pagesA4950 DatasheetIndra KurniawanNo ratings yet

- TLO72CNDocument10 pagesTLO72CNx3roNo ratings yet

- MC14008B DDocument8 pagesMC14008B DAngela SilesNo ratings yet

- Features General Description: Stereo 2.7-W Audio Power Amplifier (With DC - Volume Control)Document25 pagesFeatures General Description: Stereo 2.7-W Audio Power Amplifier (With DC - Volume Control)iuri63No ratings yet

- tl082 N PDFDocument23 pagestl082 N PDFAnonymous fnO1X07No ratings yet

- TL082 Wide Bandwidth Dual JFET Input Operational Amplifier: Features DescriptionDocument25 pagesTL082 Wide Bandwidth Dual JFET Input Operational Amplifier: Features DescriptionAnghy GómezNo ratings yet

- TL074 - Datasheet - HKDocument10 pagesTL074 - Datasheet - HKkimbalsummers801No ratings yet

- EL7532 fn7435Document8 pagesEL7532 fn7435csclzNo ratings yet

- Features: 110Mhz, High Slew Rate, High Output Current BufferDocument12 pagesFeatures: 110Mhz, High Slew Rate, High Output Current BufferPepe ChorizoNo ratings yet

- GL-90 PSU - Power MOSFET Data SheetDocument13 pagesGL-90 PSU - Power MOSFET Data SheetLohidas PailaNo ratings yet

- ICL7611-1.4MHz, Low Power CMOS Operational AmplifiersDocument13 pagesICL7611-1.4MHz, Low Power CMOS Operational Amplifiersy0956880No ratings yet

- PM175 QuickStartDocument13 pagesPM175 QuickStartKasirNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- PGX184Document4 pagesPGX184Alexandre CorreaNo ratings yet

- GC17P Manual EngDocument210 pagesGC17P Manual EngAlexandre CorreaNo ratings yet

- Round2 Parts Replacement Request FormDocument2 pagesRound2 Parts Replacement Request FormAlexandre CorreaNo ratings yet

- U.S.S. Enterprise Command: BridgeDocument2 pagesU.S.S. Enterprise Command: BridgeAlexandre CorreaNo ratings yet

- Philips32phg5000TPM15.6L LADocument87 pagesPhilips32phg5000TPM15.6L LAJose100% (1)

- Plan PDFDocument3 pagesPlan PDFAlexandre CorreaNo ratings yet

- Philips32phg5000TPM15.6L LADocument87 pagesPhilips32phg5000TPM15.6L LAJose100% (1)

- GC17P Manual EngDocument210 pagesGC17P Manual EngAlexandre CorreaNo ratings yet

- Philips32phg5000TPM15.6L LADocument87 pagesPhilips32phg5000TPM15.6L LAJose100% (1)

- Catalago Da ValvulaDocument12 pagesCatalago Da ValvulaAlexandre CorreaNo ratings yet

- Barton Nuclear Model 227A/227As Differential Pressure Indicator User ManualDocument18 pagesBarton Nuclear Model 227A/227As Differential Pressure Indicator User ManualAlexandre CorreaNo ratings yet

- Anéis do grupo 501 para encomendaDocument3 pagesAnéis do grupo 501 para encomendaAlexandre CorreaNo ratings yet

- Installation Instructions: Parts ListDocument14 pagesInstallation Instructions: Parts Listedudu022No ratings yet

- SD6830 AukDocument34 pagesSD6830 AukAlexandre CorreaNo ratings yet

- Diagrama Xbox360Document67 pagesDiagrama Xbox360HILARIO64% (14)

- Wes50 Oi PLDocument4 pagesWes50 Oi PLAlexandre CorreaNo ratings yet

- Plan PDFDocument3 pagesPlan PDFAlexandre CorreaNo ratings yet

- Co Evolution ArticleDocument6 pagesCo Evolution ArticleffctokaNo ratings yet

- GC17P Manual EngDocument210 pagesGC17P Manual EngAlexandre CorreaNo ratings yet

- TS100 V2.46 Schematic Diagram V1.0 PDFDocument1 pageTS100 V2.46 Schematic Diagram V1.0 PDFAlexandre Correa100% (1)

- WTV020 SD ManualDocument26 pagesWTV020 SD Manualfcuenca_acunaNo ratings yet

- Nuts and Volts 2010-11Document84 pagesNuts and Volts 2010-11hjhelen1100% (1)

- House 3A4Document1 pageHouse 3A4Gerardo AndradeNo ratings yet

- 372 145 Weller Wes51 Specifications 44224Document2 pages372 145 Weller Wes51 Specifications 44224Alexandre Correa0% (1)

- Weller CatalogDocument88 pagesWeller CatalogcammellieNo ratings yet

- Pop Updesignandpapermechanics 120522144931 Phpapp02Document161 pagesPop Updesignandpapermechanics 120522144931 Phpapp02Alexandre CorreaNo ratings yet

- Template Giftbox 13 X 11 X 10 CMDocument1 pageTemplate Giftbox 13 X 11 X 10 CMAlexandre CorreaNo ratings yet

- Popmake SharkDocument2 pagesPopmake SharkChiong Yew TiongNo ratings yet

- BallValve Cat 27-29Document3 pagesBallValve Cat 27-29Alexandre CorreaNo ratings yet

- Lummus Technology: Most Broad, Diversified Technology PortfolioDocument2 pagesLummus Technology: Most Broad, Diversified Technology PortfolioSARFRAZ ALINo ratings yet

- Class Nine-Ten: English First Paper 1: 1. A Dialogue Between Two Friends About Good Effects of Morning WalkDocument17 pagesClass Nine-Ten: English First Paper 1: 1. A Dialogue Between Two Friends About Good Effects of Morning WalkKazi Mahbubur RahmanNo ratings yet

- Effect of Friction Stir Processing Parameters On The Mechanical and Dynamic Responses of AA 5052-H32Document11 pagesEffect of Friction Stir Processing Parameters On The Mechanical and Dynamic Responses of AA 5052-H32Mohammed GamilNo ratings yet

- Micro Bit Lesson 456Document48 pagesMicro Bit Lesson 456jorge diazNo ratings yet

- School DaysDocument1 pageSchool DaysAmethyst CareyNo ratings yet

- Artificial Intelligence: IV B.Tech - II Semester - Regular Examinations - March 2018Document3 pagesArtificial Intelligence: IV B.Tech - II Semester - Regular Examinations - March 2018Vyshnavi ThottempudiNo ratings yet

- Capability vs Competency ExplainedDocument2 pagesCapability vs Competency ExplainedAgentSkySkyNo ratings yet

- An Jal 10 Macos X User GuideDocument21 pagesAn Jal 10 Macos X User GuideCikgu Thanesh BalakrishnanNo ratings yet

- LG - UfDocument2 pagesLG - UfshintaNo ratings yet

- Rechargeable battery backlight counting indicatorDocument2 pagesRechargeable battery backlight counting indicatorHatake BenaoudaNo ratings yet

- Chapter 6 Bearing CapacityDocument40 pagesChapter 6 Bearing CapacityVhaun AzonNo ratings yet

- Syllogism by Sumit SirDocument23 pagesSyllogism by Sumit SirdjNo ratings yet

- Logging & Debugging Python TricksDocument22 pagesLogging & Debugging Python TricksYurioWindiatmokoNo ratings yet

- Javascript BeginnerDocument309 pagesJavascript BeginnernazarNo ratings yet

- 7th Grade Module 1 - Lesson 11Document16 pages7th Grade Module 1 - Lesson 11api-369302912No ratings yet

- Q3 - WRITE SIMPLE STORY - Grade 3Document5 pagesQ3 - WRITE SIMPLE STORY - Grade 3Elimi Rebucas100% (4)

- Marine Products Fuel Pump Repair Kit Flier WF32-123BDocument4 pagesMarine Products Fuel Pump Repair Kit Flier WF32-123Bjoshuah171No ratings yet

- Customer Name DOB Income Res City EmployerDocument122 pagesCustomer Name DOB Income Res City EmployerAnshu GuptaNo ratings yet

- Areas: Isabela Ppo: Pcinsp Ronald G. Estilles Jr-Odl PO2 Charles Andrew S. MendozaDocument4 pagesAreas: Isabela Ppo: Pcinsp Ronald G. Estilles Jr-Odl PO2 Charles Andrew S. MendozaJun Rinion TaguinodNo ratings yet

- The SPDF Electron Orbital Model ParsedDocument8 pagesThe SPDF Electron Orbital Model ParsedBheim LlonaNo ratings yet

- Ashraf FouadDocument125 pagesAshraf Fouadamit.thechosen1100% (7)

- House and Furniture There Isare - 42265Document3 pagesHouse and Furniture There Isare - 42265lavica13No ratings yet

- BET PlotDocument12 pagesBET PlotMohamad Reza JahanbakhshNo ratings yet

- SMEs - Module-02-Concepts and Pervasive PrinciplesDocument44 pagesSMEs - Module-02-Concepts and Pervasive PrinciplesChris Iero-WayNo ratings yet

- Calculus of Several Variables Question BankDocument11 pagesCalculus of Several Variables Question BankKalyani ReniwalNo ratings yet

- The Two CulturesDocument2 pagesThe Two CulturesMehmet SezerNo ratings yet

- PrioritizationDocument4 pagesPrioritizationJhennie EyescandieNo ratings yet

- Data Sheet For Three-Phase Squirrel-Cage-Motors: Ordering Data: 1LE1002-1AB42-2AA4Document1 pageData Sheet For Three-Phase Squirrel-Cage-Motors: Ordering Data: 1LE1002-1AB42-2AA4nizarNo ratings yet

- Non Valuated StockDocument4 pagesNon Valuated StockGK SKNo ratings yet

- Lesson Plan Grade 4 Math - Visualizing Numbers Up To 100 000 With Emphasis On Numbers 10 001 - 50 000Document12 pagesLesson Plan Grade 4 Math - Visualizing Numbers Up To 100 000 With Emphasis On Numbers 10 001 - 50 000tinker05boushNo ratings yet