Professional Documents

Culture Documents

Organizacion STACK 16F84A

Uploaded by

JuanCarlosBenavides0 ratings0% found this document useful (0 votes)

68 views2 pagesEl PIC16F84A tiene dos bloques de memoria: memoria de programa y memoria de datos. La memoria de datos se divide en dos áreas: registros de funciones especiales (SFR) y registros de propósitos generales (GPR). La memoria de datos también se divide en dos bancos para permitir más de 116 bytes de RAM general de propósito. Los bits de control en el registro de estado se utilizan para seleccionar entre los bancos.

Original Description:

ORGANIZACION STACK DEL PIC

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentEl PIC16F84A tiene dos bloques de memoria: memoria de programa y memoria de datos. La memoria de datos se divide en dos áreas: registros de funciones especiales (SFR) y registros de propósitos generales (GPR). La memoria de datos también se divide en dos bancos para permitir más de 116 bytes de RAM general de propósito. Los bits de control en el registro de estado se utilizan para seleccionar entre los bancos.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

68 views2 pagesOrganizacion STACK 16F84A

Uploaded by

JuanCarlosBenavidesEl PIC16F84A tiene dos bloques de memoria: memoria de programa y memoria de datos. La memoria de datos se divide en dos áreas: registros de funciones especiales (SFR) y registros de propósitos generales (GPR). La memoria de datos también se divide en dos bancos para permitir más de 116 bytes de RAM general de propósito. Los bits de control en el registro de estado se utilizan para seleccionar entre los bancos.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

2.

0 ORGANIZACIÓN DE MEMORIA 1020h, 1420h, 1820h y 1C20h, la

instrucción será la misma.

Hay dos bloques de memoria en el El vector RESET está a las 0000h y el vector

PIC16F84A. de interrupción está en 0004h.

Estas son la memoria del programa y la

memoria de datos. Cada bloque tiene su

propio bus, por lo que el acceso a cada

uno

el bloqueo puede ocurrir durante el

mismo ciclo de oscilador. La memoria de

datos puede dividirse en el RAM de

propósito general y la función especial

Registros (SFR). El funcionamiento de los

SFR que controlar el "núcleo" se describe

aquí. Los SFRs utilizados

para controlar los módulos periféricos se

describen en la sección discutiendo cada

módulo periférico individual.

El área de memoria de datos también

contiene los datos Memoria EEPROM.

Esta memoria no está mapeada

directamente

en la memoria de datos, pero se mapea

indirectamente. Es decir, un puntero de

dirección indirecta especifica la dirección

del

datos de memoria EEPROM para leer /

escribir. Los 64 bytes de los datos de

memoria EEPROM tienen el rango de

direcciones 0h-3Fh.

2.2 Organización de memoria de datos

2.1 Organización de la memoria del

programa La memoria de datos está dividida en dos

áreas. El primero es el área de Registros

El PIC16FXX tiene un contador de de funciones especiales (SFR), mientras

programa de 13 bits de abordar un que el segundo es el área de Registros de

espacio de memoria de programa de 8K x Propósitos Generales (GPR).

14. Por el PIC16F84A, el primer 1K x 14 Los SFR controlan el funcionamiento del

(0000h-03FFh) son implementado dispositivo. Las porciones de memoria de

físicamente (Figura 2-1). Accediendo a datos están almacenadas. Esto es para

una ubicación encima de la dirección ambos

implementada físicamente causa un el área SFR y el área GPR. El área de GPR

envolvente, Por ejemplo, para es

ubicaciones 20h, 420h, 820h, C20h,

bancarizado para permitir más de 116 directamente o indirectamente a través

bytes de general RAM de propósito Las del

áreas bancarizadas del SFR son para el FSR (Sección 2.5).

registro que controlan las funciones Las direcciones GPR en el Banco 1 están

periféricas. Bancario mapeadas a direcciones en el Banco 0.

requiere el uso de bits de control para la Como ejemplo, dirección de ubicación

selección del banco. 0Ch u 8Ch accederán al mismo GPR.

Estos bits de control se encuentran en el

Registro ESTADO.

La figura 2-2 muestra la organización del

mapa de memoria de datos.

Las instrucciones MOVWF y MOVF

pueden mover valores del W se registra

en cualquier ubicación en el archivo de

registro ("F"),

y viceversa.

Se puede acceder a toda la memoria de

datos ya sea directamente usando la

dirección absoluta de cada archivo de

registro o indirectamente a través del File

Select Register (FSR) (Sección 2.5). El

direccionamiento indirecto usa el

presente

valor del bit RP0 para el acceso a las áreas

bancarizadas de memoria de datos.

La memoria de datos se divide en dos

bancos que contener los registros de

propósito general y el especial registro de

funciones. El banco 0 se selecciona

borrando el RP0 bit (ESTADO <5>).

Configurar el bit RP0 selecciona el Banco

1. Cada banco se extiende hasta 7Fh (128

bytes). El primero doce ubicaciones de

cada banco están reservadas para el

Registros de funciones especiales. El resto

son generales Registros de propósitos,

implementados como RAM estática.

2.2.1 REGISTRO DE PROPÓSITO GENERAL

ARCHIVO

Cada registro de propósito general (GPR)

tiene 8 bits de ancho y se accede

You might also like

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeFrom EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeNo ratings yet

- TALLER PRIMER PARCIAL MICROS 2 ElkinDocument6 pagesTALLER PRIMER PARCIAL MICROS 2 ElkinSebastian ZuluagaNo ratings yet

- UF0852 - Instalación y actualización de sistemas operativosFrom EverandUF0852 - Instalación y actualización de sistemas operativosRating: 5 out of 5 stars5/5 (1)

- Cuestionario Punteros C RespuestasDocument4 pagesCuestionario Punteros C RespuestasAndreina GarciaNo ratings yet

- Labview PruebasDocument354 pagesLabview PruebasDayanaUbilluzNo ratings yet

- TfhkaPHPTCP Español PanamáDocument10 pagesTfhkaPHPTCP Español PanamáGabriel DugarteNo ratings yet

- Tarea Direcciones Efectivas de MemoriaDocument4 pagesTarea Direcciones Efectivas de MemoriaLuis Miguel SequeliNo ratings yet

- Apuntes PicDocument155 pagesApuntes PicAmador Vivar RecarteNo ratings yet

- Microautomatizacion Y ControlDocument13 pagesMicroautomatizacion Y ControlMarcelo AvalosNo ratings yet

- PIC16F819 6to AñoDocument33 pagesPIC16F819 6to AñoAntonio Gonzalez100% (1)

- Organización de La Memoria Del PIC18f4550Document4 pagesOrganización de La Memoria Del PIC18f4550e09081110100% (1)

- ¿Cómo Trabaja El ALU Del PIC?Document3 pages¿Cómo Trabaja El ALU Del PIC?Vale Door50% (2)

- Capítulo 04-Organzación de MemoriaDocument10 pagesCapítulo 04-Organzación de MemoriaNelson VargasNo ratings yet

- Arquitectura 16 F84Document13 pagesArquitectura 16 F84torote1313No ratings yet

- Instituto Tecnologico Vigi2Document2 pagesInstituto Tecnologico Vigi2Mauro M Janco BernabeNo ratings yet

- Registro SFRDocument9 pagesRegistro SFRMauro CanelaNo ratings yet

- Mapa de MemoriaDocument7 pagesMapa de MemoriaJose Leonardo Simancas GarciaNo ratings yet

- Organización de La Memoria de Un MicrocontroladorDocument7 pagesOrganización de La Memoria de Un MicrocontroladorAlex CurielNo ratings yet

- Componentes Del MicroprocesadorDocument25 pagesComponentes Del Microprocesadorel_cuate1883% (6)

- Registros Del Pic 16f84Document24 pagesRegistros Del Pic 16f84Gloria MoralesNo ratings yet

- Pic 18F4550Document45 pagesPic 18F4550fhidalgo_8100% (3)

- Semana 2 Memoria y RegistrosDocument32 pagesSemana 2 Memoria y RegistrosKevin B SánchezNo ratings yet

- Organización de La MemoriaDocument5 pagesOrganización de La MemoriaReynel ChaparroNo ratings yet

- Guía Del Pic 16f84Document17 pagesGuía Del Pic 16f84b6dicNo ratings yet

- Pic 16F877Document9 pagesPic 16F877Jave Zabdiel Hernandez MarinNo ratings yet

- P01 Modelo de Programación Del PIC18F4550 PDFDocument11 pagesP01 Modelo de Programación Del PIC18F4550 PDFMiguel ClarosNo ratings yet

- Organización de Los AVRDocument77 pagesOrganización de Los AVRIvanNo ratings yet

- Microprocesador - El PIC 16F84Document10 pagesMicroprocesador - El PIC 16F84J84CNo ratings yet

- IndexDocument20 pagesIndexpaezmiguel268No ratings yet

- Banco 8088 y 8086Document12 pagesBanco 8088 y 8086Brayhan Torres100% (1)

- 2.1 - Estructura Del Microcontrolador ATmega328PDocument12 pages2.1 - Estructura Del Microcontrolador ATmega328PArantxa NorzagarayNo ratings yet

- Unidad 2 Estructura y Funcionamiento deDocument15 pagesUnidad 2 Estructura y Funcionamiento dejua carlosNo ratings yet

- Resgistros Pic 877aDocument12 pagesResgistros Pic 877aluis albertoNo ratings yet

- Consulta 5 AyalaDocument7 pagesConsulta 5 AyalaEDSON MISAEL RODR�GUEZ GARC�ANo ratings yet

- Pic 16 F628Document23 pagesPic 16 F628Ariel Godoy67% (3)

- Microcontrolador PIC18F4550Document19 pagesMicrocontrolador PIC18F4550Alitzel GalileaNo ratings yet

- Tema 5Document11 pagesTema 5Cometas CachetesNo ratings yet

- TE4RPDocument10 pagesTE4RPDiego SilveraNo ratings yet

- Tipos de RegistrosDocument5 pagesTipos de RegistrosSantiago Barahona100% (1)

- Memorias de Un PLC y Su ClasificaciónDocument5 pagesMemorias de Un PLC y Su ClasificaciónJhory Ore100% (1)

- Resumen de Caracteristicas Del Pic 16f887Document25 pagesResumen de Caracteristicas Del Pic 16f887PEdro CarvajalNo ratings yet

- La Familia MCS51 Modulo I.Document29 pagesLa Familia MCS51 Modulo I.Marco Antonio Manjarrez PalmaNo ratings yet

- Caracteristicas Principales Del Pic 16f887Document16 pagesCaracteristicas Principales Del Pic 16f887Douglas Joel ChaconNo ratings yet

- Exposicion MicrocontroladoresDocument33 pagesExposicion MicrocontroladoresRosita Mtz SNo ratings yet

- Microcontrolador PIC16F887Document166 pagesMicrocontrolador PIC16F887FUNDELEC GTI Desarrollo de SoftwareNo ratings yet

- Arduino 2Document30 pagesArduino 2Nicolas Quispe AguilarNo ratings yet

- Microcontroladores PIC - Estructura Interna Del MicrocontroladorDocument3 pagesMicrocontroladores PIC - Estructura Interna Del MicrocontroladorOvanio MolinaNo ratings yet

- Pic 16f886Document10 pagesPic 16f886Lenin OñateNo ratings yet

- Arquitectura de Un MicrocontroladorDocument16 pagesArquitectura de Un MicrocontroladorLazaro MorenoNo ratings yet

- 1 PIC MemDocument15 pages1 PIC MemWilfredo CanaviriNo ratings yet

- Microprocesadores PDFDocument5 pagesMicroprocesadores PDFMarielys BrijaldoNo ratings yet

- Principales Registros de Control y Manejo de Las Memorias Flash y EepromDocument18 pagesPrincipales Registros de Control y Manejo de Las Memorias Flash y Eepromgoar11886303No ratings yet

- Registros de Funciones EspecialesDocument6 pagesRegistros de Funciones EspecialesManuel Beltran NoguesNo ratings yet

- Comparación de Familias de MicroprocesadoresDocument69 pagesComparación de Familias de Microprocesadoresguardama100% (1)

- Manual de Prácticas Del Laboratorio de Dispositivos de Almacenamiento y de Entrada/SalidaDocument21 pagesManual de Prácticas Del Laboratorio de Dispositivos de Almacenamiento y de Entrada/SalidaAldo FontesNo ratings yet

- Microcontroladores AT89C5xDocument25 pagesMicrocontroladores AT89C5xMario Fernández RodríguezNo ratings yet

- Micro Control Adores 1Document12 pagesMicro Control Adores 1descarlexNo ratings yet

- Arquitectura Del Procesador y Organización Interna de La MemoriaDocument17 pagesArquitectura Del Procesador y Organización Interna de La MemoriaAndres RomeroNo ratings yet

- Configuración de Puertos de e - SDocument30 pagesConfiguración de Puertos de e - Ssofy naranjoNo ratings yet

- Trabajo Memoria RamDocument21 pagesTrabajo Memoria RamLuis rondonNo ratings yet

- Sed 03 1Document28 pagesSed 03 1RaquelNo ratings yet

- UF1468 - Almacenamiento de la información e introducción a SGBDFrom EverandUF1468 - Almacenamiento de la información e introducción a SGBDNo ratings yet

- UF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosFrom EverandUF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosNo ratings yet

- Sintaxis de BotonesDocument7 pagesSintaxis de BotonesSeol Dani Sophie Cortez SalazarNo ratings yet

- 7 2 4 3 Practica de Laboratorio Uso de Wireshark para Examinar Capturas de FTP y TFTPDocument14 pages7 2 4 3 Practica de Laboratorio Uso de Wireshark para Examinar Capturas de FTP y TFTPSebastian Montoya Castaño100% (1)

- Examen Semestral Gestión EmpresarialDocument11 pagesExamen Semestral Gestión EmpresarialVidalChuchuNo ratings yet

- Sesion 1 - 2Document8 pagesSesion 1 - 2JORGE DAVID RAMOS ROZALENNo ratings yet

- Sistemas Operativos - Formas de Sistemas de ArchivosDocument5 pagesSistemas Operativos - Formas de Sistemas de ArchivosIsra BambuNo ratings yet

- SQL Server 2000 Manual ExelenteDocument40 pagesSQL Server 2000 Manual ExelentejaramosdNo ratings yet

- 16 Al 17 Spanish 4Document35 pages16 Al 17 Spanish 4Apolo GreenNo ratings yet

- ConmutacionDocument18 pagesConmutacionpilpeneNo ratings yet

- BASE de DATOS Misael ReyesDocument9 pagesBASE de DATOS Misael ReyesFelipe PerezNo ratings yet

- Error: 3 MensajesDocument2 pagesError: 3 MensajesJoana Bedoya ZapataNo ratings yet

- Módulo Backup and MigrateDocument3 pagesMódulo Backup and Migratealejandro padillaNo ratings yet

- p29 - p30 Redes de Computadores 5ta EdicionDocument3 pagesp29 - p30 Redes de Computadores 5ta EdicionGerman Felipe Naranjo GonzalezNo ratings yet

- PDF 3Document24 pagesPDF 3JuanRerNo ratings yet

- Rosario Dariel Unidad4CuadroDocument2 pagesRosario Dariel Unidad4CuadroPeñalo MarielNo ratings yet

- Práctica Ejercicio Completo XML Con DOMDocument4 pagesPráctica Ejercicio Completo XML Con DOMDaniNo ratings yet

- HR100-70 & HR100L-70 User Guide - Espa LDocument177 pagesHR100-70 & HR100L-70 User Guide - Espa LDiegoNo ratings yet

- Proyecto Base de Datos 2 Noticias-1Document19 pagesProyecto Base de Datos 2 Noticias-1Alex GamboaNo ratings yet

- Leccion 1 - Archivos enDocument24 pagesLeccion 1 - Archivos enSergio SanchezNo ratings yet

- Base de Datos Unidad IDocument26 pagesBase de Datos Unidad Imariangel7No ratings yet

- 7.5.1. Memorias RAMDocument3 pages7.5.1. Memorias RAMWendyNo ratings yet

- Arquitectura de Computadoras BusesDocument3 pagesArquitectura de Computadoras BusesFELIPE ADRIAN KU MAYNo ratings yet

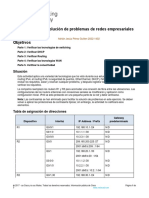

- 12.5.13 Packet Tracer - Troubleshoot Enterprise NetworksDocument7 pages12.5.13 Packet Tracer - Troubleshoot Enterprise Networksianerez 2No ratings yet

- M4 DBMSDocument24 pagesM4 DBMSDrizzzTNo ratings yet

- 04 Algebra RelacionalDocument40 pages04 Algebra RelacionalmlararivNo ratings yet

- Caso de Estudio Arquitectura de Datos DistribuidosDocument7 pagesCaso de Estudio Arquitectura de Datos DistribuidosEnrique LaurelNo ratings yet

- Actividad #3 Yormatt FreitesDocument1 pageActividad #3 Yormatt FreitesKelly LopezNo ratings yet

- Manual a2AdminBasicoDocument212 pagesManual a2AdminBasicobrayan0% (1)