Professional Documents

Culture Documents

Drum Machine

Uploaded by

jez.lowlifeOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Drum Machine

Uploaded by

jez.lowlifeCopyright:

Available Formats

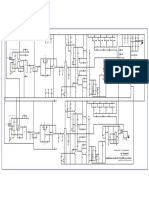

All parts are 74HC except 74C922 and 74LS189

Vcc

R3 33

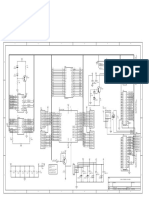

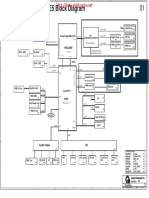

STEP KEY ENCODER CLOCK GENERATORS ADDRESS INPUT MULTIPLEXER PATTERN MEMORY TRIGGER PULSES

Vcc 16 x 4 BITS

STEP LED DECODER

74C922 U3 74153 U9 74189 U11

D1 STEP2

7485 U1 74154 U2 U15

11 17 14 4 5 1 D18

COL X1 D0 K0 (7556 or TLC556) STEP1 A D0 Q0

10 5 23 1 R14 3

S0 A0 A>Bo NC L0 A_SEL Y0 D2 10 16 556 U5 2 TRIG0

COL X2 D1 K1 1k PRESS B 6 7 2

22 2 R13 5.6k R17 D1 Q1

12 6 L1 B_SEL Y1 8 15 1 14

S1 A1 A=Bo D3 COL X3 D2 K2 DISCH1 VDD 1k 1 7

21 3 EN1 1Y 10 9 7432

L2 C_SEL Y2 7 14 R18 1.5k D2 Q2

13 7 COL X4 D3 K3 2 13 6 U15

S2 A2 A<Bo NC 20 4 D4 THRES1 DISCH2 2 K0 1C0 4 D19

L3 D_SEL Y3 12 12 11

S1 S2 S3 S4 DA 5 D3 Q3 6

15 5 3 12 cw ccw 1C1 TRIG1

S3 A3 Y4 D5 1 2 1 2 1 2 1 2 1 NC CONT1 THRES2 NC 5

ROW Y1 Vcc 1 3 4 1

6 S0 1C2 A0

9 Y5 2 4 11 R21 50k

L0 B0 D6 ROW Y2 RESET1 CONT2 NC 3 7432

7 L0 1C3 15 4052 U13

Y6 S5 S6 S7 S8 3 A1 U15

11 ROW Y3 5 10 9 D20

L1 B1 8 D7 1 2 1 2 1 2 1 2 LEDCLK OUT1 RESET2 RUN 15 9 10 12

Y7 4 EN2 2Y 14 CH0 A X0 8

ROW Y4 A2 TRIG2

14 B2 Y8 9 D8 6 19 10 2C0 9 B X1 14 10

L2 TRIG1 OUT2 STEPCLK K1 CH1

S9 S10 S11 S12 13 A3

Y9 10 11 2C1 X2 15 7432

1 B3 D9 13 OE C6 7 8

L3 1 2 1 2 1 2 1 2 GND TRIG2 U15

11 0.1uF 12 3 11 D21

1

Y10 OSC KBM S1 2C2 WE 13 X3 Vcc 12

LEDBIT X

13 D10 C9 13 1 11

Y11 5 6 L1 2C3 2 3 Y0 R23 TRIG3

S13 S14 S15 S16 4.7uF CE Y 13

4 14 D11 5 R24

1

A>Bi Y12 1 2 1 2 1 2 1 2 Y1

2

15 C3 C4 74153 U10 2 7432 D18ïD21: 1N4148

3 Y13 Y2 R25

STEPCLK A=Bi D12 0.1uF 1uF

19 G2 Y14 16 14 A 6 INH Y3 4 R26 VOICE BOARD CONNECTIONS

STEP1

2

2 A<Bi U4 D13 COUNTERS

18 G1 Y15 17 2 B CONN1

1 U6 PRESS R23ïR26: 10k Vcc

START/STOP TOGGLE CIRCUIT 4520

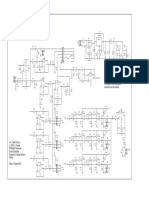

3 D14 CHANNEL DECODER

1 EN1 1Y 7 1

2 RESET 1 CP0 Q1 3

LEDBIT Vcc L0

D15 6 1C0 NOISEGEN 2

7486 LED DISPLAY K2 U14

2 CP1 Q2 4

4 8 Vcc LEDCLK L1 5 1C1 U12 1 TRIG0 3

If the LED mux count is equal to the current step number, MULTIPLEX

1 3

flicker the LED. (An XOR gate is used as a conditional inverter.) RESET VCC Q3 5 COUNTER 4 1C2 OUT0 4

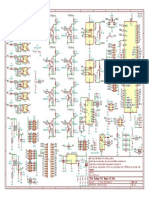

L2 S2 3 2

R6 R8 3 1C3 2 5

DISC 7

RC circuit delays the clock edge 7 RST Q4 6 L2 7486

NC 10k S17 100k L3

until after STEP2 goes high. 15 9 7408 U14

2 6 1 2 EN2 2Y 4 Vcc CONN2

TRIG THRES U12

This ensures the first beat is not U6 10 4 6

1

4520 K3 2C0 1

CTRL 5 R7 C2 skipped when playback starts. 6 5

NC 11 2C1

10k 1uF 9 CP0 Q1 11 5 NOISEGEN 2

S0 7486

R12 1k 12 2C2

S3 TRIG1 3

2

10 12 7408 U14

1 3 STEPCLK CP1 Q2 S1 13 9

GND OUT STEP L3 2C3 U12 OUT1 4

9 8

13

LM555 U5 C5

Q3 S2 COUNTER PRESS low: output = Kn (key input) Vcc 8 10 5

1nF 10

Vcc U4 15 RST Q4 14 STEP1 high: output = Ln (LED mux count) 7486

S3 CONN3

4 STEP1 low: output = Sn (step number) 7408 U14 Vcc

6 R22 12

RUN U12 1

CHANNEL SELECT ROTARY SWITCH 5 D16 10k 12 11

Vcc 11 13 NOISEGEN 2

7486 RUN WR D17 13

S? XOR gate used as inverter CLEAR 7486 TRIG2 3

1 R4 MEMORY WRITE PULSE GENERATORS CLEAR 7408 OUT2 4

10k RUN D16ïD17: 1N4148 MEMORY CLEAR BIT INVERTER

2 U7 U7 5

NOISE SOURCE POWERïON RESET NC 74123 74123

13 R16 1k

CH0 Individual bits in RAM are toggled by feeding the outputs

Vcc U4 Vcc R2 10k 3 9 A Q 5 1 A Q 13 CONN4

PATTERN CLEAR BUTTON NC DA Vcc

12

RESET Vcc

of the 74LS189 back to the inputs through a 74HC86.

11 4 Vcc 10 B Q 12 2 B Q 4 Since an XOR gate can act like a conditional inverter, 1

NOISEGEN NC PRESS WR

13 C1 PRESS

S? pins 2, 5, 10, and 13 of the ’86 are the "control" inputs. NOISEGEN 2

10uF Ce 6 Ce 14

7486 5 R5 R9 When a "control" pin is high, the ’189’s corresponding output bit,

Vcc Vcc TRIG3 3

10k S18 10k 11 7 3 15 WR

6 CLR Re/Ce C8 CLR Re/Ce which is already inverted, is inverted again, and the bit is unchanged. OUT3 4

R1 1k 1 2

13 CLEAR 220pF When a "control" pin is low, the ’189’s corresponding output bit

CH1 C? C10 PRESS pulse width: 650 ns 5

7 220pF 47pF is allowed to pass through unmodified, and the bit’s inverse is written

NC

Vcc Vcc WR pulse width: 290 ns

8 into RAM.

NC Delay, PRESS falling edge to WR falling edge: 190 ns

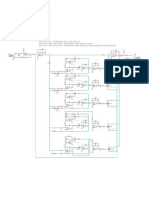

MIXER AND OUTPUT STAGE

R10 2.2k R19 2.2k

The 4052 multiplexer pulls the "control" line for the selected channel low,

STEP PULSE GENERATORS Vcc

all the others are held high by pullup resistors. U16 Vcc

74123 U8 74123 U8

4 U17

R151k OUT0 3 R27 1k R3110k

9 5 1 13 Based on one datasheet, it looks like the 74LS189 has output buffers 1 3 8 C12 1uF

STEPCLK A Q A Q NC LM324

Vcc STEPCLK 2 1

to ensure that the Qn lines retain their old value during a write cycle. LM358 AUDIO OUT

10 B Q 12 2 B Q 4 11 R32 2

STEP1 STEP2 I verified this with a logic analyzer as well.

STEP1 10k 4

Ce 6 C7 Ce 14

Vcc 220pF Vcc Vcc

7400 Drum Machine 11 CLR Re/Ce 7 3 CLR Re/Ce 15 STEP2 U16

4 R28 1k

Matt Sarnoff (www.msarnoff.org) C? C11 Sn setup time after STEPCLK falling edge: 160 ns OUT1 5

7

220pF 47pF LM324

STEP1 pulse width: 760 ns 6

October 20, 2011 Vcc Vcc

STEP2 pulse width: 240 ns 11

Delay, STEP1 falling edge to STEP2 falling edge: 240 ns

R11 2.2k R20 2.2k

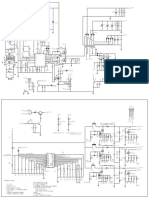

Vcc

U16

10 4 R29 1k

OUT2

8

LM324

9

11

Vcc

U16

12 4 R30 1k

OUT3

14

LM324

13

11

You might also like

- RTS5209-GR: TP CN (TP To Board) CR/TP CNDocument4 pagesRTS5209-GR: TP CN (TP To Board) CR/TP CNRoberto MouraNo ratings yet

- Fill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredFrom EverandFill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredNo ratings yet

- DatasheetDocument1 pageDatasheetOscar RamirezNo ratings yet

- Ob3362pv & MP3389Document1 pageOb3362pv & MP3389Tecnignm Electronica GeneralNo ratings yet

- Data SheetDocument1 pageData SheetDani 07No ratings yet

- DWG Descripcion Ic de Backlight K - 4L OM1 PDFDocument1 pageDWG Descripcion Ic de Backlight K - 4L OM1 PDFantonio h torres v67% (3)

- DWG Descripcion Ic de Backlight K - 4L OM1 PDFDocument1 pageDWG Descripcion Ic de Backlight K - 4L OM1 PDFantonio h torres vNo ratings yet

- 21 C 1348 Preamp 2Document1 page21 C 1348 Preamp 2GökhanNo ratings yet

- RJ9 Block Diagram: ICH7-MDocument41 pagesRJ9 Block Diagram: ICH7-MIIIkwarkaNo ratings yet

- Remove R107 If SI9435 Is Used: AMC34063ADMTDocument8 pagesRemove R107 If SI9435 Is Used: AMC34063ADMTOlegNo ratings yet

- 1W 5W 10W 30W: by "Donpetru" Amplificator Audio Hi-Fi 2x20W Rms 4 OhmiDocument1 page1W 5W 10W 30W: by "Donpetru" Amplificator Audio Hi-Fi 2x20W Rms 4 OhmiMarius Mihai TanjalaNo ratings yet

- Piu701 Piu701 Piu205Document3 pagesPiu701 Piu701 Piu205Sovi SoviNo ratings yet

- En.x Nucleo Iks02a1 SchematicDocument4 pagesEn.x Nucleo Iks02a1 SchematicIbrahim AkNo ratings yet

- PLC MegaV2 - Slim PDFDocument1 pagePLC MegaV2 - Slim PDFfrancisco ibañezNo ratings yet

- Schematic - B&K - AVR202ADocument20 pagesSchematic - B&K - AVR202AJesse JamesNo ratings yet

- 751001D4D2C4D81A6F1Document1 page751001D4D2C4D81A6F1jppreciadomNo ratings yet

- Pre Tsa 420Document1 pagePre Tsa 420Antonio Fernandes de JesusNo ratings yet

- PZ DSP28335 L开发板原理图Document1 pagePZ DSP28335 L开发板原理图Shwe Thin AungNo ratings yet

- Skyworth 168p-l5l01f-00 Psu SCHDocument2 pagesSkyworth 168p-l5l01f-00 Psu SCHTitán SotoNo ratings yet

- Quanta tw1 R3e SchematicsDocument37 pagesQuanta tw1 R3e SchematicsOssama BohamdNo ratings yet

- LLDM311B7-5 (L3110) Í Õè¡ Ý - V1.0Document36 pagesLLDM311B7-5 (L3110) Í Õè¡ Ý - V1.0Garik StepanyanNo ratings yet

- RTD2660 RTD2660: Debug InterfaceDocument1 pageRTD2660 RTD2660: Debug InterfaceWiebren van Erve100% (1)

- Ampeg Ba 110v2 SchematicDocument1 pageAmpeg Ba 110v2 SchematicFrancisco FernandezNo ratings yet

- Hitachi CDH-LE32FD18 Chassis 6M80B Televisor LCD DiagramaDocument9 pagesHitachi CDH-LE32FD18 Chassis 6M80B Televisor LCD DiagramaMario Rodriguez JuradoNo ratings yet

- Micro PLC Arduino NANO v3 RelesDocument1 pageMicro PLC Arduino NANO v3 RelesMte Ntp AlemaraNo ratings yet

- B&K AVR101 SchematicDocument21 pagesB&K AVR101 Schematiczombo8No ratings yet

- B&K AVR101 Schematic PDFDocument21 pagesB&K AVR101 Schematic PDFzombo8No ratings yet

- In Out SEL 787Document1 pageIn Out SEL 787Tosikur RahmanNo ratings yet

- AD15 - 30VT Vox AmplifierDocument11 pagesAD15 - 30VT Vox AmplifierKenn FerroNo ratings yet

- From Pre: Potência de Saida @ (1Khz) (@1Khz) Lim. 30V em 4R 225W Musical 42V em 4R 440WDocument1 pageFrom Pre: Potência de Saida @ (1Khz) (@1Khz) Lim. 30V em 4R 225W Musical 42V em 4R 440WfranciscoNo ratings yet

- PDF Created With Fineprint Pdffactory Pro Trial Version: Hy3020 Hmj20001B32Document1 pagePDF Created With Fineprint Pdffactory Pro Trial Version: Hy3020 Hmj20001B32wijtekNo ratings yet

- 308 Hyd PDFDocument1 page308 Hyd PDFchanlin100% (2)

- LCD InfDocument1 pageLCD Infkottee1977100% (2)

- Amanero USB To I2SDocument1 pageAmanero USB To I2SАндрей Кутовой100% (1)

- Piv101 Piv102 Piv201 Piv202 Piv201 Piv101 Piv102 Piv202: Piy101 Piy102 Piy102 Piy101Document1 pagePiv101 Piv102 Piv201 Piv202 Piv201 Piv101 Piv102 Piv202: Piy101 Piy102 Piy102 Piy101Adam Rzymski100% (1)

- k150 SCHDocument5 pagesk150 SCHAnonymous smdEgZN2Ie100% (1)

- Sony VGN-CS MBX-196 - Quanta - GD2 - Rev - 2a PDFDocument35 pagesSony VGN-CS MBX-196 - Quanta - GD2 - Rev - 2a PDFu3a96e na1susNo ratings yet

- Diy Inverter PSW - 2022-01-07Document1 pageDiy Inverter PSW - 2022-01-07Kareem Solar EngineeringNo ratings yet

- DAOTE5MB6FO L700-L745 Toshiba PDFDocument45 pagesDAOTE5MB6FO L700-L745 Toshiba PDFJhonCardenasNo ratings yet

- Py BoardDocument9 pagesPy BoardKazalište ArušaNo ratings yet

- Skyworth 168p-p42ttf-00 Fan7530 Fsfr1700 Str-A6159m SCHDocument1 pageSkyworth 168p-p42ttf-00 Fan7530 Fsfr1700 Str-A6159m SCH62eugenNo ratings yet

- XPROG-m - Schematic Diagram Rev BDocument2 pagesXPROG-m - Schematic Diagram Rev BIliescu Cristian100% (2)

- Anibal Garcia Venezuela @irepair - Ve: V1.0 P410 P410 DDocument32 pagesAnibal Garcia Venezuela @irepair - Ve: V1.0 P410 P410 DRafael OliveiraNo ratings yet

- Au 6850 CaDocument1 pageAu 6850 Canuevacuent904No ratings yet

- HTR 340Document40 pagesHTR 340SHERJOHN SaludadesNo ratings yet

- Tbe Inverter SchematicDocument3 pagesTbe Inverter SchematicGendil Fathe0% (1)

- 17ips71 r3 SchematicDocument2 pages17ips71 r3 SchematicMircea OlteanuNo ratings yet

- Motor VCB Feeder Wo Diff (z4)Document18 pagesMotor VCB Feeder Wo Diff (z4)Prasanta dasNo ratings yet

- Linear Psu SchematicDocument1 pageLinear Psu SchematicDelcu MarinicaNo ratings yet

- VC 4406Document4 pagesVC 4406Владимир БуклинNo ratings yet

- JH Triple Chorus SCH Page1Document1 pageJH Triple Chorus SCH Page1filmmaker221No ratings yet

- R19 47K R31 1K-1W R33 3K3-2W D7 SF14 +59,5VDC: Barra de Tweeter (8 Unidades)Document1 pageR19 47K R31 1K-1W R33 3K3-2W D7 SF14 +59,5VDC: Barra de Tweeter (8 Unidades)franciscoNo ratings yet

- HTS3375X - 78 DiagramaDocument10 pagesHTS3375X - 78 DiagramaDario EzequielNo ratings yet

- Crate BT15 - PWA Bass Amplifier PCB Schematics (848SCH - A)Document2 pagesCrate BT15 - PWA Bass Amplifier PCB Schematics (848SCH - A)Guim EloyNo ratings yet

- Bali XT2029 Moto E6 Play - SCHEMATICS - Main BoardDocument35 pagesBali XT2029 Moto E6 Play - SCHEMATICS - Main BoardAndres RamirezNo ratings yet

- CubeX Power Supply - ADP-555AR AB Schematics - PinoutDocument6 pagesCubeX Power Supply - ADP-555AR AB Schematics - Pinoutrafa0% (2)

- Parametrix EqualizerDocument1 pageParametrix EqualizerSegaNo ratings yet

- Platform Desk Assembly Instructions PDFDocument2 pagesPlatform Desk Assembly Instructions PDFjez.lowlifeNo ratings yet

- Survey QuestionnaireDocument1 pageSurvey Questionnairejez.lowlifeNo ratings yet

- Survey QuestionnaireDocument1 pageSurvey Questionnairejez.lowlifeNo ratings yet

- AnnexA POAFDocument1 pageAnnexA POAFjez.lowlifeNo ratings yet

- CBLMDocument64 pagesCBLMjez.lowlife0% (1)

- AnnexA POAF PDFDocument1 pageAnnexA POAF PDFjez.lowlifeNo ratings yet

- CBC Consumer Electronics Servicing NC IVDocument84 pagesCBC Consumer Electronics Servicing NC IVjez.lowlifeNo ratings yet

- Front Office Services NC II CG PDFDocument23 pagesFront Office Services NC II CG PDFjez.lowlife100% (1)

- ICT Sample Curriculum Map PDFDocument1 pageICT Sample Curriculum Map PDFjez.lowlifeNo ratings yet

- Cohesion and Learning in A Tutorial Spoken Dialog System: Art Ward Diane LitmanDocument43 pagesCohesion and Learning in A Tutorial Spoken Dialog System: Art Ward Diane Litmanjez.lowlifeNo ratings yet

- VRV Ii Rsxy R22Document96 pagesVRV Ii Rsxy R22Carlos Manriquez100% (2)

- Question BankDocument7 pagesQuestion BankAvinash ChauhanNo ratings yet

- Pulse and Digital CircuitsDocument2 pagesPulse and Digital CircuitsGautam ReddyNo ratings yet

- Voltage Surge (Voltage Spikes) : A Voltage Surge Is A Voltage Impulse or Wave Which IsDocument19 pagesVoltage Surge (Voltage Spikes) : A Voltage Surge Is A Voltage Impulse or Wave Which IsMonik Mishra100% (1)

- Kreatryx Analog Circuits PDFDocument43 pagesKreatryx Analog Circuits PDFshubhamNo ratings yet

- RSA306B USB Real Time Spectrum Analyzer Datasheet 37W603759Document26 pagesRSA306B USB Real Time Spectrum Analyzer Datasheet 37W603759HafiziAhmadNo ratings yet

- IEEE STD 1185-1994, IEEE Guide For Installation Methods For Generating Station CablesDocument48 pagesIEEE STD 1185-1994, IEEE Guide For Installation Methods For Generating Station Cableshebisht100% (2)

- Antennas and Radar For Environmental Scientists and EngineersDocument400 pagesAntennas and Radar For Environmental Scientists and EngineersNabil Dakhli100% (1)

- 1a455 Quanta fx5 0504 A00-03 PDFDocument50 pages1a455 Quanta fx5 0504 A00-03 PDFdigenioNo ratings yet

- ARM7Document36 pagesARM7Yogesh SutharNo ratings yet

- Ultimate Midi Guide From PDFDocument4 pagesUltimate Midi Guide From PDFnetzah2padre100% (1)

- Transistor Examples PDFDocument16 pagesTransistor Examples PDFGuganesan PerumalNo ratings yet

- Performance Tuning Guide: DB2 UDB V7.1Document418 pagesPerformance Tuning Guide: DB2 UDB V7.1karthika.subramanianNo ratings yet

- Mindwave MobileDocument46 pagesMindwave MobileRodrigo AlexanderNo ratings yet

- A - ELSB - Cat - 2020 - 02 - Residual Current Devices - LRDocument150 pagesA - ELSB - Cat - 2020 - 02 - Residual Current Devices - LRdoaa masNo ratings yet

- Installation Instructions: Door Control TS 971Document64 pagesInstallation Instructions: Door Control TS 971Bakas AthanasiosNo ratings yet

- Time and Current Grading For Protection Relay Type MK1000 & MK2000 - Mohamad Naim Mohamad - TK2821.M63 2008Document27 pagesTime and Current Grading For Protection Relay Type MK1000 & MK2000 - Mohamad Naim Mohamad - TK2821.M63 2008wcchang8100% (1)

- A 0-55-GHz Coplanar Waveguide PDFDocument6 pagesA 0-55-GHz Coplanar Waveguide PDFmujeeb.abdullah2830No ratings yet

- 1KHA001193-En Technical Data ETL600 R4 (Oct. 2012)Document4 pages1KHA001193-En Technical Data ETL600 R4 (Oct. 2012)Salvador FayssalNo ratings yet

- LG Gce 8525b Owner's ManualDocument2 pagesLG Gce 8525b Owner's ManualApocalypseNo ratings yet

- Brother P-Touch Mini Tech Service ManualDocument45 pagesBrother P-Touch Mini Tech Service ManualDuplessisNo ratings yet

- Wingspan ManualDocument9 pagesWingspan ManualalirioNo ratings yet

- The Z80 MicroprocessorDocument49 pagesThe Z80 MicroprocessorDuncan Jobando100% (1)

- Hisense Lcd3233eu 2633eu Chassis M-Star LCD TV SM Service Manual PDFDocument42 pagesHisense Lcd3233eu 2633eu Chassis M-Star LCD TV SM Service Manual PDFAnonymous CSnweOxNo ratings yet

- Precision Micropower, Low Dropout Voltage References: Nominal Output Number Voltage (V)Document24 pagesPrecision Micropower, Low Dropout Voltage References: Nominal Output Number Voltage (V)Jorge Centeno RamosNo ratings yet

- RC Infant Flow Sipap Operator Manual UG enDocument80 pagesRC Infant Flow Sipap Operator Manual UG enpericopepeNo ratings yet

- Man 41151 en 06 PDFDocument56 pagesMan 41151 en 06 PDFPanneer Selvam100% (1)

- Velomitor CT Transducer 125389-01 REV CDocument57 pagesVelomitor CT Transducer 125389-01 REV CHamid HannitNo ratings yet

- 132kV Connection Guide Version 9Document44 pages132kV Connection Guide Version 9ElwanNo ratings yet

- Signal Reception Via Multi-Platform ReceiversDocument72 pagesSignal Reception Via Multi-Platform ReceiversThalía NazarethNo ratings yet