Professional Documents

Culture Documents

128K X 8 Low Power Cmos Static Ram: Description Features

Uploaded by

vanhuong87Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

128K X 8 Low Power Cmos Static Ram: Description Features

Uploaded by

vanhuong87Copyright:

Available Formats

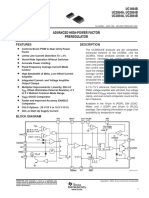

IS62C1024AL

IS65C1024AL

128K x 8 LOW POWER CMOS

JULY 2008

STATIC RAM

FEATURES DESCRIPTION

• High-speed access time: 35, 45 ns The ISSI IS62C1024AL/IS65C1024AL is a low power,

131,072-word by 8-bit CMOS static RAM. It is fabricated

• Low active power: 100 mW (typical)

using high-performance CMOS technology. This highly

• Low standby power: 20 µW (typical) CMOS reliable process coupled with innovative circuit design

standby techniques, yields higher performance and low power

• Output Enable (OE) and two Chip Enable consumption devices.

(CE1 and CE2) inputs for ease in applications When CE1 is HIGH or CE2 is LOW (deselected), the device

• Fully static operation: no clock or refresh assumes a standby mode at which the power dissipation

required can be reduced by using CMOS input levels.

• TTL compatible inputs and outputs Easy memory expansion is provided by using two Chip

• Single 5V (±10%) power supply Enable inputs, CE1 and CE2.The active LOW Write Enable

(WE) controls both writing and reading of the memory.

• Commercial, Industrial, and Automotive tem-

perature ranges available

• Standard Pin Configuration:

— 32-pin SOP/ 32-pin TSOP (Type 1)

• Lead free available

FUNCTIONAL BLOCK DIAGRAM

128K x 8

A0-A16 DECODER MEMORY ARRAY

VDD

GND

I/O

I/O0-I/O7 DATA COLUMN I/O

CIRCUIT

CE1

CE2 CONTROL

OE CIRCUIT

WE

Copyright © 2006 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no

liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on

any published information and before placing orders for products.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 1

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

PIN CONFIGURATION PIN CONFIGURATION

32-Pin SOP 32-Pin TSOP (Type 1)

NC 1 32 VDD

A11 1 32 OE

A16 2 31 A15

A9 2 31 A10

A14 3 30 CE2

A8 3 30 CE1

A12 4 29 WE

A13 4 29 I/O7

A7 5 28 A13

WE 5 28 I/O6

A6 6 27 A8 27

CE2 6 I/O5

A5 7 26 A9 A15 7 26 I/O4

A4 8 25 A11 VDD 8 25 I/O3

A3 9 24 OE NC 9 24 GND

A2 10 23 A10 A16 10 23 I/O2

A1 11 22 CE1 A14 11 22 I/O1

A0 12 21 I/O7 A12 12 21 I/O0

I/O0 13 20 I/O6 A7 13 20 A0

I/O1 14 19 I/O5 A6 14 19 A1

I/O2 15 18 I/O4 A5 15 18 A2

GND 16 17 I/O3 A4 16 17 A3

PIN DESCRIPTIONS

A0-A16 Address Inputs

CE1 Chip Enable 1 Input

CE2 Chip Enable 2 Input

OPERATING RANGE (IS62C1024AL)

OE Output Enable Input

WE Write Enable Input Range Ambient Temperature Vdd

I/O0-I/O7 Input/Output Commercial 0°C to +70°C 5V ± 10%

Industrial -40°C to +85°C 5V ± 10%

Vdd Power

GND Ground

OPERATING RANGE (IS65C1024AL)

Range Ambient Temperature Vdd

Automotive -40°C to +125°C 5V ± 10%

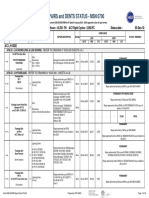

TRUTH TABLE

Mode WE CE1 CE2 OE I/O Operation Vdd Current

Not Selected X H X X High-Z Isb1, Isb2

(Power-down) X X L X High-Z Isb1, Isb2

Output Disabled H L H H High-Z Icc

Read H L H L Dout Icc

Write L L H X Din Icc

2 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

ABSOLUTE MAXIMUM RATINGS(1)

Symbol Parameter Value Unit

Vterm Terminal Voltage with Respect to GND –0.5 to +7.0 V

Tstg Storage Temperature –65 to +125 °C

Pt Power Dissipation 1.0 W

Iout DC Output Current (LOW) 20 mA

Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reli-

ability.

CAPACITANCE(1,2)

Symbol Parameter Conditions Max. Unit

Cin Input Capacitance Vin = 0V 6 pF

Cout Output Capacitance Vout = 0V 8 pF

Notes:

1. Tested initially and after any design or process changes that may affect these parameters.

2. Test conditions: Ta = 25°C, f = 1 MHz, Vdd = 5.0V.

DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

Symbol Parameter Test Conditions Options Min. Max. Unit

Voh Output HIGH Voltage Vdd = Min., Ioh = –1.0 mA 2.4 — V

Vol Output LOW Voltage Vdd = Min., Iol = 2.1 mA — 0.4 V

Vih Input HIGH Voltage 2.2 Vdd + 0.5 V

Vil Input LOW Voltage(1) -0.5 0.8 V

Ili Input Leakage GND ≤ Vin ≤ Vdd Com. -1 1 µA

Ind. -2 2

Auto. -5 5

Ilo Output Leakage GND ≤ Vout ≤ Vdd Com. -1 1 µA

CE1 = Vih, or Ind. -2 2

CE2 = Vil, or OE = Vih or Auto. -5 5

WE = Vil

Note:

1. Vil (min.) = -0.3V DC; Vil (min.) = -2.0V AC (pulse width -2.0 ns). Not 100% tested.

Vih (max.) = Vdd + 0.3V DC; Vih (max.) = Vdd + 2.0V AC (pulse width -2.0 ns). Not 100% tested.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 3

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

IS62C1024AL/IS65C1024AL

POWER SUPPLY CHARACTERISTICS(1) (Over Operating Range)

-35 ns -45 ns

Symbol Parameter Test Conditions Min. Max. Min. Max. Unit

Icc Average operating CE1 = Vil, CE2 = Vih Com. — 25 mA

Current Vin = Vih or Vil, Ind. — 30

I I/O= 0 mA, f=0 Auto. — 35

Icc1 Vdd Dynamic Operating Vdd = Max., CE1 = Vil Com. — 30 mA

Supply Current Iout = 0 mA, f = fmax Ind. — 35

Vin = Vih or Vil Auto. — 40

CE2 = Vih typ.(2) — 20

Isb1 TTL Standby Current Vdd = Max., Com. — 1 mA

(TTL Inputs) Vin = Vih or Vil, CE1 ≥ Vih, Ind. — 1.5

or CE2 ≤ Vil, f = 0 Auto. — 2

Isb2 CMOS Standby Vdd = Max., Com. — 5 µA

Current (CMOS Inputs) CE1 ≥ Vdd – 0.2V, or Ind. — 10

CE2 ≤ 0.2V, Vin ≥ Vdd – 0.2V, Auto. — 45

or Vin ≤ Vss + 0.2V, f = 0 typ.(2) — 4

Note:

1. At f = fmax, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.

2. Typical Values are measured at Vdd = 5V, Ta = 25oC and not 100% tested.

READ CYCLE SWITCHING CHARACTERISTICS(1) (Over Operating Range)

-35 ns -45 ns

Symbol Parameter Min. Max. Min. Max. Unit

trc Read Cycle Time 35 — 45 — ns

taa Address Access Time — 35 — 45 ns

toha Output Hold Time 3 — 3 — ns

tace1 CE1 Access Time — 35 — 45 ns

tace2 CE2 Access Time — 35 — 45 ns

tdoe OE Access Time — 10 — 20 ns

tlzoe(2) OE to Low-Z Output 3 — 5 — ns

thzoe(2) OE to High-Z Output 0 10 0 15 ns

tlzce1(2) CE1 to Low-Z Output 3 — 5 — ns

tlzce2(2) CE2 to Low-Z Output 3 — 5 — ns

thzce(2) CE1 or CE2 to High-Z Output 0 10 0 15 ns

Notes:

1. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0.6

to 2.4V and output loading specified in Figure 1a.

2. Tested with the load in Figure 1b. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.

4 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

AC TEST CONDITIONS

Parameter Unit

Input Pulse Level 0.6V to 2.4V

Input Rise and Fall Times 5 ns

Input and Output Timing 1.5V

and Reference Level

Output Load See Figures 1a and 1b

AC TEST LOADS

1838 Ω

1838 Ω

5V

5V

OUTPUT OUTPUT

100 pF 993 Ω 5 pF 993 Ω

Including Including

jig and jig and

scope scope

Figure 1a. Figure 1b.

AC WAVEFORMS

READ CYCLE NO. 1(1,2)

tRC

ADDRESS

tAA

tOHA

tOHA

DOUT DATA VALID

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 5

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

READ CYCLE NO. 2(1,3)

tRC

ADDRESS

tAA tOHA

OE

tDOE tHZOE

CE1 tLZOE

tACE1/tACE2

CE2

tLZCE1/

tLZCE2 tHZCE

HIGH-Z

DOUT DATA VALID

Notes:

1. WE is HIGH for a Read Cycle.

2. The device is continuously selected. OE, CE1 = Vil, CE2 = Vih.

3. Address is valid prior to or coincident with CE1 LOW and CE2 HIGH transitions.

WRITE CYCLE SWITCHING CHARACTERISTICS(1,3) (Over Operating Range, Standard and Low Power)

-35 ns -45 ns

Symbol Parameter Min. Max. Min. Max. Unit

twc Write Cycle Time 35 — 45 — ns

tsce1 CE1 to Write End 25 — 35 — ns

tsce2 CE2 to Write End 25 — 35 — ns

taw Address Setup Time to Write End 25 — 35 — ns

tha Address Hold from Write End 0 — 0 — ns

tsa Address Setup Time 0 — 0 — ns

tpwe(4) WE Pulse Width 25 — 35 — ns

tsd Data Setup to Write End 20 — 25 — ns

thd Data Hold from Write End 0 — 0 — ns

thzwe(2) WE LOW to High-Z Output — 10 — 15 ns

tlzwe(2) WE HIGH to Low-Z Output 3 — 5 — ns

Notes:

1. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0.6 to 2.4V

and output loading specified in Figure 1a.

2. Tested with the load in Figure 1b. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.

3. The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to

initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the

rising or falling edge of the signal that terminates the Write.

4. Tested with OE HIGH.

6 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

AC WAVEFORMS

WRITE CYCLE NO. 1 (WE Controlled)(1,2)

tWC

ADDRESS

tSCE1 tHA

CE1

tSCE2

CE2

tAW

tPWE(4)

WE

tSA tHZWE tLZWE

HIGH-Z

DOUT DATA UNDEFINED

tSD tHD

DIN DATA-IN VALID

WRITE CYCLE NO. 2 (CE1, CE2 Controlled)(1,2)

tWC

ADDRESS

tSA tSCE1 tHA

CE1

tSCE2

CE2

tAW

tPWE(4)

WE

tHZWE tLZWE

HIGH-Z

DOUT DATA UNDEFINED

tSD tHD

DIN DATA-IN VALID

Notes:

1. The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to

initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the

rising or falling edge of the signal that terminates the Write.

2. I/O will assume the High-Z state if OE = Vih.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 7

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

DATA RETENTION SWITCHING CHARACTERISTICS

Symbol Parameter Test Condition Min. Typ. Max. Unit

Vdr Vdd for Data Retention See Data Retention Waveform 2.0 5.5 V

Idr Data Retention Current Vdd = 2.0V, CE1 ≥ Vdd – 0.2V Com. — — 5 µA

or CE2 ≤ 0.2V Ind. — — 10

Vin ≥ Vdd – 0.2V, or Vin ≤ Vss + 0.2V Auto. — — 45

tsdr Data Retention Setup Time See Data Retention Waveform 0 — ns

trdr Recovery Time See Data Retention Waveform trc — ns

Note:

1. Typical Values are measured at Vdd = 5V, Ta = 25oC and not 100% tested.

DATA RETENTION WAVEFORM (CE1 Controlled)

tSDR Data Retention Mode tRDR

VDD

4.5V

2.2V

VDR

CE1 ≥ VDD - 0.2V

CE1

GND

DATA RETENTION WAVEFORM (CE2 Controlled)

Data Retention Mode

VDD

4.5V

tSDR tRDR

CE2

2.2V

VDR

CE2 ≤ 0.2V

0.4V

GND

8 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

ORDERING INFORMATION: IS62C1024AL

Commercial Range: 0°C to +70°C

Speed (ns) Order Part No. Package

35 IS62C1024AL-35Q Plastic SOP

35 IS62C1024AL-35T TSOP, Type 1

Industrial Range: –40°C to +85°C

peed (ns)

S Order Part No. Package

35 IS62C1024AL-35QI Plastic SOP

35 IS62C1024AL-35QLI Plastic SOP, Lead-free

35 IS62C1024AL-35TI TSOP, Type 1

35 IS62C1024AL-35TLI TSOP, Type 1, Lead-free

ORDERING INFORMATION: IS65C1024AL

Automotive Range: -40°C to +125°C

peed (ns)

S Order Part No. Package

45 IS65C1024AL-45QA3 Plastic SOP

45 IS65C1024AL-45QLA3 Plastic SOP, Lead-free

45 IS65C1024AL-45TA3 TSOP, Type 1

45 IS65C1024AL-45TLA3 TSOP, Type 1, Lead-free

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 9

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

10 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. H

06/26/08

IS62C1024AL

IS65C1024AL

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 11

Rev. H

06/26/08

You might also like

- Genie GS-1930 Parts ManualDocument194 pagesGenie GS-1930 Parts ManualNestor Matos GarcíaNo ratings yet

- Pharmd CurriculumDocument18 pagesPharmd Curriculum5377773No ratings yet

- Approved Project 25 StandardsDocument5 pagesApproved Project 25 StandardsepidavriosNo ratings yet

- Is61c512 15JDocument8 pagesIs61c512 15Jbahram adimiNo ratings yet

- Is62c256al 45vliDocument13 pagesIs62c256al 45vliRichard HungNo ratings yet

- IS61LV2568L: 256K X 8 High-Speed Cmos Static RamDocument14 pagesIS61LV2568L: 256K X 8 High-Speed Cmos Static RamTan Hung LuuNo ratings yet

- IS63LV1024 IS63LV1024L: 128K X 8 High-Speed Cmos Static Ram 3.3V Revolutionary PinoutDocument16 pagesIS63LV1024 IS63LV1024L: 128K X 8 High-Speed Cmos Static Ram 3.3V Revolutionary PinoutTan Hung LuuNo ratings yet

- 32K X 8 Low Power Cmos Static Ram: Features DescriptionDocument8 pages32K X 8 Low Power Cmos Static Ram: Features DescriptionmicaelfnNo ratings yet

- Hy628100alg 70Document9 pagesHy628100alg 70Claudiney BricksNo ratings yet

- IS61LV5128AL: 512K X 8 High-Speed Cmos Static RamDocument13 pagesIS61LV5128AL: 512K X 8 High-Speed Cmos Static RamTan Hung LuuNo ratings yet

- 6264Document8 pages6264api-3711187No ratings yet

- Ut 621024Document14 pagesUt 621024DarleiDuarteNo ratings yet

- HY628400 HynixSemiconductorDocument9 pagesHY628400 HynixSemiconductorHamidNo ratings yet

- 62WV6416ALLDocument17 pages62WV6416ALLNadeeshNo ratings yet

- General Description: Publication Release Date: March 1999 - 1 - Revision A7Document10 pagesGeneral Description: Publication Release Date: March 1999 - 1 - Revision A7algnben1746No ratings yet

- CAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionDocument11 pagesCAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionLaboratorio GTO Perú S.A.C.No ratings yet

- HY62V8100B (Rev13) PDFDocument12 pagesHY62V8100B (Rev13) PDFsmhzzNo ratings yet

- 32K X 8 Magnetic Nonvolatile CMOS RAM: PreliminaryDocument12 pages32K X 8 Magnetic Nonvolatile CMOS RAM: Preliminarytecnicogato27No ratings yet

- Atmel 29C256 MemoryDocument17 pagesAtmel 29C256 MemoryYoseth Jose Vasquez ParraNo ratings yet

- 16K (2Kx8) Parallel Eeproms AT28C16: FeaturesDocument12 pages16K (2Kx8) Parallel Eeproms AT28C16: FeaturesWilmer OscoNo ratings yet

- IS64WV64Document21 pagesIS64WV64Mizael Medeiros dos SantosNo ratings yet

- 1-Megabit (128K X 8) 5-Volt Only Flash Memory AT29C010A: FeaturesDocument19 pages1-Megabit (128K X 8) 5-Volt Only Flash Memory AT29C010A: FeaturesGeniuss JplNo ratings yet

- Memória 29L3211Document38 pagesMemória 29L3211Rafael GarciaNo ratings yet

- Memória de OperaçãoDocument5 pagesMemória de OperaçãoRafael GarciaNo ratings yet

- Cy7c1019cv33 12zcDocument8 pagesCy7c1019cv33 12zcTuhin KarakNo ratings yet

- K6X4016C3F Family Cmos Sram: Document TitleDocument10 pagesK6X4016C3F Family Cmos Sram: Document TitledarezenaNo ratings yet

- FlashMemory-DataSheets Atmel Elenota - PLDocument13 pagesFlashMemory-DataSheets Atmel Elenota - PLriegerautoNo ratings yet

- AT28HC256Document16 pagesAT28HC256Harris RaoNo ratings yet

- W27C512Document16 pagesW27C512algnben1746No ratings yet

- X28C256P 25Document24 pagesX28C256P 25malca53328No ratings yet

- 61 64WV10248Document19 pages61 64WV10248Tan Hung LuuNo ratings yet

- 1-Megabit (128K X 8) 3-Volt Only Flash Memory AT29LV010A: FeaturesDocument16 pages1-Megabit (128K X 8) 3-Volt Only Flash Memory AT29LV010A: FeaturesDuc Luu VuNo ratings yet

- Eeprom At28c64Document14 pagesEeprom At28c64Manuel FonsecaNo ratings yet

- 16K (2K X 8) Cmos Eeprom: Features Package TypesDocument8 pages16K (2K X 8) Cmos Eeprom: Features Package TypesvanmarteNo ratings yet

- UM61512A Series: 64K X 8 Bit High Speed Cmos SramDocument16 pagesUM61512A Series: 64K X 8 Bit High Speed Cmos SramCarlos ReisNo ratings yet

- Features: Description:: High-Speed 4K X 9Dual-Port Static RamDocument11 pagesFeatures: Description:: High-Speed 4K X 9Dual-Port Static RamEdward MahNo ratings yet

- 64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesDocument12 pages64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesbacagratisNo ratings yet

- AT49F512Document11 pagesAT49F512Jaroslav AcsNo ratings yet

- 256-Kbit (32K × 8) Static RAM: Features Functional DescriptionDocument16 pages256-Kbit (32K × 8) Static RAM: Features Functional DescriptionMurilo Smse SmseNo ratings yet

- SN74LS138 1-Of-8 Decoder/ Demultiplexer: LOW Power SchottkyDocument8 pagesSN74LS138 1-Of-8 Decoder/ Demultiplexer: LOW Power SchottkySiwo HonkaiNo ratings yet

- CMOS Static RAM 16K (2K X 8-Bit) : Features DescriptionDocument13 pagesCMOS Static RAM 16K (2K X 8-Bit) : Features DescriptionTấn Long Đoàn NguyễnNo ratings yet

- Sram - Cy7c199dDocument16 pagesSram - Cy7c199dbrunex000No ratings yet

- AS6C4008 DatasheetDocument15 pagesAS6C4008 DatasheetrectibeiraNo ratings yet

- 1-Mbit (128 K × 8) Static RAM: Features Functional DescriptionDocument18 pages1-Mbit (128 K × 8) Static RAM: Features Functional Descriptionjj71No ratings yet

- MX29F800Document42 pagesMX29F800Gudda BhaiNo ratings yet

- Eeprom 29c040Document13 pagesEeprom 29c040api-3710567No ratings yet

- Cmos Sram K6X1008C2D Family: Document TitleDocument10 pagesCmos Sram K6X1008C2D Family: Document TitleНиколайNo ratings yet

- S H Microelectronics Corp.: AM OPDocument12 pagesS H Microelectronics Corp.: AM OPagcauchiNo ratings yet

- CAT28F010: Licensed Intel Second SourceDocument14 pagesCAT28F010: Licensed Intel Second SourceMorteza BaratzadehNo ratings yet

- LP621024D Series: 128K X 8 Bit Cmos SramDocument16 pagesLP621024D Series: 128K X 8 Bit Cmos SramClaudiney BricksNo ratings yet

- 256K X 4 Static RAM: PreliminaryDocument10 pages256K X 4 Static RAM: PreliminaryedgarlibanioNo ratings yet

- MX26L6420Document39 pagesMX26L6420DarleiDuarteNo ratings yet

- 256 Kilobit (32 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsDocument12 pages256 Kilobit (32 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsAmine EmineNo ratings yet

- AT29C040A-p (FLASH)Document17 pagesAT29C040A-p (FLASH)abolfazlNo ratings yet

- CAT28C256: 32K-Bit Parallel E PromDocument10 pagesCAT28C256: 32K-Bit Parallel E PromAhmed AlsheikhNo ratings yet

- 512K (64K X 8) Otp Eprom AT27C512R: FeaturesDocument12 pages512K (64K X 8) Otp Eprom AT27C512R: FeaturesAndrea MartinezNo ratings yet

- Features General Description: AUGUST 2009 AS6C4008Document15 pagesFeatures General Description: AUGUST 2009 AS6C4008Carlos ReisNo ratings yet

- MX29F400TDocument44 pagesMX29F400TMhb AliloNo ratings yet

- X28C64 64K 8K X 8 Bit: Plastic Dip Cerdip Flat Pack Soic Tsop LCC PLCCDocument26 pagesX28C64 64K 8K X 8 Bit: Plastic Dip Cerdip Flat Pack Soic Tsop LCC PLCCEdson CostaNo ratings yet

- Atmel AT49F040ADocument17 pagesAtmel AT49F040Aantaeus71No ratings yet

- Connector Industry: A Profile of the European Connector Industry - Market Prospects to 1999From EverandConnector Industry: A Profile of the European Connector Industry - Market Prospects to 1999No ratings yet

- LM7900Document47 pagesLM7900nivaldo de oliveira OliveiraNo ratings yet

- LM191 PDFDocument14 pagesLM191 PDFvanhuong87No ratings yet

- Double Data Rate (DDR) SDRAMDocument83 pagesDouble Data Rate (DDR) SDRAMvanhuong87No ratings yet

- UNCGen SCH 14062007 OCRDocument72 pagesUNCGen SCH 14062007 OCRvanhuong87No ratings yet

- Ucc3580 4Document20 pagesUcc3580 4vanhuong87No ratings yet

- 4 PDFDocument14 pages4 PDFPanagiotis PanagosNo ratings yet

- Power Integrated Circuit: Switching Regulator 5 Amp Positive and Negative Power Output StagesDocument2 pagesPower Integrated Circuit: Switching Regulator 5 Amp Positive and Negative Power Output Stagesvanhuong87No ratings yet

- Ucc 2895Document59 pagesUcc 2895vanhuong87No ratings yet

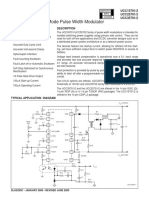

- Advanced Regulating Pulse Width Modulators: Description FeaturesDocument8 pagesAdvanced Regulating Pulse Width Modulators: Description Featuresvanhuong87No ratings yet

- Lmx93, Lm2903 Dual Differential Comparators: 1 Features 3 DescriptionDocument25 pagesLmx93, Lm2903 Dual Differential Comparators: 1 Features 3 DescriptionДмитрий МассалитинNo ratings yet

- Features Description: D D D D D D D D D D D DDocument16 pagesFeatures Description: D D D D D D D D D D D D1eugen1No ratings yet

- Advanced Voltage Mode Pulse Width Modulator: Description FeaturesDocument24 pagesAdvanced Voltage Mode Pulse Width Modulator: Description Featuresvanhuong87No ratings yet

- Current Mode PWM Controller: Features DescriptionDocument10 pagesCurrent Mode PWM Controller: Features DescriptionGris RiveroNo ratings yet

- Atmega 165 PDocument365 pagesAtmega 165 Pvanhuong87No ratings yet

- Sentinel Pro ManualDocument26 pagesSentinel Pro Manualjohnpreston44No ratings yet

- 68NPSDocument108 pages68NPSma11ikNo ratings yet

- Data Sheet: Hfbr-0400Z, Hfbr-14Xxz and Hfbr-24Xxz SeriesDocument25 pagesData Sheet: Hfbr-0400Z, Hfbr-14Xxz and Hfbr-24Xxz Seriesvanhuong87No ratings yet

- Sentinel Pro ManualDocument26 pagesSentinel Pro Manualjohnpreston44No ratings yet

- Coolset ™ Q1 Ice2Qr2280G-1: Powermanagement&MultimarketDocument27 pagesCoolset ™ Q1 Ice2Qr2280G-1: Powermanagement&Multimarketvanhuong87No ratings yet

- ATM12232B-FL-YBW: Graphic Dot Matrix LCD ModulesDocument2 pagesATM12232B-FL-YBW: Graphic Dot Matrix LCD Modulesvanhuong87No ratings yet

- Powerful and Expandable Digital Controller Module For Management of Digital and Analogue DC Power SystemsDocument2 pagesPowerful and Expandable Digital Controller Module For Management of Digital and Analogue DC Power Systemsvanhuong87No ratings yet

- Super Junction MOSFET: APT47N60HC3Document2 pagesSuper Junction MOSFET: APT47N60HC3vanhuong87No ratings yet

- 2 Pcs 01Document19 pages2 Pcs 01Vu van VuNo ratings yet

- Delta Monitoring Solution: Quick, Simple, Reliable. Always Care About Your Needs !Document3 pagesDelta Monitoring Solution: Quick, Simple, Reliable. Always Care About Your Needs !vanhuong87No ratings yet

- Sentinel Pro ManualDocument26 pagesSentinel Pro Manualjohnpreston44No ratings yet

- MP1570A W1723AE Opm4 e 8 0Document286 pagesMP1570A W1723AE Opm4 e 8 0vanhuong87No ratings yet

- Catalog PDFDocument50 pagesCatalog PDFCarvajal E MauricioNo ratings yet

- Delta Power PDFDocument62 pagesDelta Power PDFvanhuong87No ratings yet

- Delta Smps 4 U RackDocument40 pagesDelta Smps 4 U RackdeepakNo ratings yet

- Beewarp ManualDocument62 pagesBeewarp Manualvanhuong87No ratings yet

- History and Philo of ScienceDocument5 pagesHistory and Philo of ScienceJan Oliver YaresNo ratings yet

- Index PDFDocument159 pagesIndex PDFHüseyin IşlakNo ratings yet

- Chapter Three: 1 - The Coarse Grain SoilsDocument21 pagesChapter Three: 1 - The Coarse Grain SoilsSalih MohayaddinNo ratings yet

- Tsel Manual ThermoselDocument25 pagesTsel Manual ThermoselPedro AlvelaisNo ratings yet

- Reactive Dyes For Digital Textile Printing InksDocument4 pagesReactive Dyes For Digital Textile Printing InksDHRUVNo ratings yet

- Resumen C37 010 Aplicacion de Breaker Disenados IC Simetrica PDFDocument9 pagesResumen C37 010 Aplicacion de Breaker Disenados IC Simetrica PDFglendathais100% (1)

- Energy Transfer in Cell During Exercise and Oxygen Metabolism and Transport - PalakDocument85 pagesEnergy Transfer in Cell During Exercise and Oxygen Metabolism and Transport - Palakpalooo4No ratings yet

- Apcotide 1000 pc2782Document1 pageApcotide 1000 pc2782hellmanyaNo ratings yet

- Multiple Choice Enzymes Plant and Animal NutritionDocument44 pagesMultiple Choice Enzymes Plant and Animal Nutritionliufanjing07No ratings yet

- Rac Question PaperDocument84 pagesRac Question PaperibrahimNo ratings yet

- John Sisler CISSP Study GuideDocument126 pagesJohn Sisler CISSP Study GuideAnthonyNo ratings yet

- DCS YokogawaDocument17 pagesDCS Yokogawasswahyudi100% (1)

- Math 202 Syllabus-Spring18 PDFDocument2 pagesMath 202 Syllabus-Spring18 PDFvonacoc49No ratings yet

- Maths All FormulasDocument5 pagesMaths All FormulasVishnuNo ratings yet

- 9701 w09 QP 21Document12 pages9701 w09 QP 21Hubbak KhanNo ratings yet

- Chapter 04 Product and ServDocument43 pagesChapter 04 Product and ServAlireza AlborziNo ratings yet

- Is 4031 Part 4 - ConsistencyDocument4 pagesIs 4031 Part 4 - ConsistencyCrypto AbhishekNo ratings yet

- Vehicle Intercom Systems (VIS)Document4 pagesVehicle Intercom Systems (VIS)bbeisslerNo ratings yet

- Binder 3 of 4 Dec-2018Document1,169 pagesBinder 3 of 4 Dec-2018Anonymous OEmUQuNo ratings yet

- Banachek UnlimitedDocument34 pagesBanachek UnlimitedserenaNo ratings yet

- BECO UACE Chem2Document6 pagesBECO UACE Chem2EMMANUEL BIRUNGINo ratings yet

- How To Eat WellDocument68 pagesHow To Eat WelleledidiNo ratings yet

- Ni Elvis ManualDocument98 pagesNi Elvis ManualZhi YiNo ratings yet

- LighthouseDocument4 pagesLighthousejaneborn5345No ratings yet

- Chemistry Notes: SUBJECT: Leaving Cert Chemistry Level: TEACHER: Tara LyonsDocument5 pagesChemistry Notes: SUBJECT: Leaving Cert Chemistry Level: TEACHER: Tara LyonsSevinc NuriyevaNo ratings yet

- Conformational Analysis: Carey & Sundberg: Part A Chapter 3Document53 pagesConformational Analysis: Carey & Sundberg: Part A Chapter 3Dr-Dinesh Kumar100% (1)

- QuantAssay Software Manual 11-Mar-2019Document51 pagesQuantAssay Software Manual 11-Mar-2019LykasNo ratings yet