Professional Documents

Culture Documents

Icl8038 PDF

Uploaded by

marcosOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Icl8038 PDF

Uploaded by

marcosCopyright:

Available Formats

NO R OBSOLET

E

DATASHEET

conta COMMEN E PRODU

ct ou DED C

1-888 r REPL T

-INTE Technica A CEM

ICL8038 RSIL l

or ww Support C ENT FN2864

w.inte en

Precision Waveform Generator/Voltage Controlled Oscillator rsil.c ter at Rev.4.00

om/ts

c Apr 2001

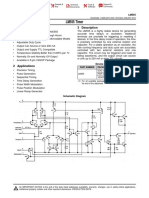

The ICL8038 waveform generator is a monolithic integrated Features

circuit capable of producing high accuracy sine, square,

triangular, sawtooth and pulse waveforms with a minimum of • Low Frequency Drift with Temperature. . . . . . 250ppm/oC

external components. The frequency (or repetition rate) can • Low Distortion . . . . . . . . . . . . . . . 1% (Sine Wave Output)

be selected externally from 0.001Hz to more than 300kHz

• High Linearity . . . . . . . . . . . 0.1% (Triangle Wave Output)

using either resistors or capacitors, and frequency

modulation and sweeping can be accomplished with an • Wide Frequency Range . . . . . . . . . . . .0.001Hz to 300kHz

external voltage. The ICL8038 is fabricated with advanced • Variable Duty Cycle . . . . . . . . . . . . . . . . . . . . . 2% to 98%

monolithic technology, using Schottky barrier diodes and thin

film resistors, and the output is stable over a wide range of • High Level Outputs. . . . . . . . . . . . . . . . . . . . . . TTL to 28V

temperature and supply variations. These devices may be • Simultaneous Sine, Square, and Triangle Wave

interfaced with phase locked loop circuitry to reduce Outputs

temperature drift to less than 250ppm/oC.

• Easy to Use - Just a Handful of External Components

Required

Ordering Information

PART NUMBER STABILITY TEMP. RANGE (oC) PACKAGE PKG. NO.

ICL8038CCPD 250ppm/oC (Typ) 0 to 70 14 Ld PDIP E14.3

ICL8038CCJD 250ppm/oC (Typ) 0 to 70 14 Ld CERDIP F14.3

ICL8038BCJD 180ppm/oC (Typ) 0 to 70 14 Ld CERDIP F14.3

ICL8038ACJD 120ppm/oC (Typ) 0 to 70 14 Ld CERDIP F14.3

Pinout Functional Diagram

ICL8038

V+

(PDIP, CERDIP) 6

TOP VIEW CURRENT

SOURCE

#1 COMPARATOR

I #1

SINE WAVE 1 14 NC 10

ADJUST

SINE 2I

2 13 NC C COMPARATOR

WAVE OUT

#2

TRIANGLE

3 12 SINE WAVE

OUT ADJUST

DUTY CYCLE 4 11 V- OR GND

FREQUENCY

ADJUST 5 10 TIMING CURRENT

CAPACITOR SOURCE FLIP-FLOP

6 9 SQUARE #2

V+

WAVE OUT V- OR GND

FM SWEEP 11

FM BIAS 7 8

INPUT

SINE

BUFFER BUFFER CONVERTER

9 3 2

FN2864 Rev.4.00 Page 1 of 12

Apr 2001

ICL8038

Absolute Maximum Ratings Thermal Information

Supply Voltage (V- to V+). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36V Thermal Resistance (Typical, Note 1) JA (oC/W) JC (oC/W)

Input Voltage (Any Pin) . . . . . . . . . . . . . . . . . . . . . . . . . . . . V- to V+ CERDIP Package. . . . . . . . . . . . . . . . . 75 20

Input Current (Pins 4 and 5). . . . . . . . . . . . . . . . . . . . . . . . . . . 25mA PDIP Package . . . . . . . . . . . . . . . . . . . 115 N/A

Output Sink Current (Pins 3 and 9) . . . . . . . . . . . . . . . . . . . . . 25mA Maximum Junction Temperature (Ceramic Package) . . . . . . . .175oC

Maximum Junction Temperature (Plastic Package) . . . . . . . .150oC

Operating Conditions Maximum Storage Temperature Range . . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

Temperature Range

ICL8038AC, ICL8038BC, ICL8038CC . . . . . . . . . . . . 0oC to 70oC

Die Characteristics

Back Side Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V-

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications VSUPPLY = 10V or +20V, TA = 25oC, RL = 10k, Test Circuit Unless Otherwise Specified

ICL8038CC ICL8038BC ICL8038AC

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX MIN TYP MAX MIN TYP MAX UNITS

Supply Voltage Operating Range VSUPPLY

V+ Single Supply +10 - +30 +10 - +30 +10 - +30 V

V+, V- Dual Supplies 5 - 15 5 - 15 5 - 15 V

Supply Current ISUPPLY VSUPPLY = 10V 12 20 - 12 20 - 12 20 mA

(Note 2)

FREQUENCY CHARACTERISTICS (All Waveforms)

Max. Frequency of Oscillation fMAX 100 - - 100 - - 100 - - kHz

Sweep Frequency of FM Input fSWEEP - 10 - - 10 - - 10 - kHz

Sweep FM Range (Note 3) - 35:1 - - 35:1 - - 35:1 -

FM Linearity 10:1 Ratio - 0.5 - - 0.2 - - 0.2 - %

Frequency Drift with f/T 0oC to 70oC - 250 - - 180 - - 120 ppm/oC

Temperature (Note 5)

Frequency Drift with Supply Voltage f/V Over Supply - 0.05 - - 0.05 - 0.05 - %/V

Voltage Range

OUTPUT CHARACTERISTICS

Square Wave

Leakage Current IOLK V9 = 30V - - 1 - - 1 - - 1 A

Saturation Voltage VSAT ISINK = 2mA - 0.2 0.5 - 0.2 0.4 - 0.2 0.4 V

Rise Time tR RL = 4.7k - 180 - - 180 - - 180 - ns

Fall Time tF RL = 4.7k - 40 - - 40 - - 40 - ns

Typical Duty Cycle Adjust D 2 98 2 - 98 2 - 98 %

(Note 6)

Triangle/Sawtooth/Ramp -

Amplitude VTRIAN- RTRI = 100k 0.30 0.33 - 0.30 0.33 - 0.30 0.33 - xVSUPPLY

GLE

Linearity - 0.1 - - 0.05 - - 0.05 - %

Output Impedance ZOUT IOUT = 5mA - 200 - - 200 - - 200 -

FN2864 Rev.4.00 Page 2 of 12

Apr 2001

ICL8038

Electrical Specifications VSUPPLY = 10V or +20V, TA = 25oC, RL = 10k, Test Circuit Unless Otherwise Specified (Continued)

ICL8038CC ICL8038BC ICL8038AC

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX MIN TYP MAX MIN TYP MAX UNITS

Sine Wave

Amplitude VSINE RSINE = 100k 0.2 0.22 - 0.2 0.22 - 0.2 0.22 - xVSUPPLY

THD THD RS = 1M - 2.0 5 - 1.5 3 - 1.0 1.5 %

(Note 4)

THD Adjusted THD Use Figure 4 - 1.5 - - 1.0 - - 0.8 - %

NOTES:

2. RA and RB currents not included.

3. VSUPPLY = 20V; RA and RB = 10k, f 10kHz nominal; can be extended 1000 to 1. See Figures 5A and 5B.

4. 82k connected between pins 11 and 12, Triangle Duty Cycle set at 50%. (Use RA and RB.)

5. Figure 1, pins 7 and 8 connected, VSUPPLY = 10V. See Typical Curves for T.C. vs VSUPPLY.

6. Not tested, typical value for design purposes only.

Test Conditions

PARAMETER RA RB RL C SW1 MEASURE

Supply Current 10k 10k 10k 3.3nF Closed Current Into Pin 6

Sweep FM Range (Note 7) 10k 10k 10k 3.3nF Open Frequency at Pin 9

Frequency Drift with Temperature 10k 10k 10k 3.3nF Closed Frequency at Pin 3

Frequency Drift with Supply Voltage (Note 8) 10k 10k 10k 3.3nF Closed Frequency at Pin 9

Output Amplitude (Note 10)

Sine 10k 10k 10k 3.3nF Closed Pk-Pk Output at Pin 2

Triangle 10k 10k 10k 3.3nF Closed Pk-Pk Output at Pin 3

Leakage Current (Off) (Note 9) 10k 10k 3.3nF Closed Current into Pin 9

Saturation Voltage (On) (Note 9) 10k 10k 3.3nF Closed Output (Low) at Pin 9

Rise and Fall Times (Note 11) 10k 10k 4.7k 3.3nF Closed Waveform at Pin 9

Duty Cycle Adjust (Note 11)

Max 50k ~1.6k 10k 3.3nF Closed Waveform at Pin 9

Min ~25k 50k 10k 3.3nF Closed Waveform at Pin 9

Triangle Waveform Linearity 10k 10k 10k 3.3nF Closed Waveform at Pin 3

Total Harmonic Distortion 10k 10k 10k 3.3nF Closed Waveform at Pin 2

NOTES:

7. The hi and lo frequencies can be obtained by connecting pin 8 to pin 7 (fHI) and then connecting pin 8 to pin 6 (fLO). Otherwise apply Sweep

Voltage at pin 8 (2/3 VSUPPLY +2V) VSWEEP VSUPPLY where VSUPPLY is the total supply voltage. In Figure 5B, pin 8 should vary between

5.3V and 10V with respect to ground.

8. 10V V+ 30V, or 5V VSUPPLY 15V.

9. Oscillation can be halted by forcing pin 10 to +5V or -5V.

10. Output Amplitude is tested under static conditions by forcing pin 10 to 5V then to -5V.

11. Not tested; for design purposes only.

FN2864 Rev.4.00 Page 3 of 12

Apr 2001

ICL8038

Test Circuit

+10V

RA RB RL

10K 10K 10K

7 4 5 6 9

SW1

N.C.

8 ICL8038 3

RTRI

10 11 12 2

C RSINE

82K

3300pF

-10V

FIGURE 1. TEST CIRCUIT

Detailed Schematic

CURRENT SOURCES 6

V+

R41 R32

REXT B REXT A

R1 4K 5.2K

8 Q1 5

11K 4 Q14

Q2 Q48 1

7 R8

Q3 Q47 R33

R2 5K

Q R19 200

39K 6 Q4 Q5 Q46

COMPARATOR 800 Q45 R34

Q7 R20 375

Q8 Q9 Q44

10

Q15 Q18 2.7K

R46 Q43 R35

R21

40K

CEXT Q16Q17 330

R9 Q42

5K 10K

R7B R7A Q41

Q10

R3 R25 R26 R27 R45

Q11 15K 10K

30K 33K 33K 33K 33K

Q12 R36

Q30

Q13 Q20 Q21 1600

Q31 Q19 Q22

R4 R5 R6 R28 R29 R30 R31

Q32 100 100 100 R10 33K 33K 33K 33K

5K Q49

Q33 R22

Q50

Q34

R13 R16 R43 10K Q51 R37

620 1.8K 27K R23 330

Q24 Q52

9 R14 Q37 2.7K Q53 R38

Q35 Q39

27K R24 375

R11 Q36 Q Q54

270 38 Q40

R41 3 R44 800 R39

Q23 Q26 Q28 Q55

Q27 200

27K 1K 12

R12 R15 R17 Q56

2.7K 470 4.7K R40

R42 REXTC

Q25 Q29 BUFFER AMPLIFIER 2 5.6K

27K 11 82K

R18

4.7K SINE CONVERTER

FLIP-FLOP

Application Information (See Functional Diagram) across it drops linearly with time. When it has reached the level

of comparator #2 (set at 1/3 of the supply voltage), the flip-flop is

An external capacitor C is charged and discharged by two

triggered into its original state and the cycle starts again.

current sources. Current source #2 is switched on and off by a

flip-flop, while current source #1 is on continuously. Assuming Four waveforms are readily obtainable from this basic

that the flip-flop is in a state such that current source #2 is off, generator circuit. With the current sources set at I and 2I

and the capacitor is charged with a current I, the voltage across respectively, the charge and discharge times are equal. Thus a

the capacitor rises linearly with time. When this voltage reaches triangle waveform is created across the capacitor and the flip-

the level of comparator #1 (set at 2/3 of the supply voltage), the flop produces a square wave. Both waveforms are fed to buffer

flip-flop is triggered, changes states, and releases current stages and are available at pins 3 and 9.

source #2. This current source normally carries a current 2I, thus

the capacitor is discharged with a net-current I and the voltage

FN2864 Rev.4.00 Page 4 of 12

Apr 2001

ICL8038

The levels of the current sources can, however, be selected

CV C 1/3 V SUPPLY R A RA C

over a wide range with two external resistors. Therefore, with t 1 = -------------- = ------------------------------------------------------------------- = ------------------

I 0.22 V SUPPLY 0.66

the two currents set at values different from I and 2I, an

The falling portion of the triangle and sine wave and the 0 state

asymmetrical sawtooth appears at Terminal 3 and pulses with

of the square wave is:

a duty cycle from less than 1% to greater than 99% are

CV C 1/3V SUPPLY R R C

A B

available at Terminal 9. t2 = ------------- = ----------------------------------------------------------------------------------- = -------------------------------------

1 V

SUPPLY

V

SUPPLY 0.66 2R A – R B

2 0.22 ------------------------ – 0.22 ------------------------

The sine wave is created by feeding the triangle wave into a R

B

R

A

nonlinear network (sine converter). This network provides a Thus a 50% duty cycle is achieved when RA = RB.

decreasing shunt impedance as the potential of the triangle

If the duty cycle is to be varied over a small range about 50%

moves toward the two extremes.

only, the connection shown in Figure 3B is slightly more

Waveform Timing convenient. A 1k potentiometer may not allow the duty cycle to

The symmetry of all waveforms can be adjusted with the be adjusted through 50% on all devices. If a 50% duty cycle is

external timing resistors. Two possible ways to accomplish this required, a 2k or 5k potentiometer should be used.

are shown in Figure 3. Best results are obtained by keeping the With two separate timing resistors, the frequency is given by:

timing resistors RA and RB separate (A). RA controls the rising 1 1

f = ---------------- = ------------------------------------------------------

portion of the triangle and sine wave and the 1 state of the t1 + t2 RA C RB

------------ 1 + -------------------------

square wave. 0.66 2R A – R B

The magnitude of the triangle waveform is set at 1/3 VSUPPLY; or, if RA = RB = R

therefore the rising portion of the triangle is, 0.33

f = ----------- (for Figure 3A)

RC

FIGURE 2A. SQUARE WAVE DUTY CYCLE - 50% FIGURE 2B. SQUARE WAVE DUTY CYCLE - 80%

FIGURE 2. PHASE RELATIONSHIP OF WAVEFORMS

V+

V+

1k RL

RA RB RL RA RB

7 4 5 6 9 7 4 5 6 9

8 ICL8038 3 8 ICL8038 3

10 11 12 2 10 11 12 2

C 82K C 100K

V- OR GND V- OR GND

FIGURE 3A. FIGURE 3B.

FIGURE 3. POSSIBLE CONNECTIONS FOR THE EXTERNAL TIMING RESISTORS

FN2864 Rev.4.00 Page 5 of 12

Apr 2001

ICL8038

Neither time nor frequency are dependent on supply voltage, Waveform Out Level Control and Power Supplies

even though none of the voltages are regulated inside the The waveform generator can be operated either from a single

integrated circuit. This is due to the fact that both currents and power supply (10V to 30V) or a dual power supply (5V to

thresholds are direct, linear functions of the supply voltage and 15V). With a single power supply the average levels of the

thus their effects cancel. triangle and sine wave are at exactly one-half of the supply

Reducing Distortion voltage, while the square wave alternates between V+ and

ground. A split power supply has the advantage that all

To minimize sine wave distortion the 82k resistor between

waveforms move symmetrically about ground.

pins 11 and 12 is best made variable. With this arrangement

distortion of less than 1% is achievable. To reduce this even The square wave output is not committed. A load resistor can

further, two potentiometers can be connected as shown in be connected to a different power supply, as long as the

Figure 4; this configuration allows a typical reduction of sine applied voltage remains within the breakdown capability of the

wave distortion close to 0.5%. waveform generator (30V). In this way, the square wave output

can be made TTL compatible (load resistor connected to +5V)

while the waveform generator itself is powered from a much

V+ higher voltage.

1k RL

RA RB

Frequency Modulation and Sweeping

7 4 5 6 9 The frequency of the waveform generator is a direct function of

the DC voltage at Terminal 8 (measured from V+). By altering

this voltage, frequency modulation is performed. For small

8 ICL8038 3

deviations (e.g. 10%) the modulating signal can be applied

directly to pin 8, merely providing DC decoupling with a

2

capacitor as shown in Figure 5A. An external resistor between

10 11 12 1

100k 10k pins 7 and 8 is not necessary, but it can be used to increase

input impedance from about 8k (pins 7 and 8 connected

C

100k together), to about (R + 8k).

10k

For larger FM deviations or for frequency sweeping, the

V- OR GND modulating signal is applied between the positive supply

FIGURE 4. CONNECTION TO ACHIEVE MINIMUM SINE WAVE voltage and pin 8 (Figure 5B). In this way the entire bias for the

DISTORTION current sources is created by the modulating signal, and a very

large (e.g. 1000:1) sweep range is created (f = Minimum at

VSWEEP = 0, i.e., Pin 8 = V+). Care must be taken, however, to

Selecting RA, RB and C regulate the supply voltage; in this configuration the charge

For any given output frequency, there is a wide range of RC current is no longer a function of the supply voltage (yet the

combinations that will work, however certain constraints are trigger thresholds still are) and thus the frequency becomes

placed upon the magnitude of the charging current for optimum dependent on the supply voltage. The potential on Pin 8 may

performance. At the low end, currents of less than 1A are be swept down from V+ by (1/3 VSUPPLY - 2V).

undesirable because circuit leakages will contribute significant V+

errors at high temperatures. At higher currents (I > 5mA),

RA RB RL

transistor betas and saturation voltages will contribute

increasingly larger errors. Optimum performance will,

7 4 5 6 9

therefore, be obtained with charging currents of 10A to 1mA.

If pins 7 and 8 are shorted together, the magnitude of the R

charging current due to RA can be calculated from: 8 ICL8038 3

R 1 V+ – V- 1 0.22 V+ – V-

I = ---------------------------------------- -------- = ------------------------------------ FM

R1 + R2 RA RA 10 11 12 2

R1 and R2 are shown in the Detailed Schematic. C 81K

V- OR GND

A similar calculation holds for RB.

The capacitor value should be chosen at the upper end of its FIGURE 5A. CONNECTIONS FOR FREQUENCY MODULATION

possible range.

FN2864 Rev.4.00 Page 6 of 12

Apr 2001

ICL8038

V+ V+

SWEEP RA RB RL RA RB 15K

VOLTAGE

4 5 6 7 4 5 9

9

8 ICL8038 3 8 ICL8038

1N914

2

10 11 12 2 11 10

1N914

C 81K C 2N4392 STROBE

V- OR GND 100K

-15V

OFF

FIGURE 5B. CONNECTIONS FOR FREQUENCY SWEEP +15V (+10V)

FIGURE 5. -15V (-10V)

ON

FIGURE 7. STROBE TONE BURST GENERATOR

Typical Applications

The sine wave output has a relatively high output impedance To obtain a 1000:1 Sweep Range on the ICL8038 the voltage

(1k Typ). The circuit of Figure 6 provides buffering, gain and across external resistors RA and RB must decrease to nearly

amplitude adjustment. A simple op amp follower could also be zero. This requires that the highest voltage on control Pin 8

used. exceed the voltage at the top of RA and RB by a few hundred

mV. The Circuit of Figure 8 achieves this by using a diode to

V+ lower the effective supply voltage on the ICL8038. The large

resistor on pin 5 helps reduce duty cycle variations with sweep.

RA RB

The linearity of input sweep voltage versus output frequency

AMPLITUDE can be significantly improved by using an op amp as shown in

7 4 5 6 2

Figure 10.

+

100K 741

8 ICL8038 - +10V

20K

1N457

10 11 4.7K DUTY CYCLE

0.1F 15K

1K

C 4.7K 4.7K

V-

FIGURE 6. SINE WAVE OUTPUT BUFFER AMPLIFIERS 5 4 6 9

10K

With a dual supply voltage the external capacitor on Pin 10 can be FREQ. 8 ICL8038 3

shorted to ground to halt the ICL8038 oscillation. Figure 7 shows

a FET switch, diode ANDed with an input strobe signal to allow

10 11 12 2

the output to always start on the same slope.

20K 15M 0.0047F DISTORTION

100K

-10V

FIGURE 8. VARIABLE AUDIO OSCILLATOR, 20Hz TO 20kHzY

FN2864 Rev.4.00 Page 7 of 12

Apr 2001

ICL8038

V2+

DUTY

CYCLE

R1

FREQUENCY TRIANGLE

ADJUST OUT

FM BIAS

V1+ 6

7 4 5 3

SQUARE SINE WAVE

WAVE OUT

OUT

9 ICL8038 2

VCO DEMODULATED

IN SINE WAVE

INPUT PHASE AMPLIFIER FM 1

8 10 11 12 ADJ.

DETECTOR R2

TIMING SINE WAVE

CAP. ADJ.

LOW PASS

FILTER

V-/GND

FIGURE 9. WAVEFORM GENERATOR USED AS STABLE VCO IN A PHASE-LOCKED LOOP

HIGH FREQUENCY

SYMMETRY

10k 100k

500

1N753A

4.7k 4.7k

(6.2V) 1M

1k 100k

1,000pF LOW FREQUENCY

4 5 6 9 SYMMETRY

+15V

- 1k SINE WAVE

ICL8038 +15V OUTPUT

741 8 3

FUNCTION GENERATOR

+ -

-VIN P4 741

+ +

10 11 12 2

10k 50F

OFFSET 100k 15V

3,900pF SINE WAVE

DISTORTION

-15V

FIGURE 10. LINEAR VOLTAGE CONTROLLED OSCILLATOR

Use in Phase Locked Loops

Its high frequency stability makes the ICL8038 an ideal building Second, the DC output level of the amplifier must be made

block for a phase locked loop as shown in Figure 9. In this compatible to the DC level required at the FM input of the

application the remaining functional blocks, the phase detector waveform generator (pin 8, 0.8V+). The simplest solution here is

and the amplifier, can be formed by a number of available ICs to provide a voltage divider to V+ (R1, R2 as shown) if the

(e.g., MC4344, NE562). amplifier has a lower output level, or to ground if its level is

higher. The divider can be made part of the low-pass filter.

In order to match these building blocks to each other, two steps

must be taken. First, two different supply voltages are used This application not only provides for a free-running frequency

and the square wave output is returned to the supply of the with very low temperature drift, but is also has the unique

phase detector. This assures that the VCO input voltage will feature of producing a large reconstituted sinewave signal with

not exceed the capabilities of the phase detector. If a smaller a frequency identical to that at the input.

VCO signal is required, a simple resistive voltage divider is

For further information, see Intersil Application Note AN013,

connected between pin 9 of the waveform generator and the

“Everything You Always Wanted to Know About the ICL8038”.

VCO input of the phase detector.

FN2864 Rev.4.00 Page 8 of 12

Apr 2001

ICL8038

Definition of Terms FM Linearity. The percentage deviation from the best fit

straight line on the control voltage versus output frequency

Supply Voltage (VSUPPLY). The total supply voltage from V+

curve.

to V-.

Output Amplitude. The peak-to-peak signal amplitude

Supply Current. The supply current required from the power

appearing at the outputs.

supply to operate the device, excluding load currents and the

currents through RA and RB. Saturation Voltage. The output voltage at the collector of Q23

when this transistor is turned on. It is measured for a sink

Frequency Range. The frequency range at the square wave

current of 2mA.

output through which circuit operation is guaranteed.

Rise and Fall Times. The time required for the square wave

Sweep FM Range. The ratio of maximum frequency to

output to change from 10% to 90%, or 90% to 10%, of its final

minimum frequency which can be obtained by applying a

value.

sweep voltage to pin 8. For correct operation, the sweep

voltage should be within the range: Triangle Waveform Linearity. The percentage deviation from

the best fit straight line on the rising and falling triangle

(2/3 VSUPPLY + 2V) < VSWEEP < VSUPPLY

waveform.

Total Harmonic Distortion. The total harmonic distortion at

the sine wave output.

Typical Performance Curves

20 1.03

1.02

NORMALIZED FREQUENCY

SUPPLY CURRENT (mA)

-55oC

15 1.01

125oC 1.00

10 25oC 0.99

0.98

5

5 10 15 20 25 30 5 10 15 20 25 30

SUPPLY VOLTAGE (V) SUPPLY VOLTAGE (V)

FIGURE 11. SUPPLY CURRENT vs SUPPLY VOLTAGE FIGURE 12. FREQUENCY vs SUPPLY VOLTAGE

1.03 200

1.02

NORMALIZED FREQUENCY

150 RISE TIME

10V 125oC

1.01 25oC

20V

TIME (ns)

30V -55oC

1.00

20V

100 125oC

10V 30V 25oC

0.99 FALL TIME

-55oC

50

0.98

0

-50 -25 0 25 75 125 0 2 4 6 8 10

TEMPERATURE (oC) LOAD RESISTANCE (k)

FIGURE 13. FREQUENCY vs TEMPERATURE FIGURE 14. SQUARE WAVE OUTPUT RISE/FALL TIME vs

LOAD RESISTANCE

FN2864 Rev.4.00 Page 9 of 12

Apr 2001

ICL8038

Typical Performance Curves (Continued)

2 1.0

NORMALIZED PEAK OUTPUT VOLTAGE

LOAD CURRENT 125oC

TO V -

25oC

SATURATION VOLTAGE

1.5

0.9

-55oC

125oC

1.0

25oC

-55oC

0.8

LOAD CURRENT TO V+

0.5

0

0 2 4 6 8 10 0 2 4 6 8 10 12 14 16 18 20

LOAD CURRENT (mA) LOAD CURRENT (mA)

FIGURE 15. SQUARE WAVE SATURATION VOLTAGE vs FIGURE 16. TRIANGLE WAVE OUTPUT VOLTAGE vs LOAD

LOAD CURRENT CURRENT

1.2 10.0

NORMALIZED OUTPUT VOLTAGE

1.1

1.0 1.0

LINEARITY (%)

0.9

0.8 0.1

0.7

0.6 0.01

10 100 1K 10K 100K 1M 10 100 1K 10K 100K 1M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 17. TRIANGLE WAVE OUTPUT VOLTAGE vs FIGURE 18. TRIANGLE WAVE LINEARITY vs FREQUENCY

FREQUENCY

1.1 12

NORMALIZED OUTPUT VOLTAGE

10

DISTORTION (%)

1.0 8

0.9 4

UNADJUSTED ADJUSTED

0

10 100 1K 10K 100K 1M 10 100 1K 10K 100K 1M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 19. SINE WAVE OUTPUT VOLTAGE vs FREQUENCY FIGURE 20. SINE WAVE DISTORTION vs FREQUENCY

FN2864 Rev.4.00 Page 10 of 12

Apr 2001

ICL8038

Dual-In-Line Plastic Packages (PDIP)

N

E14.3 (JEDEC MS-001-AA ISSUE D)

14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

E1

INDEX

1 2 3 N/2 INCHES MILLIMETERS

AREA

SYMBOL MIN MAX MIN MAX NOTES

-B-

A - 0.210 - 5.33 4

-A-

D E A1 0.015 - 0.39 - 4

BASE A2 0.115 0.195 2.93 4.95 -

PLANE A2

-C- A

B 0.014 0.022 0.356 0.558 -

SEATING

PLANE L C B1 0.045 0.070 1.15 1.77 8

L

D1 A1 eA C 0.008 0.014 0.204 0.355 -

D1

B1 e D 0.735 0.775 18.66 19.68 5

eC C

B

eB D1 0.005 - 0.13 - 5

0.010 (0.25) M C A B S

E 0.300 0.325 7.62 8.25 6

NOTES:

E1 0.240 0.280 6.10 7.11 5

1. Controlling Dimensions: INCH. In case of conflict between English

and Metric dimensions, the inch dimensions control. e 0.100 BSC 2.54 BSC -

2. Dimensioning and tolerancing per ANSI Y14.5M-1982. eA 0.300 BSC 7.62 BSC 6

3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of eB - 0.430 - 10.92 7

Publication No. 95.

L 0.115 0.150 2.93 3.81 4

4. Dimensions A, A1 and L are measured with the package seated in

JEDEC seating plane gauge GS-3. N 14 14 9

5. D, D1, and E1 dimensions do not include mold flash or protrusions. Rev. 0 12/93

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and eA are measured with the leads constrained to be perpen-

dicular to datum -C- .

7. eB and eC are measured at the lead tips with the leads uncon-

strained. eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions. Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 -

1.14mm).

© Copyright Intersil Americas LLC 2001. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN2864 Rev.4.00 Page 11 of 12

Apr 2001

ICL8038

Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

c1 LEAD FINISH F14.3 MIL-STD-1835 GDIP1-T14 (D-1, CONFIGURATION A)

-A- -D- 14 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

BASE INCHES MILLIMETERS

(c)

METAL

E SYMBOL MIN MAX MIN MAX NOTES

b1 A - 0.200 - 5.08 -

M M

-B- (b)

b 0.014 0.026 0.36 0.66 2

SECTION A-A

b1 0.014 0.023 0.36 0.58 3

bbb S C A-B S D S

b2 0.045 0.065 1.14 1.65 -

D

BASE b3 0.023 0.045 0.58 1.14 4

PLANE Q

-C- A c 0.008 0.018 0.20 0.46 2

SEATING

PLANE L c1 0.008 0.015 0.20 0.38 3

S1 D - 0.785 - 19.94 5

A A eA

b2 E 0.220 0.310 5.59 7.87 5

b e eA/2 c e 0.100 BSC 2.54 BSC -

ccc M C A-B S D S aaa M C A - B S D S eA 0.300 BSC 7.62 BSC -

eA/2 0.150 BSC 3.81 BSC -

NOTES:

1. Index area: A notch or a pin one identification mark shall be locat- L 0.125 0.200 3.18 5.08 -

ed adjacent to pin one and shall be located within the shaded Q 0.015 0.060 0.38 1.52 6

area shown. The manufacturer’s identification shall not be used

S1 0.005 - 0.13 - 7

as a pin one identification mark.

2. The maximum limits of lead dimensions b and c or M shall be 90o 105o 90o 105o -

measured at the centroid of the finished lead surfaces, when aaa - 0.015 - 0.38 -

solder dip or tin plate lead finish is applied.

bbb - 0.030 - 0.76 -

3. Dimensions b1 and c1 apply to lead base metal only. Dimension

M applies to lead plating and finish thickness. ccc - 0.010 - 0.25 -

4. Corner leads (1, N, N/2, and N/2+1) may be configured with a M - 0.0015 - 0.038 2, 3

partial lead paddle. For this configuration dimension b3 replaces N 14 14 8

dimension b2.

Rev. 0 4/94

5. This dimension allows for off-center lid, meniscus, and glass

overrun.

6. Dimension Q shall be measured from the seating plane to the

base plane.

7. Measure dimension S1 at all four corners.

8. N is the maximum number of terminal positions.

9. Dimensioning and tolerancing per ANSI Y14.5M - 1982.

10. Controlling dimension: INCH.

FN2864 Rev.4.00 Page 12 of 12

Apr 2001

You might also like

- TSPL-1905 Technical Offer Dt.16.04.2022Document4 pagesTSPL-1905 Technical Offer Dt.16.04.2022SECI 2020No ratings yet

- 通用电气GE Optima CT520Pro 全身用X射线计算机体层摄影装置7f0Document22 pages通用电气GE Optima CT520Pro 全身用X射线计算机体层摄影装置7f0service iyadMedicalNo ratings yet

- ICL8038Document14 pagesICL8038RAYLINo ratings yet

- Precision Waveform Generator/Voltage Controlled Oscillator FeaturesDocument10 pagesPrecision Waveform Generator/Voltage Controlled Oscillator FeaturesqwertyuiNo ratings yet

- 10W Amplifier With DC Volume Control: Multipower Bi50Ii TechnologyDocument13 pages10W Amplifier With DC Volume Control: Multipower Bi50Ii TechnologyfabioboogNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- Data Sheet Tda 4800Document16 pagesData Sheet Tda 4800fabioboogNo ratings yet

- Datasheet - PDF Ca723Document9 pagesDatasheet - PDF Ca723Jaime Sisalima PincayNo ratings yet

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 pagesRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNo ratings yet

- Peak 3A Bus Termination RegulatorDocument12 pagesPeak 3A Bus Termination RegulatormkubawatNo ratings yet

- CI CA1458 DatasheetDocument6 pagesCI CA1458 DatasheetRogerio EngelNo ratings yet

- D D D D D D D D D D D D: TL284x, TL384x Current-Mode PWM ControllersDocument11 pagesD D D D D D D D D D D D: TL284x, TL384x Current-Mode PWM ControllersAnonymous fAL3CNtUiNo ratings yet

- Annexure - C (Technical BOM)Document5 pagesAnnexure - C (Technical BOM)Darshit VyasNo ratings yet

- RT9173Document10 pagesRT9173duplakave30No ratings yet

- L6561Document11 pagesL6561Gilson3DNo ratings yet

- Telefone+Toshiba+FT 8808Document56 pagesTelefone+Toshiba+FT 8808api-3702225No ratings yet

- Ne5521 Sa5521 2Document11 pagesNe5521 Sa5521 2José AdelinoNo ratings yet

- Current Mode Controller AS384x SemiconductorDocument20 pagesCurrent Mode Controller AS384x SemiconductorJune SendaydiegoNo ratings yet

- KA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Document12 pagesKA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Saad LehlouNo ratings yet

- KA1L0380RDocument12 pagesKA1L0380Radisurya13.afNo ratings yet

- 5L0365RDocument20 pages5L0365RbounezraNo ratings yet

- Uc3863 Utc U863 PDFDocument9 pagesUc3863 Utc U863 PDFShailesh VajaNo ratings yet

- Features Description: Micropower Inverting DC/DC ConverterDocument6 pagesFeatures Description: Micropower Inverting DC/DC ConverterJosé FariaNo ratings yet

- Op Amp StabilityDocument32 pagesOp Amp Stabilityapdim79No ratings yet

- PM174 Powermeter Quick Start GuideDocument11 pagesPM174 Powermeter Quick Start Guideusamakhan205No ratings yet

- Pulse-Width-Modulation Control Circuits Az7500EDocument13 pagesPulse-Width-Modulation Control Circuits Az7500EMy shop Cool100% (1)

- CA3450Document8 pagesCA3450MUHAMMAD SISWANTORONo ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- Description Features: Ait Semiconductor IncDocument8 pagesDescription Features: Ait Semiconductor Incteranet tbtNo ratings yet

- TL2843B Q1 etcTIDocument18 pagesTL2843B Q1 etcTIrahma jayaNo ratings yet

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 pagesNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiNo ratings yet

- AME8500 Supervisory Reset ControllerDocument14 pagesAME8500 Supervisory Reset ControllerPierina AstudilloNo ratings yet

- TL3842 5Document12 pagesTL3842 5ajit_kmsNo ratings yet

- AS3842Document14 pagesAS3842alex castroNo ratings yet

- Ca741, Ca741c, Ca1458, Ca1558, LM741, LM741C, LM1458Document6 pagesCa741, Ca741c, Ca1458, Ca1558, LM741, LM741C, LM1458rrr2013No ratings yet

- TS78L00 Series: Taiwan SemiconductorDocument11 pagesTS78L00 Series: Taiwan SemiconductorEM JANo ratings yet

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Document8 pagesINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNo ratings yet

- Power Factor Corrector: 1 FeaturesDocument13 pagesPower Factor Corrector: 1 Featuresdeilyn rivasNo ratings yet

- TPS76030, TPS76032, TPS76033, TPS76038, TPS76050 Low-Power 50-Ma Low-Dropout Linear RegulatorsDocument17 pagesTPS76030, TPS76032, TPS76033, TPS76038, TPS76050 Low-Power 50-Ma Low-Dropout Linear RegulatorsAbdul KurniadiNo ratings yet

- T7-SCR Power Regulator Use ManualDocument48 pagesT7-SCR Power Regulator Use ManualJhon CarterNo ratings yet

- Ca3290, Ca3290A: Bimos Dual Voltage Comparators With Mosfet Input, Bipolar OutputDocument8 pagesCa3290, Ca3290A: Bimos Dual Voltage Comparators With Mosfet Input, Bipolar OutputMultiAbderrahmaneNo ratings yet

- Tv/Linear Applications RF & Microwave Transistors: Pin ConnectionDocument5 pagesTv/Linear Applications RF & Microwave Transistors: Pin ConnectionGabriel RacovskyNo ratings yet

- STB11NM80, STF11NM80 Sti11nm80, STP11NM80, STW11NM80Document22 pagesSTB11NM80, STF11NM80 Sti11nm80, STP11NM80, STW11NM80Alexandre OliveiraNo ratings yet

- TL3842PDocument18 pagesTL3842PjoelpalzaNo ratings yet

- Dual PWM Control IC with SCP/DTC FunctionDocument26 pagesDual PWM Control IC with SCP/DTC Functionmartin sembinelliNo ratings yet

- Precision Waveform Generator: ... The Analog Plus CompanyDocument17 pagesPrecision Waveform Generator: ... The Analog Plus CompanySy Phan MinhNo ratings yet

- Datasheet AME8815Document17 pagesDatasheet AME8815ALFONZO DANIELNo ratings yet

- Tea 5170Document9 pagesTea 5170Erasmo Franco SNo ratings yet

- Ka1m0880b DatasheetDocument8 pagesKa1m0880b DatasheetluisNo ratings yet

- Charge Pump Dc-To-Dc Voltage ConverterDocument11 pagesCharge Pump Dc-To-Dc Voltage ConverterRicardo KraftmanNo ratings yet

- SPS Ka1m0880: To-3p-5lDocument8 pagesSPS Ka1m0880: To-3p-5lAndrzej WojtalaNo ratings yet

- Electronic Compass IC - HM55B (Datasheet)Document7 pagesElectronic Compass IC - HM55B (Datasheet)Anirudha Mhase100% (1)

- Diseño output ripple en DCDCDocument10 pagesDiseño output ripple en DCDCherraezjorge8No ratings yet

- Power Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Document11 pagesPower Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Karim CocasNo ratings yet

- 1ch Boost Up Type White LED Driver For Large LCD: DatasheetDocument37 pages1ch Boost Up Type White LED Driver For Large LCD: DatasheetWeex HRNo ratings yet

- 2017 Lab 3 Datasheet Dotmatrix TOP-CA-1088BSDocument7 pages2017 Lab 3 Datasheet Dotmatrix TOP-CA-1088BSPatrick SibandaNo ratings yet

- FP6137Document7 pagesFP6137Langkung SaeNo ratings yet

- Tda7265 (30W+30W)Document18 pagesTda7265 (30W+30W)ShiguMiku TheyNo ratings yet

- TL494Document7 pagesTL494Share KhNo ratings yet

- Painel MareaDocument2 pagesPainel MareamarcosNo ratings yet

- EVAPDocument2 pagesEVAPmarcosNo ratings yet

- Alternator Regulator With LIN: Data Sheet: Advance InformationDocument31 pagesAlternator Regulator With LIN: Data Sheet: Advance InformationmarcosNo ratings yet

- Alternator Regulator With LIN: Data Sheet: Advance InformationDocument31 pagesAlternator Regulator With LIN: Data Sheet: Advance InformationmarcosNo ratings yet

- 49FB Sem BCDocument1 page49FB Sem BCmarcosNo ratings yet

- L 9466Document11 pagesL 9466marcosNo ratings yet

- Legislaçao LedDocument2 pagesLegislaçao LedmarcosNo ratings yet

- Colet orDocument3 pagesColet ormarcosNo ratings yet

- ListaDocument2 pagesListamarcosNo ratings yet

- Lista DellphDocument3 pagesLista DellphmarcosNo ratings yet

- Install StepDocument1 pageInstall StepmarcosNo ratings yet

- Circuito Integrado Q0465RSDocument24 pagesCircuito Integrado Q0465RSmarcosNo ratings yet

- Manual Pic18f4550 MicrochipDocument438 pagesManual Pic18f4550 MicrochipcacasecacacasecaNo ratings yet

- Catalogue Engine Management 2018Document20 pagesCatalogue Engine Management 2018beto.epNo ratings yet

- Data Sheet: High Speed CAN TransceiverDocument18 pagesData Sheet: High Speed CAN TransceiverMohamed WahiebNo ratings yet

- Gigabyte Ga-8ig1000mk - Rev 1.01 PDFDocument36 pagesGigabyte Ga-8ig1000mk - Rev 1.01 PDFmarcosNo ratings yet

- TRIO 50.0 TL OUTD US 480 - Rev.G PDFDocument4 pagesTRIO 50.0 TL OUTD US 480 - Rev.G PDFmarcosNo ratings yet

- L 9466Document11 pagesL 9466marcosNo ratings yet

- LM555 Timer (RevDocument25 pagesLM555 Timer (RevJuan Diego ValdezNo ratings yet

- D 882Document1 pageD 882GlennNo ratings yet

- 2 Relay Products Automotive Catalog PDFDocument158 pages2 Relay Products Automotive Catalog PDFmarcosNo ratings yet

- D 882Document1 pageD 882GlennNo ratings yet

- LM555 Timer (RevDocument25 pagesLM555 Timer (RevJuan Diego ValdezNo ratings yet

- LM 7805 RegulatorDocument12 pagesLM 7805 RegulatorFadel BairuniNo ratings yet

- LM555 Timer (RevDocument25 pagesLM555 Timer (RevJuan Diego ValdezNo ratings yet

- LM 7805 RegulatorDocument12 pagesLM 7805 RegulatorFadel BairuniNo ratings yet

- Stick Diagram and Layout DiagramDocument56 pagesStick Diagram and Layout DiagramRavi BellubbiNo ratings yet

- Invention of Memory RacetrackDocument6 pagesInvention of Memory Racetrackvishals_31No ratings yet

- Lift Sensors Telemecanique-SensorsolutionsforescalatorandelevatorapplicationsDocument8 pagesLift Sensors Telemecanique-SensorsolutionsforescalatorandelevatorapplicationsBling Bling BombNo ratings yet

- SewDocument68 pagesSewmiroperNo ratings yet

- Pulse Position Modulation and DemodulationDocument3 pagesPulse Position Modulation and Demodulationpravsvizag100% (1)

- Audio Amplifier Circuit DiagramDocument1 pageAudio Amplifier Circuit DiagramRicky BaquirNo ratings yet

- Cisco Sns DsDocument5 pagesCisco Sns DsRahul MadanNo ratings yet

- Cisco Model EPC3925 8x4 EuroDOCSIS 3.0Document3 pagesCisco Model EPC3925 8x4 EuroDOCSIS 3.0irfaneng76No ratings yet

- Safety BarreiraDocument32 pagesSafety Barreiratv boxNo ratings yet

- Connect lithium systems Multi QuattroDocument5 pagesConnect lithium systems Multi QuattroandresNo ratings yet

- G2YM400VL20Document4 pagesG2YM400VL20luis gonzalezNo ratings yet

- BU Sem 2 Exam Timetable V3Document19 pagesBU Sem 2 Exam Timetable V3Tan Zhea Ron0% (2)

- SG PB Ixmm5860Document86 pagesSG PB Ixmm5860Enrico CioliniNo ratings yet

- DISP TRUST 18 SEPTIEMBRE 2023 ClientesDocument100 pagesDISP TRUST 18 SEPTIEMBRE 2023 ClientesAlex David Dueñas QuinteroNo ratings yet

- 1. Advance Microwave TrainingDocument51 pages1. Advance Microwave TrainingDAVID SAMUEL FRIDAYNo ratings yet

- Eslam CVDocument7 pagesEslam CVBouziane BeldjilaliNo ratings yet

- HP ELITEBOOK 8740W Inventec Armani 6050A2266501Document61 pagesHP ELITEBOOK 8740W Inventec Armani 6050A2266501Gerardo Mediabilla0% (2)

- MH-MK2 Series Motherboard Replacement Guide: Tools NeededDocument5 pagesMH-MK2 Series Motherboard Replacement Guide: Tools Neededlaudith22No ratings yet

- Lecture 2.3: FET IntroductionDocument3 pagesLecture 2.3: FET IntroductionAids Sumalde0% (1)

- Passive Tuned Harmonic FiltersDocument4 pagesPassive Tuned Harmonic FiltersRajendra Prasad Shukla100% (1)

- Netmanias.2015.12.31.5G Network Architecture - enDocument1 pageNetmanias.2015.12.31.5G Network Architecture - enFiras Ibrahim Al-HamdanyNo ratings yet

- Classé CD DVD 1 CD DVD Player SMDocument44 pagesClassé CD DVD 1 CD DVD Player SMRogelioMartinezNo ratings yet

- Tutorial - Cdma2000 Technology Family - 1xRTT, EVDO, UMB, and EVDV - EogogicsDocument24 pagesTutorial - Cdma2000 Technology Family - 1xRTT, EVDO, UMB, and EVDV - EogogicsAmmar IkramNo ratings yet

- Data SheetDocument10 pagesData SheetFakhar AliNo ratings yet

- Accurately measure long distances with the NTS-660LCl660RC total stationDocument2 pagesAccurately measure long distances with the NTS-660LCl660RC total stationabdulNo ratings yet

- Full HD Digital T2 Terrestrial / Cable Receiver With Conax Embedded Card ReaderDocument2 pagesFull HD Digital T2 Terrestrial / Cable Receiver With Conax Embedded Card ReaderDan CooperNo ratings yet

- DTFT Review1Document10 pagesDTFT Review1Abhishek Joshi100% (1)

- Radkit Pp001c en PDocument6 pagesRadkit Pp001c en PneoflashNo ratings yet

- Opal ManualDocument26 pagesOpal ManualstonedreaderNo ratings yet