Professional Documents

Culture Documents

WWW - Manaresults.Co - In: Low Power Vlsi Design

Uploaded by

Sreekanth PagadapalliOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

WWW - Manaresults.Co - In: Low Power Vlsi Design

Uploaded by

Sreekanth PagadapalliCopyright:

Available Formats

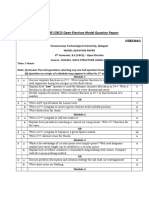

Code No: H6809/R13

M. Tech. II Semester Regular/ Supplementary Examinations, July-2016

LOW POWER VLSI DESIGN

(Common to VLSI & ES, ES & VLSI, VLSID & ES, ES & VLSID, VLSI, VLSID, VLSISD and VLSI & ME)

Time: 3 Hours Max. Marks: 60

Answer any FIVE Questions

All Questions Carry Equal Marks

1. a Explain about switching power dissipation and short circuit power dissipation. 8

b Briefly explain about velocity saturation. 4

2. a With a neat sketch, explain a variable threshold CMOS inverter circuit. 6

b Compare pipelining and parallel processing approaches. 6

3. a Write down the differences between carry select adders and carry save adders. 4

b Discuss any two types of low voltage low power logic styles. 8

4. a Draw the logic circuit of the conventional CMOS full adder and explain about it. 4

b Explain the basic theory, operation and performance evaluation of carry look-ahead adders. 8

5. a Draw the basic building blocks of the Baugh-Wooley multiplier architecture and explain its 8

operation.

b Write down the algorithm of Baugh-Wooley multiplier. 4

6. a Discuss the types of multiplier architectures. 4

b Explain about Booth multiplier. 8

7. a Compare SRAM and DRAM. 4

b Give a note on future trend and development of ROM. 4

c Write down differences between 6T and 4T static RAM cells. 4

8. a With a neat diagram, explain the block diagram of DRAM architecture. 6

b Discuss low power SRAM technologies with neat diagrams. 6

*****

WWW.MANARESULTS.CO.IN

|''|'''||''||'''||||

You might also like

- JNTUK-M Tech-2018-1st Semester-Feb-R17 R16 R15 R13-G6803022018 CMOS ANALOG IC PDFDocument1 pageJNTUK-M Tech-2018-1st Semester-Feb-R17 R16 R15 R13-G6803022018 CMOS ANALOG IC PDFRanjith DevulapalliNo ratings yet

- JNTUK2015Document1 pageJNTUK2015Sreekanth PagadapalliNo ratings yet

- WWW - Manaresults.Co - In: Design For TestabilityDocument2 pagesWWW - Manaresults.Co - In: Design For TestabilitykishorechiyaNo ratings yet

- EC19641-VLSI Design Part B Question BankDocument2 pagesEC19641-VLSI Design Part B Question BankmyavananNo ratings yet

- VLSI DesignDocument5 pagesVLSI DesignqwertyuiopNo ratings yet

- Intelligent Manufacturing SystemsDocument5 pagesIntelligent Manufacturing SystemsVenkata RamuduNo ratings yet

- Elective - III: Parallel Computing: B.E. Eighth Semester (Computer Technology) (C.B.S.)Document2 pagesElective - III: Parallel Computing: B.E. Eighth Semester (Computer Technology) (C.B.S.)Ayush PetkarNo ratings yet

- VLSI AssignDocument5 pagesVLSI AssignSrideviasokanNo ratings yet

- JNTUK - M Tech - 2017 - 2nd Semester-H6810052017 SEMICONDUCTOR MEMORY DESIGN AND TESTINGDocument1 pageJNTUK - M Tech - 2017 - 2nd Semester-H6810052017 SEMICONDUCTOR MEMORY DESIGN AND TESTINGNaresh KumarNo ratings yet

- Computer NetworksDocument2 pagesComputer NetworksAAI'S KITCHENNo ratings yet

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocument1 pageWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksNaresh KumarNo ratings yet

- M.Tech. Degree Examination Psa, MD & Cad/Cam: (Nov-17) (EEI-785)Document2 pagesM.Tech. Degree Examination Psa, MD & Cad/Cam: (Nov-17) (EEI-785)Karthik SenapatiNo ratings yet

- Elective - III: Parallel Computing: B.E. (Computer Technology) Eighth Semester (C.B.S.)Document2 pagesElective - III: Parallel Computing: B.E. (Computer Technology) Eighth Semester (C.B.S.)Ayush PetkarNo ratings yet

- M. Tech (VLSI Design) II Semester End Term Examination, May 2020 MVL 202: Analog IC DesignDocument3 pagesM. Tech (VLSI Design) II Semester End Term Examination, May 2020 MVL 202: Analog IC DesignNeeraj SharmaNo ratings yet

- 15 Ec 661Document6 pages15 Ec 661Prajwal ShettykpNo ratings yet

- 18CS44@AzDOCUMENTS inDocument6 pages18CS44@AzDOCUMENTS inAzeem TopNo ratings yet

- H6804102015 PDFDocument2 pagesH6804102015 PDFkishorechiyaNo ratings yet

- Mar - 2010 - A7707-Low Power Vlsi DesignDocument1 pageMar - 2010 - A7707-Low Power Vlsi DesignvasuvlsiNo ratings yet

- H6802102015 PDFDocument1 pageH6802102015 PDFS G ShivaPrasad YadavNo ratings yet

- Basic Electronics & Communication EngineeringDocument2 pagesBasic Electronics & Communication EngineeringMr girishNo ratings yet

- Vlsi QBDocument2 pagesVlsi QBSam Joel.DNo ratings yet

- 8108 CMOS Analog IC DesignDocument2 pages8108 CMOS Analog IC Designvenu sNo ratings yet

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocument1 pageWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksNeil SamNo ratings yet

- Assignment-2 Vlsi 29.04.2023Document1 pageAssignment-2 Vlsi 29.04.2023040-NishanthNo ratings yet

- 19ec4202 Digital Ic DesignDocument5 pages19ec4202 Digital Ic Designsrihari_56657801No ratings yet

- 18cs442 MC-2Document2 pages18cs442 MC-2M.A rajaNo ratings yet

- Previous PapersDocument12 pagesPrevious PapersKaran SanaNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- MP (4th) Dec11Document3 pagesMP (4th) Dec11moreajinkya35No ratings yet

- VLSID R20 Q BankDocument4 pagesVLSID R20 Q BankSATYA SRI LIKHITHA DUSANAPUDINo ratings yet

- Question Bank Unit 5and6Document2 pagesQuestion Bank Unit 5and6Abdallah Tali BanNo ratings yet

- Electrical Distribution SystemDocument2 pagesElectrical Distribution Systemanon_991240328No ratings yet

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocument1 pageWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksTelugu SatyanarayanaNo ratings yet

- M.Tech I Semester Supplementary Examinations February/March 2018Document1 pageM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNo ratings yet

- Elective - III: Parallel Computing: B.E. Eighth Semester (Computer Technology) (C.B.S.)Document2 pagesElective - III: Parallel Computing: B.E. Eighth Semester (Computer Technology) (C.B.S.)Ayush PetkarNo ratings yet

- WWW - Manaresults.Co - In: Electrical Distribution SystemsDocument1 pageWWW - Manaresults.Co - In: Electrical Distribution Systemsmocharla sandeepNo ratings yet

- C G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- B.Tech. DEGREE Examination Electronics & Communication EngineeringDocument2 pagesB.Tech. DEGREE Examination Electronics & Communication EngineeringNaresh KumarNo ratings yet

- Vlsi Important QuestionsDocument2 pagesVlsi Important QuestionsJoshua KumaresanNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- M.Tech. Degree Examination RF & Microwave Engineering: (Nov-17) (EEC-717)Document2 pagesM.Tech. Degree Examination RF & Microwave Engineering: (Nov-17) (EEC-717)MurthyNo ratings yet

- Unit - IDocument3 pagesUnit - IRakesh RakiNo ratings yet

- B.Tech. Degree Examination Ece &eie: (EUREC-304A/EUREI-304A)Document2 pagesB.Tech. Degree Examination Ece &eie: (EUREC-304A/EUREI-304A)kohli kingNo ratings yet

- Elective-III: Parallel Computing: B.E. (Computer Technology) Eighth Semester (C.B.S.)Document2 pagesElective-III: Parallel Computing: B.E. (Computer Technology) Eighth Semester (C.B.S.)Ayush PetkarNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- A6508 - Low Power Vlsi DesignDocument2 pagesA6508 - Low Power Vlsi Designramanaidu1No ratings yet

- Power System Modelling: M. Tech. (Integrated Power System / Power Electronics & Power System) First Semester (C.B.C.S.)Document2 pagesPower System Modelling: M. Tech. (Integrated Power System / Power Electronics & Power System) First Semester (C.B.C.S.)Mahesh ShendeNo ratings yet

- Me 8 Sem Advanced Manufacturing Techniques Winter 2018Document2 pagesMe 8 Sem Advanced Manufacturing Techniques Winter 2018AakashNo ratings yet

- Computer Networks: B.E.Sixth Semester (Computer Technology) (C.B.S.)Document13 pagesComputer Networks: B.E.Sixth Semester (Computer Technology) (C.B.S.)154Soyal LonareNo ratings yet

- Advanced Power ElectronicsDocument2 pagesAdvanced Power ElectronicsMahesh ShendeNo ratings yet

- M.E. (E & TC) (VLSI and Embedded Systems) Analog Cmos Design (2013 Pattern) (Semester-II) (504207)Document2 pagesM.E. (E & TC) (VLSI and Embedded Systems) Analog Cmos Design (2013 Pattern) (Semester-II) (504207)mssonuneNo ratings yet

- Simulation Modeling of Manufacturing SystemsDocument8 pagesSimulation Modeling of Manufacturing SystemsSrimanthula SrikanthNo ratings yet

- Eprvd-102 Eprds-102a - 01.12 PDFDocument2 pagesEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNo ratings yet

- CMOS Q BankDocument3 pagesCMOS Q BankRathore Yuvraj SinghNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Computer Architecture & Organization: B.E. (Computer Science & Engineering) (New) Third Semester (C.B.S.)Document2 pagesComputer Architecture & Organization: B.E. (Computer Science & Engineering) (New) Third Semester (C.B.S.)Chinmay MokhareNo ratings yet

- DCSFinal II April21 AssignmenrtDocument45 pagesDCSFinal II April21 AssignmenrtChirantan BiswasNo ratings yet

- Electronic Design Automation: Synthesis, Verification, and TestFrom EverandElectronic Design Automation: Synthesis, Verification, and TestNo ratings yet

- Effective Communication Protocols For Verification On Soc Using FpgaDocument6 pagesEffective Communication Protocols For Verification On Soc Using FpgaSreekanth PagadapalliNo ratings yet

- DD Flow TutorialDocument75 pagesDD Flow TutorialSreekanth PagadapalliNo ratings yet

- Dynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicDocument27 pagesDynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicSreekanth PagadapalliNo ratings yet

- ECE 1749H: Interconnection Networks For Parallel Computer Architectures: Router MicroarchitectureDocument58 pagesECE 1749H: Interconnection Networks For Parallel Computer Architectures: Router MicroarchitectureSreekanth PagadapalliNo ratings yet

- 06-Verilog Behavioral ModelingDocument27 pages06-Verilog Behavioral ModelingSreekanth PagadapalliNo ratings yet

- ECE 451 Verilog Exercises Sept 14, 2007 James Barnes (James - Barnes@colostate - Edu)Document14 pagesECE 451 Verilog Exercises Sept 14, 2007 James Barnes (James - Barnes@colostate - Edu)Sreekanth PagadapalliNo ratings yet

- An Overview of On-Chip BusesDocument25 pagesAn Overview of On-Chip BusesSreekanth PagadapalliNo ratings yet

- .. Uploads Syllabus First Year NewDocument8 pages.. Uploads Syllabus First Year NewSreekanth PagadapalliNo ratings yet

- River Float Waste Cleaning AutomationDocument6 pagesRiver Float Waste Cleaning AutomationSreekanth PagadapalliNo ratings yet

- Compiler DirectivesDocument4 pagesCompiler DirectivesSreekanth PagadapalliNo ratings yet

- The Embedded Design Life CycleDocument13 pagesThe Embedded Design Life CycleSreekanth PagadapalliNo ratings yet

- Verilog HDL Training GuideDocument67 pagesVerilog HDL Training GuideSreekanth PagadapalliNo ratings yet

- Driver Alert SystemDocument6 pagesDriver Alert SystemSreekanth PagadapalliNo ratings yet

- Es Unit - VDocument11 pagesEs Unit - VSreekanth PagadapalliNo ratings yet

- An Iot Application For Inventory Management With A Self-Adaptive Decision ModelDocument6 pagesAn Iot Application For Inventory Management With A Self-Adaptive Decision ModelSreekanth PagadapalliNo ratings yet

- Embedded Systems Unit IVDocument11 pagesEmbedded Systems Unit IVSreekanth PagadapalliNo ratings yet

- Embedded Systems Unit ViDocument18 pagesEmbedded Systems Unit ViSreekanth PagadapalliNo ratings yet

- Design and Implementation of Iot Based Integrated Model For Warehouse Inventory Management and Environment MonitoringDocument10 pagesDesign and Implementation of Iot Based Integrated Model For Warehouse Inventory Management and Environment MonitoringSreekanth PagadapalliNo ratings yet

- 8279Document88 pages8279Sreekanth PagadapalliNo ratings yet

- Adhoc Wireless and Sensor Networks: M. Tech II Semester Supplementary Examinations, February - 2014Document26 pagesAdhoc Wireless and Sensor Networks: M. Tech II Semester Supplementary Examinations, February - 2014Sreekanth PagadapalliNo ratings yet

- Python - GUI Programming (Tkinter)Document38 pagesPython - GUI Programming (Tkinter)Sreekanth PagadapalliNo ratings yet