Professional Documents

Culture Documents

JNTUK2015

Uploaded by

Sreekanth Pagadapalli0 ratings0% found this document useful (0 votes)

17 views1 pageThis document outlines exam questions for a Low Power VLSI Design course. The exam will have 8 questions covering topics like sources of leakage power, voltage scaling, CMOS logic design, binary array multipliers, ROM operation, SRAM vs DRAM, carry look ahead adders, and MOS transistor memory cells. Students must answer any 5 of the 8 questions in their exam. Each question is allotted equal marks.

Original Description:

Low power vlsi design

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document outlines exam questions for a Low Power VLSI Design course. The exam will have 8 questions covering topics like sources of leakage power, voltage scaling, CMOS logic design, binary array multipliers, ROM operation, SRAM vs DRAM, carry look ahead adders, and MOS transistor memory cells. Students must answer any 5 of the 8 questions in their exam. Each question is allotted equal marks.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

17 views1 pageJNTUK2015

Uploaded by

Sreekanth PagadapalliThis document outlines exam questions for a Low Power VLSI Design course. The exam will have 8 questions covering topics like sources of leakage power, voltage scaling, CMOS logic design, binary array multipliers, ROM operation, SRAM vs DRAM, carry look ahead adders, and MOS transistor memory cells. Students must answer any 5 of the 8 questions in their exam. Each question is allotted equal marks.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

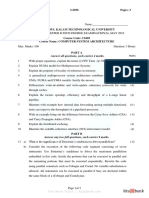

Subject Code: H6809/R13

M. Tech –II Semester Regular/ Supply Examinations, October, 2015

LOW POWER VLSI DESIGN

(Common to VLSI&ES, ES&VLSI, VLSID&ES, ES& VLSID, VLSI, VLSID,

VLSISD and VLSI&ME)

Time: 3 Hours Max Marks: 60

Answer any FIVE questions

All questions carry EQUAL marks

****

1. (a) Write about sources of leakage power with neat diagram.

(b) Write about Drain Induced Barrier Lowering of NMOS transistor.

2. (a) Write the advantages of Voltage scaling.

(b) Write about pipe lining and parallel processing

3. (a) Realize CMOS logic for 1 bit full adder.

(b) Write the drawbacks of ripple carry adder.

4. (a) What are the building blocks are needed for binary array multiplier and explain

(b) Construct Baugh-Wooley Multiplier and explain its operation

5. (a) Design a 8X3 ROM and explain its operation.

(b) Compare SRAM and DRAM memories.

6. (a) Design a carry-out circuit of 4 bit carry look ahead adder

(b) Write the advantages and disadvantages of MTCMOS circuits.

7. (a) Explain the necessity of two-dimensional decoding mechanism in memories.

(b) List out the sources of power dissipation in VLSI circuits and explain any two in

detail.

8. (a) Write the drawbacks of carry look ahead adder.

(b) Draw MOS transistor memory cell in ROM and explain the operation.

*****

WWW.MANARESULTS.CO.IN

|''|'''||''||'''||||

You might also like

- Intelligent Manufacturing SystemsDocument5 pagesIntelligent Manufacturing SystemsVenkata RamuduNo ratings yet

- H6802102015 PDFDocument1 pageH6802102015 PDFS G ShivaPrasad YadavNo ratings yet

- M.Tech I Semester Supplementary Examinations February/March 2018Document1 pageM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNo ratings yet

- WWW - Manaresults.Co - In: Low Power Vlsi DesignDocument1 pageWWW - Manaresults.Co - In: Low Power Vlsi DesignSreekanth PagadapalliNo ratings yet

- H6804102015 PDFDocument2 pagesH6804102015 PDFkishorechiyaNo ratings yet

- Previous PapersDocument12 pagesPrevious PapersKaran SanaNo ratings yet

- WWW - Manaresults.co - In: Set No. 1Document1 pageWWW - Manaresults.co - In: Set No. 1HaripriyaNo ratings yet

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- Advanced Computer ArchitectureDocument4 pagesAdvanced Computer ArchitectureSaikumarVavilaNo ratings yet

- A6508 - Low Power Vlsi DesignDocument2 pagesA6508 - Low Power Vlsi Designramanaidu1No ratings yet

- Simulation Modeling of Manufacturing SystemsDocument8 pagesSimulation Modeling of Manufacturing SystemsSrimanthula SrikanthNo ratings yet

- 54105-Mt-Vlsi Technology and DesignDocument2 pages54105-Mt-Vlsi Technology and DesignSrinivasa Rao GNo ratings yet

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocument1 pageWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksNaresh KumarNo ratings yet

- VLSI DesignDocument5 pagesVLSI DesignqwertyuiopNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- r05320402 Vlsi DesignDocument4 pagesr05320402 Vlsi DesignSRINIVASA RAO GANTANo ratings yet

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061No ratings yet

- VLSI DESIGN Question Bank: Unit 1Document12 pagesVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- VLSI Question BankDocument2 pagesVLSI Question BankVikash SharmaNo ratings yet

- VLSI DesignDocument1 pageVLSI DesignSurendar AviNo ratings yet

- Mar - 2010 - A7707-Low Power Vlsi DesignDocument1 pageMar - 2010 - A7707-Low Power Vlsi DesignvasuvlsiNo ratings yet

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyNo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- Time: 3 Hours Full Marks: 70Document3 pagesTime: 3 Hours Full Marks: 70pikluNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- VLSI Interview Questions - RoutingDocument36 pagesVLSI Interview Questions - Routing3nadhs100% (1)

- Vlsi Question PapersDocument1 pageVlsi Question PapersjahnaviNo ratings yet

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeeNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- VLSI AssignDocument5 pagesVLSI AssignSrideviasokanNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document2 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)venkiscribd444No ratings yet

- Set No: 1: Code No: V3219/R07Document4 pagesSet No: 1: Code No: V3219/R07Gopi Pavan JonnadulaNo ratings yet

- 18EI56Document6 pages18EI56Rocky BhaiNo ratings yet

- Ec 1354Document5 pagesEc 1354kvnelavarasiNo ratings yet

- C G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- VLSI Design 2010 Sept CUSATDocument1 pageVLSI Design 2010 Sept CUSATvineethvrr5948No ratings yet

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- rr321202 Vlsi Systems DesignDocument4 pagesrr321202 Vlsi Systems DesignSRINIVASA RAO GANTANo ratings yet

- CMOS Interview QuestionsDocument3 pagesCMOS Interview Questions3nadhsNo ratings yet

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423No ratings yet

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzNo ratings yet

- EC19641-VLSI Design Part B Question BankDocument2 pagesEC19641-VLSI Design Part B Question BankmyavananNo ratings yet

- Unit Wise Imp QuestionsDocument3 pagesUnit Wise Imp Questionsvk2you009100% (1)

- Nr-Vlsi Technology and DesignDocument2 pagesNr-Vlsi Technology and DesignSudhakar SpartanNo ratings yet

- Set No. 1: WWW - Manaresults.Co - inDocument1 pageSet No. 1: WWW - Manaresults.Co - inkishore kumarNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsContent for all CreatorNo ratings yet

- 9D06106c Low Power VLSI DesignDocument1 page9D06106c Low Power VLSI Designraju.kprr8862No ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- Btech Cse 4 Sem Advance Computer Architecture 2012Document7 pagesBtech Cse 4 Sem Advance Computer Architecture 2012souravnaskar12578954No ratings yet

- Mtech VLSI SyllabusDocument37 pagesMtech VLSI SyllabusRavindra vs100% (1)

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Jntu MDocument3 pagesJntu MVijay SagarNo ratings yet

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsRating: 4 out of 5 stars4/5 (3)

- DD Flow TutorialDocument75 pagesDD Flow TutorialSreekanth PagadapalliNo ratings yet

- Dynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicDocument27 pagesDynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicSreekanth PagadapalliNo ratings yet

- Effective Communication Protocols For Verification On Soc Using FpgaDocument6 pagesEffective Communication Protocols For Verification On Soc Using FpgaSreekanth PagadapalliNo ratings yet

- ECE 1749H: Interconnection Networks For Parallel Computer Architectures: Router MicroarchitectureDocument58 pagesECE 1749H: Interconnection Networks For Parallel Computer Architectures: Router MicroarchitectureSreekanth PagadapalliNo ratings yet

- 06-Verilog Behavioral ModelingDocument27 pages06-Verilog Behavioral ModelingSreekanth PagadapalliNo ratings yet

- ECE 451 Verilog Exercises Sept 14, 2007 James Barnes (James - Barnes@colostate - Edu)Document14 pagesECE 451 Verilog Exercises Sept 14, 2007 James Barnes (James - Barnes@colostate - Edu)Sreekanth PagadapalliNo ratings yet

- An Overview of On-Chip BusesDocument25 pagesAn Overview of On-Chip BusesSreekanth PagadapalliNo ratings yet

- .. Uploads Syllabus First Year NewDocument8 pages.. Uploads Syllabus First Year NewSreekanth PagadapalliNo ratings yet

- Compiler DirectivesDocument4 pagesCompiler DirectivesSreekanth PagadapalliNo ratings yet

- Verilog HDL Training GuideDocument67 pagesVerilog HDL Training GuideSreekanth PagadapalliNo ratings yet

- River Float Waste Cleaning AutomationDocument6 pagesRiver Float Waste Cleaning AutomationSreekanth PagadapalliNo ratings yet

- An Iot Application For Inventory Management With A Self-Adaptive Decision ModelDocument6 pagesAn Iot Application For Inventory Management With A Self-Adaptive Decision ModelSreekanth PagadapalliNo ratings yet

- Driver Alert SystemDocument6 pagesDriver Alert SystemSreekanth PagadapalliNo ratings yet

- Embedded Systems Unit IVDocument11 pagesEmbedded Systems Unit IVSreekanth PagadapalliNo ratings yet

- Embedded Systems Unit ViDocument18 pagesEmbedded Systems Unit ViSreekanth PagadapalliNo ratings yet

- Es Unit - VDocument11 pagesEs Unit - VSreekanth PagadapalliNo ratings yet

- 8279Document88 pages8279Sreekanth PagadapalliNo ratings yet

- Python - GUI Programming (Tkinter)Document38 pagesPython - GUI Programming (Tkinter)Sreekanth PagadapalliNo ratings yet

- Design and Implementation of Iot Based Integrated Model For Warehouse Inventory Management and Environment MonitoringDocument10 pagesDesign and Implementation of Iot Based Integrated Model For Warehouse Inventory Management and Environment MonitoringSreekanth PagadapalliNo ratings yet

- The Embedded Design Life CycleDocument13 pagesThe Embedded Design Life CycleSreekanth PagadapalliNo ratings yet

- Adhoc Wireless and Sensor Networks: M. Tech II Semester Supplementary Examinations, February - 2014Document26 pagesAdhoc Wireless and Sensor Networks: M. Tech II Semester Supplementary Examinations, February - 2014Sreekanth PagadapalliNo ratings yet