Professional Documents

Culture Documents

A Complete Analysis of New Generalized Asymmetric Multilevel Inverter Topology

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Complete Analysis of New Generalized Asymmetric Multilevel Inverter Topology

Copyright:

Available Formats

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

A Complete Analysis of New Generalized

Asymmetric Multilevel Inverter Topology

Aparna Prayag1, Sanjay Bodkhe2

1

Department of Electrical Engineering, G. H. Raisoni College of Engineering, CRPF Gate No.3, Hingna Road, Digdoh

Hills, Nagpur, Maharashtra, India

2

Department of Electrical Engineering, Shri Ramdeobaba College of Engineering & Management, Ramdeo Tekdi,

Gittikhadan, Katol Road, Nagpur India

ABSTRACT

This paper presents a new generalized topology of the asymmetric multilevel inverter. Each unit generates 9 levels with two dc

sources and eight power switches. There is no need of additional circuit to generate negative voltage levels. A generalized

topology can be developed by a series connection of n number of units which can generate higher voltages with low harmonics.

Multi-carrier sinusoidal pulse width modulation (MC-SPWM) scheme is used to attain quality output voltage. Simulation

results using MATLAB and experimental results are presented to verify the performance of proposed topology.

Keywords: Asymmetric, multilevel inverter (MLI), MC- SPWM power switches, total harmonic distortion (THD).

1. INTRODUCTION

Multilevel inverter (MLI) is an advanced and important technology in the field of electronic power conversion. It is an

arrangement of several dc sources/capacitors and power semiconductor devices to generate staircase output voltage

waveform having m- number of levels. Number of advantages such as high quality output voltage with low harmonic

content, low voltage stress on power switches, low switching losses and more efficiency, less electromagnetic

interference made this technology popular in many industrial applications such as variable speed drives,

electrical/hybrid vehicles, FACTS, HVDC, renewable energy systems etc. [1]-[3].

Three main topologies of MLI are diode clamped also known as neutral point clamped (NPC), capacitor clamped or

flying capacitor (FC) and cascaded H bridge (CHB) [4]. NPC and FC topologies require many semiconductor devices

to generate a higher number of levels also there is a problem of capacitor voltage unbalancing [5]. CHB is modular and

suitable topology to generate a large number of levels. But each H bridge requires a separate isolated dc source which is

a limitation in its expansion [6]-[8]. These topologies require a large number of switching devices and other

components to increase the number of levels and hence to improve the quality of the output waveform. This makes the

control circuit complicated, reduces reliability and increases the cost of the inverter. [9], [10].

Now researchers are engaged to develop new topologies to overcome limitations of classical topologies. These are

hybrid, cascaded and/or asymmetric topologies. Using a combination of classical topologies, applying different

modulation techniques or semiconductor technologies hybrid topologies are introduced while unequal dc sources are

used in asymmetric topologies. The main objective of novel topologies is to reduce component count and generate

higher levels of voltage. Some other optimization parameters are THD level, voltage stress on switching devices, power

loss, total blocking voltage etc.[7]-[12]. In [13] some recently proposed multilevel inverter topologies with reduced

power switch count are reviewed and analyzed. Recent advances in MLI topologies, modulation techniques, industrial

and renewable energy applications using MLIs are presented in [14]-[20].

In this paper, a new generalized MLI topology by cascading elementary units is proposed. Each elementary structure

can generate nine levels with two dc sources having magnitude ratio 3:1 and eight power switches. In that manner,

each elementary structure is also an MLI. Section 2 presents the proposed structure of MLI including operating

principle, switching states and mathematical formulation of the output voltage. Calculation of losses is presented in

section 3. A comparative study is shown in section 4. In section 5 switching scheme using MC-SPWM is explained and

simulation results are presented. In section 6 experimental results using a laboratory prototype of proposed topology are

shown and the conclusion is presented in section 7.

Volume 6, Issue 11, November 2018 Page 15

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

2. CIRCUIT TOPOLOGY

The structure of proposed multilevel inverter topology is presented in this section. Elementary unit of single phase nine

level inverter is used to describe operating principle. Detailed expressions for a number of switches, dc sources, output

voltage levels etc. are presented. Three phase structure is also presented.

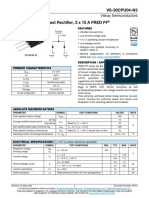

Fig. 1 shows an elementary unit of single phase asymmetric nine level inverter. It involves eight power switches (SU1,

SU2, SM1, SM2, SD1, SD2, SS1, SS2) and two dc sources (V1=3E and V2=E). When such n numbers of units are connected

in series a generalized structure is formed. Addition of output voltages of all connected units gives a total output voltage

of generalized topology.

(V )T (V ) (V ) ........ (V )n (1)

O O1 O 2 O

(V )T n (V )

O k 1 O n

The number of power switches and dc sources required in a generalized topology with n basic units connected in series

are given by following expressions

N sw 8 n (2)

N 2 n (3)

dc

The following expressions present number of levels generated by the topology.

N 8n 1 (4)

lv

The other expressions are

V pk 4E

V p 4 nE (5)

Here Vp k maximum voltage attained by k th basic unit and V p is total maximum voltage attained by generalized

topology.

Figure 2 shows two such units connected in series. According to equation (4), this structure can generate 17 levels

using different possible paths which can improve its reliability.

Table 1 shows all the parameters like number of levels generated, number of switches, the number of dc sources

required based on the number of elementary units and the desired number of levels.

Three phase circuit of nine level inverter is presented in Figure 3. Here line to line voltage levels are (2 m 1) 17 .

Figure 1 Elementary unit of single phase asymmetric nine level inverter.

Volume 6, Issue 11, November 2018 Page 16

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

Table 1: Parameters of generalized topology

Based on

Based on the

elementary

number of

units

levels

connected

Levels 8n 1 N

lv

Number of N 1

8n lv

switches

Number of Nlv 1

2n

dc sources 4

Total

voltage 11( Nlv 1) E

22nE

blocked by 4

switches

Figure 2 Generalized structure of single phase asymmetric inverter.

Volume 6, Issue 11, November 2018 Page 17

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

Figure 3 Three phase circuit of the proposed inverter

2.1 Operating Principle

The operation of proposed topology is explained using a single phase elementary unit of asymmetric nine level inverter.

The magnitudes of dc sources selected are V1= 3E and V2=E. This combination generates nine level output voltage with

a maximum and minimum level of +4E and -4E respectively by selecting proper paths through switches and dc

sources. It is possible to choose a different combination of dc source magnitudes to generate a different number of

output voltage levels.

All the switching stages of proposed topology are shown in Fig. 4 and Table 2. It is seen that load is supplied by nine

levels V1+V2, V1, V1-V2, V2, 0, -V2, -V1+V2, -V1 , -V1-V2 . From Table 2 it is seen that to attain all positive voltage levels

and one zero level, switch SU1 remains in on state while for all negative voltage levels and another zero level switch SU2

is conducting. Means these two switches are operating at a fundamental frequency to achieve nine levels. One cycle of

the output voltage and related pulse pattern of proposed topology are shown in Fig. 5. It is seen that switches. SU1, SU2,

SM2, SS2 are operating at the low frequency and other switches also at the reasonable switching frequency. This reduces

switching losses to a great amount.

Table 3 shows different paths to generate 17 levels when two units are connected in series as shown in Fig. 2. From this

table, it is seen that 1, 2, 3, …, 8 paths are possible to synthesize voltages 8E, 7E, 6E, ……, E respectively. It improves

the reliability of generalized structure as different paths are available in case of any failure of a switch or any part of the

circuit.

Table 2: Switching states and output voltage of proposed topology.

Switching Conditions

Output VL

SM1

SM2

SU1

SU2

SD1

SD2

SS1

SS2

No

Voltage

4E

1 1 0 0 1 0 1 0 0 V1 V2

3E

2 1 0 1 0 0 1 0 0 V1

2E

3 1 0 1 0 1 0 0 0 V1 V2

4 1 0 0 0 0 1 1 0 V2 E

5 1 0 0 0 1 0 1 0 0 0

6 0 1 0 1 1 0 0 0 0 0

7 0 1 1 0 1 0 0 0 V2 E

2 E

8 0 1 0 0 0 1 1 0 V1 V2

3E

9 0 1 0 0 1 0 1 0 V1

4 E

10 0 1 0 0 1 0 0 1 V1 V2

Volume 6, Issue 11, November 2018 Page 18

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

1.1 Mathematical Formulation of Output Voltage

The voltage across a load of the proposed inverter can be expressed using switching function of different switches used

as shown in Fig. 2. The switching function SFik is as follows:

SFik 1 when switch is on.

S Fik 0 when switch is off. (6)

Then load voltage can be expressed as

n

VL VOn (7)

k 1

Where

VOn SM 1n S M 2 n SU 2 n V1n SD 2 n S M 1n S S 2n V2n

The above mathematical expression for load terminal voltage of generalized topology is verified for nine level elementary

inverter with voltage source magnitudes V1= 3E and V2=E. In stage 2 operation as shown in Fig. 4 switches SM1 and SD2 are on,

therefore switching function of these switches is assumed

as 1 while switches SM2, SU2, and SS2 are off so their switching function becomes 0. Putting these switching functions in

equation (8), we will get

VO 1 0 - 0 3 E 1 -1 - 0 E 3 E

Thus the voltage appeared across the load terminal during stage 2 is 3E.

Table 3: Switching states and paths for two units connected in series

Output Voltage Total output Number

voltage of paths

[Unit 1- (VO )1 ,Unit 2- (VO ) 2 ]

No

(VO )T

1 4 E ,4 E 8E

1

2 4 E ,3 E / 3 E ,4 E 7E

2

3 4 E ,2 E / 3 E ,3 E / 2 E ,4 E 6E

3

4 4 E , E / 3E ,2 E / 2 E ,3E / E ,4 E 5E

4

5 4 E ,0 / 3 E , E / 2 E ,2 E / E ,3 E / 0,4 E 4E

5

6 4 E , E / 3 E ,0 / 2 E , E / E ,2 E / 0,3 E / E ,4 E 3E

6

7 4 E , 2 E / 3 E , E / 2 E ,0 / E , E / 0,2 E / E ,3 E / [ 2 E , 4 E ] 2E

7

8 4 E , 3 E / 3 E , 2 E / 2 E , E / E ,0 / 0, E / E ,2 E / [ 2 E , 3 E ], [ 3 E , 4 E ] E

8

4 E , 4 E / 3 E , 3 E / 2 E , 2 E / E , E / 0,0 / E , E / [ 2 E , 2 E ], [ 3 E , 3 E ], [ 4 E , 4 E ]

9

0 9

10 4 E ,3E / 3 E ,2 E / 2 E , E / E ,0 / 0, E / E , 2 E / [2 E , 3 E ], [3 E , 4 E ] E

8

11 4 E , 2 E / 3 E , E / 2 E ,0 / E , E / 0,2 E / E ,3 E / [ 2 E , 4 E ] 2E

7

12 4 E , E / 3 E ,0 / 2 E , E / E ,2 E / 0, 3 E / E , 4 E 3E

6

13 4 E ,0 / 3 E , E / 2 E , 2 E / E , 3 E / 0, 4 E 4E

5

14 4 E , E / 3 E , 2 E / 2 E , 3 E / E , 4 E 5E

4

15 4 E ,2 E / 3 E ,3 E / 2 E , 4 E 6E

3

16 4 E ,3 E / 3 E ,4 E 7E

2

17 4 E , 4 E 8E

1

Volume 6, Issue 11, November 2018 Page 19

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

Stage 1 Stage 2 Stage 3

Stage 4 Stage 5 Stage 6

Stage 7 Stage 8 Stage 9

Volume 6, Issue 11, November 2018 Page 20

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

Stage 10

Figure 4 Possible switching states

Figure 5 Output voltage and switching pulses of proposed topology for one cycle.

3. CALCULATION OF LOSSES IN THE PROPOSED STRUCTURE OF MULTILEVEL INVERTER

TOPOLOGY

There are three types of losses associated with power semiconductor components. These are

1. Conduction losses ( P ) : These losses occur when devices are conducting (on state).

lc

2. Switching losses ( P ) : These losses occur when devices are changing their state (on state to off state or vice

ls

versa).

3. Blocking losses ( P ) : These losses are due to leakage current when devices are in off state. They are almost

lb

insignificant and can be neglected [10].

Here for proposed topology evaluation of power losses is carried out by considering conduction and switching losses

only.

3.1 Conduction Losses

The power losses during on state are due to equivalent resistance and on state voltage drop of the semiconductor

devices.

Considering a typical power transistor and diode the instantaneous conduction losses can be written as:

Volume 6, Issue 11, November 2018 Page 21

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

P , T (t ) VT RT i (t ) i (t )

lc

P , D(t ) VD RD i (t ) i (t )

lc

Here

P , T (t )

lc - Instantaneous conduction losses of transistor device

P , D (t )

lc - Instantaneous conduction losses of diode

VT

-On state voltage drop of transistor device

RT

- Equivalent on state resistance of transistor device

VD

-On state voltage drop of diode

RD

- Equivalent on state resistance of diode and

-Constant governed by transistor characteristics

Let the current flowing through conducting switches at any instant of time be

i (t ) Im sin t

Depending upon switching condition the current path is either through transistor device or through the diode. For

example from Fig. 4, it is seen that, during switching condition 2, current is passing through transistors of SU1 and SD2

and diode of SM1. Suppose, at any instant of time nT (t ) , nD (t ) - the number of conducting transistors and diodes

respectively,

Then average conduction losses can be expressed as

1

P {[nT (t )VT nT (t ) RT i (t )]i (t ) [nD (t )VT nD (t ) RD i (t )]i (t )}d (t )

lc 0

Switching Losses

A linear approximation of voltage and current during the switching transition is used to calculate switching losses of

an individual switch. Fig. 6 shows switch characteristics during turn on and turn off. Energy losses during turn on and

turn off period of the ith switch can be expressed as

ton

Eon,i v(t )i(t )dt

0

ton

VO,i I

{[VO,i t][ t]}dt

0

ton ton

1

VO,i Iton

6

Volume 6, Issue 11, November 2018 Page 22

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

toff

E v(t )i(t )dt

off ,i

0

toff

VO,i I

{[ t ][I t ]}dt

0

toff toff

1

VO,i Itoff

6

Here

th

Eon ,i turn on loss of i switch

E ,i turn off loss of ith switch

off

ton turn on time

toff turn off time

Vo,i blocking voltage of ith switch

I current through the switch (assumed same after turning on and before turning off the switch

V V

I

V,I

ton toff

time

Figure 6 Linear switch characteristics.

Now, suppose in one cycle switch operates fi times, means fi is its switching frequency, then switching losses can be

expressed as

N sw

1

( P ) VOi I ton to ff f i (14)

ls i 1 6

The total power losses can be expressed as

P P P (15)

lt lc ls

4. COMPARATIVE STUDY

Table 4 shows a comparison of the proposed topology in case of nine level inverter toward popular ones and Table V

shows comparison based on the desired number of voltage levels. These topologies are NPC, FC, classic CHB, and

trinary asymmetric CHB, packed U-cell (PUC) [3] and crossed switched (CS) [21] multilevel inverter.

From Table 4, it is observed that proposed topology and trinary asymmetric CHB requires a same number of

components. Total voltage blocked by switches in trinary asymmetric CHB is less than the proposed one, but loss

calculation will show the advantage of proposed topology. The following section compares conduction losses and

switching losses of 9 level trinary asymmetric CHB and proposed topology.

Conduction losses:

Volume 6, Issue 11, November 2018 Page 23

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

Following parameters are considered to calculate power losses [21]

VT 2.5V , VD 1.5V , RT 0.15, RD 0.1, 1, RL 150, V1 150V , V2 50V

For the basic unit of the proposed multilevel inverter as seen in Fig. 4, it is clear that there are 3 devices in the current

path in any instant of time. Depending on the output voltage and current some of these devices are the transistors and

the some are diodes. Consider instant of voltage level 3E, where 2 transistors and one diode is conducting, conduction

losses are calculated using nT ( t ) 2, n D (t ) 1 in equation (11), gives Plc= 5.84 watt.

Now consider trinary asymmetric CHB topology with the same parameters. It is observed that there are 4 devices in

the current path for any instant of time. Consider same instant of voltage level 3 E, where 3 transistors and one diode

is conducting, conduction losses are calculated using nT (t ) 3 and n D (t ) 1 in equation (11), gives Plc = 8.10watt.

Switching losses:

Assume, switches operate with the same ton and toff time and carry same current I. Then switching losses expressed in

equation (14) can be written as

N sw

( P ) VOi f i (16)

ls i 1

1

where I (ton to ff )

6

In proposed basic 9-level inverter four switches operate at a fundamental frequency f f , out of them two switches block

voltage V1= 3E and two switches block voltage V1+ V2= 4E. Other four switches operate at a moderate frequency f m ,

two of them block voltage V1= 3E and other two V2= E. Hence switching losses of proposed basic 9 level inverter with

eight switches can be expressed as

( P ) [2(3E ) f f 2(4E ) f f 2(3E ) f m 2( E ) f m ]

ls

[(14 E ) f f (8E ) f m ] (17)

2 E[4 f m 7 f f ]

f f is very small as compared to f m , so switching losses can be approximated as

( P ) 2 E[4 f m ]

ls (18)

8 Ef m

In case of trinary asymmetric CHB topology all the eight switches operate at the high switching frequency, for simple

calculation consider this frequency is fm , four of them block voltage 3E and other four block voltage E. Therefore

switching losses, in this case, can be approximated as

( P ) [4(3 E ) f m 4( E ) f m ]

ls (19)

16 Ef m

From (18) and (19) it is clear that under same operating conditions switching losses taking place in proposed topology

are almost half of switching losses taking place in trinary asymmetric CHB topology.

5. MODULATION SCHEME

The main aim of the modulation method used to control inverter is to obtain the best waveform (voltage/current) with

minimum losses. Among the commonly used modulation techniques, Pulse Width Modulation (PWM) is simple and

Volume 6, Issue 11, November 2018 Page 24

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

gives high performance and therefore the most successful technique. A multicarrier level shifted PWM scheme is used

in this paper to generate pulses for the switches of the proposed inverter. The traditional sinusoidal PWM technique can

be applied to multilevel inverter topologies by using multiple carriers. Therefore it is known as multi-carrier PWM

technique. For m level inverter ( m 1) carriers are required [22].

Here for 9-level inverter, a sinusoidal reference waveform of the fundamental frequency(50 Hz) is compared with eight

high frequency (1 kHz) carrier waveforms configured in alternate phase opposition disposition mode to generate

switching signal as shown in Fig. 7. From this switching signal gate pulses for the switches of the proposed inverter

are obtained and it is shown in Fig. 8.

A single phase nine level inverter is simulated using MATLAB/Simulink to examine the performance of proposed

topology and control technique. The magnitude of dc sources selected are V1= 45 V and V2=15V. The pulse pattern

shown in Fig. 8, indicates that switches SU1 and SU2 operate at a fundamental frequency, switches SM2 and SS2

operates at a low frequency approximately equal to a fundamental frequency other four switches which have a moderate

frequency. Means total losses among the switches get distributed.

Fig. 9 shows nine level output voltage waveform with equal steps of 15V each and harmonic spectrum having THD of

15.44%. The simulation model is also built for a generalized topology with two units in series as shown in Fig. 2.

Seventeen level output voltage waveform and its harmonic spectrum for two cascaded units shown in Fig. 10. Here

THD is reduced to 6.93%.

Table 4: Table of comparison for nine level classic topologies with proposed Topology

Trinary

Classic Cross

NPC FC Asymmetri Proposed

CHB Switched

c CHB

DC link

capacitors/ 8 8 8 2 4 2

Isolated supplies

Number of

16 16 16 8 10 8

switches

Number of

56 0 0 0 0 0

clamping diodes

Number of flying

0 28 0 0 0 0

capacitors

Total component

80 52 24 10 14 10

count

Total voltage

blocked by 16E 16E 16E 16E 16E 22E

switches

Table 5: Table of comparison for N lv Level inverters ( Nlv -desired number of levels in phase voltage)

Trinary

Classic Cross

NPC FC Asymmetri PUC Proposed

CHB Switched

c CHB

DC link log( N lv 1)

1

( Nlv 1) log( Nlv ) ( Nlv 1) ( Nlv 1)

capacitors/ ( N lv 1) ( N lv 1) log(2)

2 log(3) 2 4

Isolated supplies

log( N lv 1)

Number of 2(N lv 1) log( Nlv ) 2

2( N lv 1) 2( N lv 1) 4

log(3)

log(2) ( N lv 1) ( N lv 1)

switches

Number of ( N lv 1)( N lv 2)

0 0 0 0 0 0

clamping diodes

( Nlv 1)( Nlv 2)

Number of

0 2 0 0 0 0 0

flying capacitors

Total voltage 2( N 1) E 2( N lv 1) E 2( N lv 1) E

lv 11( Nlv 1) E

blocked by 2( N lv 1) E 2( N lv 1) E 2( N lv 1) E

4

switches

Volume 6, Issue 11, November 2018 Page 25

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

4

Reference wave

CW4+ 3

CW3+ 2

CW2+

1

Ref. CW1+ 0

CW4+ CW1-

-1

CW2-

-2

CW3+ CW3-

Switching table

-3

Comparator

CW4-

CW2+ -4

0.02 0.022 0.024 0.026 0.028 0.03 0.032 0.034 0.036 0.038 0.04

4 Time(s)

CW1+ signal s(t) Gate 3

for output voltage level pulses 2

CW1- 1

signal s(t)

0

CW2-

-1

CW3- -2

-3

CW4- -4

0.02 0.022 0.024 0.026 0.028 0.03 0.032 0.034 0.036 0.038 0.04

Time(s)

(a) (b)

Figure 7 (a) Modulation scheme (b) Carrier and reference waveform alignment and corresponding switching signals

for nine level output.

SU1

SU2

SM1

SM2

SD1

SD2

SS1

SS2

Time(s)

Figure 8 Pulse pattern for switches of nine level inverter

60

40

20

Output voltage(v)

-20

-40

-60

0 0.005 0.01 0.015 0.02 0.025 0.03 0.035 0.04

Time(s)

Fundamental (50Hz) = 56.94 , THD= 15.44%

50

Mag (% of Fundamental)

40

30

20

10

0

0 2 4 6 8 10 12 14 16 18 20

Harmonic order

Figure 9 Simulation result of the output voltage and its harmonic spectrum for nine level inverter.

Volume 6, Issue 11, November 2018 Page 26

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

150

100

50

output voltage(v)

0

-50

-100

-150

0 0.005 0.01 0.015 0.02 0.025 0.03 0.035 0.04

Time(s)

Fundamental (50Hz) = 119.5 , THD= 6.93%

50

Mag (% of Fundamental)

40

30

20

10

0

0 2 4 6 8 10 12 14 16 18 20

Harmonic order

Figure 10 Simulation result of output voltage and its harmonic spectrum for seventeen level inverter.

6. EXPERIMENTAL RESULTS

A prototype of single phase nine level inverter is developed to validate the proposed topology. The schematic

diagram and hardware setup are shown in Fig. 11 and Fig. 12 respectively. The magnitudes of dc sources are V1= 45

V and V2=15V. MOSFETs IRF840 are used as power switches. The microcontroller PIC-16F877A generates gate

pulses for the switches. To amplify theses pulses and to provide isolation between the control and power stage TLP250

optoisolated gate driver is used. Amplified pulses from the driver are applied between gate and source of MOSFET.

Output voltage waveform is shown in Fig. 13(a) and its harmonic spectrum is shown in Fig. 13 (b).

TLP250 Ninelevel

PIC-16F877A inverter

Control unit Isolationand

amplificationunit Power unit

Figure 11 Schematic diagram of hardware setup

Figure 12 Photograph of hardware setup

Volume 6, Issue 11, November 2018 Page 27

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

(a) (b)

Figure 13 Experimental results (a) Output voltage of nine level inverter. (b) Harmonic spectrum of the output

voltage.

7. CONCLUSION

A new MLI topology, which can generate 9 levels, is presented in this paper. It is able to generate all levels (4

positive, 4 negative and zero) without any additional circuit. This topology uses a relatively small number of dc sources,

semiconductor devices, conducting switches as compared to other topologies. As it is modular topology cascading of

units is possible to generate high output voltage using different possible paths. It improves the reliability of generalized

inverter.

Comparison of proposed topology on the basis of losses with trinary asymmetric CHB is carried out.

The topology was investigated by simulation using MATLAB/Simulink and validated by experimental results on a

prototype in the laboratory.

References

[1] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. Franquelo, B. Wu, J. Rodriguez, M. Perez, and J. Leon,

“Recent advances and industrial applications of multilevel converters,” IEEE Trans. Ind. Electron., vol. 57, no. 8,

pp. 2553–2580, Aug. 2010.

[2] H. Abu-Rub, J. Holtz, and J. Rodriguez, “Medium-voltage multilevel converters–State of the art, challenges, and

requirements in industrial applications,” IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2581–2596, Aug. 2010

[3] Y. Ounejjar, K. Al-Haddad, and L.-A. Grégoire, “Packed U cells multilevel converter topology: Theoretical study

and experimental validation,” IEEE Trans. Ind. Electron., vol. 58, no. 4, pp. 1294–1306, Apr. 2011.

[4] J.Rodriguez, Jih-Sheng Lai, Fang Cheng Peng “Multilevel inverters: A survey of topologies, control, and

applications,” IEEE Trans. Ind. Electronics, vol. 49, no. 4, pp. 724-738, Aug. 2002

[5] P. Roshankumar, P. P. Rajeevan, K. Mathew, K. Gopakumar, J. Leon, and L. G. Franquelo. “A five-level inverter

topology with single-DC supply by cascading a flying capacitor inverter and an H-bridge,” IEEE Trans. Power

Electron., vol. 27, no. 8, pp. 3505–3512, Aug. 2012

[6] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, “A survey on cascaded multilevel inverters,”

IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

[7] Javad Ebrahimi, Ebrahim Babaei, and Gevorg B. Gharehpetian “ A new multilevel converter topology with

reduced number of power electronic components, ,” IEEE Trans. Ind. Electronics., vol. 59,No.2 pp. 655-667, Feb

2012.

[8] Ebrahim Babaei, Sara Laali, and Zahra Bayat, “ A Single-phase cascaded multilevel inverter based on a new basic

unit with reduced number of power switches, ,” IEEE Trans. Ind. Electronics, vol 62, No.2, pp.922-928, Feb

2015.

[9] Rasoul Shalchi Alishah et al “ New hybrid structure for multilevel inverter with fewer number of components for

high-voltage levels,” IET Power Electron. , vol. 7, ss. 1, pp. 96–104, 2014.

[10] Krishna Kumar Gupta, Shailendra Jain, “ A novel multilevel inverter based on switched dc sources, ” IEEE

Trans. Ind. Electronics, vol. 61, No.7, pp. 3269-3278, July.2014.

[11] Ataollah Mokhberdoran and Ali Ajami,“ Symmetric and asymmetric design and implementation of new cascaded

multilevel inverter topology,” IEEE Trans. Power Electronics, vol. 29,No.12 pp. 6712-6724,Dec.2014

Volume 6, Issue 11, November 2018 Page 28

IPASJ International Journal of Electrical Engineering (IIJEE)

Web Site: http://www.ipasj.org/IIJEE/IIJEE.htm

A Publisher for Research Motivation ........ Email:editoriijee@ipasj.org

Volume 6, Issue 11, November 2018 ISSN 2321-600X

[12] Ebrahim Babaei, Sara Laali, S.Alilu, “Cascaded multilevel inverter with series connection of novel H bridge basic

units, ” IEEE Transactions on Ind. Electron vol.61,No.12, pp. 6664-6671, Dec. 2014.

[13] Krishna Kumar Gupta, Pallavee Bhatnagar, Lalit Kumar Sahu, and Shailendra Jain, “ Multilevel inverter

topologies with reduced device count: A review, ” IEEE Trans. Power Electronics, vol. 31,No.1 pp. 135-151,

Jan.2016.

[14] E. Samadaei, S. A. Gholamian, A. Sheikholeslami, and J. Adabi, “An envelope type (E-type) module: Asymmetric

multilevel inverters with reduced components,” IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7148–7156, Nov.

2016.

[15] Y. Hu, Y. Xie, D. Fu, and L. Cheng, “A new single-phase π-type 5-level inverter using 3-terminal switch-

network,” IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7165–7174, Nov. 2016

[16] X.Sun, B.Wang, Y.Zhou, W.Wang, H.Du,and Z.Lu, “A single dc source cascaded seven-level inverter integrating

switched-capacitor techniques,” IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7184–7194, Nov. 2016.

[17] Q. A. Le and D.-C. Lee, “A novel six-level inverter topology for medium-voltage applications,” IEEE

Trans.Ind.Electron.,vol.63,no.11, pp. 7195–7203, Nov. 2016.

[18] R. Samanbakhsh and A. Taheri, “ Reduction of power electronic components in multilevel converters using new

switched capacitor-diode structure,” IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7204–7214, Nov. 2016.

[19] Viju Nair R, Arun Rahul S, R. Sudharshan Kaarthik, Abhijit Kshirsagar, and K. Gopakumar, “Generation of

higher number of voltage levels by stacking inverters of lower multilevel structures with low voltage devices for

drives,” IEEE Trans. Power Electron, vol. 32, no. 1,pp.52-59, Jan 2017.

[20] Rasoul Shalchi Alishah, Seyed Hossein, Ebrahim Babaei, and Mehran Sabahi, “Optimal design of new cascaded

switch-ladder multilevel inverter structure,” IEEE Trans. Ind. Electron., vol. 64, no. 3, pp. 2072-2080, Mar.2017.

[21] M. Farhadi Kangarlu and E. Babaei, “Cross-switched multilevel inverter: An innovative topology,” IET Power

Electron., vol. 6, no. 4, pp. 642–651, Apr. 2013.

[22] Brendan Peter McGrath, Donald Grahame Holmes, “Multicarrier PWM strategies for multilevel inverters,” IEEE

Trans. Industrial Electronics, Vol. 49, No. 4,2002.

AUTHORS

Aparna Prayag was born in Sangli, India in 1978. She received the B.E. and M.E. degree in

electrical engineering from Walchand College of Engineering, Sangli, India, in 1999 and 2004

respectively. She is currently working towards the Ph.D. degree in G. H. Raisoni college of

engineering, Nagpur, India. Her research interests include multilevel inverters, power electronics

and distributed generation

Sanjay Bodkhe received the B.E. degree in electrical engineering from Walchand College of

Engineering, Sangli, India , in 1990; M.Tech in IPS from VRCE Nagpur, India in 1996 and Ph.D.

from VNIT, Nagpur, India in the year 2011.

He is former professor of electrical engineering in G. H. Raisoni college of engineering, Nagpur,

India and currently a professor of electrical engineering with Shri Ramdeobaba College of

Engineering & Management, Nagpur, India. His research interests are electric motor drives, power

electronics and smart grid.

Volume 6, Issue 11, November 2018 Page 29

You might also like

- Cascaded Multilevel Inverters With Reduced Number of ComponentsDocument8 pagesCascaded Multilevel Inverters With Reduced Number of ComponentsAnand KumarNo ratings yet

- An Eleven-Level Switched-Capacitor Inverter With Boosting CapabilityDocument13 pagesAn Eleven-Level Switched-Capacitor Inverter With Boosting CapabilityMD REYAZ HUSSANNo ratings yet

- Cascaded Multilevel Inverter With Series Connection of Novel H-Bridge Basic UnitsDocument8 pagesCascaded Multilevel Inverter With Series Connection of Novel H-Bridge Basic Unitssatya_vanapalli3422No ratings yet

- Calculation of Power Loss and Voltage Regulation For Different Static LoadsDocument14 pagesCalculation of Power Loss and Voltage Regulation For Different Static LoadsiisteNo ratings yet

- Literature ReviewDocument20 pagesLiterature ReviewShiyona ShibuNo ratings yet

- A Novel Multilevel Inverter With Minimum Switches: Research PapersDocument6 pagesA Novel Multilevel Inverter With Minimum Switches: Research Papersmanjumtech0034269No ratings yet

- Design, Matlab/Simulink Modeling of Novel 5-Level & 7-Level Multi-Level Inverter TopologiesDocument6 pagesDesign, Matlab/Simulink Modeling of Novel 5-Level & 7-Level Multi-Level Inverter Topologiesdipendra prasad yadav.No ratings yet

- DC Exp 5 Student ManualDocument5 pagesDC Exp 5 Student ManualMuhammad ZayedNo ratings yet

- International Journal of Engineering Research and DevelopmentDocument7 pagesInternational Journal of Engineering Research and DevelopmentIJERDNo ratings yet

- Optimal Design of A New Cascaded Multilevel Inverter Topology With Reduced Switch CountDocument13 pagesOptimal Design of A New Cascaded Multilevel Inverter Topology With Reduced Switch Countfarid kerroucheNo ratings yet

- Performance Analysis of Asymmetrical Cascaded H-Bridge Nine Level Inverter With Photovoltaic ArraysDocument4 pagesPerformance Analysis of Asymmetrical Cascaded H-Bridge Nine Level Inverter With Photovoltaic ArraysijsretNo ratings yet

- Laboratory Manual For Linear ElectronicsDocument102 pagesLaboratory Manual For Linear ElectronicssamactrangNo ratings yet

- Performance Analysis of Positive Feedback Adiabatic Logic For Low PowerDocument7 pagesPerformance Analysis of Positive Feedback Adiabatic Logic For Low PowerKiran KumarNo ratings yet

- GA Based Performance Enhancement of SHE Methods For Nine-Level InverterDocument6 pagesGA Based Performance Enhancement of SHE Methods For Nine-Level InverterInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Hybrid Topology of Symmetrical Multilevel Inverter Using Less Number of DevicesDocument11 pagesHybrid Topology of Symmetrical Multilevel Inverter Using Less Number of DevicesGolam ZakariaNo ratings yet

- Ijert Ijert: Performance of Single Phase Shunt Active Filter Based On P-Q Technique Using Matlab/SimulinkDocument5 pagesIjert Ijert: Performance of Single Phase Shunt Active Filter Based On P-Q Technique Using Matlab/SimulinkR.SRIKANTHNo ratings yet

- Babae I 2014Document7 pagesBabae I 2014Anand KumarNo ratings yet

- Jsaer2015 02 01 16 21Document6 pagesJsaer2015 02 01 16 21jsaereditorNo ratings yet

- SPICE Version 2G User's GuideDocument48 pagesSPICE Version 2G User's Guidexing tangNo ratings yet

- Survey of CascadeDocument10 pagesSurvey of Cascadesumiths32No ratings yet

- LabInstr EE320L Lab7Document9 pagesLabInstr EE320L Lab7baig79No ratings yet

- Analog and Digital Electronics (Ade) Lab Manual by Prof. Kavya M. P. (SGBIT, BELAGAVI)Document74 pagesAnalog and Digital Electronics (Ade) Lab Manual by Prof. Kavya M. P. (SGBIT, BELAGAVI)Veena B Mindolli71% (7)

- American International University-Bangladesh: Department of Electrical and Electronic EngineeringDocument4 pagesAmerican International University-Bangladesh: Department of Electrical and Electronic EngineeringRuham RofiqueNo ratings yet

- A New Symmetric Multilevel Inverter Topology Using Single and Double Source Sub-Multilevel InvertersDocument10 pagesA New Symmetric Multilevel Inverter Topology Using Single and Double Source Sub-Multilevel InvertersSimhaLagendNo ratings yet

- IET-PEL - Comprehensive Analysis of A Novel Three-Phase Multilevel Inverter With Minimum Number of SwitchesDocument8 pagesIET-PEL - Comprehensive Analysis of A Novel Three-Phase Multilevel Inverter With Minimum Number of SwitchesKartick JanaNo ratings yet

- Performance Evaluation of Asymmetricalcascaded Hbridge Multilevel InverterDocument10 pagesPerformance Evaluation of Asymmetricalcascaded Hbridge Multilevel InverterKrishna KamalNo ratings yet

- Modeling and Control Design of A Static Synchronous Series CompensatorDocument6 pagesModeling and Control Design of A Static Synchronous Series Compensatorsteffy ruizNo ratings yet

- Different Multilevel Inverter Topologies With Reduced Number of DevicesDocument7 pagesDifferent Multilevel Inverter Topologies With Reduced Number of DevicesAnand TRNo ratings yet

- Common Emitter Amplifier: EE091 Electronic DevicesDocument8 pagesCommon Emitter Amplifier: EE091 Electronic DevicesVy NguyễnNo ratings yet

- 15 Electric Circuit Analysis: If The Source Is... The Analysis Type Is..Document26 pages15 Electric Circuit Analysis: If The Source Is... The Analysis Type Is..Suresh NikalajeNo ratings yet

- A Cascaded H-Bridge Multilevel Inverter With Photovoltaic MPPT ControlDocument11 pagesA Cascaded H-Bridge Multilevel Inverter With Photovoltaic MPPT ControlpreethaNo ratings yet

- Analog Non-Linear Function Synthesis: Published In: IEEE Micro, Vol. 16, No. 5, October 1996, Pp. 50-52Document5 pagesAnalog Non-Linear Function Synthesis: Published In: IEEE Micro, Vol. 16, No. 5, October 1996, Pp. 50-52Samina MohsinNo ratings yet

- A New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology With Reduced Switch Count and Voltage StressDocument11 pagesA New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology With Reduced Switch Count and Voltage StressIamIam If IamNotNo ratings yet

- MTTFmosfetDocument29 pagesMTTFmosfetSaif AbsarNo ratings yet

- Multilevel InverterDocument7 pagesMultilevel InverterJournalNX - a Multidisciplinary Peer Reviewed JournalNo ratings yet

- Modeling and Analysis of PV Fed DC-DC Converters: P. Maithili, J. Kanakaraj, T.ViswanathanDocument4 pagesModeling and Analysis of PV Fed DC-DC Converters: P. Maithili, J. Kanakaraj, T.ViswanathanVishal KevatNo ratings yet

- WCECS2015 pp204-209 PDFDocument6 pagesWCECS2015 pp204-209 PDFMohamed RafiqNo ratings yet

- AC Electrical Circuits Lab Manual 123Document98 pagesAC Electrical Circuits Lab Manual 123xyzzyzNo ratings yet

- Iceict2015i020315001 PDFDocument6 pagesIceict2015i020315001 PDFmadihaNo ratings yet

- Experiment 1Document2 pagesExperiment 1MeghaNo ratings yet

- 14 IET Power Electronics - 2018 - SaeedianDocument12 pages14 IET Power Electronics - 2018 - SaeedianRanesh SubramaniNo ratings yet

- ARTICLE Onduleurs MultiniveauxDocument14 pagesARTICLE Onduleurs MultiniveauxKhalid SalmiNo ratings yet

- 14 - New Cascaded PDFDocument9 pages14 - New Cascaded PDFsreekantha2013No ratings yet

- Simulation Model of 1-Phase Pulse-Width Modulation Rectifier by Using MATLAB/SimulinkDocument10 pagesSimulation Model of 1-Phase Pulse-Width Modulation Rectifier by Using MATLAB/SimulinkInternational Journal of Advances in Applied Sciences (IJAAS)No ratings yet

- IJSR PaperFormat-1Document5 pagesIJSR PaperFormat-1sneha sakundeNo ratings yet

- Zamiri2014 PDFDocument6 pagesZamiri2014 PDFHariesh WaranNo ratings yet

- Iec Lab - Exp 06 - Fall 23-24Document5 pagesIec Lab - Exp 06 - Fall 23-24rakibulislamakash400% (1)

- Classification of Power Quality Events Using Wavelet Analysis and Probabilistic Neural NetworkDocument12 pagesClassification of Power Quality Events Using Wavelet Analysis and Probabilistic Neural NetworkIAES IJAINo ratings yet

- Experiment Report: Characterizing Resonant Series RLC Circuits Using LabviewDocument15 pagesExperiment Report: Characterizing Resonant Series RLC Circuits Using LabviewPortia ShilengeNo ratings yet

- 46 Multileveltopology PDFDocument5 pages46 Multileveltopology PDFDeepu ChinnaNo ratings yet

- Minimization of Total Harmonic Distorsion For Cascaded Multilevel Inverter With Reduced Number of SwitchesDocument5 pagesMinimization of Total Harmonic Distorsion For Cascaded Multilevel Inverter With Reduced Number of SwitchesijcnesNo ratings yet

- Scs ManualDocument83 pagesScs ManualSandali SinghNo ratings yet

- Multi Level InverterDocument4 pagesMulti Level InverterabsalnabiNo ratings yet

- A Novel Single Phase Multilevel Inverter Topology With Reduced Number of ElementspdfDocument4 pagesA Novel Single Phase Multilevel Inverter Topology With Reduced Number of ElementspdfwasabikikkomanNo ratings yet

- 44 497252739 - 12-06-2017 PDFDocument6 pages44 497252739 - 12-06-2017 PDFEditor IJRITCCNo ratings yet

- Electronics Engineering Program - PUPSTB ECEN 30012 Basic Electronics 1 Experiment #4: Parallel Circuit - Voltage and Current Measurement PrelabDocument4 pagesElectronics Engineering Program - PUPSTB ECEN 30012 Basic Electronics 1 Experiment #4: Parallel Circuit - Voltage and Current Measurement PrelabJewel Lim100% (1)

- An Envelope Type E-Type Module Asymmetric Multilevel Inverters With Reduced ComponentsDocument9 pagesAn Envelope Type E-Type Module Asymmetric Multilevel Inverters With Reduced Componentsr.ebrahimi1993No ratings yet

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDocument7 pagesTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- The Mexican Innovation System: A System's Dynamics PerspectiveDocument12 pagesThe Mexican Innovation System: A System's Dynamics PerspectiveInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDocument6 pagesDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDocument6 pagesAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDocument12 pagesStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- A Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)Document10 pagesA Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)International Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Design and Detection of Fruits and Vegetable Spoiled Detetction SystemDocument8 pagesDesign and Detection of Fruits and Vegetable Spoiled Detetction SystemInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Soil Stabilization of Road by Using Spent WashDocument7 pagesSoil Stabilization of Road by Using Spent WashInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDocument9 pagesAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Staycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityDocument10 pagesStaycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Ijaiem 2021 01 28 6Document9 pagesIjaiem 2021 01 28 6International Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Impact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryDocument8 pagesImpact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Performance of Short Transmission Line Using Mathematical MethodDocument8 pagesPerformance of Short Transmission Line Using Mathematical MethodInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- A Deep Learning Based Assistant For The Visually ImpairedDocument11 pagesA Deep Learning Based Assistant For The Visually ImpairedInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Anchoring of Inflation Expectations and Monetary Policy Transparency in IndiaDocument9 pagesAnchoring of Inflation Expectations and Monetary Policy Transparency in IndiaInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Synthetic Datasets For Myocardial Infarction Based On Actual DatasetsDocument9 pagesSynthetic Datasets For Myocardial Infarction Based On Actual DatasetsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Design and Manufacturing of 6V 120ah Battery Container Mould For Train Lighting ApplicationDocument13 pagesDesign and Manufacturing of 6V 120ah Battery Container Mould For Train Lighting ApplicationInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Swot Analysis of Backwater Tourism With Special Reference To Alappuzha DistrictDocument5 pagesSwot Analysis of Backwater Tourism With Special Reference To Alappuzha DistrictInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- The Effect of Work Involvement and Work Stress On Employee Performance: A Case Study of Forged Wheel Plant, IndiaDocument5 pagesThe Effect of Work Involvement and Work Stress On Employee Performance: A Case Study of Forged Wheel Plant, IndiaInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Vs 30cpu04pDocument7 pagesVs 30cpu04p208020No ratings yet

- 06 - ElectronicsDocument864 pages06 - ElectronicsHaytham Ammer MushtahaNo ratings yet

- Semiconductor Diode Modeling: Jon Kirwan Electronics HobbyistDocument11 pagesSemiconductor Diode Modeling: Jon Kirwan Electronics HobbyistjkirwanNo ratings yet

- Analog DigitalDocument30 pagesAnalog DigitalReggie GustiloNo ratings yet

- Nwiee 4.5m AntennaDocument3 pagesNwiee 4.5m AntennaHudionoHoodNo ratings yet

- DP Biometric 15024Document188 pagesDP Biometric 15024adrianbernaNo ratings yet

- PA - FCP - 013 - FleXNet12.1.39 Release - APRIL FinalDocument22 pagesPA - FCP - 013 - FleXNet12.1.39 Release - APRIL FinalIsatronix SecutiryNo ratings yet

- Basic Verilog Programs FileDocument33 pagesBasic Verilog Programs FileDaniel Anderson72% (18)

- Experiment - 3: Aim: Using 8051 Generate Square Wave Having 50% and 75% Duty Cycle andDocument3 pagesExperiment - 3: Aim: Using 8051 Generate Square Wave Having 50% and 75% Duty Cycle andDevashishGuptaNo ratings yet

- Kidde Vega Spares STock As at 04-10-2021Document3 pagesKidde Vega Spares STock As at 04-10-2021MaheshkumarNo ratings yet

- Anyhertz Drive ShenzenDocument5 pagesAnyhertz Drive ShenzenJose EspinozaNo ratings yet

- General Polar Pattern: SpecificationsDocument2 pagesGeneral Polar Pattern: SpecificationsEsteban Bonilla JiménezNo ratings yet

- Technical Plans For KT-88 Valve AmplifierDocument4 pagesTechnical Plans For KT-88 Valve AmplifierMark GlennNo ratings yet

- CV3393BL G 20 CultraviewDocument15 pagesCV3393BL G 20 CultraviewSamuel Ulises Leon GonzalezNo ratings yet

- Digitrip 520&520M Trip Units For Series NRX Circuit BreakersDocument40 pagesDigitrip 520&520M Trip Units For Series NRX Circuit BreakersEdwinNo ratings yet

- BEEE CP Doc (2022-23)Document21 pagesBEEE CP Doc (2022-23)Akshat goyalNo ratings yet

- CX9000 HWenDocument61 pagesCX9000 HWenDmitry VasilevNo ratings yet

- Linux Boot Loader and Boot in Raspberry Pi: Jonne SoininenDocument6 pagesLinux Boot Loader and Boot in Raspberry Pi: Jonne SoininenGabriel Astudillo MuñozNo ratings yet

- Earth Station TechnologyDocument244 pagesEarth Station Technologyhigra_2000@yahoo.com100% (39)

- How Microprocessors Work: Control Unit DCU (Data Cache Unit) Prefetch UnitDocument2 pagesHow Microprocessors Work: Control Unit DCU (Data Cache Unit) Prefetch UnitAhmad FairuzNo ratings yet

- Datasheet HMS-18002000-4T EN NA V202110Document2 pagesDatasheet HMS-18002000-4T EN NA V202110Nelson Jesus Calva HernandezNo ratings yet

- Sony Ta Ve150Document29 pagesSony Ta Ve150hifi2000No ratings yet

- Revised Bill of MaterialsDocument1 pageRevised Bill of Materialsanon_971974432No ratings yet

- Service Manual: NSX-DP25 NSX-HMT25Document39 pagesService Manual: NSX-DP25 NSX-HMT25clacalNo ratings yet

- EGS 2200 DriveDocument68 pagesEGS 2200 DrivevihaanNo ratings yet

- JY Series UPSDocument4 pagesJY Series UPSAsad IqbalNo ratings yet

- Solis 1 Phase 6-10kWDocument2 pagesSolis 1 Phase 6-10kWLeeNo ratings yet

- Back To Maxtrac and Radius GM300Document95 pagesBack To Maxtrac and Radius GM300Supriadi NnZzNo ratings yet

- NPCL Electronics & Instrumentation PapersDocument9 pagesNPCL Electronics & Instrumentation PapersJoyita BiswasNo ratings yet