Professional Documents

Culture Documents

23 Encoding PDF

Uploaded by

Bharghav RoyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

23 Encoding PDF

Uploaded by

Bharghav RoyCopyright:

Available Formats

Lecture 23 FSM design

◆ Logistics ■ FSM-design procedure

■ HW8 due Wednesday, March 11

■ Ant extra credit due Friday, March 13 1. State diagram

■ Final exam, Wednesday March 18, 2:30-4:20 pm here 2. state-transition table

■ Review session Monday, March 16, 4:30 pm, Place TBA

3. State minimization

◆ Last lecture 4. State encoding

■ General FSM Minimization

5. Next-state logic minimization

◆ Today 6. Implement the design

■ State encoding

µ One-hot encoding

µ Output encoding

■ State partitioning

CSE370, Lecture 23 1 CSE370, Lecture 23 2

Usual example: A vending machine A vending machine: After state minimization

◆ 15 cents for a cup of coffee

◆ Doesn’t take pennies or quarters Reset Reset present inputs next output

state D N state open

D' N' 0¢ 0 0 0¢ 0

◆ Doesn’t provide any change 0 1 5¢ 0

0¢ 1 0 10¢ 0

N 1 1 – –

Vending Open D' N' N 5¢ 0 0 5¢ 0

Coin Machine Release

Sensor FSM Mechanism D 0 1 10¢ 0

D 5¢ 1 0 15¢ 0

1 1 – –

N 10¢ 0 0 10¢ 0

0 1 15¢ 0

D 10¢ D' N' 1 0 15¢ 0

Clock 1 1 – –

N+D 15¢ – – 15¢ 1

15¢ 1 symbolic state table

[open]

CSE370, Lecture 23 3 CSE370, Lecture 23 4

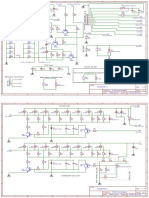

A vending machine: State encoding A vending machine: Logic minimization

Q1 Q1

D1 Q1 Open

D0

present state inputs next state output 0 0 1 1

0 1 1 0 0 0 1 0

Q1 Q0 D N D1 D0 open 0 1 1 1

0 0 0 0 0 0 0 N 1 0 1 1 N N

0 0 1 0

0 1 0 1 0 D X X X X

1 0 1 0 0 D X X X X D X X 1 X

1 1 – – – 1 1 1 1

0 1 1 1 0 0 1 0

0 1 0 0 0 1 0

0 1 1 0 0 Q0 Q0 Q0

1 0 1 1 0

1 1 – – –

1 0 0 0 1 0 0

0 1 1 1 0 D1 = Q1 + D + Q0 N

1 0 1 1 0

1 1 – – –

1 1 – – 1 1 1 D0 = Q0’ N + Q0 N’ + Q1 N + Q1 D

OPEN = Q1 Q0

CSE370, Lecture 23 5 CSE370, Lecture 23 6

A vending machine: Implementation State encoding

◆ Assume n state bits and m states

■ 2n! / (2n – m)! possible encodings

µ Example: 3 state bits, 4 states, 1680 possible state assignments

◆ Want to pick state encoding strategy that results in

optimizing your criteria

■ FSM size (amount of logic and number of FFs)

■ FSM speed (depth of logic and fan-in/fan-out)

■ FSM ease of design or debugging

CSE370, Lecture 23 7 CSE370, Lecture 23 8

State-encoding strategies One-hot encoding

◆ No guarantee of optimality ◆ One-hot: Encode n states using n flip-flops

■ An intractable problem ■ Assign a single “1” for each state

µ Example: 0001, 0010, 0100, 1000

◆ Most common strategies ■ Propagate a single “1” from one flip-flop to the next

■ Binary (sequential) – number states as in the state table µ All other flip-flop outputs are “0”

■ Random – computer tries random encodings

■ Heuristic – rules of thumb that seem to work well ◆ The inverse: One-cold encoding

µ e.g. Gray-code – try to give adjacent states (states with an arc ■ Assign a single “0” for each state

between them) codes that differ in only one bit position µ Example: 1110, 1101, 1011, 0111

■ One-hot – use as many state bits as there are states ■ Propagate a single “0” from one flip-flop to the next

■ Output – use outputs to help encode states µ All other flip-flop outputs are “1”

■ Hybrid – mix of a few different ones (e.g. One-hot +

◆ “almost one-hot” encoding (modified one-hot encoding)

heuristic)

■ Use no-hot (000…0) for the initial (reset state)

■ Assumes you never revisit the reset state till reset again.

CSE370, Lecture 23 9 CSE370, Lecture 23 10

Vending Machine:

One-hot encoding (con’t) One-hot encoded transition table

◆ Often the best/convenient approach for FPGAs present state inputs next state output

■ FPGAs have many flip-flops Q3Q2Q1Q0 D N D3 D2D1D0 open Reset

D' N'

0 0 0 1 0 0 0 0 0 1 0

◆ Draw FSM directly from the state diagram

0 1 0 0 1 0 0 0¢

■ + One product term per incoming arc 1 0 0 1 0 0 0

■ - Complex state diagram ⇒ complex design D' N' N

1 1 – – – – –

■ - Many states ⇒ many flip flops 0 0 1 0 0 0 0 0 1 0 0 5¢ D

0 1 0 1 0 0 0

1 0 1 0 0 0 0 N

1 1 – – – – – D 10¢ D' N'

0 1 0 0 0 0 0 1 0 0 0

0 1 1 0 0 0 0 N+D

1 0 1 0 0 0 0 15¢

[open] 1

1 1 – – – – –

1 0 0 0 – – 1 0 0 0 1

CSE370, Lecture 23 11 CSE370, Lecture 23 12

Advantage of one-hot encoding:

Designing from the state diagram

Output encoding

◆ Reuse outputs as state bits

Reset D0 = Q0D’N’

■ Why create new functions when you can use outputs?

D' N' D1 = Q0N + Q1D’N’ ■ Bits from state assignments are the outputs for that state

0¢ D2 = Q0D + Q1N + Q2D’N’ µ Take outputs directly from the flip-flops

D' N' N D3 = Q1D + Q2D + Q2N + Q3

Inputs Combinational

D OPEN = Q3

5¢ Logic Outputs

N

D 10¢ D' N' State Inputs State Outputs

Storage Elements

N+D

15¢

[open] 1 ◆ ad hoc - no tools

■ Yields small circuits for most FSMs

CSE370, Lecture 23 13 CSE370, Lecture 23 14

Vending machine

FSM partitioning

--- already in output encoding form

◆ Break a large FSM into two or more smaller FSMs

Reset D0 = Q0D’N’

D' N' D1 = Q0N + Q1D’N’ ◆ Rationale

0¢ D2 = Q0D + Q1N + Q2D’N’ ■ Less states in each partition

µ Simpler minimization and state assignment

D' N' N D3 = Q1D + Q2D + Q2N + Q3

µ Smaller combinational logic

D OPEN = Q3 µ Shorter critical path

5¢

■ But more logic overall

N

D D' N' ◆ Partitions are synchronous

10¢

■ Same clock!!!

N+D

15¢

[open] 1

CSE370, Lecture 23 15 CSE370, Lecture 23 16

Example: Partition the machine Introduce idle states for each partition

◆ Partition into two halves ◆ SA and SB handoff control between machines

C1

S1 S6

C2

C1 S2 C3 S5

S1 S6

C2

S3 C4 C5 S4

C3

S2 S5

S1 C1 S6

C1•S1

(C2•S6)’

C2•S6 C2

S3 C4 C5 S4 (C1•S1+

C3•S2+ C3•S2+

S2 C3+C5 SA SB C4•S3

S5

C4•S3+

C5•S2)’

S3 C4 C5•S2 S4

CSE370, Lecture 23 17 CSE370, Lecture 23 18

Partitioning rules Partitioning rules (con’t)

Rule #1: Source-state transformation Rule #3: Multiple transitions with same source or destination

Replace by transition to idle state (SA) Source ⇒ Replace by transitions to idle state (SA)

Destination ⇒ Replace with exit transitions from idle state

C1 C1 C3

S1 S6 S1 SA S2 C3+C5 C3•S2 + S5

S2 S5 C4•S3

SA SB

C4 C5 C4

Rule #2: Destination state transformation S3 S4 S3 C5•S2 S4

Replace with exit transition from idle state

Rule #4: Hold condition for idle state

C2 C2•S6 “OR exit conditions and invert”

S1 S6 S1 SA

C2•S6

C2•S6

S1 SA

CSE370, Lecture 23 19 CSE370, Lecture 23 20

Example: Six-state up/down counter Example: 6 state up/down counter

◆ Break into 2 parts ◆ Count sequence S0, S1, S2, S3, S4, S5

■ S2 goes to SA and holds, leaves after S5

U ≡ count up ■ S5 goes to SB and holds, leaves after S2

D ≡ count down ■ Down sequence is similar

U

S0 S5

U U

D

D D S0 S5

U U•S5 U U

S1 S4

D D D D (D•S3 + (D•S0+ D•S0 D

U D S1 SA U•S5)’ U•S2)’ SB S4

U D•S3

S2 S3 D D D

U U U U•S2 U

S2 S3

CSE370, Lecture 23 21 CSE370, Lecture 23 22

Example: 6 state up/down counter Example: 6 state up/down counter

Compare behavior U ◆ 4-state machines need 2 state bits each – total 4 state bits

S0 S5 Enough to represent 16 states, though the combination of the two

on UUUUUU: U U ■

D FSMs has only 6 different configurations

D D

S1 S4 ◆ Why do this?

D D ■ Each FSM may be much simpler to think about (and design logic for)

U D than the original FSM (not here, though)

U

S2 S3 ■ Essential to do this partitioning for large FSMs

U

S0 S5 S0 S5

U U•S5 U U U•S5 U

U U

D D (D•S3 + D•S0 D D D (D•S3 + D•S0 D

(D•S0+ (D•S0+

S1 SA U•S5)’ U•S2)’ SB S4 S1 SA U•S5)’ U•S2)’ SB S4

D•S3 D•S3

D D D D D D

U U U•S2 U U U U•S2 U

S2 S3 S2 S3

CSE370, Lecture 23 23 CSE370, Lecture 23 24

Minimize communication between partitions Mealy versus Moore partitions

◆ Ideal world: Two machines handoff control ◆ Mealy machine partitioning is undesirable

■ Separate I/O, states, etc. ■ Inputs can affect outputs immediately

µ “output” can be a handoff to another machine!!!

◆ Real world: Minimize handoffs and common I/O

■ Minimize number of state bits that cross boundary ◆ Moore machine partitioning is desirable

■ Merge common outputs ■ Input-to-output path always broken by a flip-flop

■ But…may take several clock cycles for input to propagate to

output

CSE370, Lecture 23 25 CSE370, Lecture 23 26

You might also like

- Finite State Machine - FSM Design: Prof. David Márquez ViloriaDocument16 pagesFinite State Machine - FSM Design: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- State Machine Timing: RetimingDocument15 pagesState Machine Timing: RetimingVeera RajuNo ratings yet

- uFpRL3AdQhah7iIwxXA0_ULTP_Fingerstyle_Mastery_01_A_Minor_CascadesDocument2 pagesuFpRL3AdQhah7iIwxXA0_ULTP_Fingerstyle_Mastery_01_A_Minor_CascadesRaquel Orozco VargasNo ratings yet

- Ports and Pins MapDocument1 pagePorts and Pins Mapnorbert.rendesNo ratings yet

- Deloitte Uk Ladder or Snake A 10 Year View of The Residential Property MarketDocument32 pagesDeloitte Uk Ladder or Snake A 10 Year View of The Residential Property MarketsannyNo ratings yet

- Music Class NotesDocument15 pagesMusic Class NotesΝικολέτα -No ratings yet

- Sensores de PistaDocument1 pageSensores de PistaspeedmatrixNo ratings yet

- Sampling Signals: OverviewDocument14 pagesSampling Signals: OverviewSanjaya SrinathNo ratings yet

- Gradient Descent: Ryan Tibshirani Convex Optimization 10-725Document27 pagesGradient Descent: Ryan Tibshirani Convex Optimization 10-725JohnNo ratings yet

- Learn NG: Flamenco Guitar Techniques - Part 1Document10 pagesLearn NG: Flamenco Guitar Techniques - Part 1dgl100% (2)

- Electrical Connection Diagram-Bluesun JoyDocument1 pageElectrical Connection Diagram-Bluesun Joyroberto_llanaNo ratings yet

- Synchronous or Phase-Sensitive DetectorDocument3 pagesSynchronous or Phase-Sensitive DetectorJoao CelloNo ratings yet

- Truck Loading RecordsDocument4 pagesTruck Loading RecordsMonica VaughanNo ratings yet

- 180 FSMDocument16 pages180 FSMBob McDonaldNo ratings yet

- Collection of LG LCD/LED/OLED TV Interconnect Diagrams Under 40 CharactersDocument364 pagesCollection of LG LCD/LED/OLED TV Interconnect Diagrams Under 40 CharactersMantención FastpackNo ratings yet

- Collection of LG LCD/LED/OLED TV Interconnect Diagrams Under 40 CharactersDocument364 pagesCollection of LG LCD/LED/OLED TV Interconnect Diagrams Under 40 Charactersgarcia5No ratings yet

- 14 Iteration Pattern Printing 2 NotesDocument12 pages14 Iteration Pattern Printing 2 NotesRahul B. WaghaleNo ratings yet

- General Finite State Machine (FSM) Design Moore/Mealy MachinesDocument4 pagesGeneral Finite State Machine (FSM) Design Moore/Mealy MachinesDebashish PalNo ratings yet

- Ñapanguita 1Document7 pagesÑapanguita 1MarceloNo ratings yet

- PT Alfa YogaDocument6 pagesPT Alfa Yogaghinaa mumthazahrachmatNo ratings yet

- Perfect Day: E A A D G CDocument1 pagePerfect Day: E A A D G CGiacomo AncillottoNo ratings yet

- State Mach Onehot PDFDocument7 pagesState Mach Onehot PDFAnil KumarNo ratings yet

- Amritha I ST Year MBBS Result 2019Document7 pagesAmritha I ST Year MBBS Result 2019Vijayan VelayudhanNo ratings yet

- EC 314: Public and Private Investment Q2: Time ValueDocument1 pageEC 314: Public and Private Investment Q2: Time ValueJamie WoodsNo ratings yet

- Financial Markets and ProductsDocument54 pagesFinancial Markets and ProductsNg Win WwaNo ratings yet

- GP1_V1.0Document1 pageGP1_V1.0pauloroberto_tecNo ratings yet

- 01 V1 - 2016CFA一级强化班 - 数量组合经济学固收3Document105 pages01 V1 - 2016CFA一级强化班 - 数量组合经济学固收3Mario XieNo ratings yet

- Flexible Learning Guide Cash FlowsDocument3 pagesFlexible Learning Guide Cash Flowsmizpah mae jolitoNo ratings yet

- Data Consumption and Cost Analysis of Paper in FY 20-21Document30 pagesData Consumption and Cost Analysis of Paper in FY 20-21Rohit AttriNo ratings yet

- La8n en Tcd210184aa 20210423 Catalog WDocument1 pageLa8n en Tcd210184aa 20210423 Catalog Wsigk sdaNo ratings yet

- Aula 1 - Tonalidades - ScoreDocument2 pagesAula 1 - Tonalidades - ScoreMaurício FigueiredoNo ratings yet

- Strategy: This Document Is Strictly For Personal Use. Do Not Share With OthersDocument24 pagesStrategy: This Document Is Strictly For Personal Use. Do Not Share With OthersDeepak ChaudharyNo ratings yet

- A6F Operation Manual Setup GuideDocument8 pagesA6F Operation Manual Setup GuideAdi PurnomoNo ratings yet

- Strategy: This Document Is Strictly For Personal Use. Do Not Share With OthersDocument23 pagesStrategy: This Document Is Strictly For Personal Use. Do Not Share With OthersDeepak ChaudharyNo ratings yet

- 1M01 Un Día Malo y Triste.: Flauta 1Document1 page1M01 Un Día Malo y Triste.: Flauta 1kevin vanegasNo ratings yet

- Belimo LM..A TM..A Installation-InstructionsDocument2 pagesBelimo LM..A TM..A Installation-InstructionsReirrac1No ratings yet

- ملخص الإحتمالاتDocument1 pageملخص الإحتمالاتBe CreativeNo ratings yet

- 24 Proba ResumDocument1 page24 Proba ResumYassine EL DahmiNo ratings yet

- Class10 31 05 2018Document22 pagesClass10 31 05 2018Mohamed El FellahiNo ratings yet

- Selected Formulas - 4thedition - Jul2018Document5 pagesSelected Formulas - 4thedition - Jul2018yantong0505No ratings yet

- Schematic - Eco Fuel 1.1.0 - 2022-04-26Document1 pageSchematic - Eco Fuel 1.1.0 - 2022-04-26Moni Que0% (1)

- Columbine Report Pgs 5201-5300Document100 pagesColumbine Report Pgs 5201-5300columbinefamilyrequestNo ratings yet

- Lect6 PDFDocument22 pagesLect6 PDF杜晓晚No ratings yet

- CDO TORRE B - CMECH - AC ID - P05 - V08 - 05 06 2023. ModelDocument1 pageCDO TORRE B - CMECH - AC ID - P05 - V08 - 05 06 2023. ModelCatalina Amar MondolNo ratings yet

- Advanced Hydraulic Fracturing Modeling by LecampionDocument16 pagesAdvanced Hydraulic Fracturing Modeling by Lecampionsmithyry2014No ratings yet

- Multiplier PDFDocument11 pagesMultiplier PDFDhurba KarkiNo ratings yet

- SJR Series GAUGE DIGITALDocument3 pagesSJR Series GAUGE DIGITALRandy YCNo ratings yet

- Repetition Control StructuresDocument53 pagesRepetition Control StructuresTobyprism TechnologyNo ratings yet

- Skala Dynamic Cone Penetrometer (DCP) : Mata Kuliah:: Lokasi::: KGDocument1 pageSkala Dynamic Cone Penetrometer (DCP) : Mata Kuliah:: Lokasi::: KGFajrul MiawanNo ratings yet

- For Claim Registration, Please Call On Toll Free Number 1800 2 666Document4 pagesFor Claim Registration, Please Call On Toll Free Number 1800 2 666Nishant JhaNo ratings yet

- Safety ORT Dosier Jan 2021Document20 pagesSafety ORT Dosier Jan 2021GautamupadhyayNo ratings yet

- Telemecanique PLC program dataDocument1 pageTelemecanique PLC program dataDragan Lini NinicNo ratings yet

- Student Bond ValuationDocument9 pagesStudent Bond Valuationtieuma712No ratings yet

- PUC - Alunos-2016-2-R01Document16 pagesPUC - Alunos-2016-2-R01gleissomachadoNo ratings yet

- Cim 8719 F.M. Suggested SolutionDocument7 pagesCim 8719 F.M. Suggested SolutionAnushka GuptaNo ratings yet

- Smarthome Sivaalti Aktuator Montaj Ve Kullanim Kilavuzu 4576225929Document2 pagesSmarthome Sivaalti Aktuator Montaj Ve Kullanim Kilavuzu 4576225929Deep BlueNo ratings yet

- (Leon Santillan - Piano PDFDocument3 pages(Leon Santillan - Piano PDFVictor BMNo ratings yet

- Ibf Bond Valuation .Document8 pagesIbf Bond Valuation .Anas4253No ratings yet

- Measures of Variation in StatisticsDocument20 pagesMeasures of Variation in StatisticsBharghav RoyNo ratings yet

- CCOpt RAKDocument55 pagesCCOpt RAKAsraa PaulNo ratings yet

- Partial and Multiple CorrelationDocument2 pagesPartial and Multiple CorrelationBharghav RoyNo ratings yet

- Correlation Analysis Techniques for EngineersDocument22 pagesCorrelation Analysis Techniques for EngineersBharghav RoyNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- MAT2001 Moments and Distribution MeasuresDocument8 pagesMAT2001 Moments and Distribution MeasuresBharghav RoyNo ratings yet

- Measures of Central Tendency: MAT2001-Statistics For EngineersDocument33 pagesMeasures of Central Tendency: MAT2001-Statistics For EngineersBharghav RoyNo ratings yet

- Moments and measures of skewness and kurtosisDocument10 pagesMoments and measures of skewness and kurtosisBharghav RoyNo ratings yet

- MAT2001 Measures of VariationDocument22 pagesMAT2001 Measures of VariationBharghav RoyNo ratings yet

- Measures of Variation in StatisticsDocument20 pagesMeasures of Variation in StatisticsBharghav RoyNo ratings yet

- SyllabDocument2 pagesSyllabSrivathson EswaranNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- MAT 2001 Statistics for Engineers: Joint, Marginal & Conditional Probability DistributionsDocument27 pagesMAT 2001 Statistics for Engineers: Joint, Marginal & Conditional Probability DistributionsBharghav RoyNo ratings yet

- PX X CP P: Tables of The Binomial Cumulative DistributionDocument8 pagesPX X CP P: Tables of The Binomial Cumulative Distributionvijay9421613648No ratings yet

- WINSEM2019-20 MAT2001 ETH VL2019205002653 Reference Material I 05-Dec-2019 Measures of Central Dent.Document26 pagesWINSEM2019-20 MAT2001 ETH VL2019205002653 Reference Material I 05-Dec-2019 Measures of Central Dent.Aditya KrishnaNo ratings yet

- MAT2001 Moments and Distribution MeasuresDocument8 pagesMAT2001 Moments and Distribution MeasuresBharghav RoyNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- Microprocessor Made Easy PDFDocument87 pagesMicroprocessor Made Easy PDFBharghav RoyNo ratings yet

- Zomato Order: Summary and Receipt: Item Quantity Unit Price Total PriceDocument1 pageZomato Order: Summary and Receipt: Item Quantity Unit Price Total PriceBharghav RoyNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- Zomato Order: Summary and ReceiptDocument1 pageZomato Order: Summary and ReceiptBharghav RoyNo ratings yet

- Classic 350 Gunmetal Grey: Technical SpecificationsDocument2 pagesClassic 350 Gunmetal Grey: Technical SpecificationsYash R PatelNo ratings yet

- JHJDocument75 pagesJHJBharghav RoyNo ratings yet

- Use of Perl in Design Flow Automation An PDFDocument37 pagesUse of Perl in Design Flow Automation An PDFBharghav RoyNo ratings yet

- LefdefrefDocument32 pagesLefdefrefSandesh Kumar B VNo ratings yet

- Nationalised Banks Number SeriesDocument72 pagesNationalised Banks Number Seriesপ্ৰকাশ বড়াNo ratings yet

- Quant Power Question Bank PDFDocument565 pagesQuant Power Question Bank PDFchetan shindeNo ratings yet

- SYALLABUSDocument2 pagesSYALLABUSBharghav RoyNo ratings yet

- Paytm Prepaid Electricity Recharge SolutionDocument11 pagesPaytm Prepaid Electricity Recharge SolutionNM GroupNo ratings yet

- 2021 MSF2021 PM MG Precon3dDocument4 pages2021 MSF2021 PM MG Precon3dPavao MarovicNo ratings yet

- Qlogic SAN CLI GuideDocument408 pagesQlogic SAN CLI Guide김대성No ratings yet

- Openshift Container Platform-4.10-Migrating From Version 3 To 4-pt-brDocument116 pagesOpenshift Container Platform-4.10-Migrating From Version 3 To 4-pt-brAdriano GrygonisNo ratings yet

- DS52 N FA410Document2 pagesDS52 N FA410Kelvin NgNo ratings yet

- CIS Apple macOS 10.13 Benchmark v1.0.0 PDFDocument196 pagesCIS Apple macOS 10.13 Benchmark v1.0.0 PDFJohn DavisonNo ratings yet

- SVKM'S Nmims Mukesh Patel School of Technology Management & Engineering Computer Engineering DepartmentDocument10 pagesSVKM'S Nmims Mukesh Patel School of Technology Management & Engineering Computer Engineering DepartmentHemit ShahNo ratings yet

- Med TransDocument8 pagesMed TransAnya MayNo ratings yet

- Notice 518427805Document1 pageNotice 518427805Cyber RegalsNo ratings yet

- Bulk Carrier Safety ABS RulesDocument3 pagesBulk Carrier Safety ABS RulesHUNG LE THANHNo ratings yet

- Sun Series Autoclave Steam SterilizerDocument12 pagesSun Series Autoclave Steam SterilizeralexisNo ratings yet

- CP Roadmap For Below ExpertsDocument5 pagesCP Roadmap For Below ExpertsOmar ChessNo ratings yet

- Aocl Programming GuideDocument50 pagesAocl Programming GuideHugo ContrerasNo ratings yet

- Service Manual Pearl Ar JSFDHWKDocument108 pagesService Manual Pearl Ar JSFDHWKChad HensonNo ratings yet

- Manual NATRDocument2 pagesManual NATRPaco Ramírez HernándezNo ratings yet

- Lesson 1 Make The Car MoveDocument26 pagesLesson 1 Make The Car MoveSWNo ratings yet

- Acer Ferrari 3200 3400 1 Quanta ZI5 - Rev1ADocument32 pagesAcer Ferrari 3200 3400 1 Quanta ZI5 - Rev1AdanielNo ratings yet

- OpenTable Case StudyDocument5 pagesOpenTable Case StudyLi LoanNo ratings yet

- Hummer Space Adventure Service ManualDocument73 pagesHummer Space Adventure Service ManualTony KututoNo ratings yet

- nAS 400 PDFDocument4 pagesnAS 400 PDFMatt TravisNo ratings yet

- CH 06A Operating System BasicsDocument49 pagesCH 06A Operating System BasicsAbdus Salam RatanNo ratings yet

- Upgrading Cowon A2 HDDDocument11 pagesUpgrading Cowon A2 HDDgaddNo ratings yet

- Proforma Servidor Conico 1Document1 pageProforma Servidor Conico 1Alejandro RochaNo ratings yet

- Servlet Filter - JavatpointDocument4 pagesServlet Filter - JavatpointHarsha Vardhan VNo ratings yet

- Communicate with embedded devices via Bluetooth with the ZX-BLUETOOTH boardDocument10 pagesCommunicate with embedded devices via Bluetooth with the ZX-BLUETOOTH boardashwanisingla013No ratings yet

- Wireless Charging Solution For Artificial Cardiac PacemakersDocument8 pagesWireless Charging Solution For Artificial Cardiac PacemakersInternational Journal of Application or Innovation in Engineering & Management100% (1)

- Preparing a Highway ModelDocument4 pagesPreparing a Highway Modelrinlu patilNo ratings yet

- Basic Prediction Techniques in Modern Video Coding Standards PDFDocument90 pagesBasic Prediction Techniques in Modern Video Coding Standards PDFAndrijaNo ratings yet

- Camera Tools in Autodesk MayaDocument32 pagesCamera Tools in Autodesk MayaMary Joy QuillopeNo ratings yet

- 1.3.2.5 Packet Tracer - Investigating Directly Connected Routes InstructionsDocument3 pages1.3.2.5 Packet Tracer - Investigating Directly Connected Routes InstructionsTadeo Alberto Arias Keb100% (1)