Professional Documents

Culture Documents

Max 32660

Uploaded by

ZalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Max 32660

Uploaded by

ZalCopyright:

Available Formats

EVALUATION KIT AVAILABLE

Click here for production status of specific part numbers.

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

General Description Benefits and Features

DARWIN is a new breed of low-power microcontrollers ●● High-Efficiency Microcontroller for Wearable Devices

built to thrive in the rapidly evolving Internet of Things (IoT). • Internal Oscillator Operates Up to 96MHz

They are smart, with the biggest memories in their class • 256KB Flash Memory

and a massively scalable memory architecture. They run • 96KB SRAM, Optionally Preserved in Lowest

forever, thanks to wearable-grade power technology. They Power Backup Mode

are also tough enough to withstand the most advanced • 16KB Instruction Cache

cyberattacks. DARWIN microcontrollers are designed • Memory Protection Unit (MPU)

to run any application imaginable—in places where you • Low 1.1V VCORE Supply Voltage

would not dream of sending other microcontrollers. • 3.6V GPIO Operating Range

Generation U microcontrollers are perfect for wearables • Internal LDO Provides Operation from Single Supply

and IoT applications that cannot afford to compromise • Wide Operating Temperature: -40°C to +105°C

power, performance or cost. The MAX32660 is an ●● Power Management Maximizes Uptime for Battery

ultra-low-power, cost-effective, highly-integrated micro- Applications

controller designed for battery-powered devices and wire- • 85μA/MHz Active Executing from Flash

less sensors. It combines a flexible and versatile power • 2μA Full Memory Retention Power in Backup Mode

management unit with the powerful Arm® Cortex®-M4 at VDD = 1.8V

with floating point unit (FPU). • 570nA Ultra-Low Power RTC at VDD = 1.8V

The MAX32660 enables designs with complex sensor • Internal 8kHz Ring Oscillator

processing without compromising battery life. It also offers ●● Optimal Peripheral Mix Provides Platform Scalability

legacy designs an easy and cost optimal upgrade path • Up to 14 General-Purpose I/O Pins

from 8- or 16-bit microcontrollers. • Up to Two SPI Master/Slave

The device integrates up to 256KB of flash memory and • I2S Master/Slave

96KB of RAM to accommodate application and sensor code. • Up to Two UARTs

• Up to Two I2C Master/Slave, 3.4Mbps High Speed

It supports SPI, UART and I2C communication in a tiny • Four-Channel Standard DMA Controller

form factor: 1.6mm x 1.6mm 16-bump WLP or 4mm x • Three 32-Bit Timers

4mm 20-pin TQFN-EP, or 3mm x 3mm 24-pin TQFN-EP. • Watchdog Timer

• CMOS-Level 32.768kHz RTC Output

Applications

●● Sports Watches

Ordering Information appears at end of data sheet.

●● Fitness Monitors

●● Wearable Medical Patches

●● Portable Medical Devices

●● Industrial Sensors

●● IoT

●● Optical Modules: QSFP-DD, QSFP, 400G

Arm and Cortex are registered trademarks of Arm Limited (or

its subsidiaries) in the US and/or elsewhere.

19-100236; Rev 4; 8/18

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

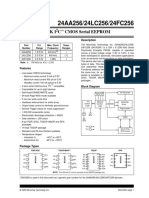

Simplified Block Diagram

MAX32660

HFIO UP TO 96MHz

HOST

32.768kHz ARM CORTEX-M4

8kHz WITH FPU CPU

NVIC

32-BIT TIMER

MEMORY

POR,

BROWNOUT GPIO AND

FLASH 2 × SPI MASTER/ SHARED PAD

RSTN MONITOR, SLAVE

BUS MATRIX – AHB, APB, IBUS, DBUS…

256KB FUNCTIONS

SUPPLY VOLTAGE

I2S SLAVE

MONITORS

TIMER

SRAM SPI GPIO

96KB /ALTERNATE

2 × I2C MASTER/ I2C

VCORE SLAVE UART FUNCTION

I2S UP TO 14

16KB CACHE 32kHz OUTPUT

REGULATOR/

VDD

POWER CONTROL

2 × UART

EXTERNAL

VSS STANDARD DMA INTERRUPTS

SERIAL WIRE DEBUG

WATCHDOG TIMER

(SWD)

2 × 32 BIT TIMER

32KIN

RTC

32KOUT

www.maximintegrated.com Maxim Integrated │ 2

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Absolute Maximum Ratings

(All voltages with respect to VSS, unless otherwise noted.) Continuous Package Power Dissipation

VCORE.................................................................-0.3V to +1.21V 20 TQFN-EP (multilayer board) TA = +70°C

VDD......................................................................-0.3V to +3.63V (derate 30.3mW/°C above +70°C)..........................2424.2mW

32KIN, 32KOUT...........................................-0.3V to VDD + 0.3V Continuous Package Power Dissipation

RSTN, GPIO.................................................-0.3V to VDD + 0.3V 24 TQFN-EP (multilayer board) TA = +70°C

Total Current into All GPIO Combined (sink)....................100mA (derate 16.3mW/°C above +70°C).............................1305mW

VSS....................................................................................100mA Operating Temperature Range.......................... -40°C to +105°C

Output Current (sink) by Any GPIO Pin..............................25mA Storage Temperature Range............................. -65°C to +150°C

Output Current (source) by Any GPIO Pin.........................-25mA Soldering Temperature (reflow)........................................+260°C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these

or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

Package Information

16 WLP

Package Code W161K1+1

Outline Number 21-100241

Land Pattern Number Refer to Application Note 1891

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA) 66.34 °C/W

Junction to Case (θJC) N/A

20 TQFN-EP

Package Code T2044+5C

Outline Number 21-0139

Land Pattern Number 90-0429

Thermal Resistance, Single-Layer Board:

Junction to Ambient (θJA) 48°C/W

Junction to Case (θJC) 2°C/W

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA) 33°C/W

Junction to Case (θJC) 2°C/W

24 TQFN-EP

Package Code T2433+2C

Outline Number 21-100264

Land Pattern Number 90-100089

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA) 61.3°C/W

Junction to Case (θJC) 2.2°C/W

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a “+”,

“#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board.

For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

www.maximintegrated.com Maxim Integrated │ 3

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

POWER SUPPLIES / BOTH SINGLE SUPPLY OPERATION AND DUAL SUPPLY OPERATION

Supply Voltage VDD 1.71 1.8 3.63 V

OVR = [00] 0.855 0.9 0.945

Dual-supply

OVR = [01] 0.95 1.0 1.05 V

Supply Voltage, Core VCORE operation

Default OVR = [10] 1.045 1.1 1.155

Single-supply operation Not Used

Monitors VDD 1.63 1.71

Power-Fail Reset Voltage VRST Monitors VCORE during dual-supply V

0.80 0.845

operation

Monitors VDD 1.4

Power-On Reset Voltage VPOR Monitors VCORE during dual supply V

0.65

operation

Sleep Mode Resume Time tSLP_ON 0.57 μs

Deep Sleep Mode Resume

tDSL_ON 1 ms

Time

Backup Mode Resume

tBKU_ON 1 ms

Time

POWER SUPPLIES / SINGLE SUPPLY OPERATION (VDD ONLY)

OVR = [10], Internal

HFIO enabled, regulator set to 1.1V, 85

total current into fSYS_CLK(MAX) = 96MHz

VDD pin, CPU

OVR = [01], Internal

VDD Dynamic Current, Ac- in Active mode,

IDD_DACT regulator set to 1.0V, 74 μA/MHz

tive Mode inputs tied to

fSYS_CLK(MAX) = 48MHz

VSS or VDD,

outputs source/ OVR = [00], Internal

sink 0mA regulator set to 0.9V, 50

fSYS_CLK(MAX) = 24MHz

HFIO enabled, OVR = [10], Internal

total current regulator set to 1.1V, 488

into VDD pin, fSYS_CLK(MAX) = 96MHz

CPU in Active OVR = [01], Internal

VDD Fixed Current, Active mode 0MHz regulator set to 1.0V, 394

IDD_FACT μA

Mode execution, fSYS_CLK(MAX) = 48MHz

inputs tied to

VSS or VDD, OVR = [00], Internal

outputs source/ regulator set to 0.9V, 324

sink 0mA fSYS_CLK(MAX) = 24MHz

www.maximintegrated.com Maxim Integrated │ 4

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10], Internal

HFIO enabled, regulator set to 1.1V, 30.3

total current fSYS_CLK(MAX) = 96MHz

into VDD pin, OVR = [01], Internal

VDD Dynamic Current,

IDD_DSLP CPU in Sleep regulator set to 1.0V, 27 μA/MHz

Sleep Mode

mode, standard fSYS_CLK(MAX) = 48MHz

DMA with two OVR = [00], Internal

channels active regulator set to 0.9V, 24

fSYS_CLK(MAX) = 24MHz

OVR = [10], Internal

HFIO enabled, regulator set to 1.1V, 485

total current into fSYS_CLK(MAX) = 96MHz

VDD pin, CPU

OVR = [01], Internal

VDD Fixed Current, Sleep in Sleep mode,

IDD_FSLP regulator set to 1.0V, 391 μA

Mode inputs tied to

fSYS_CLK(MAX) = 48MHz

VSS or VDD,

outputs source/ OVR = [00], Internal

sink 0mA regulator set to 0.9V, 321

fSYS_CLK(MAX) = 24MHz

VDD Fixed Current, Deep Standby state with full data retention and

IDD_FDSL 4.2 μA

Sleep Mode 96kB SRAM retained

0KB SRAM retained with RTC enabled;

0.63

VDD=1.8V

16KB SRAM retained with RTC enabled;

1.09

VDD=1.8V

VDD Fixed Current, Backup 32KB SRAM retained with RTC enabled;

IDD_FBKU 1.30 μA

Mode VDD=1.8V

64KB SRAM retained with RTC enabled;

1.74

VDD=1.8V

96KB SRAM retained with RTC enabled;

2.04

VDD=1.8V

POWER SUPPLIES / DUAL SUPPLY OPERATION (VDD AND VCORE)

Total current into VCORE pin, HFIO

enabled, fSYS_CLK(MAX) = 96MHz, OVR =

VCORE Dynamic Current,

ICORE_DACT [10], executing code from cache memory, 85 μA/MHz

Active Mode

CPU in Active mode, inputs tied to VSS or

VDD,outputs source/sink 0mA

HFIO enabled, OVR = [10], total current

VCORE Fixed Current, Ac- into VCORE pin, CPU in Active mode 0MHz

ICORE_FACT 403 μA

tive Mode execution, inputs tied to VSS or VDD, outputs

source/sink 0mA

www.maximintegrated.com Maxim Integrated │ 5

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

HFIO enabled, OVR = [10], fSYS_CLK(MAX) =

96MHz, total current into VDD pin, executing

VDD Dynamic Current, Ac-

IDD_DACT code from cache memory, CPU in Active 0.40 μA/MHz

tive Mode

mode, inputs tied to VSS or VDD, outputs

source/sink 0mA

HFIO enabled, OVR = [10], total current

VDD Fixed Current, Active into VDD pin, CPU in Active mode 0MHz

IDD_FACT 84.8 μA

Mode execution, inputs tied to VSS or VDD, outputs

source/sink 0mA

HFIO enabled, OVR = [10], total current into

VCORE Dynamic Current,

ICORE_DSLP VCORE pin, CPU in Sleep mode, standard 27.7 μA/MHz

Sleep Mode

DMA with two channels active

HFIO enabled, OVR [10], total current into

VCORE Fixed Current,

ICORE_FSLP VCORE pin, CPU in Sleep mode, standard 270.3 μA

Sleep Mode

DMA with two channels active

HFIO enabled, OVR = [10], total current into

VDD Dynamic Current,

IDD_DSLP VDD pin, CPU in Sleep mode, standard DMA 0.20 μA/MHz

Sleep Mode

with two channels active

HFIO enabled, OVR = [10], total current into

VDD Fixed Current, Sleep

IDD_FSLP VDD pin, CPU in Sleep mode, standard DMA 65 μA

Mode

with two channels active

VCORE Fixed Current,

ICORE_FDSL VDD = 1.8V; VCORE=1.1V 5.7 μA

Deep-Sleep Mode

VDD Fixed Current, Deep

IDD_FDSL VDD = 1.8V, VCORE=1.1V 4.2 μA

Sleep Mode

VCORE Fixed Current, VDD = 1.8V; VCORE = 1.1V, 96KB SRAM

ICORE_FBKU 5 μA

Backup Mode retained

VDD = 1.8V; VCORE = 1.1V, 96KB SRAM

800 nA

retained

0KB SRAM retained with RTC enabled; VDD

0.63

= 1.8V; VCORE = 0V or unbiased

16KB SRAM retained with RTC enabled;

1.09

VDD Fixed Current, Backup VDD = 1.8V; VCORE = 0V or unbiased

IDD_FBKU

Mode 32KB SRAM retained with RTC enabled;

1.30 μA

VDD = 1.8V; VCORE = 0V or unbiased

64KB SRAM retained with RTC enabled;

1.74

VDD = 1.8V; VCORE = 0V or unbiased

96KB SRAM retained with RTC enabled;

2.04

VDD = 1.8V; VCORE = 0V or unbiased

www.maximintegrated.com Maxim Integrated │ 6

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

GENERAL-PURPOSE I/O

Input Low Voltage for All 0.3 ×

VIL_GPIO Pin configured as GPIO V

GPIO, RSTN VDD

Input High Voltage for All

VIH_GPIO Pin configured as GPIO 0.7 × VDD V

GPIO, RSTN

VDD = 1.71V, IOL = 1mA, DS[1:0] = 00

0.2 0.4

(Note 1)

VDD = 1.71V, IOL = 2mA, DS[1:0] = 10

Output Low Voltage for All 0.2 0.4

(Note 1)

GPIO Except P0.2, P0.3, VOL_GPIO V

P0.8, and P0.9 VDD = 1.71V, IOL = 4mA, DS[1:0] = 01

0.2 0.4

(Note 1)

VDD = 1.71V, IOL = 6mA, DS[1:0] = 11

0.2 0.4

(Note 1)

Output Low Voltage for VDD = 1.71V, IOL = 2mA, DS = 0 (Note 1) 0.2 0.4

GPIO P0.2, P0.3, P0.8, VOL_I2C V

P0.9 VDD = 1.71V, IOL = 10mA, DS = 1 (Note 1) 0.2 0.4

VDD = 1.71V, IOH = 1mA, DS[1:0] = 00

VDD - 0.4

(Note 1)

VDD = 1.71V, IOH = 2mA, DS[1:0] = 10

Output High Voltage for All VDD - 0.4

(Note 1)

GPIO Except P0.2, P0.3, VOH_GPIO V

P0.8, and P0.9 VDD = 1.71V, IOH = 4mA, DS[1:0] = 01

VDD - 0.4

(Note 1)

VDD = 1.71V, IOH = 6mA, DS[1:0] = 11

VDD - 0.4

(Note 1)

Output High Voltage for VDD = 1.71V, IOH = 2mA, DS = 0 (Note 1) VDD - 0.4

GPIO P0.2, P0.3, P0.8, VOH_I2C V

P0.9 VDD = 1.71V, IOH = 10mA, DS = 1 (Note 1) VDD - 0.4

Combined IOL, All GPIO IOL_TOTAL 32 mA

Combined IOH, All GPIO IOH_TOTAL -32 mA

Input Hysteresis (Schmitt) VIHYS 300 mV

Input/Output Pin

CIO 4 pF

Capacitance for All Pins

Input Leakage Current Low IIL VIN = 0V, internal pullup disabled -500 +500 nA

Input Leakage Current

IIH VIN = 3.6V, internal pulldown disabled -500 +500 nA

High

Input Pullup Resistor to Pullup to VDD = 1.62V 22

RPU_VDD kΩ

RSTN Pullup to VDD = 3.63V 10.5

www.maximintegrated.com Maxim Integrated │ 7

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Pin configured as GPIO, pullup to VDD =

22

Input Pullup Resistor for 1.62V

RPU kΩ

All GPIO Pin configured as GPIO, pullup to VDD =

10.5

3.63V

Pin configured as GPIO, pulldown to VSS,

20

Input Pulldown Resistor for VDD = 1.62V

RPD kΩ

All GPIO Pin configured as GPIO, pulldown to VSS,

8.8

VDD = 3.63V

CLOCKS

System Clock Frequency fSYS_CLK 24 96 MHz

1/fSYS_

System Clock Period tSYS_CLK μs

CLK

High-Frequency Internal

fHFIO Default OVR = [10] 93.5 96 98.5 MHz

Oscillator (HFIO)

Nanoring Oscillator

fNANO 8 kHz

Frequency

32.768kHz watch crystal, CL = 6pF, ESR <

RTC Input Frequency f32KIN 32.768 kHz

90kΩ, C0 < 2pF

RTC Operating Current IRTC All power modes, RTC enabled 0.57 μA

RTC Power-Up Time tRTC_ ON 250 ms

FLASH MEMORY

tM_ERASE Mass erase 30

Flash Erase Time ms

tP_ERASE Page erase 30

Flash Programming Time

tPROG 60 μs

Per Word

Flash Endurance 10 kcycles

Data Retention tRET TA = +85°C 10 years

Note 1: When using a GPIO bias voltage of 2.97V, the drive current capability of the GPIO is 2x that of its drive strength when using

a GPIO bias voltage of 1.62V.

www.maximintegrated.com Maxim Integrated │ 8

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

VBAT

1.71V TO 3.63V

VDD

1µF MAX32660

LiON POWER

2.7 to 5.5V MANAGEMENT

0.855V TO 1.155V

VCORE

1µF

VSS

DUAL SUPPLY OPERATION

VBAT

1.71V TO 3.63V

VDD

1µF MAX32660

STANDARD

CELL

VCORE

1µF

VSS

SINGLE SUPPY OPERATION

Figure 1. Power Supply Operational Modes

www.maximintegrated.com Maxim Integrated │ 9

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics—SPI

(TIming specifications are guaranteed by design and not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

MASTER MODE

SPI Master Operating fSYS_CLK = 96MHz,

fMCK 48 MHz

Frequency fMCK(MAX) = fSYS_CLK/2

SPI Master SCK Period tMCK 1/fMCK ns

SCK Output Pulse-Width

tMCH, tMCL tMCK/2 ns

High/Low

MOSI Output Hold Time

tMOH tMCK/2 ns

After SCK Sample Edge

MOSI Output Valid to

tMOV tMCK/2 ns

Sample Edge

MISO Input Valid to SCK

tMIS 5 ns

Sample Edge Setup

MISO Input to SCK

tMIH tMCK/2 ns

Sample Edge Hold

SLAVE MODE

SPI Slave Operating

fSCK 48 MHz

Frequency

SPI Slave SCK Period tSCK 1/fSCK ns

SCK Input Pulse-Width

tSCH, tSCL tSCK/2

High/Low

SSx Active to First Shift

tSSE 10 ns

Edge

MOSI Input to SCK Sample

tSIS 5 ns

Edge Rise/Fall Setup

MOSI Input from SCK

Sample Edge Transition tSIH 1 ns

Hold

MISO Output Valid After

tSOV 5 ns

SCLK Shift Edge Transition

SCK Inactive to SSx Inac-

tSSD 10 ns

tive

SSx Inactive Time tSSH 1/fSCK μs

MISO Hold Time After SSx

tSLH 10 ns

Deassertion

www.maximintegrated.com Maxim Integrated │ 10

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

SHIFT SAMPLE SHIFT SAMPLE

SSx

(SHOWN ACTIVE LOW)

tMCK

SCK

CKPOL/CKPHA

0/1 OR 1/0

SCK tMCH tMCL

CKPOL/CKPHA

0/0 OR 1/1

tMOH

tMOV tMLH

MOSI/SDIOx

(OUTPUT) MSB MSB-1 LSB

tMIS tMIH

MISO/SDIOx

(INPUT) MSB MSB-1 LSB

Figure 2. SPI Master Mode Timing Diagram

SHIFT SAMPLE SHIFT SAMPLE

SSx tSSE

tSSH

(SHOWN ACTIVE LOW)

tSSD

SCK tSCK

CKPOL/CKPHA

0/1 OR 1/0

tSCH tSCL

SCK

CKPOL/CKPHA

0/0 OR 1/1

tSIS tSIH

MOSI/SDIOx

(INPUT) MSB MSB-1 LSB

tSOV tSLH

MISO/SDIOx MSB MSB-1 LSB

(OUTPUT)

Figure 3. SPI Slave Mode Timing Diagram

www.maximintegrated.com Maxim Integrated │ 11

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics—I2C

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

STANDARD MODE

Standard mode, from VOL_I2C(MIN) to

Output Fall Time tOF 150 ns

VOL_I2C(MAX)

SCL Clock Frequency fSCL 0 100 kHz

Low Period SCL Clock tLOW 4.7 μs

High Time SCL Clock tHIGH 4.0 μs

Setup Time for Repeated

tSU;STA 4.7 μs

Start Condition

Hold Time for Repeated

tHD;STA 4.0 μs

Start Condition

Data Setup Time tSU;DAT 300 ns

Data Hold Time tHD;DAT 10 ns

Rise Time for SDA and SCL tR 800 ns

Fall Time for SDA and SCL tF 200 ns

Setup Time for a Stop

tSU;STO 4.0 μs

Condition

Bus Free Time Between a

tBUS 4.7 μs

Stop and Start Condition

Data Valid Time tVD;DAT 3.45 μs

Data Valid Acknowledge

tVD;ACK 3.45 μs

Time

FAST MODE

Output Fall Time tOF From VOL_I2C(MIN) to VOL_I2C(MAX) 150 ns

Pulse Width Suppressed by

tSP 75 ns

Input Filter

SCL Clock Frequency fSCL 0 400 kHz

Low Period SCL Clock tLOW 1.3 μs

High Time SCL Clock tHIGH 0.6 μs

Setup Time for Repeated

tSU;STA 0.6 μs

Start Condition

Hold Time for Repeated

tHD;STA 0.6 μs

Start Condition

Data Setup Time tSU;DAT 125 ns

Data Hold Time tHD;DAT 10 ns

Rise Time for SDA and SCL tR 30 ns

Fall Time for SDA and SCL tF 30 ns

Setup Time for a Stop

tSU;STO 0.6 μs

Condition

www.maximintegrated.com Maxim Integrated │ 12

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics—I2C (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Bus Free Time Between a

tBUS 1.3 μs

Stop and Start Condition

Data Valid Time tVD;DAT 0.9 μs

Data Valid Acknowledge

tVD;ACK 0.9 μs

Time

FAST MODE PLUS

Output Fall Time tOF From VOL_I2C(MIN) to VOL_I2C(MAX) 80 ns

Pulse Width Suppressed by

tSP 75 ns

Input Filter

SCL Clock Frequency fSCL 0 1000 kHz

Low Period SCL Clock tLOW 0.5 μs

High Time SCL Clock tHIGH 0.26 μs

Setup Time for Repeated

tSU;STA 0.26 μs

Start Condition

Hold Time for Repeated

tHD;STA 0.26 μs

Start Condition

Data Setup Time tSU;DAT 50 ns

Data Hold Time tHD;DAT 10 ns

Rise Time for SDA and SCL tR 50 ns

Fall Time for SDA and SCL tF 30 ns

Setup Time for a Stop

tSU;STO 0.26 μs

Condition

Bus Free Time Between a

tBUS 0.5 μs

Stop and Start Condition

Data Valid Time tVD;DAT 0.45 μs

Data Valid Acknowledge

tVD;ACK 0.45 μs

Time

START STOP START

START

REPEAT tBUS

SDA

tOF tR

tSU;STO

tSP

tSU;DAT tSU;STA tHIGH

SCL

tHD;STA

tHD;DAT

tLOW

tVD;ACK

tVD;DAT

Figure 4. I2C Timing Diagram

www.maximintegrated.com Maxim Integrated │ 13

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Electrical Characteristics—I2S Slave

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Bit Clock Frequency fBCLK 96kHz LRCLK frequency 3.072 MHz

BCLK High Time tWBCLKH 0.5 1/fBCLK

BCLK Low Time 0.5 1/fBCLK

LRCLK Setup Time tLRCLK_BLCK 25 ns

Delay Time, BCLK to SD

tBCLK_SDO 12 ns

(Output) Valid

Setup Time for SD (Input) tSU_SDI 6 ns

Hold Time SD (Input) tHD_SDI 3 ns

tBLK

tWBCLKH tWBCLKL

BCLK

tLRCLK_BCLK

LRCLK

tBCLK_SDO

SD LSB MSB LSB MSB

(output)

tHD_SDI

tSU_SDI

SD

(input) LSB MSB LSB MSB

WORD N-1 RIGHT CHANNEL WORD N LEFT CHANNEL WORD N RIGHT CHANNEL

CONDITIONS: I2S_LJ = 0; I2S_MONO = 0;

CPOL = 0; CPHA = 0

Figure 5. I2S Timing Diagram

www.maximintegrated.com Maxim Integrated │ 14

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Pin Configurations

TOP VIEW TOP VIEW

P0.10

P0.11

P0.7

P0.8

P0.9

MAX32660

1 2 3 4 15 14 13 12 11

+

A

P0.6 16 10 VCORE

32KOUT 32KIN VDD VCORE

P0.5 17 9 VDD

B

MAX32660

RSTN VSS P0.9 P0.8 P0.4 18 8 32KIN

C P0.3 19 7 32KOUT

P0.0 P0.1 P0.6 P0.7

P0.2 20 EP* 6 VSS

+

D

P0.2 P0.3 P0.4 P0.5

1 2 3 4 5

16 WLP

P0.1

P0.0

P0.13

P0.12

RSTN

20 TQFN-EP

4mm x 4mm

*EP = EXPOSED PAD.

TOP VIEW

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

VDD

24 23 22 21 20

P0.1 1 19 P0.6

+

P0.0 2 18 P0.7

NC 3 17 P0.10

P0.13 4 MAX32660 16 P0.11

P0.12 5 15 NC

RSTN 6 EP* 14 P0.8

VSS 7 13 P0.9

8 9 10 11 12

VSS

32KOUT

32KIN

VSS

VDD

VCORE

P0.9

24 TQFN-EP

3mm x 3mm

*EP = EXPOSED PAD

Pin Description

PIN

20 24 NAME FUNCTION

16 WLP TQFN- TQFN-

EP EP

POWER

Digital Supply Voltage. This pin must be bypassed to VSS with a 1.0μF capaci-

tor as close as possible to the package. The device can operate soley from this

one power supply pin without the need to connect VCORE by utilizing the internal

A3 9 11, 22 VDD

VCORE regulator. The internal VCORE regulator automatically operates if the pres-

ence of a voltage on the VCORE pin is not detected. This provides single supply

battery operation capability.

www.maximintegrated.com Maxim Integrated │ 15

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Pin Description (continued)

PIN

20 24 NAME FUNCTION

16 WLP TQFN- TQFN-

EP EP

Core Supply Voltage. This pin provides dual supply operation to support PMIC-

based

systems and should be left open-circuit for single supply operation. This pin must

A4 10 12 VCORE

always

be bypassed to VSS with a 1.0μF capacitor as close as possible to the package

regardless of the supply mode of operation.

B2 6 7, 10 VSS Digital Ground

Exposed Pad (TQFN only). This pad must be connected to VSS. Refer to Applica-

— — — EP

tion Note 3273: Exposed Pads: A Brief Introduction for additional information.

CLOCK

32.768kHz Crystal Oscillator Input. Connect a 6pF 32.768kHz crystal between

A2 8 9 32KIN 32KIN and 32KOUT for RTC operation. Optionally, an external clock source can be

driven on 32KIN if the 32KOUT pin is left unconnected.

A1 7 8 32KOUT 32.768kHz Crystal Oscillator Output

RESET

Hardware Power Reset (Active-Low) Input. The device remains in reset while this

pin is in its active state. When the pin transitions to its inactive state, the device

performs a POR reset (resetting all logic on all supplies except for real-time clock

B1 5 6 RSTN circuitry) and begins execution. This pin is internally connected with an internal

pullup to the VDD supply as indicated in the Electrical Characteristics table. This pin

should be left unconnected if the system design does not provide a reset signal to

the device.

GENERAL-PURPOSE I/O (See Table 3 and Table 4 for pin mapping.)

C1 2 2 P0.0

C2 1 1 P0.1

D1 20 24 P0.2

D2 19 23 P0.3

D3 18 21 P0.4

D4 17 20 P0.5

C3 16 19 P0.6 General-Purpose I/O. Most port pins have multiple special functions. See Table 3

C4 15 18 P0.7 and Table 4 for details.

B4 12 14 P0.8

B3 11 13 P0.9

— 14 17 P0.10

— 13 16 P0.11

— 4 5 P0.12

— 3 4 P0.13

www.maximintegrated.com Maxim Integrated │ 16

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Detailed Description Memory

The MAX32660 is an ultra-low power, cost-effective, Internal Flash Memory

highly-integrated microcontroller designed for battery- 256KB of internal flash memory provides nonvolatile

powered devices and wireless sensors. It combines a storage of program and data memory.

flexible and versatile power management unit with the

Internal SRAM

powerful Arm Cortex-M4 processor with FPU. The device

enables designs with complex sensor processing without The internal 96KB SRAM provides low-power retention of

compromising battery life. It also offers legacy designs an application information in all power modes except shut-

easy and cost optimal upgrade path from 8- or 16-bit mi- down. The SRAM can be divided into granular banks that

crocontrollers. The device integrates up to 256KB of flash create a flexible SRAM retention architecture. This data

memory and 96KB of RAM to accommodate application retention feature is optional, and is configurable. This

and sensor code. granularity allows the application to minimize its power

consumption by only retaining the most essential data.

The device features four powerful and flexible power

modes. It can operate from a single- or dual-supply battery Clocking Scheme

voltage, typically provided by a PMIC. The I2C port supports The high-frequency internal oscillator (HFIO) operates at

standard, fast, fast-plus, and high-speed modes, operating a nominal frequency of 96MHz.

up to 3400kbps. The SPI ports can run up to 48MHz in

both master and slave mode, and the UARTs can run up to Optionally, two other oscillators can be selected depending

4000kbaud. Three general-purpose 32-bit timers, a watch- upon power needs:

dog timer, and a real-time clock are also provided. An I2S ●● 8kHz nano-ring oscillator

interface provides audio streaming to a codec. ●● 32.768kHz oscillator (external crystal required)

This clock is the primary clock source for the digital logic

and peripherals.

An external 32.768kHz timebase is required when using

the RTC.

RTC

CALIBRATION

OUTPUT

32KCAL

XTAL DRIVER OR ALWAYS-ON DOMAIN

EXTERNAL CLOCK 32KIN

4kHz

32kHz RTC

CRYSTAL OSC REAL-TIME CLOCK

CKT 32.768kHz

32KOUT NANO-RING

POWER SEQUENCER

~8kHz

GCR_CLKCN.CLKSEL

HFIO

PRESCALER CPU

HIGH-

FREQUENCY

INTERNAL ÷2 PERIPHERALS

OSCILLATOR

Figure 6. System Clocking Diagram

www.maximintegrated.com Maxim Integrated │ 17

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

General-Purpose I/O and Special Function Pins Power Management

Most general-purpose I/O (GPIO) pins share both a Power Management Unit

firmware-controlled I/O function and one or more special The power management unit (PMU) provides high-perfor-

function signals associated with peripheral modules. Pins mance operation while minimizing power consumption. It

can be individually enabled for GPIO or peripheral spe- exercises intelligent, precise control of power distribution

cial function use. Configuring a pin as a special function to the CPU and peripheral circuitry.

usually supersedes its use as a firmware-controlled I/O.

Though this multiplexing between peripheral and GPIO The PMU provides the following features:

functions is usually static, it can also be done dynami- ●● User-configurable system clock

cally. The electrical characteristics of a GPIO pin are ●● Automatic enabling and disabling of crystal oscillators

identical whether the pin is configured as an I/O or special based on power mode

function, except where explicitly noted in the Electrical

Characteristics tables. ●● Multiple clock domains

In GPIO mode, each pin of a port has an interrupt function ●● Fast wake-up of powered-down peripherals when

that can be independently enabled, and configured as a activity detected

level- or edge-sensitive interrupt. All GPIOs share the Active Mode

same interrupt vector. Some packages do not have all of In this mode, the CPU is executing application code

the GPIOs available. and all digital and analog peripherals are available on

When configured as GPIOs, the following features are demand. Dynamic clocking disables peripherals not in

provided. These features can be independently enabled use, providing the optimal mix of high-performance and

or disabled on a per-pin basis. low-power consumption.

●● Configurable as input, output, bidirectional, or high- Sleep Mode

impedance

This mode allows for low-power consumption operation.

●● Optional internal pullup resistor or internal pulldown The CPU is asleep, peripherals are on and the standard

resistor when configured as input DMA block is available. The GPIO or any active peripheral

●● Exit from low-power modes on rising or falling edge can be configured to interrupt and cause transition to the

Active mode.

●● Selectable standard- or high-drive modes

The MAX32660 provides up to 14 GPIOs for the 20-pin Deep-Sleep Mode

TQFN and up to 10 GPIOs for the 16-bump WLP. This mode corresponds to the Arm Cortex-M4 with FPU

Deep-sleep mode. In this mode, the register settings and

Standard DMA Controller all volatile memory is preserved. The GPIO pins retain

The standard DMA (direct memory access) controller pro- their state in this mode. The high-speed oscillator that

vides a means to off-load the CPU for memory/peripheral generates the 96MHz system clock can be shut down to

data transfer leading to a more power-efficient system. It provide additional power savings over Sleep mode.

allows automatic one-way data transfer between two enti- Multiple system events can cause the device to wake

ties. These entities can be either memories or peripherals. from Deep-sleep mode and return to the Active mode,

The transfers are done without using CPU resources. The including:

following transfer modes are supported:

●● RTC alarm

●● 4 channel

●● Enabled GPIO interrupt

●● Peripheral to data memory

Backup Mode

●● Data memory to peripheral

This mode places the CPU in a static, low-power state.

●● Data memory to data memory

In Backup mode, all of the SRAM can be retained. Data

●● Event support retention in this mode is maintained by the VDD supply

All DMA transactions consist of an AHB burst read into the only. SRAM retention can be 0KB, 16KB, 32KB, 64KB,

DMA FIFO followed immediately by an AHB burst write or full 96KB. Backup mode supports the same wake-up

from the FIFO. sources as Deep-sleep mode.

www.maximintegrated.com Maxim Integrated │ 18

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Real-Time Clock The WDT is a 32-bit, free-running counter with a configu-

A real-time clock (RTC) keeps the time of day in absolute rable prescaler. When enabled, the WDT must be periodi-

seconds. The 32-bit seconds register can count up to cally reset by the application software. Failure to reset the

approximately 136 years and be translated to calendar WDT within the user-configurable timeout period indicates

format by application software. that the application software is not operating correctly and

results in a WDT timeout. A WDT timeout can trigger an

The RTC provides a time-of-day alarm that can be pro- interrupt, system reset, or both. Either response forces

grammed to any future value between 1 second and 12 days. the instruction pointer to a known good location before

When configured for long intervals, the time-of-day alarm resuming instruction execution.

can be used as a power-saving timer, allowing the device

to remain in an extremely low-power mode, but still awaken The MAX32660 provides one instance of the watchdog

periodically to perform assigned tasks. A second indepen- timer (WDT0).

dent 32-bit 1/256 subsecond alarm can be programmed Programmable Timers

between 244μs and 256 seconds. Both can be configured

General-purpose, 32-bit timers provide timing, capture/

as recurring alarms. When enabled, either alarm can cause

compare, or generation of pulse-width modulated (PWM)

an interrupt or wake the device from most low power modes.

signals with minimal software interaction. Each of the

The time base is generated by a 32.768kHz crystal or an 32-bit timers can also be split into two 16-bit timers.

external clock source that must meet the electrical/timing

The timer provides the following features:

requirements in the Electrical Characteristics table.

●● 32-bit up/down autoreload

An RTC calibration feature provides the abil-

●● Programmable prescaler

ity for user-software to compensate for minor varia-

tions in the RTC oscillator, crystal, temperature, and ●● PWM output generation

board layout. Enabling the 32KCAL alternate func- ●● Capture, compare, and capture/compare capability

tion outputs a timing signal derived from the RTC. ●● External pin multiplexed with GPIO for timer input,

External hardware can measure the frequency and clock gating, or capture

adjust the RTC frequency in increments of ±127ppm ●● Timer output pin

with 1ppm resolution. Under most circumstances,

●● Configurable as 2 × 16-bit general-purpose timers

the oscillator does not require any calibration.

●● Timer interrupt

Watchdog Timer The MAX32660 provides three 32-bit timers: TIMER0,

Microcontrollers are often used in harsh environments TIMER1, and TIMER2.

where electrical noise and electromagnetic interference

I/O functionality is supported for TIMER0 only (TIMER_TMR0

(EMI) are abundant. Without proper safeguards, these

pin). Note that the function of a port can be multiplexed with

hazards can disturb device operation and corrupt program

other functions on the GPIO pins, so it might not be possible

execution. One of the most effective countermeasures is

to use all the ports depending on the device configuration.

the watchdog timer (WDT), which detects runaway code

or system unresponsiveness.

32-BIT TIMER BLOCK

APB

TIMER CONTROL TIME INTERRUPT

BUS

REGISTER REGISTER

32-BIT COMPARE

REGISTER

TIMER

COMPARE

APB INTERRUPT

CLOCK INTERRUPT

32-BIT TIMER PWM AND TIMER

(WITH PRESCALER) OUTPUT

CONTROL

COMPARE TIMER

32-BIT OUTPUT

PWM/COMPARE

TIMER

INPUT

Figure 7. 32-Bit Timer

www.maximintegrated.com Maxim Integrated │ 19

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Serial Peripherals Serial Peripheral Interface

I2C Interface The serial peripheral interface (SPI) is a highly con-

figurable, flexible, and efficient synchronous interface

The I2C interface is a bidirectional, two-wire serial bus that

between multiple SPI devices on a single bus. The bus

provides a medium-speed communications network. It can

uses a single clock signal and multiple data signals,

operate as a one-to-one, one-to-many or many-to-many

and one or more slave select lines to address only the

communications medium. These engines support stan-

intended target device. The SPI operates independently

dard-mode, fast-mode, fast-mode plus and high-speed

and requires minimal processor overhead.

mode I2C speeds. It provides the following features:

The provided SPI peripherals can operate in either slave

●● Master or slave mode operation

or master mode and provide the following features:

• Supports up to 4 different slave addresses in slave

●● SPI modes 0, 1, 2, 3 for single-bit communication

mode

●● 3- or 4-wire mode for single-bit slave device

●● Supports standard 7-bit addressing or 10-bit addressing

communication

●● RESTART condition

●● Full-duplex operation in single-bit, 4-wire mode

●● Interactive receive mode

●● Multimaster mode fault detection

●● Tx FIFO preloading

●● Programmable interface timing

●● Support for clock stretching to allow slower slave

●● Programmable SCK frequency and duty cycle

devices to operate on higher speed busses

●● 32-byte transmit and receive FIFOs

●● Multiple transfer rates

●● Slave select assertion and deassertion timing with

• Standard mode: 100kbps

respect to leading/trailing SCK edge

• Fast mode: 400kbps

The MAX32660 provides two instances of this SPI

• Fast mode plus: 1000kbps peripheral (SPI0, SPI1) with the following specifications

• High-speed mode: 3400kbps (Table 1):

●● Internal filter to reject noise spikes Table 1. SPI Configuration Options

●● Receiver FIFO depth of 8 bytes

SLAVE

●● Transmitter FIFO depth of 8 bytes SELECT MAXIMUM MAXIMUM

The MAX32660 provides two instances of the I2C LINES FREQUENCY FREQUENCY

INSTANCE DATA

(MASTER (SLAVE

peripheral (I2C0 and I2C1). 20 16 MODE) (MHz) MODE) (MHz)

TQFN WLP

3 wire,

SPI0 1 1 48 48

4 wire

3 wire,

SPI1 1 1 48 48

4 wire

www.maximintegrated.com Maxim Integrated │ 20

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

I2S Interface ●● Hardware flow control using RTS/CTS

The I2S interface is a bidirectional, four-wire serial bus ●● 4000kb maximum baud rate

that provides serial communications for codecs and audio ●● Two DMA channels can be connected (read and

amplifiers compliant with the I2S Bus Specification, June write FIFOs)

5, 1996. It provides the following features:

●● Programmable word size (5 bits to 8 bits)

●● Slave mode operation

The MAX32660 provides two instances of the UART

●● Normal and left-justified data alignment peripheral (UART0 and UART1) with the following

●● 16-bit audio transfer specifications (Table 2):

●● Wake-up on FIFO status (full/empty/threshold)

●● Interrupts generated for FIFO status

Table 2. UART Configuration Options

●● Receiver FIFO depth of 32 bytes FLOW CONTROL MAXIMUM BAUD

INSTANCE

●● Transmitter FIFO depth of 32 bytes 20 TQFP 16 WLP RATE (KB)

The MAX32660 provides one instance of the I2S UART0 Yes Yes 4000

peripheral that is multiplexed with the SPI1 peripheral. UART1 Yes No 4000

UART Debug and Development Interface (SWD)

The universal asynchronous receiver-transmitter (UART) The serial wire debug interface is used for code loading

interface supports full-duplex asynchronous communica- and ICE debug activities. All devices in mass production

tion with optional hardware flow control (HFC) modes have the debugging/development interface enabled.

to prevent data overruns. If HFC mode is enabled on a

given port, the system uses two extra pins to implement Additional Documentation and Technical Support

the industry standard request to send (RTS) and clear to Designers must have the following documents to use all

send (CTS) flow control signaling. Each UART is individu- the features of this device:

ally programmable. ●● This data sheet, which contains electrical/timing spec-

●● 2-wire interface or 4-wire interface with flow control ifications, package information, and pin descriptions

●● 32-byte send/receive FIFO ●● The corresponding revision-specific errata sheet

●● Full-duplex operation for asynchronous data transfers ●● The corresponding user guide, which contains

●● Interrupts available for frame error, parity error, CTS, detailed information and programming guidelines for

Rx FIFO overrun and FIFO full/partially full conditions core features and peripherals

●● Automatic parity and frame error detection Technical support is available at https://support.maxi-

mintegrated.com/micro.

●● Independent baud-rate generator

●● Programmable 9th bit parity support

●● Multidrop support

●● Start/stop bit support

www.maximintegrated.com Maxim Integrated │ 21

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Applications Information

Table 3. GPIO and Alternate Function Matrix, 16 WLP

GPIO ALTERNATE FUNCTION 1 ALTERNATE FUNCTION 2 ALTERNATE FUNCTION 3

P0.0 SWDIO** SPI1_MISO (I2S_SDI)† UART1_TX**

P0.1 SWDCLK** SPI1_MOSI (I2S_SDO)† UART1_RX**

P0.2 I2C1_SCL SPI1_SCK (I2S_BCLK)† 32KCAL

P0.3 I2C1_SDA SPI1_SS0 (I2S_LRCLK)† TMR0

P0.4 SPI0_MISO UART0_TX —

P0.5 SPI0_MOSI UART0_RX —

P0.6 SPI0_SCK UART0_CTS UART1_TX**

P0.7 SPI0_SS0 UART0_RTS UART1_RX**

P0.8 I2C0_SCL SWDIO** —

P0.9 I2C0_SDA SWDCLK** —

P0.10* — — —

P0.11* — — —

P0.12* — — —

P0.13* — — —

*GPIO not pinned out.

**This signal can be mapped to more than one GPIO, but there is only one instance of this peripheral.

†I2S_BCLK, I2S_LRCLK, I2S_SDI, I2S_SDO when enabled.

Table 4. GPIO and Alternate Function Matrix, 20 TQFN and 24 TQFN

GPIO ALTERNATE FUNCTION 1 ALTERNATE FUNCTION 2 ALTERNATE FUNCTION 3

P0.0 SWDIO** SPI1_MISO (I2S_SDI)†** UART1_TX**

P0.1 SWDCLK** SPI1_MOSI (I2S_SDO)†** UART1_RX**

P0.2 I2C1_SCL SPI1_SCK (I2S_BCLK)†** 32KCAL

P0.3 I2C1_SDA SPI1_SS0 (I2S_LRCLK)†** TMR0

P0.4 SPI0_MISO UART0_TX —

P0.5 SPI0_MOSI UART0_RX —

P0.6 SPI0A_SCK UART0_CTS UART1_TX**

P0.7 SPI0A_SS0 UART0_RTS UART1_RX**

P0.8 I2C0_SCL SWDIO** —

P0.9 I2C0_SDA SWDCLK** —

P0.10 SPI1_MISO (I2S_SDI)†** UART1_TX —

P0.11 SPI1_MOSI (I2S_SDO)†** UART1_RX —

P0.12 SPI1_SCK (I2S_BCLK)†** UART1_CTS —

P0.13 SPI1_SS0 (I2S_LRCLK)†** UART1_RTS —

**This signal can be mapped to more than one GPIO, but there is only one instance of this peripheral.

†I2S_BCLK, I2S_LRCLK, I2S_SDI, I2S_SDO when enabled.

www.maximintegrated.com Maxim Integrated │ 22

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Typical Application Circuit

VBAT

1.71V TO 3.63V

STANDARD 1µF

CELL

VBAT

VDD RSTN

100nF

NOISE

4.7kΩ 4.7kΩ SPI1_MOSI 10Ω SNUBBER

SPI1_MISO

I2C1_SCL SPI1_CLK

I2C1_SDA SPI1_SS0

UART0_TX

SWDIO

UART0_RX

SWDCLK

UART0_CTS

UART0_RTS

P0.8

P0.9

VCORE

1.0µF

VSS 32KIN 32KOUT

32.768kHz, 6pF

www.maximintegrated.com Maxim Integrated │ 23

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

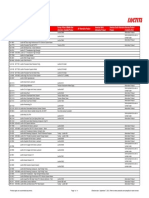

Ordering Information

BOOT

PART FLASH (KB) SRAM (KB) PIN-PACKAGE

LOADER

MAX32660GWE+ 256 96 No 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GWE+T 256 96 No 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GTP+ 256 96 No 20 TQFN-EP (4mm x 4mm x 0.75mm, 0.5mm pitch)

MAX32660GTP+T 256 96 No 20 TQFN-EP (4mm x 4mm x 0.75mm, 0.5mm pitch)

MAX32660GTG+ 256 96 No 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.4mm pitch)

MAX32660GTG+T 256 96 No 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.4mm pitch)

MAX32660GWEBL+* 256 96 Yes 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GWEBL+T* 256 96 Yes 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GTGBL+* 256 96 Yes 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.5mm pitch)

MAX32660GTGBL+T* 256 96 Yes 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.5mm pitch)

MAX32660GWELA+* 128 64 No 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GWELA+T* 128 64 No 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GTGLA+* 128 64 No 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.5mm pitch)

MAX32660GTGLA+T* 128 64 No 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.5mm pitch)

MAX32660GWELB+* 64 32 No 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GWELB+T* 64 32 No 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch)

MAX32660GTGLB+* 64 32 No 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.5mm pitch)

MAX32660GTGLB+T* 64 32 No 24 TQFN-EP (3mm x 3mm x 0.75mm, 0.5mm pitch)

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel. Full reel.

*Future product—contact factory for availability.

www.maximintegrated.com Maxim Integrated │ 24

MAX32660 Ultra-Low Power Arm Cortex-M4

with FPU-Based Microcontroller

for Wearable and IoT Sensors

Revision History

REVISION REVISION PAGES

DESCRIPTION

NUMBER DATE CHANGED

0 1/18 Initial release —

Updated General Description, Applications, Benefits and Features, Absolute Maximum

1, 3, 8, 15,

1 4/18 Ratings, Package Information, Electrical Characteristics table, Pin Configurations, Pin

16, 22–24

Descriptions, Table 4 title, Ordering Information, and added Typical Application Circuit

Updated Simplified Block Diagram, Electrical Characteristics table, Figure 1, Figure 2, 2, 4–6, 8–10,

2 6/18

Figure 3, Clocking Scheme section, Figure 6, and Ordering Information table 11, 17, 24

3 8/18 Updated Ordering Information 24

4 8/18 Updated Ordering Information 24

For pricing, delivery, and ordering information, please visit Maxim Integrated’s online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses

are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits)

shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc. © 2018 Maxim Integrated Products, Inc. │ 25

You might also like

- MAX32660 DatasheetDocument25 pagesMAX32660 DatasheetSteve CooperNo ratings yet

- MAX32520Document29 pagesMAX32520duval fortesNo ratings yet

- MAX32665-MAX32668 Low-Power Arm Cortex-M4 With FPU-Based Microcontroller With Bluetooth 5 For WearablesDocument46 pagesMAX32665-MAX32668 Low-Power Arm Cortex-M4 With FPU-Based Microcontroller With Bluetooth 5 For WearablesmstrkoskiNo ratings yet

- Esp32 BluetothDocument70 pagesEsp32 Bluetothcristal cristalNo ratings yet

- Slas 396 DDocument66 pagesSlas 396 DAmin KhanNo ratings yet

- Familia Mcu FlashDocument356 pagesFamilia Mcu FlashsergioNo ratings yet

- ESP32 DatasheetDocument70 pagesESP32 DatasheetaaiioNo ratings yet

- MAX32625-MAX32626 DatasheetDocument28 pagesMAX32625-MAX32626 DatasheetSteve CooperNo ratings yet

- STM32L5 Series: Excellence in Ultra-Low Power With More SecurityDocument2 pagesSTM32L5 Series: Excellence in Ultra-Low Power With More SecurityMastan ValiNo ratings yet

- MSP430F22x2 Automotive Mixed-Signal Microcontrollers: 1 FeaturesDocument78 pagesMSP430F22x2 Automotive Mixed-Signal Microcontrollers: 1 FeaturesMiljenko PolićNo ratings yet

- Stm32, The Optimal Platform Choice The Stm32 Key Benefits: 72 MHZ Cortex-M3 Cpu - Wide Selection of DevicesDocument6 pagesStm32, The Optimal Platform Choice The Stm32 Key Benefits: 72 MHZ Cortex-M3 Cpu - Wide Selection of DevicesBa VuVanNo ratings yet

- Hoja de Cálculo Sin TítuloDocument3 pagesHoja de Cálculo Sin TítuloEc ObregonNo ratings yet

- Familiariztion of Msp430 Launchpad (Repaired)Document38 pagesFamiliariztion of Msp430 Launchpad (Repaired)Aliya GNo ratings yet

- STM32F429 SeminarDocument259 pagesSTM32F429 SeminarDaniel FalcoffNo ratings yet

- Esp32-S2 Datasheet enDocument54 pagesEsp32-S2 Datasheet enkaeterNo ratings yet

- Video Lecture: Microprocessors MicrocontrollersDocument96 pagesVideo Lecture: Microprocessors MicrocontrollersRAVICHANDRA KILARU0% (1)

- Datasheet PDFDocument33 pagesDatasheet PDFMARWENNo ratings yet

- Datasheet PDFDocument33 pagesDatasheet PDFMARWENNo ratings yet

- At91 Arm Thumb - Based Microcontrollers AT91SAM7S256 PreliminaryDocument33 pagesAt91 Arm Thumb - Based Microcontrollers AT91SAM7S256 PreliminaryMARWENNo ratings yet

- Esp32-S2 Datasheet enDocument49 pagesEsp32-S2 Datasheet enRenato FerreiraNo ratings yet

- Esp32-S2 Datasheet enDocument51 pagesEsp32-S2 Datasheet enJYK STONENo ratings yet

- Tagmicro-Txfn: Ultra Low Power 8-Bit Microcontroller and Fractional-N RF TransmitterDocument2 pagesTagmicro-Txfn: Ultra Low Power 8-Bit Microcontroller and Fractional-N RF TransmitterVitaliyNo ratings yet

- ADuC845 7 8 - ADocument108 pagesADuC845 7 8 - Aapi-3736461No ratings yet

- Cc2652P Simplelink™ Multiprotocol 2.4 GHZ Wireless Mcu With Integrated Power AmplifierDocument77 pagesCc2652P Simplelink™ Multiprotocol 2.4 GHZ Wireless Mcu With Integrated Power AmplifiercuNo ratings yet

- Msp430intro 170625172931 PDFDocument40 pagesMsp430intro 170625172931 PDFSingam SridharNo ratings yet

- MSP432™ MCUsDocument64 pagesMSP432™ MCUsJason HouNo ratings yet

- Cypr S A0013039613 1-3004804Document79 pagesCypr S A0013039613 1-3004804jose diaz lamedaNo ratings yet

- Mixed-Signal ISP Flash MCU: Analog Peripherals - High Speed 8051 C Core - MemoryDocument214 pagesMixed-Signal ISP Flash MCU: Analog Peripherals - High Speed 8051 C Core - MemoryDikdik PribadiNo ratings yet

- Silicon Labs C805CCXXX231 GQ DataDocument146 pagesSilicon Labs C805CCXXX231 GQ DatasikeshkkNo ratings yet

- Arm STM32WB55 PDFDocument178 pagesArm STM32WB55 PDFtungNo ratings yet

- xc2287 PBDocument2 pagesxc2287 PBАндрей ОлененкоNo ratings yet

- b4 Digi Connectcore 93 DsDocument4 pagesb4 Digi Connectcore 93 Dsccuenin777No ratings yet

- STM8S Value Line 8-Bit Microcontrollers PDFDocument2 pagesSTM8S Value Line 8-Bit Microcontrollers PDFdcesentherNo ratings yet

- Max 78002Document55 pagesMax 78002duval fortesNo ratings yet

- 32-Bit Power Architecture MCU For Automotive General Purpose Applications - Chorus FamilyDocument139 pages32-Bit Power Architecture MCU For Automotive General Purpose Applications - Chorus FamilyEcus ElectronicsNo ratings yet

- Tagmicro-Tx: Ultra Low Power 8-Bit Microcontroller and RF TransmitterDocument2 pagesTagmicro-Tx: Ultra Low Power 8-Bit Microcontroller and RF TransmitterVitaliyNo ratings yet

- (SAM4S Microcontroller Family) (60001419B)Document2 pages(SAM4S Microcontroller Family) (60001419B)andrewtangNo ratings yet

- ADuCM350-Amperometric, Voltametric, and ImpedometricDocument40 pagesADuCM350-Amperometric, Voltametric, and Impedometricestraj1954No ratings yet

- STM 32 H 745 ZiDocument252 pagesSTM 32 H 745 Zisaif amriNo ratings yet

- Esp32-C3 Datasheet enDocument48 pagesEsp32-C3 Datasheet enSaul CovalNo ratings yet

- Esp32-C3 Datasheet enDocument47 pagesEsp32-C3 Datasheet enStepan BorisovichNo ratings yet

- SKEA64PB, Product Brief - Product BriefDocument14 pagesSKEA64PB, Product Brief - Product BriefMayank VyasNo ratings yet

- CYRF6936 2.4 GHZ MODEM DSMXDocument31 pagesCYRF6936 2.4 GHZ MODEM DSMXBabis BabisNo ratings yet

- JN DS JN5121 1v8Document78 pagesJN DS JN5121 1v8table9No ratings yet

- Amd Au1100 400mbd BF DatasheetDocument2 pagesAmd Au1100 400mbd BF DatasheetFirdaus HanipahNo ratings yet

- MSP 430 G 2433Document89 pagesMSP 430 G 2433Danny MendozaNo ratings yet

- MSP430G2x33, MSP430G2x03 Mixed-Signal Microcontrollers: 1 Device OverviewDocument94 pagesMSP430G2x33, MSP430G2x03 Mixed-Signal Microcontrollers: 1 Device OverviewcafosokNo ratings yet

- PIC24F16KL402 Family Data Sheet DS30001037DDocument264 pagesPIC24F16KL402 Family Data Sheet DS30001037DDaniNo ratings yet

- ADuC845 847 848Document108 pagesADuC845 847 848Tim BeckNo ratings yet

- stm32wb55vg PDFDocument183 pagesstm32wb55vg PDFShivbraham Singh RajawatNo ratings yet

- STM 32 WB 10 CCDocument112 pagesSTM 32 WB 10 CCbimaagus22No ratings yet

- Cc2674R10 Simplelink™ High-Performance Multiprotocol 2.4-Ghz Wireless McuDocument69 pagesCc2674R10 Simplelink™ High-Performance Multiprotocol 2.4-Ghz Wireless Mcujainil shahNo ratings yet

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q064A FeaturesDocument81 pagesMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q064A FeaturesalfredosnNo ratings yet

- V850 Family: Product Letter DescriptionDocument4 pagesV850 Family: Product Letter DescriptionMaiChiVuNo ratings yet

- MCF5253FSDocument2 pagesMCF5253FSAdrian GarciaNo ratings yet

- En flstm32f469Document2 pagesEn flstm32f469Yul GoncalvesNo ratings yet

- MSP 430 FR 2533Document108 pagesMSP 430 FR 2533tunaNo ratings yet

- Integrated Device Technology 9LPRS477CKLFT DatasheetDocument26 pagesIntegrated Device Technology 9LPRS477CKLFT DatasheetQuaddroNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Cir CuloDocument1 pageCir CuloZalNo ratings yet

- WP Cable LoadingDocument15 pagesWP Cable LoadingZalNo ratings yet

- Cort Ev Ultimo HojeDocument90 pagesCort Ev Ultimo HojeZalNo ratings yet

- Pocket 1Document127 pagesPocket 1ZalNo ratings yet

- Pocket 1Document127 pagesPocket 1ZalNo ratings yet

- Pocket 3Document72 pagesPocket 3ZalNo ratings yet

- CortevDocument5 pagesCortevZalNo ratings yet

- Cort Ev Ultimo HojeDocument90 pagesCort Ev Ultimo HojeZalNo ratings yet

- Profile 2Document15 pagesProfile 2ZalNo ratings yet

- Cort Ev Ultimo HojeDocument5 pagesCort Ev Ultimo HojeZalNo ratings yet

- Poocket 7Document64 pagesPoocket 7ZalNo ratings yet

- Flasher stm32 PDFDocument3 pagesFlasher stm32 PDFZalNo ratings yet

- Test 4Document5 pagesTest 4ZalNo ratings yet

- Pocket 1Document72 pagesPocket 1ZalNo ratings yet

- Pocket 1Document72 pagesPocket 1ZalNo ratings yet

- Introduction To MicrocontrollersDocument1 pageIntroduction To MicrocontrollersZalNo ratings yet

- TesteDocument5 pagesTesteZalNo ratings yet

- UVTrainingGuide PDFDocument6 pagesUVTrainingGuide PDFZalNo ratings yet

- 365b ManualDocument83 pages365b ManualZalNo ratings yet

- Les Paul Neck RadiusDocument1 pageLes Paul Neck RadiusZalNo ratings yet

- STM32F101x4 STM32F101x6Document87 pagesSTM32F101x4 STM32F101x6ZalNo ratings yet

- Audio Transformers ChapterDocument30 pagesAudio Transformers Chapterforing100% (4)

- Mouser Passive ComponentsDocument1 pageMouser Passive ComponentsZalNo ratings yet

- Mach3 USB interface board manualDocument13 pagesMach3 USB interface board manualZal80% (5)

- New 2012 Catalogue of PickupsDocument10 pagesNew 2012 Catalogue of PickupsZalNo ratings yet

- FileDocument13 pagesFileZalNo ratings yet

- Iydiydoydhdits S Jfs Fs Fajrajrsta S Jfzjtsjtsjtsitsjtajtsjt Ts Jrs Ta Jts Jts Jts Jtajtajts Js S JraDocument1 pageIydiydoydhdits S Jfs Fs Fajrajrsta S Jfzjtsjtsjtsitsjtajtsjt Ts Jrs Ta Jts Jts Jts Jtajtajts Js S JraZalNo ratings yet

- Guerrilla Guide To CNC Machining, Mold Making, and Resin CastingDocument15 pagesGuerrilla Guide To CNC Machining, Mold Making, and Resin CastingZalNo ratings yet

- Tabela TaxasDocument5 pagesTabela TaxasZalNo ratings yet

- Mahmud Hossain JewelDocument64 pagesMahmud Hossain JewelSULEIMAN USMAN MUHAMMADNo ratings yet

- Fire Alarm SynopsisDocument3 pagesFire Alarm SynopsisNANDITA NANDINo ratings yet

- Computer Hardware BookDocument336 pagesComputer Hardware BookbharathydglNo ratings yet

- 5 W, Two-Channel Power Amplifier With Very Few External PartsDocument21 pages5 W, Two-Channel Power Amplifier With Very Few External PartsSavuDanielFNo ratings yet

- Balun Basics Primer - A Tutorial On Baluns, Balun Transformers, Magic-Ts, and 180° HybridsDocument8 pagesBalun Basics Primer - A Tutorial On Baluns, Balun Transformers, Magic-Ts, and 180° HybridsArun KumarNo ratings yet

- Current Mirror Circuit - Wilson and Widlar Current Mirroring TechniquesDocument13 pagesCurrent Mirror Circuit - Wilson and Widlar Current Mirroring TechniquesGanga PandeyNo ratings yet

- 24lc21 KullanimiDocument8 pages24lc21 KullanimiskiziltoprakNo ratings yet

- Controlling Relays With PC's Parallel PortDocument2 pagesControlling Relays With PC's Parallel Porteka nuryantoNo ratings yet

- Laser Safety ReportDocument27 pagesLaser Safety ReportGabriel Jose SabulaoNo ratings yet

- Agenda For Today: - Overview of FpldsDocument52 pagesAgenda For Today: - Overview of FpldsvmspraneethNo ratings yet

- S3F94xx BatteryCharger An REV000 060109-0Document40 pagesS3F94xx BatteryCharger An REV000 060109-0Jack ChanNo ratings yet

- Non-Isolated Buck Offline LED Driver Description FeaturesDocument2 pagesNon-Isolated Buck Offline LED Driver Description FeaturesAlberto100% (1)

- Mask Design LayoutDocument1 pageMask Design Layoutapi-121385755No ratings yet

- Gp1ua26xk - Ir Detecting Unit Remote ControlDocument2 pagesGp1ua26xk - Ir Detecting Unit Remote ControlElias ChavezNo ratings yet

- FAN6921MR Integrated Critical Mode PFC and Quasi-Resonant Current Mode PWM ControllerDocument25 pagesFAN6921MR Integrated Critical Mode PFC and Quasi-Resonant Current Mode PWM ControllereduardskNo ratings yet

- EEPROM 24LC256 - Microchip PDFDocument28 pagesEEPROM 24LC256 - Microchip PDFValdir DerlannNo ratings yet

- Agilent Impedance Measurement HandbookDocument134 pagesAgilent Impedance Measurement HandbooksinetemporeNo ratings yet

- An All-Digital PLL Clock Multiplier: M PD OSC FilterDocument4 pagesAn All-Digital PLL Clock Multiplier: M PD OSC FilterArun JyothiNo ratings yet

- Load Pull Overview - Muray MicrowaveDocument97 pagesLoad Pull Overview - Muray Microwaveravi010582No ratings yet

- Dielectric Material'sDocument9 pagesDielectric Material'sRaza AliNo ratings yet

- Loctite PDFDocument4 pagesLoctite PDFOsvaldo Cansigno PeláezNo ratings yet

- FS FSQ510Document15 pagesFS FSQ510Slobodan Boba JovanovićNo ratings yet

- Second Generation Current ConveyorDocument4 pagesSecond Generation Current Conveyormuhammad_andinovaNo ratings yet

- VLSI Companies ChennaiDocument2 pagesVLSI Companies ChennaiSubbulakshmi VenkatachalamNo ratings yet

- Design and Experiments of A High Conversion Efficiency Recgenna at 5.8 GHZDocument8 pagesDesign and Experiments of A High Conversion Efficiency Recgenna at 5.8 GHZaqib qayyumNo ratings yet

- Axial Leaded - 600W P6KE SeriesDocument5 pagesAxial Leaded - 600W P6KE SeriesSamrul YoNo ratings yet

- 16 MM XA Series & 22 MM HW, XW Series SEMI S2 Compliant EMODocument4 pages16 MM XA Series & 22 MM HW, XW Series SEMI S2 Compliant EMOMuhamad PriyatnaNo ratings yet

- Electrical Transmission and Distribution System and DesignDocument67 pagesElectrical Transmission and Distribution System and DesignAdrian Toribio100% (3)

- Mbed Pin IO Tutorial PDFDocument5 pagesMbed Pin IO Tutorial PDFIanNo ratings yet

- Current Electricity: Key ConceptsDocument19 pagesCurrent Electricity: Key Concepts68 Kumuda MathapatiNo ratings yet