Professional Documents

Culture Documents

DICA Lab Manual PDF

Uploaded by

ssptc MagazineOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DICA Lab Manual PDF

Uploaded by

ssptc MagazineCopyright:

Available Formats

Digital IC Applications Lab Manual

Mahaveer Institute of Science & Technology

Vysapuri, Bandlaguda, post:Keshavgiri, Hyderabad-500005

(Approved by AICTE, Affiliated to JNTUH)

(A Constitute college of Mahaveer Educational society)

EAMCET CODE : MIST, JNTUH College code:E3

DIGITAL IC APPLICATIONS LABORATORY MANUAL

ECE III Year I SEMESTER

DEPARTMENT OF ELECTRONICS & COMMUNICATION

ENGINEERING

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

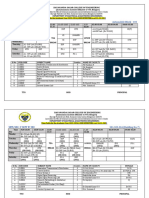

List of Experiments

Design and Implementation of:

1. Design a 16 x 4 priority encoder using two 8 x 3 priority encoder

2.Design a 16 bit comparator using 4 bit Comparators.

3.Design a model to 53 counter using two decade counters

4.Design a 450 KHz clock using NAND / NOR gates.

5. Design a 4 bit pseudo random sequence generator using 4 – bit ring counter.

6.Design a 16 x 1 multiplexer using 8 x 1 multiplexer.

7.Design a 16 bit Adder / Subtractor using 4 – bit Adder / Subtractor IC’s.

8.Plot the transform Characteristics of 74H, LS, HS series IC’s.

9. Design a 4 – bit Gray to Binary and Binary to Gray Converter.

10. Designa two Digit 7 segment display unit using this display the Mod counter output

of experiment 3.

11.Design an 8 bit parallel load and serial out shift register using two 4 bit shift register.

12.Design an 8 bit Serial in and serial out shift register using two 4 bit shift register.

13..Design a Ring counter and Twisted ring counter using a 4-bit shift register.

14.Design a 4 digit hex counter using synchronous one digit hex counters.

15. Design a 4 digit hex counter using Asynchronous one digit hex counters

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 1

16x4 PRIORITY ENCODER USING 8x3 PRIORITY ENCODER

Aim:- To study and implement 16x4 priority encoder using 8x3 priority encoder

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

A priority encoder is a circuit or algorithm that compresses multiple binary inputs into a

smaller number of outputs. The output of a priority encoder is the binary representation of the

original number starting from zero of the most significant input bit. In this experiment we are

going to build the 16x4 using 8x3. The IC number used in the experiment is 74LS148. This IC is

8x3 priority encoder using two ice’s in cascading we building the 16x4 priority encoder.

Pin-diagram (74ls148):-

Figure (1)74ls148 pin configuration

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Internal circuit diagram:-

Figure (2) internal logic diagram of IC

Procedure:-

1) The power supply is given in the inside so no need to connect the externally.

2) Connect the logic inputs i1-i15 using patch chords to the logic switches.

3) Connect the outputs to the led’s.

4) Now switch on the trainer kit you will observe the led indication.

5) Verify the truth table given below.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

TRUTH TABLE:-

Inputs Outputs

EI 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Y3 Y2 Y1 Y0

L L L L L L L L L L L L L L L L L L L L

L H L L L L L L L L L L L L L L L L L H

L H H L L L L L L L L L L L L L L L H L

L H H H L L L L L L L L L L L L L L H H

L H H H H L L L L L L L L L L L L H L L

L H H H H H L L L L L L L L L L L H L H

L H H H H H H L L L L L L L L L L H H L

L H H H H H H H L L L L L L L L L H H H

L H H H H H H H H L L L L L L L H L L L

L H H H H H H H H H L L L L L L H L L H

L H H H H H H H H H H L L L L L H L H L

L H H H H H H H H H H H L L L L H L H H

L H H H H H H H H H H H H L L L H H L L

L H H H H H H H H H H H H H L L H H L H

L H H H H H H H H H H H H H H L H H H L

L H H H H H H H H H H H H H H H H H H H

Where H=logic ‘1’

L=logic ‘0’

Result:- Hence the 16x4 priority encoder is verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 2

16 BIT COMPARATOR USING 4 BIT COMPARATOR

Aim:- To study and implement 16bit comparator using 4bitcomparator.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

These 4-bit magnitude comparators perform comparison of straight binary or BCD codes.

Three fully-decoded decisions about two, 4-bit words (A, B) are made and are externally

available at three outputs. These devices are fully expandable to any number of bits without

external gates. Words of greater length may be compared by connecting comparators in cascade.

The A > B, A < B, and A = B outputs of a stage handling less-significant bits are connected to

the corresponding inputs of the next stage handling more-significant bits. The stage handling the

least significant bits must have a high-level voltage applied to the A = B input. The cascading

path is implemented with only a two-gate-level delay to reduce overall comparison times for

long words. The 4bit comparator should be cascaded to build the 16bit comparator. The IC

74ls85 can be performs the 4bit comparator. This IC is having the A0, A1, A2, A3 and B0, B1,

B2, B3 are the inputs the result will be shown at the output indications are A=B, A>B and A<B.

These signals are cascaded for making the 16bit comparator.

Pin diagram (74ls85):-

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Cascaded:-

Figure (1) cascaded 4bit comparators to construct the 16bit comparator

Internal logic diagram:-

Figure (2) internal logic diagram of IC 74ls85

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure:-

1) Connect the A0-A15 to the logic switches using the patch chords.

2) Connect the B0-B15 to the logic switches using the patch chords.

3) Connect the A<B, A=B and A>B to the output indication led’s given right side.

4) Now switch on the trainer kit you will find the led indication there.

5) Now apply the logic inputs

Example 1: A0-A15=0000 0000 0000

0000 B0-B15=0000 0000

0000 0000

The result is A=B

Example 2: A0-A15=0000 0000 0000

1111 B0-B15=0000 0000

0000 0000

The result is A>B

Example 3: A0-A15=0000 0000 0000

0000 B0-B15=0000 1111

0000 0000

The result is A<B

6) Verify the truth table.

Truth table:-

Result: - Hence the 16bit comparator is constructed and verified the output.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 3

MODULO N COUNTER USING DECADE COUNTER

Aim: - To study and implement 53 Mod counter using two decade counters.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

The decade counter, which divides input by 10 counter and provides BCD output 0 to 9:

this is also called as decimal counter. This counter comprises of a divide by 2’ and divide

by 5’ counters. To use as decade we have to cascade divide by 2’ and divide by 5. Output

Q0 Q3 are BCD outputs, inputs A and B are clock inputs to the counter, divide by 2’and

divide by 5’ counters respectively. Ro1 and R02 are the reset inputs, when these are

activated counter go to 0000.So1 and S02 are the set inputs to the counter, when these

inputs are activated counter output go to 1001.casecading of the two decade counters we

are performing the 53 counter.

Pin-diagram (74LS90):-

Figure (1) Pin-diagram 74LS90

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Circuit diagram:-

Figure (2) 53 counter circuit

The above circuit consisting of two decade counters and the 1Hz clock generation

block is given for connecting to the clock input of the circuit. The operation of the circuit

is connecting the two decade counter in a cascade manner. The below decade counter is

counting the 0000 to 1001 it means one decade count. When it is completed the one

decade count one clock is given to the first decade counter then the first decade counter is

incremented by one count this process is repeated for the 53 counts. When is reached to

the 53 counts it will be stopped or otherwise it reset. In this circuit the first decade is

divided by the so that it can count up to five and second one is counts the decade.

Procedure:-

1) Connect the clock output (1Hz) to the input of the decade counter.

2) Connect the first ic ouputs i.e Q0, Q1, Q2 and Q3 to the led’s.

3) Connect the second ic ouputs i.e Q0, Q1, Q2 and Q3 to the led’s after connected the

first ic.

4) Now short the first ic R91, R92 using a patch chord connect these shorted line to the

logic switch.

5) Now short the second ic R91, R92 using a patch chord connect these shorted line to

the logic switch.

6) Connect the power chord to the AC supply. Now switch on the trainer kit.

7) Using logic switches reset the circuit to the zero position.

8) Now the counter will start the counting. Observe the output on led’s.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Truth table:-

INPUTS OUTPUTS

R92 R91 Qd Qc Qb Qa

X L L L L L

H H H L L H

L L COUNT

Result:- Hence the 53 counter using two decade counter is implemented and verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 4

450 KHZ CLOCK GENERATOR USING NAND/NOR GATES

Aim: - To study and implement 450 kHz clock generator using NAND/NOR gates.

Apparatus:-

1) Trainer kit

2) Patch chords

3) CRO

4) Power supply

Theory:-

A clock generator is a circuit that produces a timing signal (known as a clock signal and

behaves as such) for use in synchronizing a circuit's operation. The signal can range from a

simple symmetrical square wave to more complex arrangements. The basic parts that all clock

generators share are a resonant circuit and an amplifier. Since all logic operations in a

synchronous machine occur in synchronism with a clock, the system clock becomes the basic

timing unit. The system clock must provide a periodic wave forms that can be used as a

synchronous signal. The square waveform is a typical clock waveform used in a digital system.

The clock defines a basic timing interval during which logic operation must be

performed. This basic timing interval is defined as a clock cycle time and is equal to one period

of the clock waveform. Thus all logic elements, flip-flops, gates, and so on must complete their

transition in less than one clock cycle time. In this experiment to generating the clock we are

using the NAND and NOR gates using these gates we generating the 450KHZ clock signal.

Circuit diagram:-

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure:-

1) Connect the power chord to the mains power supply

2) Turn on the trainer kit you can observe the led indication on the kit.

3) Now connect the CRO probe in channel ‘1’ to the NAND gate and connect

the positive to the output of the circuit and negative to the ground.

4) Observe the waveform on the CRO and note down the waveform time

period and amplitude of the signal.

5) Plot the graph for the above readings.

6) Do the above steps for the same NOR gate also.

Output waveforms:-

NAND

A

m O/P

p

l

i

t

u

d NOR

e

O/P

Frequency

Result:- Hence the generation of the 450Khz clock is verified using the NAND and NOR

gates.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 5

4-BIT PSEUDO RANDOM SEQUECNE GENERATOR USING 4 BIT RING COUNTER

AIM:

To study & verify the 4-bit pseduo random sequence generator

THEORY:

Timing signals that control the sequence of operations are essential in digital computer

systems. The counter which is used for their basic timing is known as a ring counter.

A ring counter is a circular shift register with only one flip flop being set at any particular

time and all other flip flops are cleared. The single bit is shifted from one flip flop to

other to produce the sequence of timing signals

Let us consider a 4 bit ring counter and examine how it utilizes one flip-flop for each

state in its sequence. The logic diagram for 4 bit ring counter is the ring counter

sequences for 4 bits.

In this logic diagram, notice that the output Q and Q of each flip-flop are connected to the

next flip-flop and the output of the fourth flip flop are connected to the first flip flop.

The clock input is applied simultaneously to all flip flops.

CIRCUIT DIAGRAM

OPERATION:

Initially a logic one is preset in to the first flip flop. and the rest of flip flops are cleared.

Then the output of the counter is given by Q=Qd Qc Qb Qa.

Q =0001.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Clock Pulse No FFA FFB FFC FFD

0 1 0 0 0

1 0 1 0 0

2 0 0 1 0

3 0 0 0 1

4 1 0 0 0

Single bit logic 1 is shifted with every clock pulse and circulates back from the fourth flip

flop to the first flip flop. Note that each flip flop is in the 1 state once for every four clock

pluses.

From above table we can notice that the 1 is always retained in the 4 counter and simply

shifted “around the ring advancing one stage for each clock pulse.

The basic operation of this counter is also illustrated in the timing diagram shown in

figure.

Rotational Movement of a 4-BIT SEDUO RANDOM SEQUECN GENERATOR Ring

Counter

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

TIMING DIAGRAM:

Result:- Hence the generation of the pseudo random sequence is generated using 4 bit

ring counter.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 6

16x1 MULTIPLEXER USING 8x1 MULTIPLEXER

Aim:- To study and implement 16x1 multiplexer using 8x1 multiplexer

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

A multiplexer (MUX) is a device that allows digital information from several sources to

be routed onto a single line for transmission over that line to a common destination. The basic

multiplexer has several data-inputs lines and a single output line. It also has data-select inputs,

which permit digital data on any one of the inputs to be switched to the output line, multiplexers

are also known as data selectors. Here the IC 74ls151 is an 8x1 multiplexer using this

multiplexer we are constructing the 16x1 multiplexer.

Pin configuration (74LS151):-

Figure (1) pin-diagram of 74ls151

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Cascaded diagram (74LS151):-

Figure (2) 16x1 multiplexer

Procedure:-

1) Connect the inputs i0-i15 to the logic switches. Here the i0-i15 is the input data lines.

2) Connect the selection lines S0, S1, S2 and S3 to the logic switches given below.

3) Connect the out puts Y, Y to the led’s given in the right side on the kit.

4) Now switch on the trainer kit you will find the led indication on the kit.

5) Now do the experiment. Based on the selection lines the input data will be selected.

6) Verify the truth table

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Truth table:-

Selection Inputs O/P

lines

S

3 S2 S1 S0 I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 14 115 Y Y

L L L L L X X X X X X X X X X X X X X X L H

L L L L H X X X X X X X X X X X X X X X H L

L L L H X L X X X X X X X X X X X X X X L H

L L L H X H X X X X X X X X X X X X X X H L

L L H L X X L X X X X X X X X X X X X X L H

L L H L X X H X X X X X X X X X X X X X H L

L L H H X X X L X X X X X X X X X X X X L H

L L H H X X X H X X X X X X X X X X X X H L

L H L L X X X X L X X X X X X X X X X X L H

L H L L X X X X H X X X X X X X X X X X H L

L H L H X X X X X L X X X X X X X X X X L H

L H L H X X X X X H X X X X X X X X X X H L

L H H L X X X X X X L X X X X X X X X X L H

L H H L X X X X X X H X X X X X X X X X H L

L H H H X X X X X X X L X X X X X X X X L H

L H H H X X X X X X X H X X X X X X X X H L

H L L L X X X X X X X X L X X X X X X X L H

H L L L X X X X X X X X H X X X X X X X H L

H L L H X X X X X X X X X L X X X X X X L H

H L L H X X X X X X X X X H X X X X X X H L

H L H L X X X X X X X X X X L X X X X X L H

H L H L X X X X X X X X X X H X X X X X H L

H L H H X X X X X X X X X X X L X X X X L H

H L H H X X X X X X X X X X X H X X X X H L

H H L L X X X X X X X X X X X X L X X X L H

H H L L X X X X X X X X X X X X H X X X H L

H H L H X X X X X X X X X X X X X L X X L H

H H L H X X X X X X X X X X X X X H X X H L

H H H L X X X X X X X X X X X X X X L X L H

H H H L X X X X X X X X X X X X X X H X H L

H H H H X X X X X X X X X X X X X X X L L H

H H H H X X X X X X X X X X X X X X X H H L

Result :- Hence the 16x1 multiplexer is verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 7

16 BIT ADDER/SUBTRACTOR USING 4 BIT

ADDER/SUBTRACTOR

Aim:- To study and implement 16 bit adder/subtractor using 4 bit adder/subtractor

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

Adders are important not only in computers but in many types of digital systems in which

numerical data are processed. An understanding of the basic adder operation is fundamental to

the study of digital system. In this experiment using the 4 bit add/sub constructing the 16 bit

add/sub. The IC number for 4 bit add/sub is 74LS83A. These full adders perform the addition of

two 4-bit binary numbers. The sum (∑) outputs are provided for each bit and the resultant carry

(C4) is obtained from the fourth bit. These adders feature full internal look ahead across all four

bits. This provides the system designer with partial look ahead performance at the economy and

reduced package count of a ripple-carry implementation. The adder logic, including the carry, is

implemented in its true form meaning that the end-around carry can be accomplished without the

need for logic or level inversion. The cascading of the 4 bit adder we can form the 16 bit adder.

The carry should be forwarded to another IC.

Pin configuration:-

Figure (1) pin diagram of 74LS83A

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Logic circuit (74LS83A):-

Circuit diagram:-

Figure (2) cascading of 4 bit add/sub

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure:-

Addition:-

1) Connect the A0-A15 to the logic switches provided on the trainer kit.

2) Connect the B0-B15 to the logic switches provided on the trainer kit.

3) Connect the outputs to the led indicators.

4) Connect the mode switch to the logic switches.

5) Now put the mode switch in logic ‘0’ it is indicated that addition operation performing.

6) Now give the input data using the A0-A15 and B0-B15 logic

switches. Ex:-

Input data A0-A15 = 0000 0000 0000 1010 Input

data B0-B15 = 0000 0000 0000 0101

output 0000 0000 0000 1111

Subtraction:-

1) Connect the A0-A15 to the logic switches provided on the trainer kit.

2) Connect the B0-B15 to the logic switches provided on the trainer kit.

3) Connect the outputs to the led indicators.

4) Connect the mode switch to the logic switches.

5) Now put the mode switch in logic ‘1’ it is indicated that Subtraction operation

performing.

6) Now give the input data using the A0-A15 and B0-B15 logic switches.

7) To perform the subtraction operation we 1’s compliment the data of the ‘B’ input.

8) Now Add two data’s A and B when u get the result add ‘1’ to the result data.

Ex:-

Input data A0-A15 = 0000 0000 0000 1010

Input data B0-B15 = 0000 0000 0000 0101

1’s compliment i/p Bdata 1111 1111 1111 1010

9) Now add the data input A and 1’s Complimented data B

11 1 1 1 1 1 1 1 1 1 1 1

Input data A0-A15= 0000 0000 0000 1010

1’s compliment i/p Bdata 1111 1111 1111 1010

Output data 1 0000 0000 0000 0100

Carry bit

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

10) Now add the ‘1’ to the result data

1 0000 0000 0000 0100

1

Final o/p 1 0000 0000 0000 0101

11) You can perform with different data’s.

Result :- Hence the 16 bit addition and subtraction is verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 8

Transfer Characteristics and Delay Time Estimation of 74H,LS,HS series

Aim:- To study Transfer Characteristics and Delay Time Estimation of 74H,LS,HS series

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

Voltage Transfer Characteristics and As Inverter :

The static voltage transfer characteristic of a logic gate is simply a plot of the gate output voltage

VOUT versus the gate input voltage VIN. We can mathematically describe the transfer

characteristic as VOUT = f (VIN). We use the word static to describe the transfer characteristic

because it represents behavior in response to slowly changing signals so that dynamic effects

such as the delaying of the signal from gate input to gate output are avoided in measurements.

Figure 1-(a) shows an ideal static transfer characteristic for an inverter with input VIN,output

VOUT and power supply voltage VCC. What can we learn from a static transfer characteristic

that is useful in characterizing gate operation? In order to answer this question, we need to

define some terminology. First, we will consider the operating points for the inverter. These

points correspond to the High and Low values on the outputs of the inverter. Since the output

voltage depends on the input voltage, to find the value of the High operating point for an

inverter output, the value of the Low operating point for the same inverter needs to be applied to

its input.

Likewise, to find the value of the Low operating point, the value of the High operating point

needs to be applied. This requires that we know the values we are trying to determine! By

Analytically using feedback, we can combine the transfer characteristic

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Transfer Characteristic and Operating Points

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Figure 2

This is done by connecting two inverters in a loop as shown in Figure 1(b). For the two inverters,

we note that VIN2 = VOUT1 and VIN1 = VOUT2. Since both of the inverters have the same

transfer characteristic, we take the transfer characteristic of inverter 2 and mirror it about the

VOUT = VIN line so that its VIN axis lies coincident with the VOUT axis of the transfer

characteristic for inverter 1 as shown in Figure. 1(b); then the VIN axis of gate 1 also coincides

with the VOUT axis of gate 2. By this mirroring operation, the relationships given in Figure 1(b)

are satisfied on the axes of the plot. Because of the voltage equalities, the only points where both

static transfer characteristics can be satisfied on this plot are where they intersect. These

intersection points are (VIN1 = 0.15V, VOUT1= 4.05V), (VIN1 = 1.50V, VOUT1 = 1.50V), and

(VIN1 = 4.05V, VOUT1 = 0.15V); these operating points are marked with OP (numerical

values are taken for example). A small change in VIN1 from 1.5V will cause departure fromthe

(VIN1 = 1.5V, VOUT1 = 1.5V) point toward one of the other two points. Thus, this point is

unstable, will not persist, and is of little interest. Small departures from the other two operating

points, however, are reversible and with the appropriate change in VIN1 will result in a return to

those points. These are stable operating points for the inverters. They define the voltage values

that Correspond to High and Low on inputs and outputs of this particular inverter. Since we are

using Positive logic, High corresponds to 1 and Low corresponds to 0. Thus for the given

inverter, the voltage Values for 0 and 1 are 0.15V and 4.05V, respectively. For VOUT, the Low

value is Voutput LOW,

Denoted VOL, and the High value, V output high, denoted VOH. So, for this inverter, VOL is

0.15V and VOH is 4.05V. Finally, since the Low value on the input produces a High value on

the output and vice-versa, an inversion of the voltage values has occurred. For either positive or

negative logic, the inverter is also often called a Not gate since it negates the input value to

produce the output value.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Noise Margins :

Next, we define the concept of noise margins. Noise is assumed to be an effective voltage on one

or more inputs to a gate that is added to or subtracted from the voltage normally present. The

normal voltage is a stable operating point voltage. Examples of sources of noise are fluctuations

in the power Supply voltage VCC, noise generated by other digital circuits changing values

rapidly, or external Electromagnetic radiation. Intuitively, noise margins represent the amount of

effective noise voltage that can be tolerated on an input without seriously disturbing the gate

output.

Noise Margins and Logic Family Transfer Characteristics

Figure 3

In order to evaluate the noise margins, we need to define two additional voltages from the

transfer characteristic. These are the two input voltages at which dVOUT/dVIN = – 1. The lower

of these two voltages is V input Low denoted by VIL, and the higher is V input high denoted by

VIH. These voltages are chosen somewhat arbitrarily as the highest value that will act as a Low

input and the lowest value that will act as a High input. Intuitively, this makes some sense in that

if any voltage between these two voltages is applied to the input, any noise superimposed on that

voltage produces a larger noise voltage on the output, i.e., the noise voltage is amplified. This

amplification of noise is interpreted as a serious disturbance of the gate output. For the inverter

in Figure 1, VIL = 0.90V and VIH = 1.70V. With these two values plus VOH and VOL, we can

define the static voltage noise margins for a logic gate. The Lownoise margin, is NML = VIL –

VOL, and the High noise margin is NMH =VOH – VIH. Static again means that dynamic effects

are ignored and implies that the margins may not apply for high frequency noise. For the inverter

transfer characteristic in Figure 1(a), the noise margins are NML = 0.90 – 0.15 = 0.75V and

NMH = 4.05 – 1.70 = 2.35V. The intuitive implication of these values is that:

1. An input noise voltage of 0.75V added to input VOL gives an output that would still be

interpreted as a High, and

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

2. An input noise voltage of 2.35V subtracted from input value VOH gives an output that would

still be interpreted as a Low. Now we can consider fully the question: ‘‘what is logic 0 and what

is logic 1 (for positive logic)?’’ For the inverter just analyzed, a 0 on an output has value 0.15V

and a 1 on an output has a value of 4.05V. However, on the input, any voltage between GND

and 0.90V is logic 0 and anvoltage between 1.70V and VCC is logic 1. This is shown pictorially

in Figure 2(a). So we have defined the physical meaning of 0 and 1 in terms of voltages values

and ranges. In general, these physical values are specified for an entire family of gates, for many

different production lots, for different loading on the outputs, for variation in the power supply

values, and for a broad range of operating temperatures.

The results are a large number of transfer characteristics which collectively might appear as in

Figure 2(b). From this collection of curves, we find the range of values which appears on the

outputs and the range Of values that can act as valid inputs by using the same techniques as

employed for the individual characteristic in Figure 1 and take the worst case values for each

voltage. The end result, as illustrated in Figure 2(c), is the definition of logic 0 and logic 1 for the

entire family of gates. We note that in thiscase, with all of the variations taken into account, the

noise margins become smaller than for the individual gate.

Gate Delay :

Here we consider two primary gate delay parameters. In order to define these parameters, we

will use an inverter as an example. We will assume that a pulse is applied to the inverter input

VIN as shown in Figure 3. The response to this pulse on the output of the inverter is VOUT, also

shown in Figure 3. The two parameters are the high-to-low propagation time, tPHL and the low-

to-high propagation time, tPLH. We make both of these timing parameter measurements at the

50% level on the waveforms for VIN and VOUT. Formally, the 50% level is defined as the

voltage 0.5(VOH – VOL) + VOL. tPHL is the time measured from this voltage on the rising

input waveform to the same voltage on the falling output waveform. tPLH is the Time measured

from this voltage on the falling input waveform to the same voltage on the rising output

waveform.

Gate Delay Parameter Definitions

Figure 4

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Note that the subscripts on these parameters refer to the direction of change on theoutput

waveform. These two gate delay times are defined graphically on thewaveforms in Figure 4. In

addition, we define a secondary parameter, the worst casepropagation delay, tPD = Maximum

(tPHL, tPLH). It should be noted that the 50% levelfor measuring delay is not universally used.

For example, some manufacturers use1.3V as the level for delay measurement for Low Power

Schottky Transistor-Transistor Logic (LSTTL). Also, tPD does not universally represent the

maximumpropagation delay for a single gate. Some text authors use tPD to represent the average

of tPHL and tPLH; we will call this tPD (average). Returning to tPD for the case of

manyinverters of the same type, we are taking the worst case (maximum) values that canpossibly

occur for each of tPHL and tPLH and then taking the maximum of these twovalues. The end

result, tPD, is the longest delay that can ever occur for a signal changepropagating from an input

of a gate to the output of the gate, regardless of thedirection of the signal changes. These same

parameters can also be defined from agiven input to a given output of more complex integrated

circuits or parts thereof

Equipments Needed :

1. Patch cords

2. CRO

3. Signal Generator

4. Two Digital Multimeters

Circuit diagram :

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Setup for Finding Transfer Characteristics

Procedure :

1. Verify that the power supply to the Trainer model No IC -46 switched off.

2. Place the logic board at the place provided on the digital lab board.

3. Take a Note of the fact that comprises of devices from two logic families viz. TTL and

CMOS and

hence different power supplies and different input voltage facilities are given on this board and

these two classes are separated by a horizontal dotted line for clarification. Out of the two supply

input given on the board, one (5Vcc) is for TTL devices and the other one (3-15V) is for CMOS

devices.

Voltage Transfer Characteristics :

1. Make the connection as shown in the Figure above.

2. Now increase the input voltage in small steps using pot P1 and note down the

corresponding values of the output voltage.

3. Draw the graph between input voltage and the output voltage. To get a fine shape of the

transfer curve at the knees take sufficient point for your observation near the transition

region and then draw the graph between input and output voltages. This is the required voltage

transfer characteristics for a TTL inverter of 74LSXX series.

VTC Observation On CRO :

You can also directly view the complete transfer curve on your CRO screen. Followthe

following steps:

1. Switch off the power supply to the board. Then connect the input of the inverterto a triangular

wave generator and also take care of the fact that the maximumamplitude of the triangular input

should not exceed the maximum limits of thedevice under test. For TTL inverter the maximum

amplitude of the triangularinput should be kept between 4-5Volts

2. Connect this same input to the X-channel of the CRO and connect the other CRO input i.e. Y-

channel to the output of the inverter and press XY mode switch of CRO. You will observe the

complete transfer characteristics on the CRO screen. If however the view is not symmetrical or

not in expected shape then just adjust the settings of CRO to get the clear picture. Also you can

change the input triangular wave amplitude within tolerable limits to get the perfect view of the

VTC.

Finding NML And NMH :

1. After obtaining the Transfer characteristics curve on the graph paper make the mirror of this

curve by taking the VOUT axis as independent axis and VIN axis as dependent axis and then

draw the mirrored graph on the same sheet as suggested by the Figure 1.

2. These two curves will intersect each other at three points, out of which two points are the

stable points marked as OP in Figure 1.and one unstable point. These two stable points

correspond to the two stable states of the inverter. Mark the reflections of these points on

vertical axes as VOH and VOL and they denote the output high and output low of the particular

inverter.

3. Obtain the points of unity slope on the original curve and mark their reflections on the

horizontal axis as VIL and VIH which represent the maximum limit of the low input and

minimum limit of the high input (Figure 1.).

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

4. Calculate the values of High Noise Margin NMH, Low Noise Margin NML and Transition

Period using the following formulae: NMH = VOH-VIH,NML = VOL-VIL Transition Period

= VIH-VIL

Estimation of Gate Delay :

To estimate the gate delay of a TTL inverter, five inverters are connected back to back on DB27

in order to provide a delay to an input in such an amount which can be appreciated over any

20MHz oscilloscope generally available in every electronics lab. Follow the procedure given

below:

1. Apply a square wave of 100 KHz frequency and 5volt peak to peak voltage at the input of the

inverter chain i.e. at A3 and also apply this same input to the CRO X – channel. Connect the

output of the inverter chain to the CRO Y-input and run the CRO in dual mode.

2. Now get the two stable waveforms on the CRO screen for both input and output of the inverter

chain. Keep the Time/div. switch fully clockwise i.e. at the lowest value of time per division. Try

to superimpose these waveforms over each other keeping their magnitude equal.

3. Now press the X5 magnifying tab on the CRO to get a magnified view of the two voltages

especially near the transition region. However, if your CRO is not having high bandwidth, you

may not be able to appreciate the time delay. So it is instructive here to use high bandwidth CRO

or better a digital storage

Oscilloscope.

4. Observe the time difference between the two waveforms at the points at which the two waves

are crossing the 50% mark of their maximum amplitudes as illustrated in Figure 4. Accordingly

there are two delay time values- TPHL and TPLH. (One for rising edge and one for falling edge).

5. Calculate the actual value of these time differences by dividing them by a factor of 5 so as to

compensate for magnification.

6. The values of TPHL and TPLH so obtained are the delay time values for five inverters

together. So the value of delay time for a single inverter can be estimated as tphl= TPHL/5 ;

tplh= TPLH/5 : Calculate the average value of the delay time as: TD = (tphl + tplh

Equipments Needed

1. SSLAb . IC 46 digital logic board.

2. Patch cords

3. CRO

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

5. Two Digital Multimeter

Circuit diagram :

Figure 6

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure :

1. Connect point A to A2 and point C2 to C/D point at the output.

2. Also connect these input and output voltage socket to the two digital multimeters to record the

input voltage and corresponding output voltage.

3. Use the steps explained already in the experiment 1 to draw VTC on the graph paper and

observe the Voltage Transfer Characteristics on CRO as well.

Equipments Needed :

1. Digital lab,

2. IC-46 digital logic board.

3. Patch cords

4. CRO

5. Signal Generator

6. Two Digital Multimeters

Circuit diagram :

Figure 7

Procedure :

1. Verify that the power supply to the Digital Lab is switched off.

2. Place the logic board IC-49 at the place provided on the digital lab board.

3. Take a note of the fact that now in this experiment you will have to use 3-15Volt power

supply, i.e. you can use any of the value between 3 to 15volt for power supply. So connect this

supply input pin to the variable power supply outlet on the Digital Lab . But while performing or

collecting the data for a single mexperiment do not change power supply value.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Voltage Transfer Characteristics :

Connect the Pot P2 to the input of the CD4069 inverter gate and output of this gate to the output

node on the board. Also connect these points to the DMMs to record the input and output values

as shown in the setup Figure given above.Repeat the procedure as given in the experiment 1 step

by step to perform this experiment as well. The only changes you can expect here is that you

have to repeat the entire experiment for different power supply values. Take the readings for

5volt, 10volt and 15volt power supply ranges to appreciate some substantial change and plot

the corresponding curves on the same graph sheet. Another change you can expect here is the

change in the value of the delay time. Due to the capacitive loadings, the response of these gates

to the fast varying signals is a bit slow in the comparison to TTL logic gates.

Equipments Needed :

1. IC-46 digital logic board.

2. Patch cords

3. CRO

4. Two Digital Multimeter

Circuit diagram :

Figure 8

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure :

1. Connect the point B to the B2 and point D2 to C/D point at the output.

2. Also connect these input and output voltage socket to the two Digital

multimeters to record the input voltage and corresponding output voltage.

3. Use the steps explained already in the experiment-1 to draw VTC on graph

paper and observe the Voltage Transfer Characteristics on CRO as well.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 9

4 BIT GRAY TO BINARY AND BINARY TO GRAY CODE CONVERTION

Aim: - To study and implementation of 4 bit gray to binary and binary to gray code convertion.

Apparatus:-

1)Trainer kit

2)Patch chords

3)Power supply

Theory:-

The availability of a large variety of codes for the same discrete elements of information

results in the use of different codes by different digital system. It is sometimes necessary to use

the output of one system as the input to another. A conversion circuit must be inserted between

the two systems if each uses different codes for the same information. Thus, a code converter is a

circuit that makes the two systems compatible even though each uses a different binary code.

The binary number system is a system that uses only the digits 0 & 1 as codes. To represent a

group of 2n distinct element in a binary code requires a minimum of n bits. This is because it is

possible to arrange n bits in 2n distinct ways. Although the minimum number of bits required to

code 2n distinct quantities is n, there is no maximum number of bits that may be used for binary

code. For example, a group of four distinct quantities can be represented by a two bit code, with

each quantity assigned one of the following bit combinations: 00, 01, 10, and 11. A group of

eight elements requires a three bit code, with each element assigned to one and only one of the

following 000, 001, 010, 011, 100, 101, 110, and 111. Gray code (reflected code) is shown in

Table 1. Number in the gray code changes by only one bit as it proceeds from one number to the

next. For example in going from decimal 7 to 8, the gray code number changes from 0100 to

1100; these number differ only in MSB. So it is with the entire gray code; every number differs

by only one bit from the preceding number. The logic diagram for binary code to gray code

converter. Here we are using the XOR gates the IC 74ls86 is quardpack XOR gate Ices.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

The pin diagram (74LS86):-

Figure (1) IC 74LS86

Logic diagram:-

B0

G0

B1

G1

B2

G2

B3 G3

Figure (2) binary to gray Logic

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure (Binary to gray):-

1) The inputs are B0, B1, B2 and B3 connected to the logic switches.

2) The outputs are G0, G1, G2 and G3 connected to the led indication.

3) Now switch on the trainer kit.

4) By applying the binary inputs through the logic switches observe the outputs G0, G1, G2

and G3 led indication.

5) Note down the outputs in a truth table.

Truth table:-

Inputs Outputs

Decimal

B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 1

2 0 0 1 0 0 0 1 1

3 0 0 1 1 0 0 1 0

4 0 1 0 0 0 1 1 0

5 0 1 0 1 0 1 1 1

6 0 1 1 0 0 1 0 1

7 0 1 1 1 0 1 0 0

8 1 0 0 0 1 1 0 0

9 1 0 0 1 1 1 0 1

10 1 0 1 0 1 1 1 1

11 1 0 1 1 1 1 1 0

12 1 1 0 0 1 0 1 0

13 1 1 0 1 1 0 1 1

14 1 1 1 0 1 0 0 1

15 1 1 1 1 1 0 0 0

The logic for the Binary to Gray code converter is

G0 = B0 B1

G1 = B1 B2

G2 = B2 B3

G3 = B3

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Logic diagram:-

G0

B0

B1

G1

G2 B2

G3 B3

Procedure (Gray to binary):-

1) The inputs are G0, G1, G2 and G3 connected to the logic switches.

2) The outputs are B0, B1, B2 and B3 connected to the led indication.

3) Now switch on the trainer kit.

4) By applying the gray inputs through the logic switches observe the outputs B0, B1, B2

and B3 led indication.

5) Note down the outputs in a truth table.

Truth table:-

Inputs Outputs

Decimal

G3 G2 G1 G0 B3 B2 B1 B0

0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 1

2 0 0 1 1 0 0 1 0

3 0 0 1 0 0 0 1 1

4 0 1 1 0 0 1 0 0

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

5 0 1 1 1 0 1 0 1

6 0 1 0 1 0 1 1 0

7 0 1 0 0 0 1 1 1

8 1 1 0 0 1 0 0 0

9 1 1 0 1 1 0 0 1

10 1 1 1 1 1 0 1 0

11 1 1 1 0 1 0 1 1

12 1 0 1 0 1 1 0 0

13 1 0 1 1 1 1 0 1

14 1 0 0 1 1 1 1 0

15 1 0 0 0 1 1 1 1

The logic for the Gray to Binary code converter is

B0 = G3 G2 G1 G0

B1 = G3 G2 G1

B2 = G3 G2

B3 = G3

Result:- Hence the Binary to Gray and Gray to Binary code convertion is verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 10

TWO DIGIT 7 SEGMENT DISPLAY USING 53 COUNTER

Aim: - To study and implementation of two digit 7 segment display using 53 counter.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

The decade counter, which divides input by 10 counter and provides BCD output 0 to 9:

this is also called as decimal counter. This counter comprises of a divide by 2’ and divide

by 5’ counters. To use as decade we have to cascade divide by 2’ and divide by 5. Output

Q0 Q3 are BCD outputs, inputs A and B are clock inputs to the counter, divide by 2’and

divide by 5’ counters respectively. Ro1 and R02 are the reset inputs, when these are

activated counter go to 0000.So1 and S02 are the set inputs to the counter, when these

inputs are activated counter output go to 1001.casecading of the two decade counters we

are performing the 53 counter.

Pin-diagram (74LS90):-

Figure (1) Pin-diagram 74LS90

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Circuit diagram:-

Figure (2) 53 counter circuit

The above circuit consisting of two decade counters and the 1Hz clock generation

block is given for connecting to the clock input of the circuit. The operation of the circuit

is connecting the two decade counter in a cascade manner. The below decade counter is

counting the 0000 to 1001 it means one decade count. When it is completed the one

decade count one clock is given to the first decade counter then the first decade counter is

incremented by one count this process is repeated for the 53 counts. When is reached to

the 53 counts it will be stopped or otherwise it reset. In this circuit the first decade is

divided by the so that it can count up to five and second one is counts the decade.

Procedure:-

1) Connect the clock output (1Hz) to the input of the decade counter.

2) Connect the first ic ouputs i.e Q0, Q1, Q2 and Q3 to the 7 segment.

3) Connect the second ic ouputs i.e Q0, Q1, Q2 and Q3 to the 7 segment after

connected the first ic.

a. Now short the first ic R91, R92 using a patch chord connect these shorted line to

the logic switch.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

5) Now short the second ic R91, R92 using a patch chord connect these shorted line

to the logic switch.

6) Connect the power chord to the AC supply. Now switch on the trainer kit.

7) Using logic switches reset the circuit to the zero position.

8) Now the counter will start the counting. Observe the output on 7 segments it will

be count 0 to 52 counts.

Truth table:-

INPUTS OUTPUTS

R92 R91 Qd Qc Qb Qa

X L L L L L

H H H L L H

L L COUNT

Result:- Hence the two digit 7 segment display using 53 counter is implemented and verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 11

8 BIT PARALLEL LOAD AND SERIAL OUT USING TWO 4 BIT SHIFT REGISTER

Aim: - To study and implementation of 8 bit parallel load and serial out using two 4 bit shift

Register.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

A register is simply a group of flip flops that can be used to store a binary number. A

shift register is a group of flip flops connected such that the binary number can be entered

(shifted) into the register and possibly shifted out. There are two ways to shift the data (bits in

the binary number) from one place to another. The first method involves shifting the data 1 bit at

a time in a serial fashion, beginning with either MSB or LSB. This technique is referred to as

serial shifting. The second method involves shifting all the data bits simultaneously and is

referred to as parallel shifting. There are two ways to shift data into a register (serial or parallel)

and similarly two ways to shift data out of the register. This leads to the construction of four

basic types of registers.

This bidirectional shift register is designed to incorporate virtually all of the features a

system designer may want in a shift register; they feature parallel inputs, parallel outputs, right-

shift and left-shift serial inputs, operating-mode-control inputs, and a direct overriding clear line.

The register has four distinct modes of operation, namely:

Parallel (broadside) load

Shift right (in the direction QA toward QD)

Shift left (in the direction QD toward QA)

Inhibit clock (do nothing)

Synchronous parallel loading is accomplished by applying the four bits of data and taking

both mode control inputs, S0 and S1, HIGH. The data is loaded into the associated flip-flops and

appear at the outputs after the positive transition of the clock input. During loading, serial data

flow is inhibited. Shift right is accomplished synchronously with the rising edge of the clock

pulse when S0 is HIGH and S1 is LOW. Serial data for this mode is entered at the shift-right data

input. When S0 is LOW and S1 is HIGH, data shifts left synchronously and new data is entered

at the shift-left serial input.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Pin diagram (74LS194):-

Figure (1) pin configuration

8 bit parallel load and serial out using two 4 bit shift register:-

Circuit Diagram:-

Figure (2) parallel load and serial out circuit.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure:-

1) Connect the above circuit on the trainer kit.

2) Here the selection lines of the two IC can be shorted then it can be form the S0 and S1.

3) Connect the first pin of the two Ic’s then it can be form a clear then it connect to the logic

switch.

4) Short the pin number 11 of the both the ic’s then it forms a common clock line then it is

connected to the 1Hz clock generator or the pulsar switch.

5) Now connect the parallel data inputs of the first ic and the second ic to the

logic switches.

6) Connect the QA, QB, QC and QD of the first ic to the led’s shown in the circuit.

7) Connect the QA, QB, QC and QD of the second ic to the led’s shown in the circuit

assume it as QE, QF, QG and QH.

8) Connect the 2pin of the first ic to the 12pin of the second ic.

9) Connect the serial input of the second IC (pin7) to the logic switch put in logic ‘0’.

10) Connect the 2pin of the second ic to the 12pin of the first ic.

11) Connect the 7pin of the second ic to the 15pin of the first ic.

12) Connect the parallel inputs (ABCD) first ic to the logic switches similarly connect the

Parallel inputs (ABCD) of the second ic to the logic switches and assume it as EFGH.

13) Now put the selection lines both are high that is S0=’1’ and S1=’1’ now apply the

input Data. Whatever you given it will be indicated on the led’s.

Ex:

A=1,B=0,C=0,D=0,A=0,B=1,C=0,D=0=1000 0100

14) After applying the parallel data put the S0=’0’ and S1=’1’ then the data is shifted

right side.

15) The input data serially exited at the QA you will observe that using the pulsar

switch giving a single pulse at a time.

16) Observe the truth table below.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Truth table:-

INPU OUTPU

TS TS

Mod Cloc

e S0 S1 Clear k Q Q Q Q

A B C D E F G H A QB QC D QE QF G H

Hold 1 1 H 1 0 0 0 0 1 0 0 1 0 0 0 0 1 0 0

0 1 H 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0

0 1 H 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0

Shift 0 1 H 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0

right 0 1 H 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0

0 1 H 1 0 0 0 0 1 0 0 1 0 0 0 0 0 0 0

0 1 H 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0

Result: - Hence the 8 bit parallel load and serial out using two 4 bit shift Register

constructed and verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 12

8 BIT SERIAL IN AND SERIAL OUT USING TWO 4 BIT SHIFT REGISTER

Aim: - To study and implementation of 8 bit serial in and serial out using two 4 bit shift

Register.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

A register is simply a group of flip flops that can be used to store a binary number. A

shift register is a group of flip flops connected such that the binary number can be entered

(shifted) into the register and possibly shifted out. There are two ways to shift the data (bits in

the binary number) from one place to another. The first method involves shifting the data 1 bit at

a time in a serial fashion, beginning with either MSB or LSB. This technique is referred to as

serial shifting. The second method involves shifting all the data bits simultaneously and is

referred to as parallel shifting. There are two ways to shift data into a register (serial or parallel)

and similarly two ways to shift data out of the register. This leads to the construction of four

basic types of registers.

This bidirectional shift register is designed to incorporate virtually all of the features a

system designer may want in a shift register; they feature parallel inputs, parallel outputs, right-

shift and left-shift serial inputs, operating-mode-control inputs, and a direct overriding clear line.

The register has four distinct modes of operation, namely:

Parallel (broadside) load

Shift right (in the direction QA toward QD)

Shift left (in the direction QD toward QA)

Inhibit clock (do nothing)

Synchronous parallel loading is accomplished by applying the four bits of data and taking

both mode control inputs, S0 and S1, HIGH. The data is loaded into the associated flip-flops and

appear at the outputs after the positive transition of the clock input. During loading, serial data

flow is inhibited. Shift right is accomplished synchronously with the rising edge of the clock

pulse when S0 is HIGH and S1 is LOW. Serial data for this mode is entered at the shift-right data

input. When S0 is LOW and S1 is HIGH, data shifts left synchronously and new data is entered

at the shift-left serial input.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Pin diagram (74LS194):-

Figure (3) pin configuration

8 bit serial in and serial out using two 4 bit shift register:-

Circuit Diagram:-

Figure (4) parallel load and serial out circuit.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure:-

a. Connect the above circuit on the trainer kit.

b. Here the selection lines of the two IC can be shorted then it can be form the S0

and S1.

c. Connect the first pin of the two Ic’s then it can be form a clear then it connect to

the logic switch.

d. Short the pin number 11 of the both the ic’s then it forms a common clock line

then it is Connected to the 1Hz clock generator or the pulsar switch.

e. Now connect the shift right serial input data inputs of the first ic to the logic

switche.

1)Connect the QA, QB, QC and QD of the first ic to the led’s shown in the circuit.

2)Connect the QA, QB, QC and QD of the second ic to the led’s shown in the circuit

assume it as QE, QF, QG and QH.

3)Connect the 7pin of the first ic to the 15pin of the second ic.

4)Connect the 2pin of the second ic to the 12pin of the first ic.

5)Connect the serial input of the second IC pin7 to the logic switch.

6) Now put the selection lines S0=’0’ and S1=’1’ now apply the input data through the pin7

of second ic Data serially by varying the logic switch. Whatever you given it will be

indicated on the led’s and it is exited at the top led.

Ex: Shift right serial input=1010 0000

a. The input data serially exited at the QA you will observe that using the

pulsar switch Giving a single pulse at a time.

b. Observe the truth table below.

Truth table:-

OUTPUTS

Mode S0 S1 Clear Clock QA QB QC QD QE QF QG QH

Hold 1 1 H A B C D E F G H

0 1 H Rin QA QB QC QD QE QF QG

0 1 H 1 0 1 0 0 0 0 0

Shift

0 1 H 0 1 0 0 0 0 0 0

right

0 1 H 1 0 0 0 0 0 0 0

0 1 H 0 0 0 0 0 0 0 0

Result: - Hence the 8 bit serial in and serial out using two 4 bit shift register. Constructed and

verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 13

4 BIT RING AND TWISTED RING COUNTER

Aim: - To study and implementation of 4 bit ring and twsted ring counter.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:

The Ring Counter

In the previous Shift Register tutorial we saw that if we apply a serial data signal to the input of

a serial-in to serial-out shift register, the same sequence of data will exit from the last flip-flip in

the register chain after a preset number of clock cycles thereby acting as a sort of time delay

circuit to the original signal. But what if we were to connect the output of this shift register back

to its input so that the output from the last flip-flop, QD becomes the input of the first flip-flop,

DA. We would then have a closed loop circuit that "recirculates" the DATA around a continuous

loop for every state of its sequence, and this is the principal operation of a Ring Counter . Then

by looping the output back to the input, we can convert a standard shift register into a ring

counter. Consider the circuit below.

4-bit Ring and twisted Counter

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

The synchronous Ring Counter example above, is preset so that exactly one data bit in the

register is set to logic "1" with all the other bits reset to "0". To achieve this, a "CLEAR" signal

is firstly applied to all the flip-flops together in order to "RESET" their outputs to a logic "0"

level and then a "PRESET" pulse is applied to the input of the first flip-flop (FFA) before the

clock pulses are applied. This then places a single logic "1" value into the circuit of the ring

counter . On each successive clock pulse, the counter circulates the same data bit between the

four flip-flops over and over again around the "ring" every fourth clock cycle. But in order to

cycle the data correctly around the counter we must first "load" the counter with a suitable data

pattern as all logic "0"'s or all logic "1"'s outputted at each clock cycle would make the ring

counter invalid.

This type of data movement is called "rotation", and like the previous shift register, the effect of

the movement of the data bit from left to right through a ring counter can be presented

graphically as follows along with its timing diagram:

Rotational Movement of a Ring ring Counter

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Since the ring counter example shown above has four distinct states, it is also known as a

"modulo-4" or "mod-4" counter with each flip-flop output having a frequency value equal to

one-fourth or a quarter (1/4) that of the main clock frequency.

The "MODULO" or "MODULUS" of a counter is the number of states the counter counts or

sequences through before repeating itself and a ring counter can be made to output any modulo

number. A "mod-n" ring counter will require "n" number of flip-flops connected together to

circulate a single data bit providing "n" different output states. For example, a mod-8 ring

counter requires eight flip-flops and a mod-16 ring counter would require sixteen flip-flops.

However, as in our example above, only four of the possible sixteen states are used, making ring

counters very inefficient in terms of their output state usage.

Twisted Ring Counter

The Johnson Ring Counter or "Twisted Ring Counters", is another shift register with feedback

exactly the same as the standard Ring Counter above, except that this time the inverted output Q

of the last flip-flop is now connected back to the input D of the first flip-flop as shown below.

The main advantage of this type of ring counter is that it only needs half the number of flip-flops

compared to the standard ring counter then its modulo number is halved. So a "n-stage" Johnson

counter will circulate a single data bit giving sequence of 2n different states and can therefore be

considered as a "mod-2n counter".

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

4-bit twisted Counter

This inversion of Q before it is fed back to input D causes the counter to "count" in a different

way. Instead of counting through a fixed set of patterns like the normal ring counter such as for a

4-bit counter, "0001"(1), "0010"(2), "0100"(4), "1000"(8) and repeat, the Johnson counter counts

up and then down as the initial logic "1" passes through it to the right replacing the preceding

logic "0". A 4-bit Johnson ring counter passes blocks of four logic "0" and then four logic "1"

thereby producing an 8-bit pattern. As the inverted output Q is connected to the input D this 8-bit

pattern continually repeats. For example, "1000", "1100", "1110", "1111", "0111", "0011",

"0001", "0000" and this is demonstrated in the following table below.

Truth Table for a 4-bit twisted Ring Counter

Clock Pulse No FFA FFB FFC FFD

0 0 0 0 0

1 1 0 0 0

2 1 1 0 0

3 1 1 1 0

4 1 1 1 1

5 0 1 1 1

6 0 0 1 1

7 0 0 0 1

As well as counting or rotating data around a continuous loop, ring counters can also be used to

detect or recognise various patterns or number values within a set of data. By connecting simple

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

logic gates such as the AND or the OR gates to the outputs of the flip-flops the circuit can be

made to detect a set number or value. Standard 2, 3 or 4-stage Johnson ring counters can also be

used to divide the frequency of the clock signal by varying their feedback connections and

divide-by-3 or divide-by-5 outputs are also available.

A 3-stage Johnson Ring Counter can also be used as a 3-phase, 120 degree phase shift square

wave generator by connecting to the data outputs at A, B and NOT-B. The standard 5-stage

Johnson counter such as the commonly available CD4017 is generally used as a synchronous

decade counter/divider circuit. The smaller 2-stage circuit is also called a "Quadrature"

(sine/cosine) Oscillator/Generator and is used to produce four individual outputs that are each

"phase shifted" by 90 degrees with respect to each other, and this is shown below.

Result: Hence the 8 bit serial in and serial out using two 4 bit shift register. Constructed and

verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 14

4 DIGIT HEX COUNTER USING SYNCHRONOUS ONE DIGIT HEXCOUNTER

Aim: - To study and implementation of 4 digit hex counter using synchronous one digit hex

Counter.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

The external clock pulses (pulses to be counted) are fed directly to each of the J-K flip-

flops in the counter chain and that both the J and K inputs are all tied together in toggle mode,

but only in the first flip-flop, flip-flop FFA (LSB) are they connected HIGH, logic “1” allowing

the flip-flop to toggle on every clock pulse. Then the synchronous counter follows a

predetermined sequence of states in response to the common clock signal, advancing one state

for each pulse.

The J and K inputs of flip-flop FFB are connected directly to the output QA of flip-flop

FFA, but the J and K inputs of flip-flops FFC and FFD are driven from separate AND gates

which are also supplied with signals from the input and output of the previous stage. These

additional AND gates generate the required logic for the JK inputs of the next stage. If we enable

each JK flip-flop to toggle based on whether or not all preceding flip-flop outputs (Q) are

“HIGH” we can obtain the same counting sequence as with the asynchronous circuit but without

the ripple effect, since each flip-flop in this circuit will be clocked at exactly the same time.

Then as there is no inherent propagation delay in synchronous counters, because all the

counter stages are triggered in parallel at the same time, the maximum operating frequency of

this type of frequency counter is much higher than that for a similar asynchronous counter

circuit.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Pin-diagram:-

Figure (1) Pin-diagram 74LS73

Block diagram on pcb:-

Figure (2) Circuit diagram

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Circuit connection diagram:-

7 Segment display:-

Figure (3) 7 Segment display

The 7-segment display, also written as “seven segment display”, consists of seven LEDs

(hence its name) arranged in a rectangular fashion as shown. Each of the seven LEDs is called a

segment because when illuminated the segment forms part of a numerical digit (both Decimal

and Hex) to be displayed. An additional 8th LED is sometimes used within the same package

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

thus allowing the indication of a decimal point, (DP) when two or more 7-segment displays are

connected together to display numbers greater than ten.

Each one of the seven LEDs in the display is given a positional segment with one of its

connection pins being brought straight out of the rectangular plastic package. These individually

LED pins are labeled from a through to g representing each individual LED. The other LED pins

are connected together and wired to form a common pin. So by forward biasing the appropriate

pins of the LED segments in a particular order, some segments will be light and others will be

dark allowing the desired character pattern of the number to be generated on the display. This

then allows us to display each of the ten decimal digits 0 through to 9 on the same 7-segment

display and it can be displays the hex values. The truth table is given below

Truth table for 7Segment:-

Digit Display a b c d e f g

0 0 on on on on on on off

1 1 off on on off off off off

2 2 on on off on on off on

3 3 on on on on off off on

4 4 off on on off off on on

5 5 on off on on off on on

6 6 on off on on on on on

7 7 on on on off off off off

8 8 on on on on on on on

9 9 on on on on off on on

A on on on off on on on

b off off on on on on on

C on off off on on on off

d off on on on on off on

E on off off on on on on

No

F on off off off on on on

display

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Procedure:-

1) Connect the first J-K flip-flop to logic switch using a patch chord.

2) Connect the output of 1st flip-flop ‘1QA’ to the 2nd flip-flop J-K. Connect this point to

the 7seg ‘A’ input using patch chord and connect this point to the AND gate input.

3) Connect the output of 2nd flip-flop ‘1QB’ to the 3rd flip-flop J-K. Connect this point to the

7seg ‘B’ input using patch chord and connect this point to the AND gate input.

4) Connect the output of AND gate ‘1QC’ to the 4th flip-flop J-K. connect this point to the

7seg ‘C’ input using patch chord connect this point to the AND gate input.

5) Make the all connection shown in the circuit connection diagram.

6) Connect the 1st stage outputs QA, QB, QC and QD to the 1st 7segment.

7) Connect the 2nd stage outputs QA, QB, QC and QD to the 2nd 7segment.

8) Connect the 3rd stage outputs QA, QB, QC and QD to the 3rd 7segment.

9) Connect the 4th stage outputs QA, QB, QC and QD to the 4th 7segment.

10) Now switch on the trainer kit put the reset and the J-K flip-flop switches in logic

switch put in logic’1’.

11) Verify the counting of the 7segments. The first stage completes the ‘F’ the second stage

will be incremented by one this process is continues until the all the stages reaches to

the ‘FFFF’.

12) After completion of the all the stages ‘F’ the counter will be automatically resets and

it starts from ‘0000’.

Result:- Hence the implementation of 4 digit hex counter using synchronous one digit hex

Counter is verified.

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

EXPERIMENT NO: 15

4 DIGIT HEX COUNTER USING ASYNCHRONOUS ONE DIGIT HEXCOUNTER

Aim: - To study and implementation of 4 digit hex counter using asynchronous one digit hex

Counter.

Apparatus:-

1) Trainer kit

2) Patch chords

3) Power supply

Theory:-

Asynchronous Counters use flip-flops that are serially connected together so that the

input clock pulse ripples through the counter giving them the name of ripple counter. In this

asynchronous circuit the clock signal should be connected to the only the first J-K flip-flop and

the output of the first flip-flop that is ‘Q’ is connected to the clock input of the second flip-flop.

It means that whenever the first flip-flop complete its function then the output ‘Q’ will be

activated it gives a clock pulse to the next flip-flop. The second flip-flop will be activated then

the output of the second stage is given to the third stage clock input of the J-K flip-flop. The

sequence is four stages so the outputs will be QA, QB, QC and QD. The QA is the output of the

first stage and QB is the output of the second stage similarly remaining QC and QD respective

stages. The output of the single stage counts the 0000- 1111 it means that it counts the zero to

fifteen so it is called the one hex count. This is only for the single stage using this single stage we

are build the four digit hex counter. To build this we are using the 74LS73 it is having the two J-

K flip-flops.

Pin-diagram:-

Figure (1) Pin-diagram 74LS73

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

Block diagram on pcb:-

Figure (2) Circuit diagram

Circuit connection diagram:-

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

7 Segment display:-

Figure (3) 7 Segment display

The 7-segment display, also written as “seven segment display”, consists of seven LEDs

(hence its name) arranged in a rectangular fashion as shown. Each of the seven LEDs is called a

segment because when illuminated the segment forms part of a numerical digit (both Decimal

and Hex) to be displayed. An additional 8th LED is sometimes used within the same package

thus allowing the indication of a decimal point, (DP) when two or more 7-segment displays are

connected together to display numbers greater than ten.

Each one of the seven LEDs in the display is given a positional segment with one of its

connection pins being brought straight out of the rectangular plastic package. These individually

LED pins are labeled from a through to g representing each individual LED. The other LED pins

are connected together and wired to form a common pin. So by forward biasing the appropriate

pins of the LED segments in a particular order, some segments will be light and others will be

dark allowing the desired character pattern of the number to be generated on the display. This

then allows us to display each of the ten decimal digits 0 through to 9 on the same 7-segment

display and it can be displays the hex values. The truth table is given below

Truth table for 7Segment:-

Digit Display a b c d e f g

0 0 on on on on on on off

1 1 off on on off off off off

2 2 on on off on on off on

3 3 on on on on off off on

4 4 off on on off off on on

5 5 on off on on off on on

6 6 on off on on on on on

7 7 on on on off off off off

8 8 on on on on on on on

9 9 on on on on off on on

Department of ECE, MIST Page 12

Digital IC Applications Lab Manual

on on on off on on on

b off off on on on on on

C on off off on on on off

d off on on on on off on

E on off off on on on on

N

o

F on off off off on on on

display

Procedure:-

1) Connect the Reset to the logic switch through the patch chord.

2) Connect the first J-K flip-flop all to be shorted and give them to logic switch using

a patch chord.

3) Connect the output of 1st flip-flop ‘1QA’ to the 2nd flip-flop clk. Connect this point to

the 7seg ‘A’ input using patch chord.

4) Connect the output of 2nd flip-flop ‘1QB’ to the 3rd flip-flop clk. Connect this point to

the 7seg ‘B’ input using patch chord.

5) Connect the output of 3rd flip-flop ‘1QC’ to the 4th flip-flop clk. connect this point to the

7seg ‘C’ input using patch chord.

6) Connect the output of 4th flip-flop ‘1QD’ to the 7seg ‘D’ input using patch chord this

is only for the single digit.

7) Connect the output of 1st stage ‘1QD’ to the clock input of the 2nd stage.

8) Make the all connection shown in the circuit connection diagram.

9) Connect the 1st stage outputs QA, QB, QC and QD to the 1st 7segment.

10) Connect the 2nd stage outputs QA, QB, QC and QD to the 2nd 7segment.

11) Connect the 3rd stage outputs QA, QB, QC and QD to the 3rd 7segment.

12) Connect the 4th stage outputs QA, QB, QC and QD to the 4th 7segment.

13) Now switch on the trainer kit put the reset and the J-K flip-flop switches in logic switch.

14) Verify the counting of the 7segments. The first stage completes the ‘F’ the second stage

will be incremented by one this process is continues until the all the stages reaches to

the ‘FFFF’.

15) After completion of the all the stages ‘F’ the counter will be automatically resets and

it starts from ‘0000’.

Result:- Hence the implementation of 4 digit hex counter using asynchronous one digit hex

Counter is verified.

Department of ECE Page 65

You might also like

- Rfic & Mmic-0Document12 pagesRfic & Mmic-0PhilippeaNo ratings yet

- PIC Projects and Applications using C: A Project-based ApproachFrom EverandPIC Projects and Applications using C: A Project-based ApproachRating: 4 out of 5 stars4/5 (2)

- UNIT V Digital Integrated Circuits Introduction Part IIDocument135 pagesUNIT V Digital Integrated Circuits Introduction Part IINayab Rasool SK100% (1)

- Typical VIOS Network Configuration in Production EnvironmentDocument6 pagesTypical VIOS Network Configuration in Production EnvironmentCassamo NurmahomedNo ratings yet

- Design of Half Full Adder, Half Full Subtractor and Parallel AddersubtractorDocument7 pagesDesign of Half Full Adder, Half Full Subtractor and Parallel AddersubtractorMani Bharathi100% (1)

- Cmd-V4 Service ManualDocument442 pagesCmd-V4 Service ManualGABRIELA100% (1)

- Dica Lab Manual PDFDocument74 pagesDica Lab Manual PDFRuchithareddy MandaNo ratings yet

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 pagesDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiNo ratings yet

- DLD Lab ManualDocument101 pagesDLD Lab ManualHamza100% (1)