Professional Documents

Culture Documents

Biiile I3116 PDF

Uploaded by

jay shahOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Biiile I3116 PDF

Uploaded by

jay shahCopyright:

Available Formats

DHARMS INH DESAI UNIVERS ITY, NADIAD

FACULTY OF TECHNOLOGY

THIRD S ESSIONAL EXAMINATION

SUBJ ECT: ( CI308 ) LINEAR EL ECTRONICS-I

Examination : B. Tech. Semester III [EC/ IC] Seat No : ____________________

Date : 06/10/2015 Day :Tues day

Ti me : 10:15 a.m. to 11:30 a.m. Max. Marks : 36

INSTRUCTIONS:

1. Figures to the right indicate maximu m marks for that question.

2. The symbols used carry their usual meanings.

3. Assume suitable data, if required & mention them clearly.

4. Draw neat sketches wherever necessary.

Q.1 Do as directed. [12]

a. represent: [1]

(A) output admittance, (B) output resistance, (C) input resistance, (D) None of these.

b. Which of the following cascading connections can provide low input resistance, low [1]

output resistance, high voltage gain.

(A) CC-CE-CB, (B) CB-CE-CC, (C) CC-CE-CC, (D) CB-CE-CB.

c. Prove . [2]

d. State true/false with reason; BVceo is less than BVcbo. [2]

e. Determine input and output time constant for Hybrid-π model of a transistor in the CE [2]

configuration with RL = 2 kΩ, Cc = 3 pF, rb’e = 1 kΩ, Ce = 100 pF and gm = 50 mA/V.

f. Discuss bias compensation technique for ICO germanium transistor with necessary [2]

equations.

g. State true or false with justification [2]

(i) “The The base spreading resistance rbb’ increases with temperature”.

(ii) “The diffusion capacitance is proportional to the emitter bias current I E”.

Q.2 Do as directed. (Any Two) [12]

a. (I) Prove: . [4]

(II)Why two separate diodes connected in series opposing cannot work as a transistor. [2]

b. Draw transistor amplifier circuit using h parameters. Derive the equation of AI, AV, Zi, [6]

AVs, AIs, Yo .

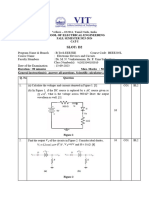

c. For the amplifier shown if Figure:1 calculate . [6]

[Assume ]

Q.3 Do as Directed. [12]

a. Design self-bias circuit using a silicon transistor to meet the following specification [6]

over the temperature range 25 to 65 ºC:

(ΔIc/Ic ) ≤ 21%, VBE at 25 ºC = 650 + 50 mV, Vcc= 20 V, β spread 150 to 600 at Ic = 1

mA and T = 25 ºC, Lowest β at 25 ºC= 150, highest β at 65 ºC= 1200, Ico at 25 ºC= 50

nA max, Ico at 65 ºC= 3 µA max.

b. Derive Hybrid-π input conductance gb’e, feedback conductance gb’c, and output [6]

conductance gce in terms of h parameters of CE configuration.

OR

Q.3 Do as Directed. [12]

a. Discuss compensation techniques using temperature sensitive resistive elements with [4]

necessary circuit diagrams.

b. Find the stability factor S’’ for the circuit of figure 2 with Rc= 2.3K, R=50K Vc=2V [4]

and =55.

c. Derive the CE short-circuit current gain Ai and the frequency at which gain drops to [4]

unity with the help of Hybrid-π model.

VCC

10kΩ

100kΩ Vo

10kΩ

Vs

Ri' Ri

Figure:1 Q. 2(c) Figure: 2 Q.3(b)

Page 1 of 1

You might also like

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Mid Term Sem 2 2014 - 2015Document10 pagesMid Term Sem 2 2014 - 2015FARAZ ABDUL BASITNo ratings yet

- Basic Electronics Engineering I SemDocument3 pagesBasic Electronics Engineering I Semshubhambani45No ratings yet

- rr12302 Electrical and Electronics EngineeringDocument12 pagesrr12302 Electrical and Electronics EngineeringSRINIVASA RAO GANTANo ratings yet

- Faculty of Engineering Electronic and Computer EngineeringDocument4 pagesFaculty of Engineering Electronic and Computer EngineeringSamuelNo ratings yet

- Mid-Sem Sem2Document10 pagesMid-Sem Sem22023kucp1012No ratings yet

- Candidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksDocument2 pagesCandidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarkssushilNo ratings yet

- EEE 2202 ANALOGUE ELECTRONICS I - July17 - ExamDocument5 pagesEEE 2202 ANALOGUE ELECTRONICS I - July17 - Exameric wahomeNo ratings yet

- 2017 NovDocument7 pages2017 Novezekiel makandwaNo ratings yet

- r5100207 Electronic Devices and CircuitsDocument4 pagesr5100207 Electronic Devices and CircuitssivabharathamurthyNo ratings yet

- Ae53 Ac53 At53Document4 pagesAe53 Ac53 At53M Taher BamyaniNo ratings yet

- 2nd Sem Bee Feb 2020 RND RDocument2 pages2nd Sem Bee Feb 2020 RND RBikash SarrafNo ratings yet

- Jagrut Awaaz: Gujarat Technological UniversityDocument2 pagesJagrut Awaaz: Gujarat Technological UniversityMaaz AnsariNo ratings yet

- Basicelectronicdevicesandcircuits Jntu Model Paper (WWW - Studentyogi.com)Document7 pagesBasicelectronicdevicesandcircuits Jntu Model Paper (WWW - Studentyogi.com)sapabapliveNo ratings yet

- Final Question - ECE1312 - Sem1 - 14-15Document9 pagesFinal Question - ECE1312 - Sem1 - 14-15FARAZ ABDUL BASITNo ratings yet

- Analog Circuits (Ecen 2101)Document5 pagesAnalog Circuits (Ecen 2101)sumitbhuia10No ratings yet

- Ec-101 - Final PDFDocument2 pagesEc-101 - Final PDFarjunv_14No ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- B C1103 Pages: 3: Answer Any Two Full Questions, Each Carries 15 MarksDocument3 pagesB C1103 Pages: 3: Answer Any Two Full Questions, Each Carries 15 MarksanuNo ratings yet

- Set No. 1: CEO CBODocument9 pagesSet No. 1: CEO CBO29viswa12No ratings yet

- Pulse and Digital CircuitsDocument8 pagesPulse and Digital Circuitssravya sriNo ratings yet

- rr102306 Electrical and Electronics EngineeringDocument1 pagerr102306 Electrical and Electronics EngineeringsivabharathamurthyNo ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, MCT)pramodNo ratings yet

- Q1371 Analog ElectronicsDocument1 pageQ1371 Analog ElectronicsDivyanshu BoseNo ratings yet

- Tutorial 01 - 2022 BatchDocument2 pagesTutorial 01 - 2022 Batchthushara0322No ratings yet

- Pcc-Ee 305Document4 pagesPcc-Ee 305Amlan SarkarNo ratings yet

- 133 BK 112017Document3 pages133 BK 1120172BL20EC096spoorti NidoniNo ratings yet

- Final Put 2023Document3 pagesFinal Put 2023Akash AnandNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat NoMeet TodankarNo ratings yet

- Semester-1 - Chemistry Stream - Mid+end PaperDocument15 pagesSemester-1 - Chemistry Stream - Mid+end PaperGopiNo ratings yet

- Edc 8Document9 pagesEdc 829viswa12No ratings yet

- WWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, Etm, MCT)Document2 pagesWWW - Manaresults.Co - In: (Common To Eee, Ece, Cse, Eie, It, Etm, MCT)Roman CenaNo ratings yet

- Tsheet1 EEDocument2 pagesTsheet1 EEHeena FarooqNo ratings yet

- Scenario:: Internal Verification Form D1Document10 pagesScenario:: Internal Verification Form D1tanmoyr2001No ratings yet

- Edc 4Document10 pagesEdc 429viswa12No ratings yet

- EEE 207 Final Summer 2015Document3 pagesEEE 207 Final Summer 2015rj OpuNo ratings yet

- NPTEL - Assignment - 11 - Travelling WaveDocument6 pagesNPTEL - Assignment - 11 - Travelling WaveAKSH0211No ratings yet

- Gujarat Technological UniversityDocument3 pagesGujarat Technological Universityvineets058No ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- Ee211 Test 1Document6 pagesEe211 Test 1Chimwemwe Kaonga100% (1)

- Analog Circuits: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesAnalog Circuits: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- HSSC-II PHYSICS HALF SYLLABUS (16-To-20) April 2021Document4 pagesHSSC-II PHYSICS HALF SYLLABUS (16-To-20) April 2021Heaven ColoursNo ratings yet

- Analogue II Exams Eee 2210 Mechatronics-PrintreadyDocument4 pagesAnalogue II Exams Eee 2210 Mechatronics-PrintreadyMike ShakespeareNo ratings yet

- Basic Electronics (ECE 1051)Document2 pagesBasic Electronics (ECE 1051)aryansorout1612No ratings yet

- 2002UNIT2PAPER2Document16 pages2002UNIT2PAPER2petey78No ratings yet

- Kbhilai School of Engineering, DurgDocument4 pagesKbhilai School of Engineering, DurgBhupatimtechNo ratings yet

- Questions Edc Set3Document2 pagesQuestions Edc Set3Severus SnapeNo ratings yet

- ISC Class 12 Physics Question Paper 2016Document8 pagesISC Class 12 Physics Question Paper 2016Harshita AgarwalNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- UnitTest - D25-Jun-2022 (1) VZSGV CDocument23 pagesUnitTest - D25-Jun-2022 (1) VZSGV CAadil ShaikhNo ratings yet

- EC21101 Basic Electronics ES 2018Document4 pagesEC21101 Basic Electronics ES 2018Santanu KunduNo ratings yet

- UnitTest D13 Jun 2022Document12 pagesUnitTest D13 Jun 2022Abhishek GoyalNo ratings yet

- r059210202 Pulse and Digital CircuitsDocument11 pagesr059210202 Pulse and Digital CircuitsSrinivasa Rao GNo ratings yet

- Model Question Paper: Basic ElectronicsDocument3 pagesModel Question Paper: Basic Electronicsravishpy100% (2)

- 131AK112017Document2 pages131AK112017Ranjeet Singh BishtNo ratings yet

- Phy3622 11 Nor 2018Document5 pagesPhy3622 11 Nor 2018Jay KayyNo ratings yet

- ECE201CDocument2 pagesECE201CMahakNo ratings yet

- RR Set No. 2Document8 pagesRR Set No. 2radhakodirekka8732No ratings yet

- Eca Q 2Document1 pageEca Q 2Shiva GlennNo ratings yet

- Digital RatioDocument85 pagesDigital Ratiojay shahNo ratings yet

- MQ2 Data SheetDocument3 pagesMQ2 Data SheetPVPPP100% (2)

- Project Report ON " Warning Bell "Document24 pagesProject Report ON " Warning Bell "jay shahNo ratings yet

- Jay ShahDocument13 pagesJay Shahjay shahNo ratings yet

- Polar Degrees PDFDocument1 pagePolar Degrees PDFjay shahNo ratings yet

- Tda 1579Document13 pagesTda 1579nooneezNo ratings yet

- BJT Diff AmplifierDocument15 pagesBJT Diff AmplifierAdrià Amézaga SàrriesNo ratings yet

- Communications Systems - LBB 1935/20 Plena Power AmplifierDocument3 pagesCommunications Systems - LBB 1935/20 Plena Power Amplifierprasad357No ratings yet

- Max9814 PDFDocument14 pagesMax9814 PDFsitiuswatun hasanahNo ratings yet

- Appendix 1: Decibels and NeperDocument2 pagesAppendix 1: Decibels and NeperDanang Ainal HakimNo ratings yet

- Single Stage Transistor Amplifier: Specific Gain MethodDocument17 pagesSingle Stage Transistor Amplifier: Specific Gain MethodAshish KumarNo ratings yet

- Lab8 X16-Discrete Time Filters (MDFD)Document7 pagesLab8 X16-Discrete Time Filters (MDFD)Soughah AlkendiNo ratings yet

- Lic Lab Manual Final - 2017-2018Document36 pagesLic Lab Manual Final - 2017-2018DeepakMishraNo ratings yet

- Interface Circuits For Microsensor Integrated Systems PDFDocument172 pagesInterface Circuits For Microsensor Integrated Systems PDFVKNo ratings yet

- Lica Lab ManualDocument47 pagesLica Lab Manualvishnu_yaraNo ratings yet

- 05-670 Microx User Manual V233P PDFDocument33 pages05-670 Microx User Manual V233P PDFYoucef KherroubiNo ratings yet

- The Audio Pages: Simple Class-A AmplifierDocument10 pagesThe Audio Pages: Simple Class-A AmplifierDaniel Scardini100% (1)

- Chapter 1Document72 pagesChapter 1Chittira ManoharenNo ratings yet

- SD6109Document10 pagesSD6109Alonso Corado100% (1)

- Chapter 5Document17 pagesChapter 5firomsaguteta12No ratings yet

- AD797 DatasheetDocument20 pagesAD797 Datasheetolle_elgonnoNo ratings yet

- ST - Joseph College of Engineering: SriperumbudurDocument45 pagesST - Joseph College of Engineering: SriperumbudurSuryaNo ratings yet

- ES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierDocument7 pagesES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierAhmed SalehNo ratings yet

- TRX Klopik Main Board V 2.1 ENGDocument5 pagesTRX Klopik Main Board V 2.1 ENGȺɌįfNo ratings yet

- High Performance Multi-Channel High-Speed IO Circuits PDFDocument91 pagesHigh Performance Multi-Channel High-Speed IO Circuits PDFVăn CôngNo ratings yet

- Asahi Kasei Microdevices AK4637EN - C2649367Document96 pagesAsahi Kasei Microdevices AK4637EN - C2649367Artur SchmidtNo ratings yet

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WDocument13 pagesClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428No ratings yet

- Utc Tea1062/1062A Linear Integrated Circuit: Low Voltage Telephone Transmission Circuit With Dialler InterfaceDocument14 pagesUtc Tea1062/1062A Linear Integrated Circuit: Low Voltage Telephone Transmission Circuit With Dialler InterfaceSai KrishnaNo ratings yet

- LM1868 AM/FM Radio System: General Description FeaturesDocument12 pagesLM1868 AM/FM Radio System: General Description Featuresvali dNo ratings yet

- Features Description: SBOS014Document15 pagesFeatures Description: SBOS014Paolo RamírezNo ratings yet

- Rocktron Hush Super CDocument13 pagesRocktron Hush Super CawaplaxNo ratings yet

- PrelimDocument26 pagesPrelimeun mun kang100% (3)

- Sige HBT Type: TransistorsDocument4 pagesSige HBT Type: TransistorsPhong DoNo ratings yet

- Manual Digital 400.4 Evox Ingl Rev10!1!1Document17 pagesManual Digital 400.4 Evox Ingl Rev10!1!1Jean cavionNo ratings yet