Professional Documents

Culture Documents

Reconfigurable FIR Filter Design Using DA Algorithm For Sand Monitoring System

Uploaded by

Zameema ZanbakhOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Reconfigurable FIR Filter Design Using DA Algorithm For Sand Monitoring System

Uploaded by

Zameema ZanbakhCopyright:

Available Formats

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

Reconfigurable FIR Filter Design using DA

Algorithm for Sand Monitoring System

Harsh Sharma1, Rajesh Mehra2

M.E. Scholar, Dept. of ECE, NITTTR, Chandigarh, India1

Associate Professor, Dept. of ECE, NITTTR, Chandigarh, India2

ABSTRACT: In the oil industry Sand analysing system is used toovercome the problem of equipment deterioration

and production failure. For the measurement of sand production in oil and gas systems the effective design and

implementation is done using FPGA as real time application. The analysing system consists of two acoustic sensors for

the measurement of assessing the impact of sand along with one Doppler sensor to measure the pace of sand particles.

For the actual time information acquisition and processing the system is implemented using FPGA. For the high

accuracy measurement of sand production Fully Parallel, Fully Serial and DA architecture are implemented. DA

architecture has better performance than other architectures as it uses Multiplier-less technology which increases the

speed of the system (136.049 MHz). The proposed cost effective sand analysing system can achieve high accuracy.

KEYWORDS: Distributive Arithmetic (DA), Finite Impulse Response (FIR) filter, Reconfigurable filter, Field

Programmable Gate Array(FPGA).

I.INTRODUCTION

In the oil organizations, to shield the gear from the harm brought on by sand disintegration system utilizes the sand

examining framework to enhance the unwavering quality and precision. Sand disintegration can be observed and

distinguished by the Acoustic based and Doppler based framework. To maintain a strategic distance from the breaking

down component into the pipe the system utilizes acoustic based system. The measure of sand creation which is

measured by examining the effect brought on because of the striking of sand on the dividers of pipe. The sand

gathering rate is measured in gram/sec. The disintegration based strategy utilized as a part of the framework is to

investigate the divergence in the insubordination as stream of oil goes from the sensor based funnels. To store the

uniqueness in the disobedience of the components (examining) which was brought about in light of the diminishing in

their width because of sand disintegration.This framework examinations straightforwardly the particles and not delicate

to the clamour[1, 2].

For the sand dissecting system has two strategies yet both have a few inadequacies. In acoustic based framework, as it

is inhumane to temperature so it can't achieve the genuine time dissecting, as here the data is gathered at MHz level and

data is handled utilizing signal preparing device. Encourage, in framework which depends on disintegration, that

framework is unmanageable for the long keep running as it is very delicate to the temperature and precision. The

consistent handling of the data is unrealistic because of the huge accumulated dataand which is to be prepared in a short

interim of time. The acoustic based framework is affected by the ecological commotion as wind blow and rain drops,

operation of compressors and pumps. This business investigating framework brings about the imperfect sand location

brought about by close-by unsettling influences in the field, advancing the false ready.

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6138

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

Fig.1. Sand Monitoring System[1]

The field programmable entryway exhibit (FPGA) is profoundly reconfigurable and quick, permitting fast prototyping

of new strategies and direct the framework for appraisal and real world applications. It is actualized for such a broad

utilization of infinite impulse response (IIR) channel application, ionizing radiation discovery , and vibrational studies

for modern applications for ecological mindfulness , among others[3]-[5]. To effortlessly coordinate the modules, a

FPGA based outline is utilized for a compelling framework, used to grasp the data handling utilized by different control

and dissecting framework. To direct the control and examining for different applications coordinated frameworks in

light of FPGA are utilized, for example, reconfiguration and blame recognition for power electronic converters , data

securing and breaking down for multichannel frameworks, investigation and dissecting of wavelet bundles[6, 7].

II.DISTRIBUTED ARITHMETIC ALGORITHM

Distributed Arithmetic (DA) is a slow technique due to its bitserial nature. When the number of vector elements is

somewhat same as of wordsize, DA is very fast, as it `places’ROM look-ups over the explicit multiplications, which is

an efficient technique for the implementation of Field Programmable Gate Arrays (FPGAs). In DA, multiplications are

rearranged and mixed such that, the arithmetic becomes “distributed” through the structure rather than being “lumped”

Area savings from using DA can be up to 80% in DSP hardware designs. While distributed arithmetic technique itself

has been around for more than 30 years, interest in this has been invigorated by the use of Field Programmable Gate

Arrays (FPGAs) for DSP because of DA implementation in FPGAs, one can exploit memory in FPGAs to execute the

MAC operation [8, 9].

DA based algorithm is used when long convolution and large order filter is to implemented. In various convolutions

one input is sample and another is fixed. The DSP algorithm uses DA computation for digital convolution. In this

method it saves the pre-calculated results in the memory element so as to produce quicker outputs as compare to

multiplier- accumulator based design. But memory requirement is increased with increase in convolution order. Due to

the systolic decomposition scheme for the DA computation it provides area time trade off because due to smaller

address length the memory size is reduced but complexity and latency is increased[10].

Distributed algorithm is used for the realisation of FIR and IIR filter. It performs dot product and weighted sum of

products operations. It is a influential tool for FPGA design because it reduces the size of parallel hardware multiply –

accumulate. The constant coefficient of FIR filter are stored in Look-up-table in DA algorithm .2k is the size of look up

table filter tap is indicated by k , due to increase in filter taps number LUT size also increases offset binary code(OBC)

is used to reduce the size of LUT. In many Applications MAC(Multiplier and Accumulator) based FIR filter is used but

in DA based method MAC is replaced by LUT causes power and area efficiency. Using DA based method multiplier

fewer Filters is designed using FPGA. Distributed arithmetic computation is bit serial, it replaces multiply and

accumulate operations by set of addition along with shifting operations. The fundamental operations required are a

series of look-up tables, subtraction, additions and shifts of the input data sequence. all possible partial products are

stored in the Look Up Table (LUT) over the filter coefficient space[11].

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6139

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

Field Programmable Gate Array:It is a coordinated circuit which is utilized by the prerequisite of the client. FPGAs

execution in different fields and its proficiency makes it appropriate for operable in different fields.It can join million

numbers of doors, memory squares and DSP units. Its simple programming makes it dependable for the use. It

underpins parallelism because of which many number of procedures should be possible at the same time. An

opportunity to-showcase is diminished which is thought to be its greatest accomplishment. FPGA can be customized

utilizing the VERILOG Language and HDL Language for the specific applications. In FPGA, its throughput limit is

high as contrast with the traditional processors like DSP and its acknowledgment cost is additionally less. FPGA

likewise contains different pieces like ALUfor the AND and XOR operation, flip-flops as memory elements,

interconnections using wires, logic blocks. Soft Microprocessor can be implemented by FPGA like Altera Nios II and

Xilinx Micro blaze. FPGA can also be used as controlling device and A/D conversion control module, synchronization

and modulating signal generation module [12].

III. FIR FILTER DESIGN SIMULATION

Generally digitals filters can be implemented using two methods: Finite Impulse Response(FIR) and Infinite Impulse

Response(IIR). FIR filters are generally non-recursive in nature, of the form

y(n)=h(0)x(n) + h(1)x(n-1) +…+ h(n-1)x(1) + h(n)x(0) (1)

Fir filter is generally stable and its phase can be exactly linear.

Figure 2: Block Diagram of FIR filter.

FIR is generally BIBO (“bounded-input, bounded-output”) stable[12].In FIR filter no nonzero pole exist in the transfer

function. It is simple to realize and can be intended to have linear phase property but on the other hand IIR filter is

recursive in nature and sometimes not stable. In IIR filter nonzero pole exists in the transfer function and Lowers the

filter order than a FIR filter. It generally has nonlinear phase property.

Fig 3: Block diagram of IIR Filter.

The filter which is to be designed in the paper is FIR band stop filter implemented on Kaiser Window having Filter

Order 78 and Shape Parameter(β) given as 3.872, Sampling

Frequency(Fs)is given as 1200 kHz and first cut off frequency is 510 kHz and other cut off frequency is 550 kHz.

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6140

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

Fig. 4: Magnitude Response of FIR Filter

Fig. 5: Phase Response of FIR Filter

Fig. 6: Impulse Response of FIR Filter Fig. 7: Pole-Zero Response of FIR Filter

IV.HARDWARE SYNTHESIS

For better results, proper selection of methodology is required. The selection of parameters and the architecture used

plays a vital role in designing. The hardware can be synthesized in various ways like by using different architecture like

fully parallel, fully serial, DA, etc and by varying different parameters of the filter o be designed. In this paper, system

is using DA, fully parallel and fully serial architecture for the designing of filter.

Distributive Arithmetic: Distributed Arithmetic (DA) is aslow technique due to its bit serial nature. When the number

of vector elements is somewhat same as of word size[11], DA is very fast, as it `places’ ROM look-ups over the

explicit multiplications, which is an efficient technique for the implementation of Field Programmable Gate Arrays

(FPGAs). In DA, multiplications are rearranged and mixed such that, the arithmetic becomes “distributed” through the

structure rather than being “lumped” „ Area savings from using DA can be up to 80% in DSP hardware designs „

While distributed arithmetic technique itself has been around for more than 30years, interest in this has been

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6141

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

invigorated by the use of Field Programmable Gate Arrays (FPGAs) for DSP „ because of DA implementation in

FPGAs, one can exploit memory in FPGAs to execute the MAC operation [14].

DA based algorithm is used when long convolution and large order filter is to implemented

Fig.8: DA Algorithm for FIR Filter[14]

Fully Parallel FIR filter design: In fully parallel architecture,it is basically designed fr the cost effective circuits

having smaller filter order, which in turns requires less number of multipliers to carry out the equation of filter[14,15].

Mathematically, the transfer function is given by:

H(z) = C + ∑ Hk(z) (2)

(Summation varies from n=1 to k.)

In equation (2), it is generally the basic equation representation of the FIR filter. The k in the above equation is the

integer part of (N+1)/2.

The fully parallel architectures are basically used for high speed operable filter designing.

Fig. 9: Parallel-Form of IIR filter

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6142

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

Fully serial: In fully serial architecture, it is very simple forimplementation purpose, as in this architecture the output of one

stage becomes the input of next stage[17, 18].

Fig. 10: Serial form of FIR filter

The fully serial architecture is quite slow in nature as it follows step wise operation.

The design is realized on Xilinx Spartan 3AN XC700AN device of FPGA in Verilog Language. On the basis of figure 12

comparison the speed of different architecture as frequency of DA architecture is more than fully serial and fully parallel

architecture. In figure 10 there is a comparison of number of slices flip-flop used and number of LUTs used is depicted between

DA, Fully Serial and Fully Parallel Architecture.

V. RESULTS

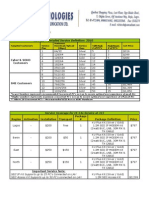

Table 1. Utilization Table

Resources Fully serial Fully DA

parallel

No of slice ff 557 1166 3018

4 input 344 784 4963

LUTs

Bonded 28 28 52

IOBs

MULT 1/20 20/20 -

18x18 SIOs

Frequency 74.478MHz 124.331MHz 136.049MHz

Table 1

Fig. 11: Speed Comparison of different architecture

Fig.12: Resource Comparison different architectures

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6143

ISSN (Print) : 2320 – 3765

ISSN (Online): 2278 – 8875

International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering

(An UGC Approved Journal)

Website: www.ijareeie.com

Vol. 6, Issue 8, August 2017

Fig. 13: Input Waveform for DA architecture

VI.CONCLUSION

The proposed method compares fully serial, fully parallel and DA architecture and found that the DA based filter is

more speedy in terms of frequency (136.049MHz) and also uses multiplier less feature. The DA architecture also

utilizes less time for the operation i.e. 7.350ns. In case of fully serial architecture the number of LUTs required will be

less and also number of slice flipflop requires is smallest in fully serial architecture as compared to DA. Area efficiency

will be high using fully serial method but speed of operation is less. This proposed filter is used in high accuracy

measurement of sand production system.

REFERENCES

[1] Xi-Yue Xiang, ItthichokJangjaimon, MohammadMadani and Nian-Feng Tzeng “A Reliable and Cost-Effective Sand Monitoring System

ontheFieldProgrammable Gate Array (FPGA),” IEEE Transactions on Instrumentation And Measurement, Vol. 62, No. 7, pp1870-

1882 , July 2013

[2] L. Contreras-Medina, R. de Jesus Romero-Troncosco, E.Cabal-Yepez, J. de Jesus Rangel-Magdaleno, and J. R.Millan-Almaraz,“FPGA-

basedmultiple-channelvibration analyzer for industrial applications in induction motor failure detection,” IEEE Transaction onInstrumentation

and Measurement, Vol. 59, No. 1, pp. 63–72, January 2010.

[3] M. Abdallah, O. Elkeelany, and A. Alouani, “A low-coststand-alone multichannel data acquisition, monitoring, and archival system with on-

chip signal preprocessing,”IEEE Transaction on Instrumentation and Measurement, Vol. 60, No. 8,pp. 2813–2827, August 2011.

[4] T. Buerkle, J. B. LaMeres, T. J. Kaiser, E. Gowens, L.Smoot, T.Heetderks, K. Schipf, L. Clem, S. Schielke, and R. Luhr, “Ionizing

radiation detector for environmental awareness in FPGA-based flight computer,” IEEE Sensors J., Vol. 12, No. 6, pp. 2229–2236, June 2012.

[5] M. Shahbazi, P. Poure, S. Saadate, and M. R. Zolghadri, “FPGA-based fast detection with reduced sensor count fora fault-tolerant three-phase

converter,” IEEE Transaction on Industrail Information, to be published.

[6] ].http://ijsetr.org/wp-content/uploads/2014/04/IJSETR-VOL-3-ISSUE-4-729-735.pdf Vol. 3, No. 4, pp. 729-735,April 2014.

[7] A. Peled and B. Liu, A new hardware realization of digital filters, IEEE Transactions on Acoustics, Speech, and Signal Processing, Vol.

ASSP-22, No. 6, pp. 456-462, December 1974.

[8] P. K. Meher, “Hardware-efficient systolization of DA-based calculation of finite digital convolution,” IEEETransaction Circuits System II,

Exp. Briefs, Vol. 53, No. 8, pp. 707–711, August 2006.

[9] S. A. White, “Applications of distributed arithmetic todigital signal processing: A tutorial review,” IEEE ASSP Magazine, Vol. 6, No. 3,

pp. 4–19,July 1989.

[10] T. Atalık, M. Deniz, E. Koc, C.O. Gercek, B. Gultekin, M. Ermis, and I. Cadırcı, “Multi-DSP and-FPGA basedFully-Digital Control System

for Cascaded Multilevel Converters used in FACTS Applications,” IEEE Transaction Industrial Informatics., volume- 8, Issue no. 3, pp. 511–

527, August 2012.

[11] RanjeetaVerma , Pooja Singh and Rajesh Mehra, “Resource Estimation for Design of IIR Filters usingPolyphase Decomposition”, Proc. of

International Conference on Emerging Trends in Engineering and Technology, DOI: 03.AETS.2013.3.42.

[12] Sunil Kumar Yadav, Rajesh Mehra, “Analysis of FPGA Sunil Kumar Yadav, Rajesh Mehra, “Analysis of FPGABased Recursive Filter Using

Optimization Techniques for High Throughput”, International Journal ofEngineering and Advanced Technology (IJEAT), ISSN:

2249 – 8958, Volume-3, Issue-4, April 2014

[13] Harish V. Dixit, Dr.Vikas Gupta, “ IIR filters using Xilinx System Generator for FPGA Implementation”, International Journal of Engineering

Research and Applications (IJERA) ISSN: 2248-9622,com Vol. 2, Issue 5, September- October 2012, pp.303-307.

[14] Sang Yoon park &Pramod Kumar Meher, “EfficientFPGA and ASIC Realizations of a DA-Based Reconfigurable FIR Digital Filter”

IEEE transactions on circuits and systems-II. Vol 61, No 07, July 2014.

[15] Sunil Kumar Yadav, Rajesh Mehra“ Analysis of Different IIR Filter Based on Implementation Cost Performance” International Journal of

Engineering and Advance Technology, ISSN: 2249 – 8958, Volume-3, pp. 267-270, Issue-4, April 2014.

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2017.0608027 6144

You might also like

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesFrom EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNo ratings yet

- Efficient Sphere Detector Algorithmfor Massive MIMOusing GPUHardware AcceleratorDocument13 pagesEfficient Sphere Detector Algorithmfor Massive MIMOusing GPUHardware AcceleratorTiến Anh VũNo ratings yet

- Parallel Field Programmable Gate Array Implementation of The Sum of Absolute Differences Algorithm Used in The Stereoscopic SystemDocument10 pagesParallel Field Programmable Gate Array Implementation of The Sum of Absolute Differences Algorithm Used in The Stereoscopic SystemTELKOMNIKANo ratings yet

- FPGA Based Area Efficient Edge Detection Filter For Image Processing ApplicationsDocument4 pagesFPGA Based Area Efficient Edge Detection Filter For Image Processing ApplicationsAnoop KumarNo ratings yet

- FPGA Implementation of ARM Processor: November 2014Document9 pagesFPGA Implementation of ARM Processor: November 2014Nana Arbab AliNo ratings yet

- 142 - DENSITY BASED TRAFFIC LIGHT - N - DC - Same PDFDocument7 pages142 - DENSITY BASED TRAFFIC LIGHT - N - DC - Same PDFRamadan DurakuNo ratings yet

- Design and Implementation of 6-Tap FIR Filter Using MAC For Low Power ApplicationsDocument8 pagesDesign and Implementation of 6-Tap FIR Filter Using MAC For Low Power ApplicationsIJRASETPublicationsNo ratings yet

- A Low Power High Speed Accuracy Controllable Approximate Multiplier DesignDocument8 pagesA Low Power High Speed Accuracy Controllable Approximate Multiplier DesignIJRASETPublicationsNo ratings yet

- Design and Optimize Substation Grounding Grid Based On Ieee Std. 80 - 2000 Using Gui and Matlab CodesDocument2 pagesDesign and Optimize Substation Grounding Grid Based On Ieee Std. 80 - 2000 Using Gui and Matlab CodesDp PdNo ratings yet

- Approximative Signed Wallace Tree Multiplier Using Reversible LogicDocument7 pagesApproximative Signed Wallace Tree Multiplier Using Reversible LogicIJRASETPublicationsNo ratings yet

- Approximative Signed Wallace Tree Multiplier Using Reversible LogicDocument7 pagesApproximative Signed Wallace Tree Multiplier Using Reversible LogicIJRASETPublicationsNo ratings yet

- Ijecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)Document10 pagesIjecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)IAEME PublicationNo ratings yet

- Design and Analysis of A Meander Line Cornered Microstrip Patch Antenna With Square Slotted EBG Structure For ISM/WLAN ApplicationsDocument11 pagesDesign and Analysis of A Meander Line Cornered Microstrip Patch Antenna With Square Slotted EBG Structure For ISM/WLAN ApplicationsVishnu PriyaNo ratings yet

- 46 PDFDocument8 pages46 PDFGeneral ZodNo ratings yet

- Implementation of 4x4 Data Bit Multiplier Using Dadda Algorithm and Optimized Full AdderDocument6 pagesImplementation of 4x4 Data Bit Multiplier Using Dadda Algorithm and Optimized Full AdderIJRASETPublicationsNo ratings yet

- Comparison of Reactive and Hybrid Routing Protocols in MANET Networks Using FTP ApplicationsDocument7 pagesComparison of Reactive and Hybrid Routing Protocols in MANET Networks Using FTP ApplicationsDso AnakpanahNo ratings yet

- 39 EfficientDocument7 pages39 EfficientHarryNo ratings yet

- Review of Broadband Techniques For Microstrip Patch AntennaDocument5 pagesReview of Broadband Techniques For Microstrip Patch AntennaLeena Rohan MehtaNo ratings yet

- Design of Reconfigurable Antenna For 5G ApplicationsDocument32 pagesDesign of Reconfigurable Antenna For 5G ApplicationsIJRASETPublicationsNo ratings yet

- Applsci 12 09599 v2Document14 pagesApplsci 12 09599 v2Ťüšhâř ĶêšãvâñNo ratings yet

- High Speed and Area Efficient Scalable N-Bit DigitDocument9 pagesHigh Speed and Area Efficient Scalable N-Bit DigitN Nagalakshumma GCETNo ratings yet

- 2021 - A 3.3 Gbps CCSDS 123.0-B-1 Multispectral Amp Hyperspectral Image Compression Hardware Accelerator On A Space-Grade SRAM FPGADocument14 pages2021 - A 3.3 Gbps CCSDS 123.0-B-1 Multispectral Amp Hyperspectral Image Compression Hardware Accelerator On A Space-Grade SRAM FPGASaru 2002No ratings yet

- Solar Data Logger: NtroductionDocument7 pagesSolar Data Logger: NtroductionShubhamNo ratings yet

- Solar Data LoggerDocument7 pagesSolar Data LoggerIJSTENo ratings yet

- Batch 25Document18 pagesBatch 25ShabbirNo ratings yet

- Fpga Based High-Speed A-Oms Lut & Fir System Design: Research ArticleDocument4 pagesFpga Based High-Speed A-Oms Lut & Fir System Design: Research ArticleSowmya PNo ratings yet

- A Data-Driven Approach IOTDocument12 pagesA Data-Driven Approach IOTDominik AntunovicNo ratings yet

- Vardhini 2021Document7 pagesVardhini 2021Abdelkbir WsNo ratings yet

- WDMA Optical System Designing With Simulating Tools and CodesDocument3 pagesWDMA Optical System Designing With Simulating Tools and CodeserpublicationNo ratings yet

- Sigma Delta Modulators: A Review: ArticleDocument10 pagesSigma Delta Modulators: A Review: ArticlevivekNo ratings yet

- Review On Distributed Canny Edge Detectorusing FpgaDocument8 pagesReview On Distributed Canny Edge Detectorusing FpgaSimrandeep SinghNo ratings yet

- Study On Intelligent Automatic Vehicle Accident Prevention and Detection SystemDocument5 pagesStudy On Intelligent Automatic Vehicle Accident Prevention and Detection Systemvalchuks2k1No ratings yet

- Fin Irjmets1680116934Document4 pagesFin Irjmets1680116934kasturi haseNo ratings yet

- Design and Implementation of PID Controller Using HDL On FPGADocument9 pagesDesign and Implementation of PID Controller Using HDL On FPGAcointoinNo ratings yet

- Adaptive Air Quality Sensing Using Machine LearningDocument10 pagesAdaptive Air Quality Sensing Using Machine LearningIJRASETPublicationsNo ratings yet

- An Energy-Efficient Routing Protocol For The Internet of Things Networks Based On Geographical Location and Link QualityDocument13 pagesAn Energy-Efficient Routing Protocol For The Internet of Things Networks Based On Geographical Location and Link QualityHanaw BabashexNo ratings yet

- Comparative Study of Sewer Version 3.0 and Sewergems V8I Softwares For Sanitary Sewer Network DesignDocument6 pagesComparative Study of Sewer Version 3.0 and Sewergems V8I Softwares For Sanitary Sewer Network DesignsunainaknoufalNo ratings yet

- Implementationof Time Efficient VLSI Designusing Kogge Stone AdderDocument6 pagesImplementationof Time Efficient VLSI Designusing Kogge Stone AdderIJRASETPublicationsNo ratings yet

- FFT Spectrum Analyzer Using Goertzel FilterDocument6 pagesFFT Spectrum Analyzer Using Goertzel Filterdell911100% (1)

- Journal 1Document8 pagesJournal 1mkhNo ratings yet

- Simulation and Implemetation of High-Speed Data Transmission Over Aurora Protocol Using FPGADocument7 pagesSimulation and Implemetation of High-Speed Data Transmission Over Aurora Protocol Using FPGAIJRASETPublicationsNo ratings yet

- A Reconfigurable Time Multiplexed Multichannel ADC Model For Efficient Data AcquisitionDocument4 pagesA Reconfigurable Time Multiplexed Multichannel ADC Model For Efficient Data Acquisitionaakashbari.ec20No ratings yet

- HIMAKETHANADocument88 pagesHIMAKETHANACSE DEPARTMENTNo ratings yet

- Design and Development of An Arduino Based Data Logger For Photovoltaic Monitoring SystemDocument6 pagesDesign and Development of An Arduino Based Data Logger For Photovoltaic Monitoring SystemDeepak ChaharNo ratings yet

- 2023 Influence Analysis of Director's Elements On The Circular Yagi Disc Antenna Performance at 1.8 GHZDocument9 pages2023 Influence Analysis of Director's Elements On The Circular Yagi Disc Antenna Performance at 1.8 GHZEd ItrNo ratings yet

- An Efficient, Optimized and Solar Based Automatic Irrigation System Using GSM ModuleDocument6 pagesAn Efficient, Optimized and Solar Based Automatic Irrigation System Using GSM ModuleIJRASETPublicationsNo ratings yet

- Sensors: An FPGA Based Tracking Implementation For Parkinson's PatientsDocument24 pagesSensors: An FPGA Based Tracking Implementation For Parkinson's Patientsm_gandalfNo ratings yet

- 10 18100-Ijamec 1058257-2193753Document4 pages10 18100-Ijamec 1058257-2193753saud.ismail.etcn139No ratings yet

- Smart Antenna SystemsDocument7 pagesSmart Antenna SystemsIJRASETPublicationsNo ratings yet

- 5G Campus Networks A First Measurement StudyDocument21 pages5G Campus Networks A First Measurement StudyGANGLIAN DRAMANo ratings yet

- Aurdino Based Automatic Plant Watering System With Internet of ThingsDocument8 pagesAurdino Based Automatic Plant Watering System With Internet of ThingsAanam FathimaNo ratings yet

- Remote Distributed Monitoring System of Switched Reluctance MotorDocument15 pagesRemote Distributed Monitoring System of Switched Reluctance Motorعبد الكريم ملوحNo ratings yet

- IOT Based Industrial Plant Safety Gas Leakage DetectionDocument6 pagesIOT Based Industrial Plant Safety Gas Leakage DetectionIJRASETPublicationsNo ratings yet

- Lab STICC UBO Recherche Post Doc Pour Projet Druide 1573353028 PDFDocument1 pageLab STICC UBO Recherche Post Doc Pour Projet Druide 1573353028 PDFSunil SharmaNo ratings yet

- Designing of IIR Filter Using Radix-4 Multiplier by Precharging TechniqueDocument8 pagesDesigning of IIR Filter Using Radix-4 Multiplier by Precharging TechniqueEditor IJTSRDNo ratings yet

- IOT Based Vehicle Tracking & Vehicular Emergency System-A Case Study and ReviewDocument12 pagesIOT Based Vehicle Tracking & Vehicular Emergency System-A Case Study and ReviewJay Prakash RaikaNo ratings yet

- Low Power Digital Image Compression Using Approximate AddersDocument12 pagesLow Power Digital Image Compression Using Approximate AddersIJRASETPublicationsNo ratings yet

- (IJCST-V9I2P10) :DR - Shine N DasDocument6 pages(IJCST-V9I2P10) :DR - Shine N DasEighthSenseGroupNo ratings yet

- Mutual Coupling Suppression Between Two Closely Placed Patch Antennas Using Higher-Order ModesDocument9 pagesMutual Coupling Suppression Between Two Closely Placed Patch Antennas Using Higher-Order ModesSuman NelaturiNo ratings yet

- C-Band and Ku-Band Price ListDocument9 pagesC-Band and Ku-Band Price ListOlajide J. OlawuyiNo ratings yet

- Gain, Attenuation, AM Modulation Index, and AM PowerDocument9 pagesGain, Attenuation, AM Modulation Index, and AM PowerChristine Alderama MurilloNo ratings yet

- PPN Installation Guide Rev 1.5 PDFDocument23 pagesPPN Installation Guide Rev 1.5 PDFpp1jlbr100% (1)

- Instruction Manual: Digital Proportional Radio Control SystemDocument60 pagesInstruction Manual: Digital Proportional Radio Control SystemSergio Gustavo StangaliniNo ratings yet

- 5G Antennas Comscope Webinar PDFDocument25 pages5G Antennas Comscope Webinar PDFuttuttimail100% (1)

- Xbee /Xbee-Pro RF Modules: Product Manual V1.Xex - 802.15.4 ProtocolDocument69 pagesXbee /Xbee-Pro RF Modules: Product Manual V1.Xex - 802.15.4 ProtocolMounesh PanchalNo ratings yet

- Four Zone Mixer: Setup GuideDocument2 pagesFour Zone Mixer: Setup GuideNico QuieroNo ratings yet

- Tutorial Diagnostics Randall PDFDocument84 pagesTutorial Diagnostics Randall PDFkfathi55No ratings yet

- High Sensitivity Crystal SetDocument3 pagesHigh Sensitivity Crystal SetCelestial ShamanNo ratings yet

- Sav-331 PDFDocument5 pagesSav-331 PDFAbolfazl Yousef ZamanianNo ratings yet

- Test.m Fmod.m SPLL.M: %how To Use It: Simply Copy The 3 Files To A Matlab Path Directory and Type "Test". The Test.mDocument9 pagesTest.m Fmod.m SPLL.M: %how To Use It: Simply Copy The 3 Files To A Matlab Path Directory and Type "Test". The Test.mAllanki Sanyasi RaoNo ratings yet

- Wirless Digital CommunicationDocument4 pagesWirless Digital CommunicationStalin BabuNo ratings yet

- DMR Repeaters & SystemsDocument5 pagesDMR Repeaters & SystemsJoseph SharonNo ratings yet

- Research Issues and Challenges in Wireless Networks: An OverviewDocument2 pagesResearch Issues and Challenges in Wireless Networks: An OverviewInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Physical Layer ProceduresDocument145 pagesPhysical Layer ProceduresTanzyy.2018No ratings yet

- Autoplug Fuel ProbesDocument2 pagesAutoplug Fuel ProbesTINANo ratings yet

- Microwave Engineering-IntroductionDocument35 pagesMicrowave Engineering-IntroductionKobid Karkee100% (1)

- Wimax ReportDocument21 pagesWimax Reportmadhanmaddy777No ratings yet

- DSP LabworkDocument10 pagesDSP Labworksachinshetty001No ratings yet

- Calculating PIM 2018Document16 pagesCalculating PIM 2018Владан ДакићNo ratings yet

- L3Document46 pagesL3DomsNo ratings yet

- Smitch ChartDocument3 pagesSmitch ChartBharat ChNo ratings yet

- 01 - DWDM BasicsDocument52 pages01 - DWDM Basicsmutungwa50% (2)

- 2g& 3G PagingDocument13 pages2g& 3G PagingJoão RamosNo ratings yet

- TM 11-5820-919-40-2 - Radio - Set - AN - PRC-104 - 1986 PDFDocument106 pagesTM 11-5820-919-40-2 - Radio - Set - AN - PRC-104 - 1986 PDFWurzel1946No ratings yet

- WLAN Network Planning GuideDocument107 pagesWLAN Network Planning GuideJoel Tejada LatorreNo ratings yet

- Blind System IdentificationDocument18 pagesBlind System IdentificationlalusebanNo ratings yet

- 350 Fall 12 FinalDocument10 pages350 Fall 12 Finalchuck212No ratings yet

- Installation Manual Operation Manual: Emergency Locator TransmitterDocument60 pagesInstallation Manual Operation Manual: Emergency Locator TransmitterHaneet BhardwajNo ratings yet

- CH 3 Connected Devices and Protocols PDFDocument126 pagesCH 3 Connected Devices and Protocols PDFWahid AhmedNo ratings yet