Professional Documents

Culture Documents

Accurate Modeling of Submicron Symmetric-Load Ring Vcos

Uploaded by

JeffOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Accurate Modeling of Submicron Symmetric-Load Ring Vcos

Uploaded by

JeffCopyright:

Available Formats

Accurate Modeling of Submicron Symmetric-load Ring VCOs

M. Helena Fino*, António B. Leal **

*Department of Electrotechnical Engineering, FCT, hfino@ieee.org

** Chipidea - Microelectronica, S.A., www.chipidea.com

ABSTRACT the velocity saturation and mobility degradation,

This paper proposes an accurate model for submicron among others, must be accounted for. To

PMOS symmetric-load ring VCOs. The accuracy of overcome the inaccuracy of Shockley’s MOSFET

the model is achieved by adopting the Npower

model when applied to submicron circuits,

transistor model. The explicit dependency of the VCO

model on MOS technological parameters makes it Sakurai’s Npower model was proposed [2]. This

quite robust against technological evolution. The model has been successfully used in the derivation

simplicity and efficiency of the model as well as the of analytical expressions for evaluating delay and

accuracy of the results obtained make it suitable to be power dissipation in submicron CMOS gates [3-

integrated into an environment for the automatic 5].

design of VCOs

The previously proposed models for the ring

Index Terms – Ring VCO Models, Submicron Mofet VCOs considered in this paper, although quite

models simple, turn out to be rather innacurate when

applied to submicron technologies. In this paper

I. INTRODUCTION we propose de adoption of the Npower MOS

Voltage Controlled Oscillators (VCOs) are a key model as a basis for deriving ring VCO models.

element in PLLs. The design of VCOs is a Besides this introduction, this paper comprises

complex task since it involves the solution of seven additional sections. In Section II a brief

many design trade-offs depending on the description of Sakurai’s model is presented. In

application of the PLL. To make things worse, the Section III we present a brief description of a

simulation of VCOs is a very time consuming Python script, we have developed for evaluating

process, because transient circuit simulations must Npower parameters for a given technology. In

run long enough so that the steady state is Section IV ring VCOs are introduced. Section V

attained. This makes the design methodology describes previously proposed models and in

based on iterative simulations, usually adopted for Section VI we apply the Npower MOS model to

analog circuits, not practical for this class of deriving the VCO model and we note some

circuits. The development of efficient and reliable limitations of the model proposed. In Section VII

VCO models is therefore a key element for the a working example is presented. Section VIII is

automation of the circuit design. Besides accuracy dedicated to conclusions

and simplicity, models must easily adapt to the

rapid technology evolution. Such robustness can II. MOSFET MODELING FOR SUBMICRON

only be obtained if we develop models based on CIRCUITS

transistor level technological parameters.

The quadratic Shockley’s MOSFET model has In order to accurately characterize short-

been widely used as the basis for the analysis of channel circuits, Sakurai proposed the Npower

analog and digital circuits[1]. The simplicity of model where the MOS transistor behavior is

the model makes it amenable to be used as a basis described by equations 1 trough 6.

for derived formulas ranging from the small signal VTh = VT 0 + γ ( 2.φ F − V BS − 2.φ F ) (1)

models of MOSFET transistors up to more

complex formulas as amplifiers gain, bandwidth, V D SAT = K .(VGS − VTh )m (2)

pole zeros expressions in analog circuits. Should

we consider the digital world, we may enumerate I D SAT = W .B.(VGS − VTh )n (3)

Leff

such derived formulas as those used for evaluating

CMOS gate delay or power estimation. λ = λ0 − λ1.VBS (4)

Unfortunately, as the sizes of MOSFET ID = I D SAT .(1 + λ .VDS ) ⇐ VDS ≥ VDSAT (5)

transistors scale down, the quadratic model is no

longer applicable, for new physical effects such as

VDS V characteristics obtained with the model, over the

I D = I D SAT . 2 − . DS ⇐ VDS < VDSAT (6) characteristics obtained with Hspice.

VDSAT VDSAT

For illustration purposes we will consider the

For practical use on circuits employing current

case for obtaining MOS parameters needed for the

technologies, several points should be noted:

model of the VCO to be shown in the application

− VBS plays an important role in circuit example, in Section VII. There we consider a

characterization. VCO comprising 1.8V SMIC018 transistors with

− The border between Saturation and Triode is no sizes in table 1.

longer given by the simple expression TABLE 1

VGS − VTh but depends also on model parameters, TRANSISTOR SIZES FOR THE APPLICATION EXAMPLE

i.e., K and m. Switch (Nmos) Load (Pmos) Bias (Nmos)

− The dependency of Id on Vgs is no longer W = 50µ W = 5µ W = 30µ

L .66 L .5 µ L 2µ

quadratic. The power is n as stated in eq. (3). This

has severe implications not only in the static The parameters obtained for the VCO Load

behavior of circuits but in the dynamic behavior as transistors for the typical case, as well as for two

well, since expressions usually adopted for gm are additional corners, are shown in Table 2. In this

no longer valid. table we also show the values for the transistors

− The usually ignored dependency on VDS for the effective length, Lef, obtained from Hspice

TABLE 2

static behavior characterization of transistors in NPOWER MODEL PARAMETERS FOR 1.8V SMIC018 PMOS

the saturation region must now be taken into

Typical Corner Corner

account. Case C1 C2

Temperature 27 -40 125

III. AUTOMATIC GENERATION OF NPOWER Vdd 1.8 1.98 1.62

MODEL PARAMETERS Mos Model mos_tt mos_ff mos_ss

For the automatic generation of Npower MOS Lef (µ) . 4665 . 4542 . 4788

model parameters, we have developed a Python B(µ) 21.276 28.182 16.077

script. For the VCO model we will only use n 1.60 1.54 1.69

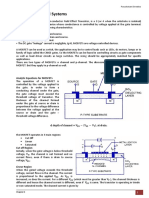

transistors with VBS=0, for the topology detailed K . 828 .884 .891

in Section IV. In this case, only six DC simulation m .770 .743 .795

points of Id(VDS,VGS), as illustrated in figure 1 λ0 .053 .054 .030

need to be evaluated [2]. Vt0 .462 .495 .428

Figure 2 shows the accordance of the

8.0E-04

Id(VDS,VGS)characteristics obtained with the

model, against those obtained with Hspice.

6.0E-04

ID(Vgs,Vds)

Id

4.0E-04

1.2E-02

2.0E-04

8.0E-03

0.0E+00 Vds

0.0 1.1 2.2 3.3

Id

4.0E-03

Fig. 1. Points for Npower model generation

To determine the model parameters (B, n, K, 0.0E+00

m, λ0 and Vt0), the program invokes Hspice for 0.0 0.6 1.2 1.8

Vds

performing a DC simulation of one transistor at

the six different points (automatically elected by

the program) and then, the algorithm described in Fig. 2. ID(VDS, VGS) for 1.8V SMIC018 PMOS

[2] is applied. A verification option is available,

transistor with W/Lµ=5/.5 : (-) simulated with

enabling the user to plot the Id(VDS,VGS)

Hspice, (*) from Npower model

IV. PMOS SYMMETRIC-LOAD RING VCOS inverse of the transconductance gm of one of the

two equally sized load transistors when biased at

Ring VCOs consisting of differential inverting the control voltage Vc. By considering the drain

stages, as illustrated in figure 3, have been current of one of the transistors given by eq. (9),

proposed [6]. taking the derivative with respect to Vc yields

eq.(10).

I D = (β 2)(Vc − Vt ) 2 (9)

Reff = gm−1 = (β (Vc −Vt) )−1 (10)

Combining the previous eq.s (7), (8) and (10)

Fig. 3. Differential buffers VCO structure we obtain eq. (11) for the VCO linear model.

β (Vc − Vt )

f osc = (11)

Each differential stage contains PMOS 2.N .C eff

symmetric loads as illustrated in figure 4 [7]. In [8] a new model is proposed, yielding more

accurate results for the case of small values of the

control voltage. This model considers the

effective resistance of the symmetric load as the

ratio between the maximum voltage swing, VLMax,

and ILmax,. Since by design constraints, the

maximum voltage swing equals the control

voltage, Reff is given by eq. 12, leading to the VCO

model represented in eq. 13

Vc

Reff = (12)

β .(Vc − Vt ) 2

β .(Vc − Vt ) 2

f osc = (13)

2.N .C eff .Vc

Fig. 4. VCO Symmetric loads differential buffer VI. NEW VCO MODEL

The bias current source, Ibias, is designed so

The proposed models rely on the quadratic

that the maximum voltage accross the symmetric

MOS model, thus leading to inaccurate results

load is equal to the control voltage Vc.

when submicron technologies are used. Much

more accurate results may be obtained if we

V. PREVIOUS VCO MODELS

consider Npower MOS model in the evaluation of

the effective resistance of the VCO symmetric

The frequency of oscillation of these ring loads. As the MOS transistors comprising the

oscillators is usually evaluated with eq.7, where symmetric loads have a null bulk source voltage,

tdelay is the propagation delay of each buffer stage the Npower model will resume to eq. 14, and eq.

f osc = (2.N .t delay )

−1

(7) 15, for transistors in saturation region.

The first model proposed for the VCO VTh = VT 0 (14)

comprising the delay cells represented in figure 4 I D = I D SAT .(1 + λ 0 .V DS ) ⇐ V DS ≥ V DSAT (15)

considers eq.(8) for the evaluation of tdelay where Using the previous equations we obtain eq.16

the effective buffer output capacitance, Ceff, and for the symmetric load effective resistance,

the effective resistance Reff of the symmetric load yielding the new VCO model in eq.(17)

are considered. −1

2.B.W (VC − VTh ) (1 + λ0 .Vc )

n

t delay = Reff .C eff (8)

Reff = (16)

In [7] Reff is considered as directly proportional Leff Vc

to the small signal resistance at the ends of the

swing range of the output voltage, and thus the

B.W (VC − VTh ) (1 + λ 0 .Vc )

n conditions as well as for granting the access to the

f osc = . (17) technology files, which made this work possible.

Leff Vc.N .C eff

The proposed model is based on an

2.2E+08

approximate expression for evaluating the

symmetric load effective resistance. To overcome

1.8E+08

this limitation, a charge-based analytical model

Frequency

which accounts for the symmetric load transistor

1.4E+08

operating regions should be derived. Yet, the

accuracy of the results we have obtained for

1.0E+08

several examples is quite good, thus making a

more complex model unnecessary.

6.0E+07

The second limitation of the model proposed is

1.0E+00 1.2E+00 1.4E+00 Vc

that it contains no information regarding the limits

of validity of the model. This additional

information will be considered in future work.

Fig. 5. Frequency vs. Vc for a 1.8V SMIC018

VII. APPLICATION EXAMPLE seven stage VCO: (*)Hspice; (__) New model; (__)

Model [8]

TABLE 3

As an application example we have considered

MAXIMUM AND AVERAGE RELATIVE ERRORS.

a seven-stage symmetrical load differential VCO.

Typical Corner C1 Corner C2

Each stage considered is illustrated in Figure 4, New Model New Model New Model

with the transistor sizes shown in Table 1. The Model [8] Model [8] Model [8]

results obtained for the typical case as well as for Av. 2.0% 13.0% 3.4% 16.0% 1.8% 3.8%

corners C1(upper lines) and C2 (lower lines) are Max 3.0% 24.0% 7.0% 29.4% 3.0% 9.0%

illustrated in figure 5.

In Table 3 we present the maximum and REFERENCES

average relative errors of results obtained from [1] W. Schokley, “ A Unipolar field effect transistor”,

proceedings of IRE, vol. 40, pp. 1365-1376, Nov. 1952

both models. From them we may see that the [2] T. Sakurai, A. R. Newton, “ A simple MOSFET Model

proposed model shows an average error in the for Circuit Analysis”, IEEE transactions on Electron

order of 3%, much smaller then what we obtain Devices, Vol. 38, Nº 4, pp. 887-893, April 1991.

with the model proposed in [8]. [3] L.Bisdounis, S. Nikolaidis, O. Koufopavlou, “ Analytical

Model for CMOS Short-Circuit Power Dissipation”,

Integrated Computer-Aided Engineering Journal, Vol. 5,

VIII. CONCLUSIONS Nº 2, Special issue on Low-power electronic systems, pp.

129-140, April 1998.

This paper described an accurate model for [4] Hamoui, N.Rumin, “ An Analytical Model for Current,

PMOS Symmetric Load ring VCOs. The adoption Delay and Power analysis of Submicrometer CMOS

of the Npower model for transistor Logic Circuits”, IEEE Transactions on Circuits and

Systems-II: Analog and digital Signal Processing,, Vol.

characterization enabled us to obtain a VCO Nº47, Nº10, pp. 999-1007, October 2000.

characterization producing quite accurate results [5] J.L.Rossello, J.Segura, “ Charge-Based analytical model

even for sub micrometer technologies. for the evaluation of power consumption in sub-

micrometer CMOS buffers”, IEEE transactions on

The automatic generation of the Npower Computer-Aided Design, Vol.21, Nº 4, pp. 433-448,

parameters granted us the straightforward April 2002.

generation of VCO models for any given [6] J.G. Maneatis, M. Horowitz “Precise Delay Generation

technology. The simplicity and accuracy of our using Coupled Oscillators”, IEEE Journal of Solid-State

Circuits, Vol. 28, Nº 12, December, 1993

model as well as its robustness against [7] J.G. Maneatis, “Low-Jitter Process-Independent DLL and

technological evolution makes it suitable for using PLL Based on Self-Biased Techniques”, in IEEE Journal

in the automation of VCO design. of Solid State Circuits, Vol. 31, No. 11, pp.1723-1732,

November 1996.

[8] T. H. Toifl, “Integrated Circuits for The Synchronization

ACKNOWLEDGMENT of High-Energy Physics Experiments”, PdD. Dissertation,

M. Helena Fino would like to thank Chipidea - Technische Universitat Wien, February 1999.

Microelectronica, S.A., for providing excellent working

You might also like

- Analytical Transient Response and Propagation Delay Model For Nanoscale CMOS InverterDocument4 pagesAnalytical Transient Response and Propagation Delay Model For Nanoscale CMOS InverterLohith DharavathNo ratings yet

- Automated Parameter Extraction and SPICE ModelDocument4 pagesAutomated Parameter Extraction and SPICE ModelkimjinNo ratings yet

- Challenges of MOS Analog Circuit Simulation With SPICEDocument5 pagesChallenges of MOS Analog Circuit Simulation With SPICEVinodNo ratings yet

- Analog - RF VLSI Design (ECE 503) (Makeup) PDFDocument2 pagesAnalog - RF VLSI Design (ECE 503) (Makeup) PDFRahul PinnamaneniNo ratings yet

- Chapter03 ExDocument10 pagesChapter03 ExKarthikeya VemparalaNo ratings yet

- Homework 2Document4 pagesHomework 2sissishinyNo ratings yet

- Mosfet CharacteristicsDocument12 pagesMosfet CharacteristicsNavaneethaan NathamoorthyNo ratings yet

- MOS IV Characteristics in Cadence VirtuosoDocument15 pagesMOS IV Characteristics in Cadence VirtuosoShafeey100% (2)

- Rabaey Exercises Collected PDFDocument64 pagesRabaey Exercises Collected PDFbatoolNo ratings yet

- Unit 3 - VLSI Design - WWW - Rgpvnotes.inDocument12 pagesUnit 3 - VLSI Design - WWW - Rgpvnotes.inPushpendra gourNo ratings yet

- 08 Antonio CerdeiraDocument57 pages08 Antonio CerdeiraMoaaz AhmedNo ratings yet

- EVL562 ECL523 Digital IC Design Dec2020Document3 pagesEVL562 ECL523 Digital IC Design Dec2020akash rawatNo ratings yet

- Dic 2021Document1 pageDic 2021akash rawatNo ratings yet

- CMOS DelayCal Alpha PowerLawDocument11 pagesCMOS DelayCal Alpha PowerLawSANT SARANNo ratings yet

- Evaluation of Modern MOSFET Models For Bulk-Driven ApplicationsDocument4 pagesEvaluation of Modern MOSFET Models For Bulk-Driven Applications1zxcNo ratings yet

- Experiment No. 1: Aim: Study of Tanner Tools THEORY: Tanner ToolsDocument24 pagesExperiment No. 1: Aim: Study of Tanner Tools THEORY: Tanner ToolsVarun GargNo ratings yet

- SBM 96Document6 pagesSBM 96Vivek AzadNo ratings yet

- Extracting Electrical and Physical Parameters From MOSFETsDocument4 pagesExtracting Electrical and Physical Parameters From MOSFETsJagan RamasamyNo ratings yet

- EE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THDocument4 pagesEE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THvedeshNo ratings yet

- 15 A - Cryo-CMOS - Voltage - Reference - in - 28-nm - FDSOIDocument4 pages15 A - Cryo-CMOS - Voltage - Reference - in - 28-nm - FDSOIBalaramamurty SannidhiNo ratings yet

- Modeling of SiC MOSFET in MatlabSimulinkDocument5 pagesModeling of SiC MOSFET in MatlabSimulinkDaniel Labiano AnduezaNo ratings yet

- Question Bank Vlsi Design MEC-020Document2 pagesQuestion Bank Vlsi Design MEC-020Sougata GhoshNo ratings yet

- MOSFET DC Ids-Vds Characteristic Curve and Spice Extraction of Small Signal Model ParametersDocument22 pagesMOSFET DC Ids-Vds Characteristic Curve and Spice Extraction of Small Signal Model ParametersRobert Tac-an Nericua100% (2)

- Nirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VDocument15 pagesNirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VPragya jhalaNo ratings yet

- IET Submission DoubleColumn Template PDFDocument9 pagesIET Submission DoubleColumn Template PDFWesley de PaulaNo ratings yet

- Laboratory 6: Models For MOS Devices: Part 3: Square-Law Parameter ExtractionDocument3 pagesLaboratory 6: Models For MOS Devices: Part 3: Square-Law Parameter Extractionabdallah04No ratings yet

- Ps 1Document5 pagesPs 1Seshareddy KatamNo ratings yet

- Antenna Diode Vlsi Operation Positive ChargeDocument21 pagesAntenna Diode Vlsi Operation Positive ChargeNegin HashemiNo ratings yet

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNo ratings yet

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsArchana TrivediNo ratings yet

- Transistor Wien Bridge Oscillator Circuit Using Transistor Simulation Using MultisimDocument5 pagesTransistor Wien Bridge Oscillator Circuit Using Transistor Simulation Using MultisimManju BhuvanNo ratings yet

- The Analog Behavior of Pseudo Digital Ring Oscillators Used in VCO ADCsDocument14 pagesThe Analog Behavior of Pseudo Digital Ring Oscillators Used in VCO ADCszhaohhhengNo ratings yet

- Sub-Pico Joule Switching High-Speed Reliable Cmos Circuits Are FeasibleDocument11 pagesSub-Pico Joule Switching High-Speed Reliable Cmos Circuits Are FeasibleKODOMNo ratings yet

- ECE124A F11 HW5 SolutionsDocument4 pagesECE124A F11 HW5 SolutionsPeter VerlangieriNo ratings yet

- GTU VLSI Question Bank Covers Design, Fabrication & CircuitsDocument4 pagesGTU VLSI Question Bank Covers Design, Fabrication & CircuitsAmish TankariyaNo ratings yet

- TOBB ETU Department of ELE ELE 224L Electronic Circuits Experiment 4 - MOSFET CircuitsDocument5 pagesTOBB ETU Department of ELE ELE 224L Electronic Circuits Experiment 4 - MOSFET CircuitsBugrahan UstundagNo ratings yet

- Fully-Differential High-Speed and High-Precision Operational Amplifier DesignsDocument9 pagesFully-Differential High-Speed and High-Precision Operational Amplifier DesignskimjimNo ratings yet

- Transistors 12700Document4 pagesTransistors 12700randyNo ratings yet

- Eee-Vii-Vlsi Circuits and Design (10ee764) - NotesDocument225 pagesEee-Vii-Vlsi Circuits and Design (10ee764) - Notessammy100% (1)

- Write Your Own Generic SPICE Power Supplies Controller ModelsDocument13 pagesWrite Your Own Generic SPICE Power Supplies Controller ModelssureshchattuNo ratings yet

- Multilevel Inverter With Reduced Number of Switches: Arun - Thorat@ritindia - EduDocument5 pagesMultilevel Inverter With Reduced Number of Switches: Arun - Thorat@ritindia - EduagastinNo ratings yet

- CMOS Inverter VTC and Noise Margin AnalysisDocument6 pagesCMOS Inverter VTC and Noise Margin Analysisujjwal mishraNo ratings yet

- Vlsi Design Question Bank EEC 703Document10 pagesVlsi Design Question Bank EEC 703selvi0412No ratings yet

- Cmos BooksDocument10 pagesCmos BooksMuthiah RajaNo ratings yet

- Electronics 08 01156 With CoverDocument18 pagesElectronics 08 01156 With Coverlravikumar.19.eeeNo ratings yet

- EECS141 Homework VTC and Transistor ModelingDocument18 pagesEECS141 Homework VTC and Transistor ModelingDevaraj SubrmanayamNo ratings yet

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - NotesDocument214 pagesEce-V-fundamentals of Cmos Vlsi (10ec56) - NotesNithindev Guttikonda0% (1)

- SiC Schottky Diode Modelling in SPICEDocument4 pagesSiC Schottky Diode Modelling in SPICEKrishna KumarNo ratings yet

- Monte Carlo Simulation With HSPICE - REVDocument4 pagesMonte Carlo Simulation With HSPICE - REVYicong LiNo ratings yet

- A Doubly Grounded Boost Seven Level PV Inverter Topology With Model Predictive ControllerDocument6 pagesA Doubly Grounded Boost Seven Level PV Inverter Topology With Model Predictive ControllerRodovarNo ratings yet

- Simple Vs Low Compliance Cascode Current Mirror: PART 1: Sizing ChartDocument12 pagesSimple Vs Low Compliance Cascode Current Mirror: PART 1: Sizing ChartAhmad KamalNo ratings yet

- Lab 323Document3 pagesLab 323deepak negiNo ratings yet

- Objective: "Introduction To Microwind and Analysis of Mosfets and Different Gates Implementation"Document8 pagesObjective: "Introduction To Microwind and Analysis of Mosfets and Different Gates Implementation"unity123d deewNo ratings yet

- Question BankDocument13 pagesQuestion BankRishi JhaNo ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Digital Power Electronics and ApplicationsFrom EverandDigital Power Electronics and ApplicationsRating: 3.5 out of 5 stars3.5/5 (3)

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Mat 540 Quiz 1 With AnswersDocument9 pagesMat 540 Quiz 1 With AnswersJeff100% (1)

- Mat 540 Quiz 2 With AnswersDocument10 pagesMat 540 Quiz 2 With AnswersJeff83% (6)

- Mat 540 Quiz 3 With AnswersDocument9 pagesMat 540 Quiz 3 With AnswersJeff100% (2)

- Mat 540 Quiz 5 With AnswersDocument9 pagesMat 540 Quiz 5 With AnswersJeff100% (5)

- Optimizing Transportation Costs with Excel SolverDocument14 pagesOptimizing Transportation Costs with Excel SolverJeff100% (1)

- Mat 540 Quiz 1 With AnswersDocument9 pagesMat 540 Quiz 1 With AnswersJeffNo ratings yet

- Mat 540 Quiz 4 With AnswersDocument10 pagesMat 540 Quiz 4 With AnswersJeff100% (2)

- Understanding the Historical Context and Philosophical Foundations of Modern Education SystemsDocument9 pagesUnderstanding the Historical Context and Philosophical Foundations of Modern Education SystemsJeffNo ratings yet

- PLL Tutorial Isscc 2004Document131 pagesPLL Tutorial Isscc 2004JeffNo ratings yet

- Cmos Charge-Pump Circuit With Positive Feedback For PLLDocument4 pagesCmos Charge-Pump Circuit With Positive Feedback For PLLJeffNo ratings yet

- PLL Frequency Synthesizers, Phase Noise and Wide BandDocument220 pagesPLL Frequency Synthesizers, Phase Noise and Wide BandJeffNo ratings yet

- Voltage-Supply (Voltage Display - LCD Panel) - TV Problems and Repair SolutionsDocument4 pagesVoltage-Supply (Voltage Display - LCD Panel) - TV Problems and Repair SolutionsverNo ratings yet

- Mosfet-Based Preamplifier For FM Radio Dxing: N.S. Harisankar, Vu3NshDocument2 pagesMosfet-Based Preamplifier For FM Radio Dxing: N.S. Harisankar, Vu3NshKuntaweeNo ratings yet

- MOSFET design and operationDocument44 pagesMOSFET design and operationAbdul KhaliqNo ratings yet

- Coimbatore Institute of TechnologyDocument3 pagesCoimbatore Institute of TechnologyMani BharathiNo ratings yet

- Chapter 12Document42 pagesChapter 12Felipe SouzaNo ratings yet

- GATE Questions on MOSFET, CMOS & Introduction to VLSI (1987-2014Document18 pagesGATE Questions on MOSFET, CMOS & Introduction to VLSI (1987-2014Elakkiya ENo ratings yet

- Lect4 Stick DiagramDocument23 pagesLect4 Stick Diagrammanicks369601No ratings yet

- Leakage CurrentDocument5 pagesLeakage CurrentImam WijayaNo ratings yet

- Moving To GAA FETsDocument11 pagesMoving To GAA FETsck maitiNo ratings yet

- Test Motherboard VRMs QuicklyDocument6 pagesTest Motherboard VRMs QuicklydtoxidNo ratings yet

- Chapter 9 Frequency Response of BJT & MosfetDocument54 pagesChapter 9 Frequency Response of BJT & Mosfetshubhankar palNo ratings yet

- Simulation of Single-ElectronDocument161 pagesSimulation of Single-Electronمزمل اقبالNo ratings yet

- ContinueDocument3 pagesContinueDavidNo ratings yet

- I R D S: Nternational Oadmap FOR Evices and YstemsDocument23 pagesI R D S: Nternational Oadmap FOR Evices and YstemsSnehaNo ratings yet

- M.E. Applied Electronics Curriculum RegulationsDocument21 pagesM.E. Applied Electronics Curriculum RegulationsRamya VNo ratings yet

- Three-Dimensional MBCFET As An Ultimate TransistorDocument3 pagesThree-Dimensional MBCFET As An Ultimate TransistorRàhuł MathiasNo ratings yet

- 1ST Sem 21 22 IM Living in The IT EraDocument63 pages1ST Sem 21 22 IM Living in The IT EraMaricar Mercado ApostolNo ratings yet

- Electron Devices and IcsDocument4 pagesElectron Devices and IcspuppyrNo ratings yet

- Field-Effect Transistors: See 2253: Electronic CircuitsDocument37 pagesField-Effect Transistors: See 2253: Electronic CircuitsSazali Husin100% (1)

- Philips 42 Inch LCD Power Ic-Fsq510Document14 pagesPhilips 42 Inch LCD Power Ic-Fsq510Raja Pathamuthu.GNo ratings yet

- Power Dissipation and Low Power Design TechniquesDocument17 pagesPower Dissipation and Low Power Design Techniquesnadeem47No ratings yet

- Question Paper VlsiDocument2 pagesQuestion Paper VlsiH&P GamingNo ratings yet

- Linkswitch-Tn: FamilyDocument16 pagesLinkswitch-Tn: FamilyJulián Peláez RestrepoNo ratings yet

- SSTC ReportDocument50 pagesSSTC ReportVishal ShahNo ratings yet

- A Low-Power Delay Buffer Using Gated Driver TreeDocument8 pagesA Low-Power Delay Buffer Using Gated Driver TreeJudeesh JacobNo ratings yet

- Schematic and Layout Design of a Differential Amplifier CircuitDocument9 pagesSchematic and Layout Design of a Differential Amplifier CircuitFrancisco De KamimoreNo ratings yet

- Control Systems and MOSFET OperationDocument7 pagesControl Systems and MOSFET OperationpurushresthaNo ratings yet

- Use of Test Structures For Characterization and Modeling of Inter-And Intra-Layer Capacitances in A CMOS ProcessDocument9 pagesUse of Test Structures For Characterization and Modeling of Inter-And Intra-Layer Capacitances in A CMOS ProcessAlex WongNo ratings yet

- High Speed Integrated Circuit TechnologyDocument372 pagesHigh Speed Integrated Circuit TechnologyZied Houaneb100% (1)

- VLSI Design Course OverviewDocument4 pagesVLSI Design Course OverviewDr.P. RAJASEKARNo ratings yet