Professional Documents

Culture Documents

Sb5101 Samsung Upgrade

Uploaded by

johnny-lawless3277Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sb5101 Samsung Upgrade

Uploaded by

johnny-lawless3277Copyright:

Available Formats

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

128Mb F-die SDRAM Specification

54 TSOP-II with Pb-Free

(RoHS compliant)

Revision 1.2

August 2004

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

Revision History

Revision 1.0 (January, 2004)

- First release.

Revision 1.1 (May, 2004)

• Added Note 5. sentense of tRDL parameter.

Revision 1.2 (August, 2004)

• Corrected typo.

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

8M x 4Bit x 4 Banks / 4M x 8Bit x 4 Banks / 2M x 16Bit x 4 Banks SDRAM

FEATURES

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system clock.

• Burst read single-bit write operation

• DQM (x4,x8) & L(U)DQM (x16) for masking

• Auto & self refresh

• 64ms refresh period (4K Cycle)

• 54 TSOP(II) Pb-free Package

• RoHS compliant

GENERAL DESCRIPTION

The K4S280432F / K4S280832F / K4S281632F is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x

8,388,608 words by 4 bits / 4 x 4,194,304 words by 8 bits / 4 x 2,097,152 words by 16 bits, fabricated with SAMSUNG′s high perfor-

mance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible

on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to

be useful for a variety of high bandwidth, high performance memory system applications.

Ordering Information

Part No. Orgainization Max Freq. Interface Package

K4S280432F-UC(L)75 32M x 4 133MHz LVTTL 54pin TSOP(II)

K4S280832F-UC(L)75 16M x 8 133MHz LVTTL 54pin TSOP(II)

K4S281632F-UC(L)60/75 8M x 16 166MHz LVTTL 54pin TSOP(II)

Organization Row Address Column Address

32Mx4 A0~A11 A0-A9, A11

16Mx8 A0~A11 A0-A9

8Mx16 A0~A11 A0-A8

Row & Column address configuration

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

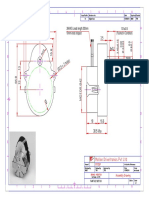

Package Physical Dimension

0~8°C

0.25

TYP

0.010

#54 #28

0.018~0.030

0.45~0.75

0.463±0.008

11.76±0.20

0.400

10.16

#1 #27

( 0.50 )

0.125+0.075

0.020

-0.035

22.62 0.005+0.003

-0.001

MAX

0.891

22.22 ± 0.10 0.21 ± 0.05 1.00 ± 0.10 1.20

0.875 ± 0.004 ± 0.002 ± 0.004

MAX

0.008 0.039 0.047

0.10

MAX

0.004 0.05

+0.10

0.71 0.30 -0.05 0.80 MIN

( ) 0.002

0.028 0.012 +0.004

-0.002

0.0315

54Pin TSOP Package Dimension

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

FUNCTIONAL BLOCK DIAGRAM

I/O Control

LWE

Data Input Register

LDQM

Bank Select

8M x 4 / 4M x 8 / 2M x 16

Refresh Counter

Output Buffer

Row Decoder

Sense AMP

Row Buffer

8M x 4 / 4M x 8 / 2M x 16

DQi

Address Register

8M x 4 / 4M x 8 / 2M x 16

CLK

8M x 4 / 4M x 8 / 2M x 16

ADD

Column Decoder

LRAS

LCBR

Col. Buffer

Latency & Burst Length

LCKE

Programming Register

LRAS LCBR LWE LCAS LWCBR LDQM

Timing Register

CLK CKE CS RAS CAS WE L(U)DQM

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

PIN CONFIGURATION (Top view)

x16 x8 x4 x4 x8 x16

VDD VDD VDD 1 54 VSS VSS VSS

DQ0 DQ0 N.C 2 53 N.C DQ7 DQ15

VDDQ VDDQ VDDQ 3 52 VSSQ VSSQ VSSQ

DQ1 N.C N.C 4 51 N.C N.C DQ14

DQ2 DQ1 DQ0 5 50 DQ3 DQ6 DQ13

VSSQ VSSQ VSSQ 6 49 VDDQ VDDQ VDDQ

DQ3 N.C N.C 7 48 N.C N.C DQ12

DQ4 DQ2 N.C 8 47 N.C DQ5 DQ11

VDDQ VDDQ VDDQ 9 46 VSSQ VSSQ VSSQ

DQ5 N.C N.C 10 45 N.C N.C DQ10

DQ6 DQ3 DQ1 11 44 DQ2 DQ4 DQ9

VSSQ VSSQ VSSQ 12 43 VDDQ VDDQ VDDQ

DQ7 N.C N.C 13 42 N.C N.C DQ8

VDD VDD VDD 14 41 VSS VSS VSS

LDQM N.C N.C 15 40 N.C/RFU N.C/RFU N.C/RFU

WE WE WE 16 39 DQM DQM UDQM

CAS CAS CAS 17 38 CLK CLK CLK

RAS RAS RAS 18 37 CKE CKE CKE

CS CS CS 19 36 N.C N.C N.C

BA0 BA0 BA0 20 35 A11 A11 A11

BA1 BA1 BA1 21 34 A9 A9 A9

A10/AP A10/AP A10/AP 22 33 A8 A8 A8

A0 A0 A0 23 32 A7 A7 A7

A1 A1 A1 24 31 A6 A6 A6

A2 A2 A2 25 30 A5 A5 A5 54Pin TSOP

A3 A3 A3 26 29 A4 A4 A4 (400mil x 875mil)

VDD VDD VDD 27 28 VSS VSS VSS (0.8 mm Pin pitch)

PIN FUNCTION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

Disables or enables device operation by masking or enabling all inputs except

CS Chip select

CLK, CKE and DQM

Masks system clock to freeze operation from the next clock cycle.

CKE Clock enable CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row/column addresses are multiplexed on the same pins.

A0 ~ A11 Address Row address : RA0 ~ RA11,

Column address : (x4 : CA0 ~ CA9,CA11), (x8 : CA0 ~ CA9), (x16 : CA0 ~ CA8)

Selects bank to be activated during row address latch time.

BA0 ~ BA1 Bank select address

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

RAS Row address strobe

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

CAS Column address strobe

Enables column access.

Enables write operation and row precharge.

WE Write enable

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

DQM Data input/output mask

Blocks data input when DQM active.

Data inputs/outputs are multiplexed on the same pins.

DQ0 ~ N Data input/output

(x4 : DQ0 ~ 3), (x8 : DQ0 ~ 7), (x16 : DQ0 ~ 15)

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

Isolated power supply and ground for the output buffers to provide improved noise

VDDQ/VSSQ Data output power/ground

immunity.

No connection

N.C/RFU This pin is recommended to be left No Connection on the device.

/reserved for future use

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Value Unit

Voltage on any pin relative to Vss VIN, VOUT -1.0 ~ 4.6 V

Voltage on VDD supply relative to Vss VDD, VDDQ -1.0 ~ 4.6 V

Storage temperature TSTG -55 ~ +150 °C

Power dissipation PD 1 W

Short circuit current IOS 50 mA

Note : Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to VSS = 0V, TA = 0 to 70°C)

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD, VDDQ 3.0 3.3 3.6 V

Input logic high voltage VIH 2.0 3.0 VDD+0.3 V 1

Input logic low voltage VIL -0.3 0 0.8 V 2

Output logic high voltage VOH 2.4 - - V IOH = -2mA

Output logic low voltage VOL - - 0.4 V IOL = 2mA

Input leakage current ILI -10 - 10 uA 3

Notes : 1. VIH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.

2. VIL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.

3. Any input 0V ≤ VIN ≤ VDDQ.

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.

CAPACITANCE (VDD = 3.3V, TA = 23°C, f = 1MHz, VREF =1.4V ± 200 mV)

Pin Symbol Min Max Unit Note

Clock CCLK 2.5 3.5 pF

RAS, CAS, WE, CS, CKE, DQM CIN 2.5 3.8 pF

Address CADD 2.5 3.8 pF

(x4 : DQ0 ~ DQ3), (x8 : DQ0 ~ DQ7), (x16 : DQ0 ~ DQ15) COUT 4.0 6.0 pF

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

DC CHARACTERISTICS (x4, x8)

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Version

Parameter Symbol Test Condition Unit Note

-75

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 90 mA 1

(One bank active)

IO = 0 mA

Precharge standby current in ICC2P CKE ≤ VIL(max), tCC = 10ns 2

mA

power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 2

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 20

Precharge standby current in Input signals are changed one time during 20ns

mA

non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC2NS 10

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 5

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 5

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 30 mA

Input signals are changed one time during 20ns

non power-down mode

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC3NS 25 mA

Input signals are stable

Operating current IO = 0 mA

ICC4 110 mA 1

(Burst mode) Page burst

Refresh current ICC5 tRC ≥ tRC(min) 200 mA 2

C 2 mA 3

Self refresh current ICC6 CKE ≤ 0.2V

L 800 uA 4

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S2804(08)32F-UC

4. K4S2804(08)32F-UL

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

DC CHARACTERISTICS (x16)

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Version

Parameter Symbol Test Condition Unit Note

-60 -75

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 130 100 mA 1

(One bank active)

IO = 0 mA

Precharge standby current in ICC2P CKE ≤ VIL(max), tCC = 10ns 2

mA

power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 2

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 20

Precharge standby current in Input signals are changed one time during 20ns

mA

non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC2NS 10

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 5

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 5

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 30 mA

Input signals are changed one time during 20ns

non power-down mode

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞ 25

ICC3NS mA

Input signals are stable

Operating current IO = 0 mA

ICC4 150 140 mA 1

(Burst mode) Page burst

Refresh current ICC5 tRC ≥ tRC(min) 220 200 mA 2

C 2 mA 3

Self refresh current ICC6 CKE ≤ 0.2V

L 800 uA 4

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S281632F-UC

4. K4S281632F-UL

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

AC OPERATING TEST CONDITIONS (VDD = 3.3V ± 0.3V, TA = 0 to 70°C)

Parameter Value Unit

Input levels (Vih/Vil) 2.4/0.4 V

Input timing measurement reference level 1.4 V

Input rise and fall time tr/tf = 1/1 ns

Output timing measurement reference level 1.4 V

Output load condition See Fig. 2

3.3V Vtt = 1.4V

1200Ω 50Ω

VOH (DC) = 2.4V, IOH = -2mA

Output Output Z0 = 50Ω

VOL (DC) = 0.4V, IOL = 2mA

50pF 50pF

870Ω

(Fig. 1) DC output load circuit (Fig. 2) AC output load circuit

OPERATING AC PARAMETER

(AC operating conditions unless otherwise noted)

Version

Parameter Symbol Unit Note

- 60 (x16 only) - 75

Row active to row active delay tRRD(min) 12 15 ns 1

RAS to CAS delay tRCD(min) 18 20 ns 1

Row precharge time tRP(min) 18 20 ns 1

tRAS(min) 42 45 ns 1

Row active time

tRAS(max) 100 us

Row cycle time tRC(min) 60 65 ns 1

Last data in to row precharge tRDL(min) 2 CLK 2,5

Last data in to Active delay tDAL(min) 2 CLK + tRP - 5

Last data in to new col. address delay tCDL(min) 1 CLK 2

Last data in to burst stop tBDL(min) 1 CLK 2

Col. address to col. address delay tCCD(min) 1 CLK 3

CAS latency=3 2

Number of valid output data ea 4

CAS latency=2 - 1

Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time

and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported.

SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP.

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

- 60 (x16 only) - 75

Parameter Symbol Unit Note

Min Max Min Max

CLK cycle CAS latency=3 6 7.5

tCC 1000 1000 ns 1

time CAS latency=2 - 10

CLK to valid CAS latency=3 5 5.4

tSAC ns 1,2

output delay CAS latency=2 - 6

Output data CAS latency=3 2.5 3

tOH ns 2

hold time CAS latency=2 - 3

CLK high pulse width tCH 2.5 2.5 ns 3

CLK low pulse width tCL 2.5 2.5 ns 3

Input setup time tSS 1.5 1.5 ns 3

Input hold time tSH 1 0.8 ns 3

CLK to output in Low-Z tSLZ 1 1 ns 2

CLK to output CAS latency=3 5 5.4

tSHZ ns

in Hi-Z CAS latency=2 - 6

Notes : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

DQ BUFFER OUTPUT DRIVE CHARACTERISTICS

Parameter Symbol Condition Min Typ Max Unit Notes

Measure in linear

Output rise time trh 1.37 4.37 Volts/ns 3

region : 1.2V ~ 1.8V

Measure in linear

Output fall time tfh 1.30 3.8 Volts/ns 3

region : 1.2V ~ 1.8V

Measure in linear

Output rise time trh 2.8 3.9 5.6 Volts/ns 1,2

region : 1.2V ~ 1.8V

Measure in linear

Output fall time tfh 2.0 2.9 5.0 Volts/ns 1,2

region : 1.2V ~ 1.8V

Notes : 1. Rise time specification based on 0pF + 50 Ω to VSS, use these values to design to.

2. Fall time specification based on 0pF + 50 Ω to VDD, use these values to design to.

3. Measured into 50pF only, use these values to characterize to.

4. All measurements done with respect to VSS.

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

IBIS SPECIFICATION 66MHz and 100MHz/133MHz Pull-up

0 0.5 1 1.5 2 2.5 3 3.5

IOH Characteristics (Pull-up)

0

100MHz 100MHz 66MHz

Voltage 133MHz 133MHz Min

Min Max -100

(V) I (mA) I (mA) I (mA)

3.45 -2.4

-200

3.3 -27.3

3.0 0.0 -74.1 -0.7

mA

2.6 -21.1 -129.2 -7.5 -300

2.4 -34.1 -153.3 -13.3

2.0 -58.7 -197.0 -27.5

-400

1.8 -67.3 -226.2 -35.5

1.65 -73.0 -248.0 -41.1

1.5 -77.9 -269.7 -47.9 -500

1.4 -80.8 -284.3 -52.4

1.0 -88.6 -344.5 -72.5

-600

0.0 -93.0 -502.4 -93.0

Voltage

IOH Min (100MHz/133MHz)

IOH Min (66MHz)

IOH Max (66 and 100MHz/133MHz)

66MHz and 100MHz/133MHz Pull-down

IOL Characteristics (Pull-down)

250

100MHz 100MHz 66MHz

Voltage 133MHz 133MHz Min

Min Max

200

(V) I (mA) I (mA) I (mA)

0.0 0.0 0.0 0.0

0.4 27.5 70.2 17.7

150

0.65 41.8 107.5 26.9

mA

0.85 51.6 133.8 33.3

1.0 58.0 151.2 37.6

100

1.4 70.7 187.7 46.6

1.5 72.9 194.4 48.0

1.65 75.4 202.5 49.5

50

1.8 77.0 208.6 50.7

1.95 77.6 212.0 51.5

3.0 80.3 219.6 54.2

0

3.45 81.4 222.6 54.9

0 0.5 1 1.5 2 2.5 3 3.5

Voltage

IOL Min (100MHz/133MHz)

IOL Min (66MHz)

IOL Max (100MHz/133MHz)

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

Minimum VDD clamp current

VDD Clamp @ CLK, CKE, CS, DQM & DQ (Referenced to VDD)

VDD (V) I (mA)

20

0.0 0.0

0.2 0.0

0.4 0.0

0.6 0.0 15

0.7 0.0

0.8 0.0

0.9 0.0

mA

1.0 0.23 10

1.2 1.34

1.4 3.02

1.6 5.06

1.8 7.35 5

2.0 9.83

2.2 12.48

2.4 15.30

0

2.6 18.31

0 1 2 3

Voltage

I (mA)

Minimum VSS clamp current

VSS Clamp @ CLK, CKE, CS, DQM & DQ

-3 -2 -1 0

VSS (V) I (mA)

-2.6 -57.23 0

-2.4 -45.77

-2.2 -38.26 -10

-2.0 -31.22

-1.8 -24.58

-1.6 -18.37 -20

-1.4 -12.56

-1.2 -7.57

mA

-30

-1.0 -3.37

-0.9 -1.75

-0.8 -0.58 -40

-0.7 -0.05

-0.6 0.0 -50

-0.4 0.0

-0.2 0.0

-60

0.0 0.0

Voltage

I (mA)

Rev. 1.2 August 2004

SDRAM 128Mb F-die (x4, x8, x16) CMOS SDRAM

SIMPLIFIED TRUTH TABLE (V=Valid, X=Don′t care, H=Logic high, L=Logic low)

A0 ~ A9,

Command CKEn-1 CKEn CS RAS CAS WE DQM BA0,1 A10/AP Note

A11,

Register Mode register set H X L L L L X OP code 1,2

Auto refresh H 3

H L L L H X X

Entry L 3

Refresh Self

L H H H 3

refresh Exit L H X X

H X X X 3

Bank active & row addr. H X L L H H X V Row address

Read & Auto precharge disable L Column 4

column address H X L H L H X V address

Auto precharge enable H 4,5

Write & Auto precharge disable L Column 4

column address H X L H L L X V address

Auto precharge enable H 4,5

Burst stop H X L H H L X X 6

Bank selection V L

Precharge H X L L H L X X

All banks X H

H X X X

Clock suspend or Entry H L X

L V V V X

active power down

Exit L H X X X X X

H X X X

Entry H L X

L H H H

Precharge power down mode X

H X X X

Exit L H X

L V V V

DQM H X V X 7

H X X X

No operation command H X X X

L H H H

Notes : 1. OP Code : Operand code

A0 ~ A11 & BA0 ~ BA1 : Program keys. (@ MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 CLK cycles of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

4. BA0 ~ BA1 : Bank select addresses.

If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.

If BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected.

If BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected.

If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.

If A10/AP is "High" at row precharge, BA0 and BA1 is ignored and all banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0),

but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

Rev. 1.2 August 2004

You might also like

- 256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Document14 pages256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Cường MchwNo ratings yet

- K4S561632EDocument15 pagesK4S561632ELelik GhhNo ratings yet

- 64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632KDocument14 pages64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632KCường MchwNo ratings yet

- 64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Document12 pages64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Luis AntunesNo ratings yet

- Data SheetDocument11 pagesData SheetManuel VillarNo ratings yet

- 013 - k4s64xx32n - Rev111 RAM DinámicaDocument15 pages013 - k4s64xx32n - Rev111 RAM DinámicanachcratchNo ratings yet

- Iiic - CC: 128Mb K-Die SDRAM SpecificationDocument15 pagesIiic - CC: 128Mb K-Die SDRAM SpecificationTan Hung LuuNo ratings yet

- 10/100 PC Card LAN Magnetic Modules: MechanicalsDocument2 pages10/100 PC Card LAN Magnetic Modules: MechanicalsAbdelrhman ElsayedNo ratings yet

- Voltage Mode Multiplying DAC Reference DesignDocument16 pagesVoltage Mode Multiplying DAC Reference DesignMouloud IbelaidenNo ratings yet

- Detail 02 L Vinkel Var 1Document14 pagesDetail 02 L Vinkel Var 1BrcakNo ratings yet

- Mechanical Data: D (R-PDSO-G ) Plastic Small-Outline PackageDocument2 pagesMechanical Data: D (R-PDSO-G ) Plastic Small-Outline PackageEva AvilésNo ratings yet

- 12GB (3X4GB) - 3SH13339R5H-12GT Features: Figure 1: Available ProfileDocument1 page12GB (3X4GB) - 3SH13339R5H-12GT Features: Figure 1: Available ProfileAyman SeaudiNo ratings yet

- SML-D14x (C) Series: Data SheetDocument10 pagesSML-D14x (C) Series: Data SheetKhadija EL ATRASSINo ratings yet

- MB1S Puente de Diodos de Alterna A DirectaDocument3 pagesMB1S Puente de Diodos de Alterna A DirectaGerardo SarmientoNo ratings yet

- KVR667D2N5K2 2GDocument1 pageKVR667D2N5K2 2GetendardNo ratings yet

- 2 N 2243 ADocument1 page2 N 2243 AAhmed EL-arabyNo ratings yet

- 40 X 40 X 10 MM SERIES: Dimensions DrawingDocument9 pages40 X 40 X 10 MM SERIES: Dimensions DrawingVíctor RomeuNo ratings yet

- KHX3200A 1gDocument2 pagesKHX3200A 1gOvidiu VranceanuNo ratings yet

- Dimensions in MM (Inches) .: TO39 (TO205AD) PinoutsDocument2 pagesDimensions in MM (Inches) .: TO39 (TO205AD) PinoutsJinsmon AlexNo ratings yet

- AnBon-S9014 C541685Document4 pagesAnBon-S9014 C541685karlos OliveraNo ratings yet

- 步进电机详细参数资料Document13 pages步进电机详细参数资料Andy YouQuanTexNo ratings yet

- CSL0406WBCW Series: Data SheetDocument10 pagesCSL0406WBCW Series: Data SheetpabloNo ratings yet

- Data SheetDocument1 pageData Sheetrosyadi28No ratings yet

- Axial Fan DELTAQFR1212GHEDocument1 pageAxial Fan DELTAQFR1212GHEJosé Edilson da PazNo ratings yet

- 120 X 120 X 38 MM SERIES: Dimensions DrawingDocument1 page120 X 120 X 38 MM SERIES: Dimensions DrawingrseheNo ratings yet

- 14PM M201V NMBDocument1 page14PM M201V NMBCristianEnacheNo ratings yet

- Id HolderDocument14 pagesId Holdereleazar rmNo ratings yet

- 26AWG Leads Length 200mm 10mm Ends Stripped (Pushed in Condition)Document1 page26AWG Leads Length 200mm 10mm Ends Stripped (Pushed in Condition)Aaron Eipe JohnNo ratings yet

- Datasheet Encoder 9720 V02-1747EN-952646Document12 pagesDatasheet Encoder 9720 V02-1747EN-952646HGL PrintNo ratings yet

- Pg240128a DisplayDocument1 pagePg240128a Displaybancadasol03No ratings yet

- DC Fan DatasheetDocument1 pageDC Fan DatasheetPhantom PNo ratings yet

- sj5 43502pmDocument1 pagesj5 43502pmthatatkdferreiraNo ratings yet

- Surface Roughness Conversion Chart Tables - Engineers EdgeDocument10 pagesSurface Roughness Conversion Chart Tables - Engineers Edgejames.anitNo ratings yet

- Linear Optical Incremental Encoder ModulesDocument7 pagesLinear Optical Incremental Encoder ModulesHasnain TariqNo ratings yet

- Part 777Document1 pagePart 777Omri AgaiNo ratings yet

- BDX 94Document1 pageBDX 94Jadi PurwonoNo ratings yet

- Efb505010 515937Document2 pagesEfb505010 515937Fabian MirandaNo ratings yet

- HP Color Laserjet Cp3525 PrintersDocument3 pagesHP Color Laserjet Cp3525 Printersringerc011No ratings yet

- Bu 9348 KDocument3 pagesBu 9348 KbinkyfishNo ratings yet

- Adm485 13Document1 pageAdm485 13mhasansharifiNo ratings yet

- Line Pipes PDFDocument6 pagesLine Pipes PDFRuDdy GunawanNo ratings yet

- 1SMB5 917BDocument3 pages1SMB5 917Bsansanyohan139875No ratings yet

- TIL308, TIL309 Numeric Displays With LogicDocument7 pagesTIL308, TIL309 Numeric Displays With LogicNadjNo ratings yet

- BRUSH and BRUSH-HOLDER TOLERANCES On T and A DIMENSIONS - Carbone Lorraine - INGDocument2 pagesBRUSH and BRUSH-HOLDER TOLERANCES On T and A DIMENSIONS - Carbone Lorraine - INGClaylson Figueiredo JúlioNo ratings yet

- Memory Module Specification: KHX6400D2LLK2/2GDocument2 pagesMemory Module Specification: KHX6400D2LLK2/2GΒΙΒΗ ΓΚΑΣΙΩΝΗNo ratings yet

- AR1298 CougarComponentsDocument2 pagesAR1298 CougarComponentsandreasmonNo ratings yet

- ET2 N16 (Relay)Document4 pagesET2 N16 (Relay)David MendezNo ratings yet

- CENTRIC DAYLIGHT Full Spectrum Flicker-Free A19 10W LED Bulb 4000K Photometric ReportDocument1 pageCENTRIC DAYLIGHT Full Spectrum Flicker-Free A19 10W LED Bulb 4000K Photometric ReportTonyNo ratings yet

- Optically Coupled 20 Ma Current Loop Receiver: HCPL-4200Document13 pagesOptically Coupled 20 Ma Current Loop Receiver: HCPL-4200bigm94iNo ratings yet

- PAUT Equipments For Reactors Connections Ammonia 2 at of Sorfert PlantDocument1 pagePAUT Equipments For Reactors Connections Ammonia 2 at of Sorfert PlantFethi BELOUISNo ratings yet

- Frame UnitDocument27 pagesFrame UnitVN MÁY TỰ ĐỘNGNo ratings yet

- RDamper CatalogDocument12 pagesRDamper CatalogEvandro MoreiraNo ratings yet

- Data Sheet Dan 202 KDocument3 pagesData Sheet Dan 202 KTarso BrasilNo ratings yet

- BP26 12Document1 pageBP26 12zakaria alhosinyNo ratings yet

- DC Output TransformerDocument5 pagesDC Output TransformerJay SriNo ratings yet

- Center Tapped TransformerDocument5 pagesCenter Tapped TransformerJay SriNo ratings yet

- Snap-In Mounting: Specifications IntroductionsDocument2 pagesSnap-In Mounting: Specifications IntroductionsMangueras Hidraulicas H-RojasNo ratings yet

- Datasheet - HK 1ss357 2716684Document2 pagesDatasheet - HK 1ss357 2716684Jairo Antonio Carreño RodriguezNo ratings yet

- AIXVUG VIOS SSP3 v23Document53 pagesAIXVUG VIOS SSP3 v23Redbulls ThailandNo ratings yet

- Toad Development Suite For Oracle 12.1: Installation GuideDocument20 pagesToad Development Suite For Oracle 12.1: Installation GuidelinethNo ratings yet

- Wi 5038Document8 pagesWi 5038jorge_moralesmNo ratings yet

- Cs 252 Java Basics 12Document70 pagesCs 252 Java Basics 12Ojas DhoneNo ratings yet

- Practical List: Charotar University of Science & TechnologyDocument83 pagesPractical List: Charotar University of Science & TechnologyMananNo ratings yet

- ADADMINDocument27 pagesADADMINapi-3744496100% (2)

- 01 12 21Document8 pages01 12 21hans motorNo ratings yet

- Motor Feedback Evaluation KitDocument4 pagesMotor Feedback Evaluation Kitnunes999No ratings yet

- Ds - 300vin Mini Family 709486 PDFDocument15 pagesDs - 300vin Mini Family 709486 PDFJESUS RIMACHI R.No ratings yet

- 4 de Febrero de 2022: Nuevos Ryzen Con GraficosDocument2 pages4 de Febrero de 2022: Nuevos Ryzen Con GraficosCharlyBeltránSánchezNo ratings yet

- EL2002 Sistem Digital - PR6 - SolusiDocument6 pagesEL2002 Sistem Digital - PR6 - SolusianneNo ratings yet

- TWSP Narrative ReportDocument5 pagesTWSP Narrative ReportLeoj EdlarocNo ratings yet

- Konfigurasi Router Ke CloudDocument4 pagesKonfigurasi Router Ke CloudWahyuddin NoorNo ratings yet

- PDC - Lecture - No. 2Document31 pagesPDC - Lecture - No. 2nauman tariqNo ratings yet

- OpsCenter v10 9 3 Installation and Configuration Guide MK-99OPS001-19Document161 pagesOpsCenter v10 9 3 Installation and Configuration Guide MK-99OPS001-19smowaishyderNo ratings yet

- Rolls MO2020 Oscillator Manual & SchematicDocument2 pagesRolls MO2020 Oscillator Manual & SchematicNiX Pro AudioNo ratings yet

- CoprocessorDocument23 pagesCoprocessorsarthakNo ratings yet

- Install Lithium-Ion Batteries, Battery 6619Document12 pagesInstall Lithium-Ion Batteries, Battery 6619Gabriel LugiraNo ratings yet

- Variador Altivar Atv320 CatalogoDocument67 pagesVariador Altivar Atv320 CatalogoCristhian RamirezNo ratings yet

- Distributed SwitchDocument20 pagesDistributed SwitchBiên ĐặngNo ratings yet

- Finite Word Length EffectsDocument31 pagesFinite Word Length EffectsSugumar Sar DuraiNo ratings yet

- MS in CS (Information Security) +bachelor in Computer Science & Engineering +work ExpDocument1 pageMS in CS (Information Security) +bachelor in Computer Science & Engineering +work ExpNova HerondaleNo ratings yet

- CallRecord LogDocument55 pagesCallRecord LogPhillipNo ratings yet

- Alv Tutotial For Beginers With Examples - Abap Development - SCN WikiDocument33 pagesAlv Tutotial For Beginers With Examples - Abap Development - SCN WikiAlejandro Calderón AguirreNo ratings yet

- Structures and UnionsDocument58 pagesStructures and UnionsRuchita AgarwalNo ratings yet

- OW360 - 20 - Operator Station User GuideDocument764 pagesOW360 - 20 - Operator Station User GuideRicardas KragnysNo ratings yet

- 9 Axis E-Compass Manager Instruction-160613Document14 pages9 Axis E-Compass Manager Instruction-160613Hoang VuNo ratings yet

- Memory Sizes of Windows OSDocument28 pagesMemory Sizes of Windows OSvdchuyenNo ratings yet

- Led TV: User ManualDocument2 pagesLed TV: User ManualAnonymous 74EiX2MzgcNo ratings yet

- Oracle Solaris Guide For Linux Users: December 2016 (Edition 1.0) Fujitsu LimitedDocument74 pagesOracle Solaris Guide For Linux Users: December 2016 (Edition 1.0) Fujitsu LimitedShero KhanNo ratings yet