Professional Documents

Culture Documents

VFD Driver IC Controls Vacuum Fluorescent Displays

Uploaded by

movvOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VFD Driver IC Controls Vacuum Fluorescent Displays

Uploaded by

movvCopyright:

Available Formats

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

DESCRIPTION

PT6315 is a Vacuum Fluorescent Display (VFD) Controller driven on a 1/4 to 1/12 duty factor. Sixteen

segment output lines, 4 grid output lines, 8 segment/grid output drive lines, one display memory, control circuit,

key scan circuit are all incorporated into a single chip to build a highly reliable peripheral device for a single chip

micro computer. Serial data is fed to PT6315 via a three-line serial interface. It is housed in a 44-pin, SSOP

and LQFP Package.

FEATURES

• CMOS Technology

• Low Power Consumption

• Key Scanning (16 x 2 matrix)

• Multiple Display Modes: (16 segments, 12 digits to 24 segments, 4 digits)

• 8-Step Dimming Circuitry

• LED Ports Provided (4 channels, 20 mA max.)

• Serial Interface for Clock, Data Input, Data Output, Strobe Pins

• No External Resistors Needed for Driver Outputs

• Available in 44-pin, SSOP and LQFP Package

APPLICATION

• Microcomputer Peripheral Device

PT6315 v2.0 Page 1 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

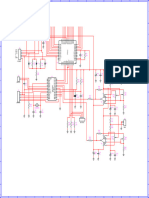

BLOCK DIAGRAM

SG1/KS1

SG2/KS2

SG3/KS3

SG4/KS4

SG5/KS5

SG6/KS6

SG7/KS7

SG8/KS8

24 12 SG9/KS9

SG10/KS10

SG11/KS11

SG12/KS12

SG13/KS13

SG14/KS14

SG15/KS15

SG16/KS16

SG21/GR8

SG22/GR7

SG23/GR6

SG24/GR5

Figure 1: PT6315 Internal Block Diagram

PT6315 v2.0 Page 2 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

PIN CONFIGURATION 44PIN LQFP

SG24/GR5

SG23/GR6

SG22/GR7

SG21/GR8

SG20/GR9

VDD

GR1

GR2

GR3

GR4

VSS

LED1 SG19/GR10

LED2 SG18/GR11

LED3 SG17/GR12

LED4 VEE

OSC SG16/KS16

DOUT SG15/KS15

DIN SG14/KS14

CLK SG13/KS13

STB SG12/KS12

K1 SG11/KS11

K2 SG10/KS10

SG1/KS1

SG2/KS2

SG3/KS3

SG4/KS4

SG5/KS5

SG6/KS6

SG7/KS7

SG8/KS8

SG9/KS9

VSS

VDD

Figure 2: PT6315 LQFP Pin Configuration

PT6315 v2.0 Page 3 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

PIN CONFIGURATION 44PIN SSOP

GR4 1 44 SG24/GR5

GR3 2 43 SG23/GR6

GR2 3 42 SG22/GR7

GR1 4 41 SG21/GR8

VDD 5 40 SG20/GR9

VSS 6 39 SG19/GR10

LED1 7 38 SG18/GR11

LED2 8 37 SG17/GR12

LED3 9 36 VEE

LED4 10 35 SG16/KS16

OSC 11 34 SG15/KS15

DOUT 12 33 SG14/KS14

DIN 13 32 SG13/KS13

CLK 14 31 SG12/KS12

STB 15 30 SG11/KS11

K1 16 29 SG10/KS10

K2 17 28 SG9/KS9

VSS 18 27 SG8/KS8

VDD 19 26 SG7/KS7

SG1/KS1 20 25 SG6/KS6

SG2/KS2 21 24 SG5/KS5

SG3/KS3 22 23 SG4/KS4

Figure 3: PT6315 SSOP Pin Configuration

PT6315 v2.0 Page 4 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

PIN DESCRIPTION

Pin Name I/O Description Pin No.

LED1 to LED4 O LED Output Pin 1 to 4

Oscillator Input Pin

OSC I A resistor is connected to this pin to 5

determine the oscillation frequency

Data Output Pin (N-Channel, Open-Drain)

This pin outputs serial data at the falling

DOUT O 6

edge of the shift clock (starting from the

lower bit).

Data Input Pin

DIN This pin inputs serial data at the rising edge

I 7

(Schmitt Trigger) of the shift clock (starting from the lower

bit)

Clock Input Pin

CLK

I This pin reads serial data at the rising edge 8

(Schmitt Trigger)

and outputs data at the falling edge.

Serial Interface Strobe Pin

STB The data input after the STB has fallen is

I 9

(Schmitt Trigger) processed as a command.

When this pin is "HIGH", CLK is ignored.

Key Data Input Pins

K1 to K2 I The data inputted to these pins are latched 10 ,11

at the end of the display cycle.

VSS - Logic Ground Pin 12,44

VDD - Logic Power Supply 13,43

High-Voltage Segment Output Pins 14 to

SG1/KS1 to SG16/KS16 O

Also acts as the Key Source 29

VEE - Pull-Down Level 30

31 to

SG17/GR12 to SG24/GR5 O High Voltage Segment/Grid Output Pins

38

39 to

GR4 to GR1 O High-Voltage Grid Output Pins

42

PT6315 v2.0 Page 5 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

FUNCTIONAL DESCRIPTION

Commands

Commands determine the display mode and status of PT6315. A command is the first byte (b0 to b7) inputted

to PT6315 via the DIN Pin after STB Pin has changed from “HIGH” to “LOW” State. If for some reason

the STB Pin is set to “HIGH” while data or commands are being transmitted, the serial communication is

initialized, and the data/commands being transmitted are considered invalid.

COMMAND 1: DISPLAY MODE SETTING COMMANDS

PT6315 provides 8 display mode settings as shown in the diagram below: As stated earlier a

command is the first one byte (b0 to b7) transmitted to PT6315 via the DIN Pin when STB is

“LOW”. However, for these commands, the bits 5 to 6 (b4 to b5) are ignored, bits 7 & 8 (b6 to

b7) are given a value of “0”.

The Display Mode Setting Commands determine the number of segments and grids to be used

(1/4 to 1/12 duty, 16 to 24 segments). When these commands are executed, the display is

forcibly turned off, the key scanning stops. A display command “ON” must be executed in order

to resume display. If the same mode setting is selected, no command execution is take place,

therefore, nothing happens.

When Power is turned “ON”, the 12-digit , 16-segment modes is selected.

MSB LSB

0 0 - - b3 b2 b1 b0

Display Mode Settings:

Not Relevant 0000 : 4 digits, 24 segments

0001: 5 digits, 23 segments

0010: 6 digits,22 segments

0011: 7 digits, 21 segments

0100: 8 digits, 20 segments

0101: 9 digits, 19 segments

0110: 10 digits, 18 segments

0111: 11 digits, 17 segments

1XXX: 12 digits, 16 segments

Figure 3: Display Mode Settings

PT6315 v2.0 Page 6 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

Display Mode and RAM Address

Data transmitted from an external device to PT6315 via the serial interface are stored in the

Display RAM and are assigned addresses. The RAM Addresses of PT6315 are given below in 8

bits unit.

SG1 SG4 SG5 SG8 SG9 SG12 SG13 SG16 SG17 SG20 SG21 SG24

00H L 00H U 01H L 01H U 02H L 02H U DIG1

03H L 03H U 04H L 04H U 05H L 05H U DIG2

06H L 06H U 07H L 07H U 08H L 08H U DIG3

09H L 09H U 0AH L 0AH U 0BH L 0BH U DIG4

0 C H L 0CH U 0DH L 0DH U 0EH L 0EH U DIG5

0FHL 0FH U 10H L 10H U 11H L 11HU DIG6

12H L 12H U 13H L 13H U 14H L 14H U DIG7

15H L 15H U 16H L 16H U 17H L 17H U DIG8

18H L 18H U 19H L 19H U 1AHL 1AH U DIG9

1BH L 1BH U 1 C HL 1 C H U 1DHL 1DH U DIG10

1EH L 1EH U 1FH L 1FH U 20H L 20H U DIG11

21H L 21H U 22H L 22H U 23H L 23H U DIG12

b0 b3 b4 b7

xxHL xxHU

Lower 4 bits Higher 4 bits

Figure 4: PT6315 RAM Address

PT6315 v2.0 Page 7 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

COMMAND 2: DATA SETTING COMMANDS

The Data Setting Commands executes the Data Write or Data Read Modes for PT6315. The data

Setting Command, the bits 5 and 6 (b4, b5) are ignored, bit 7 (b6) is given the value of “1” while

bit 8 (b7) is given the value of “0”. Please refer to the diagram below.

When power is turned ON, the bit 4 to bit 1 (b3 to b0) are given the value of “0”.

Don't Care

Figure 5: Data Settings

PT6315 v2.0 Page 8 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

PT6315 Key Matrix & Key Input Data Storage RAM

PT6315 Key Matrix consists of 16 x 2 array as shown below:

K1

K2

SG1/KS1

SG2/KS2

SG3/KS3

SG4/KS4

SG5/KS5

SG6/KS6

SG7/KS7

SG8/KS8

SG9/KS9

SG10/KS10

SG11/KS11

SG12/KS12

SG13/KS13

Figure 6: PT6315 Key Matrix

Each data inputted by each key are stored as follows. They are read by a READ Command, starting

from the last significant bit. When the most significant bit of the data (SG1, b0) has been read, the least

significant bit of the next data (SG16, b7) is read.

K1 ........... K2 K1 ............... K2 K1 ........... K2 K1 ............... K2

SG1/KS1 SG2/KS2 SG3/KS3 SG4/KS4

SG5/KS5 SG6/KS6 SG7/KS7 SG8/KS8 READING

SEQUENCE

SG9/KS9 SG10/KS10 SG11/KS11 SG12/KS12

SG11/KS11 SG14/KS14 SG15/KS15 SG16/KS16

b0 ............b1

Figure 7: PT6315 Key Input Data Storage

PT6315 v2.0 Page 9 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

LED Display

PT6315 provides 4 LED Display Terminals, namely LED1 to LED4. Data is written to the LED

Port starting from the least significant bit (b0) of the port using a WRITE Command. Each bit

starting from the least significant (b0) activates a specific LED Display Terminal -- b0

corresponds LED1 Display, b1 activates LED2 and so forth. Since there are only 4 LED display

terminals, bits 5 to 8 (b4 ~ b7) are not used and therefore ignored. This means that b4 to b7

does NOT in anyway activate any LED Display, they are totally ignored.

When a bit (b0 ~ b3) in the LED Port is “1”, the corresponding LED is OFF. Conversely, when

the bit is “0”, the LED Display is turned ON. For example, Bit 1 (as designated by b0) has the

value of “1”, then this means that LED1 is OFF. It must be noted that when power is turned

ON, bit 1 to bit 4 (bo to b3) are given the value of “0” (all LEDs are turned ON). Please

refer to the diagrams below.

MSB LSB

- - - - b3 b2 b1 b0

LED1

NOT USED LED2

LED3

LED4

Figure 8: PT6315 LED Display Designation

PT6315 v2.0 Page 10 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

COMMAND 3: ADDRESS SETTING COMMANDS

Address Setting Commands are used to set the address of the display memory. The address is

considered valid if it has a value of “00H” to “23H”. If the address is set to 24H or higher, the

data is ignored until a valid address is set. When power is turned ON, the address is set at “00H”.

Please refer to the diagram below.

MSB LSB

1 1 b5 b4 b3 b2 b1 b0

Address: 00H to 23H

Figure 10: Address Settings

PT6315 v2.0 Page 11 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

COMMAND 4: DISPLAY CONTROL COMMANDS

The Display Control Commands are used to turn ON or OFF a display. It also used to set the pulse

width. Please refer to the diagram below. When the power is turned ON, a 1/16 pulse width is

selected and the displayed is turned OFF (the key scanning is stopped).

Figure 11: Display Control Settings

PT6315 v2.0 Page 12 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

SCANNING AND DISPLAY TIMING

The Key Scanning and display timing diagram is given below. One cycle of key scanning consists of 2 frames.

The data of the 16 x 2 matrix is stored in the RAM.

Internal Operating Frequency (fosc) = 224/T

TDISPLAY=500us Key Scan Data

1 2 8

T

SGn 9 10 16

G1

G2

G3

Gn

1 Frame=TDISPLAY x (n +1)

Figure 12: PT6315 Scanning & Display Timing Diagram

Note: T is the width of Segment only

PT6315 v2.0 Page 13 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

SERIAL COMMUNICATION FORMAT

The following diagram shows the PT6315 serial communication format. The DOUT Pin is an N-channel, open-

drain output pin, therefore, it is highly recommended that an external pull-up resistor (1 KOhms to 10 KOhms)

must be connected to DOUT.

b0 b1 b2 b3 b4 b5

Figure 13: PT6315 Serial Communication Format

where: twait (waiting time) > 1us

It must be noted that when the data is read, the waiting time (twait) between the rising of the eighth clock that has

set the command and the falling of the first clock that has read the data is greater or equal to 1µs.

PT6315 v2.0 Page 14 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

SWITCHING CHARACTERISTIC WAVEFORM

PT6315 Switching Characteristics Waveform is given below.

where: PW CLK (Clock Pulse Width)>400ns PW STB (Strobe Pulse Width)>1us

t setup (Data Setup Time) >100ns thold (Data Hold Time)>100ns

tCLK-STB (Clock - Strobe Time)>1us tTHZ (Fall Time)<150us

tTZH2 (Grid Rise Time)<0.5us (at VDD=5V) tPZL (Propagation Delay Time)<100ns

tTZH2 (Grid Rise Time)<1.0us (at VDD=3.3V) tPLZ (Propagation Delay Time)<400ns

tTZH1 (Segment Rise Time)<2.0us (at VDD=5V) fosc = Oscillation Frequency

tTZH1 (Segment Rise Time)<3.0us (at VDD=3.3V)

Figure 14: PT6315 Switching Characteristic Waveform

PT6315 v2.0 Page 15 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

APPLICATIONS

Display memory are updated by incrementing addresses. Please refer to the following diagram.

where: Command 1: Display Mode Setting Command

Command 2: Data Setting Command

Command 3: Address Setting Command

Data 1 to n : Transfer Display Data (36 Bytes max.)

Command 4: Display Control Command

Figure 15: Display Memory Updated by Address Increments

The following diagram shows the waveforms when updating specific addresses.

3 3

Data Setting Command

3 Address Setting Command

Figure 16: Address Update

PT6315 v2.0 Page 16 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

RECOMMENDED SOFTWARE FLOWCHART

START

Delay 200 ms

SET

COMMAND 2

(Write Data)

SET

COMMAND 3

Clear Display RAM

INITIAL

(See Note 5)

SETTING

SET

COMMAND 1

SET

COMMAND 4

(88H ~ 8FH : Display

ON)

MAIN

PROGRAM

SET

COMMAND 2

(READ KEY &

WRITEDATA

INCLUDED)

MAIN

L O O P

SET

COMMAND 3

SET

COMMAND 1

SET

COMMAND 4

END

Note: 1. Command 1: Display Mode Commands

2. Command 2: Data Setting Commands

3. Command 3 : Address Setting Commands

4. Command 4: Display Control Commands

5. When IC power is applied for the first time, the contents of the Display RAM are not defined; thus, it

is strongly suggested that the contents of the Display RAM must be cleared during the initial setting.

Figure 17: Recommended Software Flowchart

PT6315 v2.0 Page 17 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

ABSOLUTE MAXIMUM RATINGS

(Unless otherwise stated, Ta=25o C, GND=0V)

Parameter Symbol Ratings Unit

Logic Supply Voltage V DD -0.5 to +7 Volts

Driver Supply Voltage V EE V DD+0.5 to VDD- 4 0 Volts

Logic Input Voltage VI -0.5 to V DD+0.5 Volts

VFD Driver Output Voltage Vo V E E- 0 . 5 t o V D D + 0 . 5 Volts

LED Driver Output Current IO L E D +20 mA

-40 (Grid)

VFD Driver Output Current IO V F D mA

-15 (Segment)

RECOMMENDED OPERATING RANGE

(Unless otherwise stated, Ta=-20 to +70o C, GND=0V)

Parameter Symbol Min. Typ. Max. Unit

Logic Supply Voltage V DD 3.0 5 5.5 V

High-Level Input Voltage V IH 0.7VD D - V DD V

Low-Level Input Voltage V IL 0 - 0.3VD D V

Driver Supply Voltage V EE VD D-35 - 0 V

PT6315 v2.0 Page 18 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

ELECTRICAL CHARACTERISTICS

(Unless otherwise stated, VDD =5V, GND=0V, VEE =VDD -35 V, Ta=25o C)

Parameter Symbol Test Condition M in. Typ. Max. Unit

High-Level IO H L E D = - 1 2 m A

VOHLED V DD - 1 - - V

Output Voltage LED1 to LED4

Low-Level IOLLED= + 1 5 m A

VOLLED - - 1 V

Output Voltage LED1 to LED4

Low-Level D OUT,

VOLDOUT - - 0.4 V

Output Voltage IO L D O U T= 4 m A

Vo=V DD- 2 V

High-Level

IO H S G SG1/KS1 to -3 - - mA

Output Current

SG16/KS16

Vo=V DD- 2 V

High-Level GR1 to GR8,

IO H G R -15 - - mA

Output Current SG17/GR12 to

SG24/GR5

Oscillation R=82 Kohms

fosc 350 500 650 KHz

Frequency (see Note)

Schmitt-Trigger

VD D=5V

Transfer Voltage V T+ 2.7 3 3.3 V

(DIN, CLK, STB)

(+)

Schmitt-Trigger

VD D=5V

Transfer Voltage V T- 0.7 1.0 1.3 V

(DIN, CLK, STB)

(-)

Hysteresis VD D=5V

V hys 1.4 2.0 - V

Voltage (DIN, CLK, STB)

Input Current II V I = V DD or VSS - - ±1 uA

Dynamic Current Under no load

ID D d y n - - 5 mA

Consumption Display OFF

Note: The frequency value is for PTC test condition. fosc=224/T

If you want to know details data, please see page 13.

PT6315 v2.0 Page 19 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

ELECTRICAL CHARACTERISTICS

(Unless otherwise stated, VDD =3.3V, GND=0V, VEE =VDD -35 V, Ta=25o C)

Parameter Symbol Test Condition M in. Typ. Max. Unit

High-Level IOHLED =-6mA

VOHLED V DD - 1 - - V

Output Voltage LED1 to LED4

Low-Level IOLLED= + 1 5 m A

VOLLED - - 1 V

Output Voltage LED1 to LED4

Low-Level D OUT,

VOLDOUT - - 0.4 V

Output Voltage IO L D O U T= 4 m A

Vo=V DD- 2 V

High-Level

IO H S G SG1/KS1 to -1.5 - - mA

Output Current

SG16/KS16

Vo=V DD- 2 V

High-Level GR1 to GR8,

IO H G R -6 - - mA

Output Current SG17/GR12 to

SG24/GR5

Oscillation R=100 Kohms

fosc 350 500 650 KHz

Frequency (see Note)

Schmitt-Trigger

VDD=3.3V

Transfer Voltage V T+ 1.8 2.0 2.2 V

(DIN, CLK, STB)

(+)

Schmitt-Trigger

VDD=3.3V

Transfer Voltage V T- 0.2 0.4 0.6 V

(DIN, CLK, STB)

(-)

Hysteresis VDD=3.3V

V hys 1.0 1.6 - V

Voltage (DIN, CLK, STB)

Input current II V I = V DD or VSS - - ±1 uA

Dynamic Current Under no load

ID D d y n - - 3 mA

Consumption Display OFF

Note: The frequency value is for PTC test condition. fosc=224/T

If you want to know details data, please see page 13.

PT6315 v2.0 Page 20 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

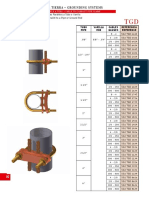

APPLICATION CIRCUIT 1

44 PIN LQFP

Vcc

G9 G8 G7 G6 G5 G4 G3 G2 G1

VCC 9-GRID X 19-SEGMENT VFD

S19 S18 S17 S16 S15 S14 S13 S12 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1

44 43 42 41 40 39 38 37 36 35 34

330

33

330

10K 32

330

31

330

30 -VEE

29

100K

MCU

PT6315 28

27

26

25

24

23

12 13 14 1 5 16 1 7 18 19 20 21 22

Vcc 0.1 F

1N4148 x 16

10K 10K

Figure 18: PT6315 LQFP Applicaiton Circuit

Note: The capacitor (0.1uF) connected between the GND and the VDD pins must be located as close

as possible to the PT6315 chip.

PT6315 v2.0 Page 21 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

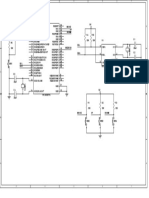

APPLICATION CIRCUIT 2

44 PIN SSOP

VCC

44

43 G9 G8 G7 G6 G5 G4 G3 G2 G1

42 9-GRID X 19-SEGMENT VFD

41 S19 S18 S17 S16 S15 S14 S13 S12 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1

VCC 40

39

330

38

330

37

330

10K 36 -VEE

330

35

34

100K

33

MCU PT6315 32

31

30

29

28

27

0.1 F

26

Vcc 25

24

23

10K 10K

1N4148 X 16

10K 10K

Figure 19: PT6315 SSOP Applicaiton Circuit

Note: The capacitor (0.1uF) connected between the GND and the VDD pins must be located as close

as possible to the PT6315 chip.

PT6315 v2.0 Page 22 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

ORDER INFORMATION

Order Part Number Package Type Top Code

PT6315 44 pin LQFP Package PT6315

PT6315-S 44 pin SOP Package PT6315-S

PT6315 L or "L"in circle 44 pin LQFP Package PT6315

PT6315-S L or "L"in circle 44 pin SOP Package PT6315-S

Note: 1. L = Lead Free

2. The Lead Free mark is put in front of the date code.

PT6315 v2.0 Page 23 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

PACKAGE DIMENSION

44-Pin LQFP Package (Body Size: 10mm x 10mm; Pitch: 0.80mm; THK

Body: 1.40mm)

D

D1

-D-

-A- -B-

E1

E

e

b

1

-C- SEATING PLANE

R1

R2

-H-

GAUGE PLANE

0.25mm

S L

PT6315 v2.0 Page 24 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

Symbol Min. Nom. Max.

A - - 1.60

A1 0.05 - 0.15

A2 1.35 1.40 1.45

b 0.30 0.37 0.45

- -

D 12.00 BSC

D1 10.00 BSC

e 0.80 BSC

E 12.00 BSC

E1 10.00 BSC

θ 0o 3.5o 7o

θ1 0o - -

θ2 11o 12o 13o

θ3 11o 12o 13o

C 0.09 - 0.20

L 0.45 0.60 0.75

L1 1.00 REF

R1 0.08 - -

R2 0.08 - 0.20

S 0.20 - -

Notes:

1. Controlling Dimensions are in millimeters .

2. Dimensioning and tolerancing per ASME Y14.5M-1994.

3. The top packge body size may be smaller than the bottom package size by as much as 0.15mm.

4. Datums A-B and D to be determined at datum plane H.

5. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. D1 and

E1 are maximum plastic body size dimensions including mold mismatch.

6. Details of pin1 identifier are optional but must be located within the zone indicated.

7. Dimension b does not include dambar protrusion. Alowable dambar protrusion shall not cause the lead to

exceed the maximum b dimension by more than 0.08mm. Dambar cannot be located on the lower radius or

the foot. Minimum space between protrusion and an adjacent lead is 0.07mm for 0.4mm and 0.5mm pitch

packages.

8. A1 is defined as the distance from the seating plane to the lowest point on the package body.

9. Refer to JEDEC STD MS-026 Variation BCB

JEDEC is the trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

PT6315 v2.0 Page 25 Sep. 2002

Tel : 886-2-29162151

Fax: 886-2-29174598

VFD Driver/Controller IC PT6315

44-Pin SSOP Package

c

GAUGE PLANE

F

L

0.01INCH

E1 E

h x 45

e b 0.004 C

A1 SEATING PLANE

Notes:

1. Dimension D do not include mold flash, protrusions or gate burrs.

2. Mold flash, protrusions or gate burrs shall not exceed 0.006 inch (0.152 mm) per side

PT6315 v2.0 Page 26 Sep. 2002

You might also like

- Control LED Drive Circuit: FeaturesDocument14 pagesControl LED Drive Circuit: FeaturesJacksonVelozNo ratings yet

- LED Driver IC: DescriptionDocument12 pagesLED Driver IC: Descriptionanand shekhawatNo ratings yet

- TM1628Document14 pagesTM1628chandra sekhar BeheraNo ratings yet

- TM1628 LED driver chip overviewDocument14 pagesTM1628 LED driver chip overviewIstván FeketeNo ratings yet

- Vma425 SchemeDocument1 pageVma425 Schemejakalae5263No ratings yet

- CMZ700 Basic Interconnection DiagramDocument2 pagesCMZ700 Basic Interconnection Diagramioannides_christosNo ratings yet

- Description: Technical DataDocument17 pagesDescription: Technical DataDhivya NNo ratings yet

- PTC Princeton Tech PT6312BLQ - C110225Document21 pagesPTC Princeton Tech PT6312BLQ - C110225tulio enrique leon ayalaNo ratings yet

- MC2101 TM1628 PDFDocument22 pagesMC2101 TM1628 PDFPol ErnNo ratings yet

- TM1638 enDocument18 pagesTM1638 enfotakis michaelNo ratings yet

- Gordak 952-vDocument1 pageGordak 952-vivouhfNo ratings yet

- Total Count of DE 2 4 1 6 2 Total Count of NDE 2 4 1 6 2Document3 pagesTotal Count of DE 2 4 1 6 2 Total Count of NDE 2 4 1 6 2Novian LisdiNo ratings yet

- Datasheet TM1637Document12 pagesDatasheet TM1637DiegoNo ratings yet

- Senco Nails ChartDocument2 pagesSenco Nails ChartlsgmzNo ratings yet

- Gas springs help lift heavy equipment doorsDocument2 pagesGas springs help lift heavy equipment doorsDaveNo ratings yet

- FORM JADWAL PELAJARAN DAN KODE GURU TAHUN 2022-2023 V3 Ok PDFDocument10 pagesFORM JADWAL PELAJARAN DAN KODE GURU TAHUN 2022-2023 V3 Ok PDFGanendra Ptraa /21 /Xtpm2No ratings yet

- DDR Termination Regulator: Features General DescriptionDocument1 pageDDR Termination Regulator: Features General DescriptionLina LinuNo ratings yet

- Grapas GAR RefDocument1 pageGrapas GAR RefyogeunysNo ratings yet

- Grounding cable to pipe clamps for multiple sizesDocument1 pageGrounding cable to pipe clamps for multiple sizesJorge Enrique Garcia GarciaNo ratings yet

- Grayloc Product Catalog Woodco Usa PDFDocument7 pagesGrayloc Product Catalog Woodco Usa PDFDesign2 Department0% (1)

- inventarioDocument6 pagesinventariowaracaoyNo ratings yet

- Tool Project PT EUP PT KPA 2022Document6 pagesTool Project PT EUP PT KPA 2022gegebener coy17No ratings yet

- EasyPact TVS LC1E06 to 630 coordination tableDocument2 pagesEasyPact TVS LC1E06 to 630 coordination tableJhonSitanalaNo ratings yet

- Recommended Spark PlugsDocument3 pagesRecommended Spark PlugsDjebali MouradNo ratings yet

- CNC Crimping Terminal Lugs (Short Barrel-One Hole) : Non-Insulated Copper MaterialDocument1 pageCNC Crimping Terminal Lugs (Short Barrel-One Hole) : Non-Insulated Copper MaterialCiel AireNo ratings yet

- Service Manual (All Indoor Unit)Document125 pagesService Manual (All Indoor Unit)U Kyaw San OoNo ratings yet

- Total Result 7 1 5 1 12 2 6 1 3 30 11 19 Total Result 32 5 12 49Document4 pagesTotal Result 7 1 5 1 12 2 6 1 3 30 11 19 Total Result 32 5 12 49Valins TasikmalayaNo ratings yet

- GD75232Document18 pagesGD75232ijf_a3780No ratings yet

- Fig 06-30-00 - 11700-A Typical Arrangement of Stringers On The Frames: Sheet 1Document1 pageFig 06-30-00 - 11700-A Typical Arrangement of Stringers On The Frames: Sheet 1Franco GomezNo ratings yet

- Sdls055A - December 1972 - Revised May 2007Document19 pagesSdls055A - December 1972 - Revised May 2007EduardoFonsecaNo ratings yet

- Genie Units Data UpdatedDocument38 pagesGenie Units Data UpdatedAshley RiveraNo ratings yet

- Seal Master SC-32Document1 pageSeal Master SC-32Walter CoresNo ratings yet

- MBSM - Pro, Compressor, Aspera, B3119Z, 234 W, 1/4 HP, R134a: Publié Le 25 Mai 2022 - ParDocument7 pagesMBSM - Pro, Compressor, Aspera, B3119Z, 234 W, 1/4 HP, R134a: Publié Le 25 Mai 2022 - Parأبو زينب المهندسNo ratings yet

- Monitoring Keluar Masuk Material ProyekDocument7 pagesMonitoring Keluar Masuk Material ProyekaronmdavinchyNo ratings yet

- 227 - COMM - Manual - Eng - Mitsubishi MELSEC SeriesDocument29 pages227 - COMM - Manual - Eng - Mitsubishi MELSEC SeriesPhuocauto CncNo ratings yet

- Telephone Audio Fed Back 1Document1 pageTelephone Audio Fed Back 1v2brotherNo ratings yet

- Contact and electronics inventory for ship parts supplierDocument6 pagesContact and electronics inventory for ship parts supplierfotini100% (1)

- FreqC 16F628A ElementsDocument1 pageFreqC 16F628A Elementsjubeng100% (1)

- Spare Parts List For Drive Unit Digga Pd6 - Pd7Document5 pagesSpare Parts List For Drive Unit Digga Pd6 - Pd7NOVIKOVNo ratings yet

- Part List 2.1 Amplifier Tda2030Document1 pagePart List 2.1 Amplifier Tda2030Antonieta Cano CruzNo ratings yet

- 2nd Nov Shruthi OrderDocument1 page2nd Nov Shruthi OrderRampam HemadriNo ratings yet

- TOTEM ELECTRO Crossreference Diod Tyristor Power Block-1Document10 pagesTOTEM ELECTRO Crossreference Diod Tyristor Power Block-1Mgc ElektronikNo ratings yet

- Recommended Spark Plug and Gasket Part NumbersDocument3 pagesRecommended Spark Plug and Gasket Part NumbersDjebali MouradNo ratings yet

- UL and CSA Approved: Magnetic Contactors and StartersDocument18 pagesUL and CSA Approved: Magnetic Contactors and StartersJerwei WooNo ratings yet

- Fiat Chrysler Materials Cross ReferenceDocument3 pagesFiat Chrysler Materials Cross Referencerolo6945No ratings yet

- L EDD Ri Ve R Co NT Ro LL Er T M163 8: 1, DescriptionDocument18 pagesL EDD Ri Ve R Co NT Ro LL Er T M163 8: 1, DescriptionJorge Luis Vega CaballeroNo ratings yet

- SN 7486Document20 pagesSN 7486mychelfNo ratings yet

- Sungrow Blue'log Driver: Description of FunctionsDocument3 pagesSungrow Blue'log Driver: Description of FunctionscanNo ratings yet

- SDNL 1Document1 pageSDNL 1Trọng LêNo ratings yet

- Spark Plug Selection TableDocument3 pagesSpark Plug Selection TableTamal Kumar PaulNo ratings yet

- MCP23009Document52 pagesMCP23009João Oliveira BentesNo ratings yet

- Tablica Vzaimozamenamosti Torcevie UplotneniaDocument1 pageTablica Vzaimozamenamosti Torcevie UplotneniaАйрат ГараевNo ratings yet

- Data Burst Controller – Rev 1Document2 pagesData Burst Controller – Rev 1vasireddysamratNo ratings yet

- Self-Aligning Bearing Units NTN-SNRDocument125 pagesSelf-Aligning Bearing Units NTN-SNRDenis DavydovNo ratings yet

- Racking BC 2014Document52 pagesRacking BC 2014kusnin nenNo ratings yet

- Inventaris Gedung Poliklinik 2022 FisioDocument1 pageInventaris Gedung Poliklinik 2022 FisioDolalaaaaNo ratings yet

- Tender Tracking Sheet - Updated 5th April2019Document97 pagesTender Tracking Sheet - Updated 5th April2019jaya shankarNo ratings yet

- BOQ VSD 2 X 90 KWDocument12 pagesBOQ VSD 2 X 90 KWAhmad Saepul BahriNo ratings yet

- UNIT3 - Introduction To IC Technology - 290617 - EditedDocument82 pagesUNIT3 - Introduction To IC Technology - 290617 - EditedKISHAN SHUKLANo ratings yet

- Pines City National High School Science 10 Quarter 2 Week 1 Answer SheetsDocument8 pagesPines City National High School Science 10 Quarter 2 Week 1 Answer SheetsAaron BalsaNo ratings yet

- Homework1 PDFDocument3 pagesHomework1 PDFYuanhao LiuNo ratings yet

- IP46 - Guide To Use BAPCO WPS & Welding ProceduresDocument4 pagesIP46 - Guide To Use BAPCO WPS & Welding ProceduressajiNo ratings yet

- Basic C MCQ - FinalDocument51 pagesBasic C MCQ - FinalDhivya DharshniNo ratings yet

- Sybsc Physics Practical Usphp3Document3 pagesSybsc Physics Practical Usphp3Ujjwala GokheNo ratings yet

- IOP Conference Series: Materials Science and EngineeringDocument9 pagesIOP Conference Series: Materials Science and EngineeringMahesh MNo ratings yet

- TDT4171 Artificial Intelligence Methods Task 5 Creating A Decision Support SystemDocument12 pagesTDT4171 Artificial Intelligence Methods Task 5 Creating A Decision Support SystemKermess McNo ratings yet

- B. Solving Quadratic EquationsDocument23 pagesB. Solving Quadratic EquationsHasnain -GamerNo ratings yet

- Ice o Matic - Cim0436faDocument2 pagesIce o Matic - Cim0436faJean RamosNo ratings yet

- Quality Control Analysis of Chlorpheniramine Maleate Marketed in NigeriaDocument7 pagesQuality Control Analysis of Chlorpheniramine Maleate Marketed in Nigeriaحمزة الفنينيNo ratings yet

- Kollidon 30 Technical InformationDocument10 pagesKollidon 30 Technical InformationhomarearisugawaNo ratings yet

- Probability DPP (1 To 7) 13th WADocument16 pagesProbability DPP (1 To 7) 13th WARaju SinghNo ratings yet

- List of Practical Cs With SolutionDocument57 pagesList of Practical Cs With SolutionArjun KalaNo ratings yet

- Planetary AlignmentDocument7 pagesPlanetary AlignmentEbn MisrNo ratings yet

- Molecular Cell Biology Lodish 7th Edition Solutions ManualDocument8 pagesMolecular Cell Biology Lodish 7th Edition Solutions ManualmarisorbornewwssNo ratings yet

- Multi-Band Booster With HRLB - In-Band Routed DCN Solution GuideDocument26 pagesMulti-Band Booster With HRLB - In-Band Routed DCN Solution GuideAchintha AluthmanageNo ratings yet

- Composition, Thermal and Rheological Behaviour of Selected Greek HoneysDocument13 pagesComposition, Thermal and Rheological Behaviour of Selected Greek HoneyssyazaqilahNo ratings yet

- The Pauli Exclusion PrincipleDocument33 pagesThe Pauli Exclusion Principle3449336893No ratings yet

- Inductive TransducersDocument12 pagesInductive TransducersMUKESH SUNDARARAJANNo ratings yet

- DBMS Lab QuestionsDocument4 pagesDBMS Lab Questionsvignesh dhayalanNo ratings yet

- Python Notes - 1Document364 pagesPython Notes - 1hopefulantonelliNo ratings yet

- Jm-10 Operation Manual Rev02 UnlockedDocument121 pagesJm-10 Operation Manual Rev02 UnlockedAlan Jimenez GonzalezNo ratings yet

- Medical Oxygen Cylinder Filling System User ManualDocument57 pagesMedical Oxygen Cylinder Filling System User ManualAldo Tolaba QuirogaNo ratings yet

- DMF360 Tandem Lift With ForkliftDocument4 pagesDMF360 Tandem Lift With Forkliftreda mesbahNo ratings yet

- Westminster Academy, Islamabad: Physics (0625) Topic Test:Sound WavesDocument5 pagesWestminster Academy, Islamabad: Physics (0625) Topic Test:Sound Wavessaimee77No ratings yet

- What Is XRF ?: Prepared by Lusi Mustika SariDocument34 pagesWhat Is XRF ?: Prepared by Lusi Mustika SariBayuNo ratings yet

- Essential Statistics For The Behavioral Sciences 1st Edition Privitera Solutions ManualDocument7 pagesEssential Statistics For The Behavioral Sciences 1st Edition Privitera Solutions Manualspinifexcandock8zf100% (26)

- Hazardous Area Hazardous Area ClassificaDocument106 pagesHazardous Area Hazardous Area ClassificaHedi Ben MohamedNo ratings yet

- Mic 2282Document10 pagesMic 2282mariusz sNo ratings yet