Professional Documents

Culture Documents

Vlsi Design Eee Ii Mid Qpaper

Uploaded by

Mahesh Babu MahiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vlsi Design Eee Ii Mid Qpaper

Uploaded by

Mahesh Babu MahiCopyright:

Available Formats

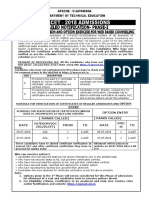

St.

Johns College of Engineering & Technology

Yerrakota, Yemmiganur – 518 360, Kurnool (Dist) A.P.

II-Mid Term Examination [Objective Type] Academic Year 2010-11 Invigilator Sign.

Year & Sem.: IV-B.Tech. I-Semester (R07) Branch & Section: EEE

Subject: VLSI DESIGN Max. Marks: 20 M

Regd.

Name: No.

Answer the following questions: 1 X 20 = 20 M

1. Logic synthesis systems are very useful for [ ]

a. transforming between technologies b. very good silicon implementation

c. to create control logic d. to create micro code

2. Behavioral synthesis is [ ]

a. technology dependent and specify the implementation

b. technology independent and specify the implementation

c. technology independent and without specify the implementation

d. technology dependent and without specify the implementation

3. Which of the following synthesis converts RTL description to a set of registers and combinational logic [ ]

a. behavioral synthesis b. RTL synthesis c. logic level synthesis d. layout synthesis

4. The number of input and output pins offered for CPLDs are [ ]

a. Higher b. Lower c. Less than FPGAs d. None

5. RTL description are captured using [ ]

a. hardware description language (HDL) b. software description language c. cathedral series d. micro controllers

6. The most detailed and accurate simulation technique is [ ]

a. gate level b. timing c. logic level d. circuit-level

7. In layout synthesis generally two phases are required they are [ ]

a. designing and minimizing b. placement and routing c. optimization of logic d. testing and verification

8. Many design systems generally used HDL because of [ ]

a. easy b. quickly understood c. small in size d. easily modified

9. The traditional method of capturing a digital system design is [ ]

a. schematic editor b. flow table c. ASIC design d. compiler

10. Simulations with delays are used to check the [ ]

a. timing problems b. DRC errors c. functionality d. speed of system

11. A design-rule-checker is used to [ ]

a. find DRC errors b. conforms the layout to the geometric design rules

c. verify the functionality of the geometric design rules d. verify the functionality of the design

12. The last step in the design process is [ ]

a. Layout extraction b. Back annotation c. Pattern Generation d. Design rule verification

13. For MOS circuits the dominant faults are due to [ ]

a. short circuits in diffusion layers b. open circuits in diffusion layer c. short circuits in interconnections d. none

14. Manufacturing tests are used to verify that [ ]

a. function of a chip as a whole b. every gate operates as expected c. function in the field d. none

15. VHDL, verilog hardware description languages are used for testing of [ ]

a. manufacturing tests b. functionality test c. Design testing d. chip testing

16. A FSM with 'n' possible i/ps to the combinational logic and 'm' elements then required test vectors are [ ]

a. m+n b. 2m c. 2nDocuments\LSI. d. none

17. Controllability in testing means [ ]

a. able to set known internal states b. able to generate all states c. able to generate all circuit states d. none

18. The faults occur due to thin-oxide shorts or metal-to metal shorts are called [ ]

a. stuck at zero faults b. short-circuit faults c. open-circuit faults d. bridge faults

19. The tests that are usually carried after chip is manufactured are called [ ]

a. functionality test b. design verification c. manufacturing test d. technology test

20. The layout is tested by using [ ]

a. Design rule checker b. simulator c. PROBE d. BILBO

St. Johns College of Engineering & Technology

Yerrakota, Yemmiganur – 518 360, Kurnool (Dist) A.P.

II-Mid Term Examination [Theory Type] Academic Year 2010-11

Branch &

Year & Semester: III-B.Tech. II-Semester (R07) Section: EEE

Name of the Max. Marks: 20 Marks

Subject: VLSI DESIGN

Section: A

Answer any two questions from the following three questions 2 X 7 = 14 M

1. What are the advantages of PLAs? Give the sketch for AND matrixes used in PLAs and explain its functionality?

2. What are different design verification tools and explain them in brief?

3. Explain about

a. Chip level test technique b. System level test technique

Section: B

Answer any one question from the following two questions 1X6=6M

4. Explain about CMOS testing and mention test principle for testing?

5. Using block schematics explain the terms: a. CPLDs b. FPGAs

______________________________________________________________________________________________

St. Johns College of Engineering & Technology

Yerrakota, Yemmiganur – 518 360, Kurnool (Dist) A.P.

II-Mid Term Examination [Theory Type] Academic Year 2010-11

Branch &

Year & Semester: III-B.Tech. II-Semester (R07) Section: EEE

Name of the Max. Marks: 20 Marks

Subject: VLSI DESIGN

Section: A

Answer any two questions from the following three questions 2 X 7 = 14 M

1. What are the advantages of PLAs? Give the sketch for AND matrixes used in PLAs and explain its functionality?

2. What are different design verification tools and explain them in brief?

3. Explain about

a. Chip level test technique b. System level test technique

Section: B

Answer any one question from the following two questions 1X6=6M

4. Explain about CMOS testing and mention test principle for testing?

5. Using block schematics explain the terms: a. CPLDs b. FPGAs

______________________________________________________________________________________________

You might also like

- Instructions / Checklist For Filling KYC FormDocument16 pagesInstructions / Checklist For Filling KYC FormMahesh Babu MahiNo ratings yet

- Global Banks Bodys Chief Supports Aadhaar 27042019 PDFDocument1 pageGlobal Banks Bodys Chief Supports Aadhaar 27042019 PDFMahesh Babu MahiNo ratings yet

- LNM 1Document42 pagesLNM 1KANHIYA78100% (1)

- Geometric Representation of Modulation Signals: Behnaam AazhangDocument4 pagesGeometric Representation of Modulation Signals: Behnaam AazhangMahesh Babu MahiNo ratings yet

- EDC Manual PDFDocument83 pagesEDC Manual PDFMrinal MitraNo ratings yet

- SNO Description Status: Option Entry Option Entry (Ranks Called) Date From TO Date FRO M TODocument2 pagesSNO Description Status: Option Entry Option Entry (Ranks Called) Date From TO Date FRO M TOsaiteja kattaNo ratings yet

- Electronic Devices and Circuits Lab Manual PDFDocument33 pagesElectronic Devices and Circuits Lab Manual PDFECE dept sietNo ratings yet

- The LC-3b ISADocument26 pagesThe LC-3b ISAJeff PrattNo ratings yet

- Ica Lab (135) Iii-IDocument87 pagesIca Lab (135) Iii-IesesesNo ratings yet

- 3858 Microprocessors and InterfacingDocument1 page3858 Microprocessors and InterfacingMahesh Babu MahiNo ratings yet

- Ece R15 PDFDocument195 pagesEce R15 PDFMahesh Babu MahiNo ratings yet

- Systemverilog Interview QuestionsDocument39 pagesSystemverilog Interview Questionsduck2No ratings yet

- 5441 Microprocessors & InterfacingDocument1 page5441 Microprocessors & InterfacingMahesh Babu MahiNo ratings yet

- Low Power VLSI Design: April 2015Document59 pagesLow Power VLSI Design: April 2015Mahesh Babu MahiNo ratings yet

- MP ManualDocument83 pagesMP ManualMithunKumarNo ratings yet

- R ResultDocument44 pagesR ResultMahesh Babu MahiNo ratings yet

- Final THE BIONIC CONTACT LENSDocument4 pagesFinal THE BIONIC CONTACT LENSMahesh Babu MahiNo ratings yet

- RR220201 Managerial Economics and Financial AnalysisDocument1 pageRR220201 Managerial Economics and Financial AnalysisMahesh Babu MahiNo ratings yet

- 37fuzzy LogicDocument12 pages37fuzzy LogicMahesh Babu MahiNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Oracle Solaris Guide For Linux Users: December 2016 (Edition 1.0) Fujitsu LimitedDocument74 pagesOracle Solaris Guide For Linux Users: December 2016 (Edition 1.0) Fujitsu LimitedShero KhanNo ratings yet

- Thought WorksDocument8 pagesThought WorksPritam MondalNo ratings yet

- Apc PCNS Hyper VDocument125 pagesApc PCNS Hyper VFaisal KNo ratings yet

- Change Request Template v1.1Document6 pagesChange Request Template v1.1Nikhil SatavNo ratings yet

- Uc 3841Document10 pagesUc 3841Nguyen Trong Long LongkioNo ratings yet

- BJT Terminal CharacteristicsDocument11 pagesBJT Terminal CharacteristicsTowsifTaherNo ratings yet

- Microsoft Dynamics CRM: by Akshata Raut - 77 Urvashi Roy - 78Document13 pagesMicrosoft Dynamics CRM: by Akshata Raut - 77 Urvashi Roy - 78Urvashi RoyNo ratings yet

- Network Security-Virus Attacks and Defence Using Antivirus SoftwareDocument3 pagesNetwork Security-Virus Attacks and Defence Using Antivirus SoftwareAhsan SakheeNo ratings yet

- User Manual Version 2Document17 pagesUser Manual Version 2Joseph ChanNo ratings yet

- ATtiny13, ATtiny2313, Instruction SetDocument19 pagesATtiny13, ATtiny2313, Instruction SetMihai PaunNo ratings yet

- 8051 Chap1 IntroductionDocument37 pages8051 Chap1 IntroductionNguyên NgọcNo ratings yet

- 2 Data Literacy Essentials of Azure Data FactoryDocument4 pages2 Data Literacy Essentials of Azure Data FactoryYue ZhaoNo ratings yet

- Dcs McqsDocument31 pagesDcs Mcqsiraj shaikhNo ratings yet

- IT103 Special Topics MidtermDocument5 pagesIT103 Special Topics MidtermMiles FranNo ratings yet

- Lecture 2 Introduction To Cloud ComputingDocument122 pagesLecture 2 Introduction To Cloud ComputingSteffyRobert0% (1)

- Public SolidworksDocument6 pagesPublic SolidworksSreedhar ReddyNo ratings yet

- 9 Axis E-Compass Manager Instruction-160613Document14 pages9 Axis E-Compass Manager Instruction-160613Hoang VuNo ratings yet

- Title Examine and Distinguish TCP/IP and OSI Model Using Packet Tracer. (CLO-3, PLO-5)Document6 pagesTitle Examine and Distinguish TCP/IP and OSI Model Using Packet Tracer. (CLO-3, PLO-5)Hadia RashidNo ratings yet

- Circuits Second 2nd Edition Ulaby Maharbiz CH1 SolutionsDocument53 pagesCircuits Second 2nd Edition Ulaby Maharbiz CH1 SolutionsConor Loo33% (3)

- CS 372 Answer KeyDocument22 pagesCS 372 Answer KeyDaniel NasolNo ratings yet

- 10.1.4.8 Lab - Configure ASA 5505 Basic Settings and Firewall Using ASDMDocument40 pages10.1.4.8 Lab - Configure ASA 5505 Basic Settings and Firewall Using ASDMerojasNo ratings yet

- Sv7k Technical OverviewDocument81 pagesSv7k Technical OverviewDashito_elreyNo ratings yet

- Layout Managers SwingDocument13 pagesLayout Managers Swingmelbin mathewNo ratings yet

- Networx Series: Nx-216E Zone Expander Module Installation and StartupDocument16 pagesNetworx Series: Nx-216E Zone Expander Module Installation and StartupEdison Macleiry Tejeda NúñezNo ratings yet

- Design and Play A MIDI Synthesizer - MATLAB & SimulinkDocument5 pagesDesign and Play A MIDI Synthesizer - MATLAB & SimulinkCavemaaaanNo ratings yet

- Manual FX9500Document78 pagesManual FX9500Gerardo LeyesNo ratings yet

- DFNT Protocol Manual p1Document35 pagesDFNT Protocol Manual p1eumetallicaNo ratings yet

- The Data Transfer Techniques: The Batch Input TechniqueDocument3 pagesThe Data Transfer Techniques: The Batch Input TechniquePreethan MurthyNo ratings yet

- Programming in Matlab: Ciro DonalekDocument25 pagesProgramming in Matlab: Ciro DonalekthynameisraymondNo ratings yet

- Hefshine Softwares Recruitment Praposal by Akshayt ParamaneDocument8 pagesHefshine Softwares Recruitment Praposal by Akshayt ParamaneAvinash JadhavNo ratings yet