Professional Documents

Culture Documents

LINE DIFF PROT

Uploaded by

Nirmal RajaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LINE DIFF PROT

Uploaded by

Nirmal RajaCopyright:

Available Formats

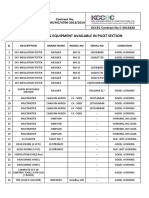

ASV KYV

ES1 ES2

SR1 SR2 SR3 SR4

L1 L2

Line Differential Protection Scheme Modelling for

Underground 420 kV Cable Systems

EMTDC/PSCAD Relays Modelling

Michal Sztykiel, Claus Leth Bak

Department of Energy Technology

Aalborg University

Aalborg, Denmark

clb@iet.aau.dk

Wojciech Wiechowski, Sebastian Dollerup

Protection & Control Systems

Energinet.dk

Fredericia, Denmark

sdo@energinet.dk

Abstract Based on the analysis of a specific relay model and an

HVAC (High Voltage Alternating Current) cable system, a new

approach to EMTDC/PSCAD modelling of protective relays is

presented. Such approach allows to create complex and accurate

relay models derived from the original algorithms. Relay models

can be applied with various systems, allowing to obtain the most

optimal configuration of the protective relaying. The present

paper describes modelling methodology on the basis of Siemens

SIPROTEC 4 7SD522/610. Relay model was verified

experimentally with its real equivalent by both EMTP-simulated

and real world generated current signals connected to the relay.

Keywords line differential protection; XLPE HVAC cable;

EMTDC/PSCAD relay model; SIPROTEC 4 7SD522; 7SD610

I. INTRODUCTION

Relay computer modelling is an important issue for

establishing proper protection scheme for the specified system.

Nowadays, it is difficult to obtain accurate relay computer

model, since relay manufacturers offer their products with a

variety of algorithms and features that may significantly

change operation of relays under specific conditions and states.

For this purpose, essential study over new approach for

creating relay models in EMTDC/PSCAD is given. The

methodology relies on obtained relays technical specification

(given by relays manufacturer), so that unique features and

algorithms - characteristic for each relay type, can be

developed. As a result, this would give complex relay model

narrowed and useful only for specified type of relay. In

compensation, relay computer model would be very accurate

(mainly in terms of sensitivity and operating speed) with easy

and user-friendly configuration panel, which is programmed

with the same parameter values as in real devices.

Established relay models would easily allow to perform

simulations of chosen study cases and examine possibilities of

unwanted tripping that might occur (e.g. due to transient power

electronics switching, overvoltages, external faults,

energization states, etc.).

This paper presents such analysis for Siemens line

differential relays SIPROTEC 4 SD522/610, as these relays are

planned to protect HVAC underground transmission cable

system built in Denmark in years 2012-2014.

Large capacitance of underground cables in comparison to

overhead lines brings original issues for the differential

protection scheme to consider, as both steady and transient

states have to be deeply analyzed. For steady state, charging

current is the factor that mostly affects relays function. For

transient states, relays may be affected by inrush currents that

occur due to shunt reactors switching operations (necessary for

reactive power compensation).

In order to properly reflect cable systems influence over

relays current signals in mentioned states, cable system is

modelled with the usage of EMTDC/PSCAD software, as it

provides satisfactory accuracy for both steady and transient

analysis.

When both cable system and protection scheme models are

completed, relay models accuracy can be finally verified

through experimental testing. Having identical parameter

setting both for relay model and real device, sensitivity and

operating speed are compared thus showing high accuracy of

the relay model.

Results from experimental analysis prove that presented

approach for relay modelling can be successfully adapted for

specific relays with original algorithms and features.

II. PROTECTED CABLE SYSTEM - BACKGROUND

A. Cable System - Description

The single phase diagram of total cable system is shown on

Fig. 1.

Figure 1. Schematic Representation of the Underground 420 kV Cable

System.

Fault Type Control

-------------------------------

1 = NoFault

2 = Phase Ato Ground

3 = Phase Bto Ground

4 = Phase CtoGround

5 = Phase AB toGround

6 = Phase ACto Ground

7 = Phase BCto Ground

8 = Phase ABCtoGround

9 = Phase AB

10 =PhaseABC

C1XLPE

S1

C2

S2

C3

S3

A

B

C

C1XLPE10

S1

C2

S2

C3

S3

C1XLPE2

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1 XLPE2

S1

C2

S2

C3

S3

C1XLPE3

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1 XLPE3

S1

C2

S2

C3

S3

C1XLPE4

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1 XLPE4

S1

C2

S2

C3

S3

C1XLPE5

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1 XLPE5

S1

C2

S2

C3

S3

A

B

C

C1XLPE6

S1

C2

S2

C3

S3

A

B

C

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1XLPE6

S1

C2

S2

C3

S3

C1 XLPE7

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

XLPE6 C

C1XLPE7

S1

C2

S2

C3

S3

C1 XLPE8

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1XLPE8

S1

C2

S2

C3

S3

C1 XLPE9

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1XLPE9

S1

C2

S2

C3

S3

C1 XLPE10

S1

C2

S2

C3

S3

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

C1 XLPE

S1

C2

S2

C3

S3

5.61 [H]2.858 [ohm]

5.61 [H]2.858 [ohm]

5.61 [H]2.858 [ohm]

KYVr

5.61 [H]2.858 [ohm]

5.61 [H]2.858 [ohm]

5.61 [H]2.858 [ohm]

A B C

ASVr

4.01 [H]2.159 [ohm]

4.01 [H]2.159 [ohm]

4.01 [H]2.159 [ohm]

4.01 [H]2.159 [ohm]

4.01 [H]2.159 [ohm]

4.01 [H]2.159 [ohm]

C B A

TOR2r

KYVr

ASVr

TOR2r

TOR1r

Timed Breaker Logic Open@t0

Timed Breaker Logic Open@t0

Timed Breaker Logic Open@t0

Timed Breaker Logic Open@t0

Ip1

Ip1

A

B

C

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

0.001 [ohm]

XLPE C XLPE2 C XLPE3 C XLPE4 C XLPE5 C

XLPE7 C XLPE8 C XLPE9 C XLPE10 C

Ip2

C B A

TOR1r

EN_1

EN_1

Timed Breaker Logic Closed@t0

Timed Breaker Logic Closed@t0 EN_2

EN_2

Ip2

Timed Fault Logic

A B C

FAULTS C

B

A

Timed Fault Logic

A B

V

Ph C

400.0 [kV], 50.0 [Hz]

10592 [MVA]

Z1 = 0.829 [ohm] + j16.6 [ohm]

A B

V

Ph C

400.0 [kV], 50.0 [Hz]

10477 [MVA]

Z1 = 0.839 [ohm] + j16.78 [ohm]

P_KYV

Q_KYV

P_ASV

Q_ASV

KYV

180

-180

PhaseAngle_1

0

degrees

PhaseAngle_1

0

500

0

Voltage_1

400

kV

Voltage_1

400

P_KYV

944

Q_KYV

82.6045

Main: Phasecurrents

0.000 0.025 0.050 0.075 0.100 0.125 0.150 0.175 0.200 ...

...

...

-1.00

-0.80

-0.60

-0.40

-0.20

0.00

0.20

0.40

0.60

0.80

kA

Ia1 Ia2

-0.80

-0.60

-0.40

-0.20

0.00

0.20

0.40

0.60

0.80

kA

Ia1 Ia2

-10.0 -8.0

-6.0 -4.0

-2.0 0.0 2.0 4.0 6.0

8.0 10.0

kA

Ia1 Ia2

Faults : Controls

10

9

8

7

6

5

4

3

2

1

External Fault

0

Sources Control Set Faults Control Set Faults Control Set

Description

Line Circuit Breakers

Control Set

Shunt Reactors Circuit Breakers

Control Set

Phase Currents Waveforms - both line ends

EXTERNAL FAULT INTERNAL FAULT

KYV source

ASV source

KYV shunt reactor

TOR1 shunt reactor TOR2 shunt reactor

ASV shunt reactor

ASV

180

-180

PhaseAngle_2

0

degrees

PhaseAngle_2

0

500

0

Voltage_2

400

kV

Voltage_2

400

P_ASV

1304.54

Q_ASV

444.498

Faults : Controls

10

9

8

7

6

5

4

3

2

1

Internal Fault

1

ASV KYV

Protected Zone

FO

DR DR

CT CT

The system consists of the following components:

1) XLPE HVAC Underground Cable Sections (L1L2):

Selected cable is made of three aluminium single-core cables

buried underground on the depth of 1,3 m and laid in a flat

formation within 300 mm from each other. Total cable is

divided into two sections of lengths accordingly 28 km and

29,5 km. Metallic screens of each cable section are cross-

bonded approximately each 2 km, and earthed each 6 km.

Detailed information about cable structure is presented on

table I.

TABLE I. TECHNICAL DATA OF XLPE UNDERGROUND 420 KV CABLE

Description Value

Cross-section of conductor (mm

2

) 1600

Diameter of conductor (mm) 52

Insulation thickness (mm) 27,0

Diameter over insulation (mm) 110,0

Cross-section of screen (mm

2

) 185

Outer diameter of cable (mm) 127,0

Capacitance (F/km) 0,21

Inductance (mH/km) 0,50

Charging current per phase (A/km) 14,9

2) Shunt Reactor Banks (SR1SR4): For reactive power

compensation, four switchable shunt reactors are installed;

each on ASV, KYV bus bars with reactive power of 100

MVARs and two between cable sections with reactive power

of 140 MVARs.

3) Supply Sources (ES1ES2): Power system on both sides

of the cable is modelled by ES1 and ES2 sources that are

Thevenin equivalents consisting of voltage sources and its

short-circuit impedances. Parameter values are listed on table

II.

TABLE II. TECHNICAL DATA OF CABLES SUPPLY SOURCES

Supply Source

Voltage

(kV)

Short-circuit impedance

()

ES1 420 0.829 + j16.60

ES2 420 0.839 + j16.78

B. EMTDC/PSCAD Model of Cable System

In Fig. 2, described cable system is modelled in

EMTDC/PSCAD software by frequency dependent (phase)

model, giving highest accuracy among other available models

[5]. Such modelled cable system may accurately reflect

behaviour of the protection scheme under various transient

states that are likely to appear. Further detailed information

about establishing computer model of the cable is available in

[5].

Shunt reactors are modelled with series resistance and

inductance parameter values for each phase.

Figure 2. EMTDC/PSCAD Representation of the Underground 420 kV

Cable System.

Table III shows validation results for three possible currents

that can flow through protected cable. Parameters were chosen

that mostly affect proper function of established differential

protection. Detailed methodology for cable model validation

along with series of calculations are given in [1-3].

TABLE III. VALIDATION RESULTS FOR EMTDC/PSCAD UNDERGROUND

CABLE MODEL

Description

Theoretical

Analysis

EMTDC/PSCAD

Model

Relative

error er

(%)

Maximum Charging

Current (kA)

0,878 0,805 8,3

External Fault at ASV

substation (kA)

9,555 11,49 16

Internal Fault in the

middle of the cable (kA)

11,85 12,94 8,4

Relative error is calculated from er = 100 |ITA - IPSCAD| / ITA, where: ITA current parameter value

obtained algebraically; IPSCAD current parameter value obtained numerically.

Relative error originates from cable geometry, since mutual

couplings between internal conductive cable layers take place.

This corresponds to core conductors and screens that are in

close proximity to each other. Resulting inductive reactance for

single phase is lower than calculated algebraically, thus giving

higher current value which rises significantly when high

currents flow through cable [2].

Validation results allow to conclude that certain error level

occurs and has to be taken into account. Higher fault current

values from EMTDC/PSCAD simulations allow to keep

safety margin for the analysis based on simulation results.

C. Differential Protection Scheme Description

Total differential protection scheme for the analyzed cable

system is presented in Fig. 3.

Figure 3. Schematic Representation of the Differential Protection Scheme

over Underground 420 kV Cable System.

cross_A

cross_A

cross_B

PHASE C

A

B

Ctrl

Ctrl = 1

1

EN_1

EN_2

EN_1

EN_2

e-sT

e-sT

e-sT

SAMPLER

PHASE A

PHASE B

cross_B

cross_C

cross_C

trip_C

trip_B

trip_B

trip_C

ib1

ic1

ia1

cross_Ar

cross_Ar

cross_Br A

B

Ctrl

Ctrl = 1

1

B2 cross_Br

cross_Cr

cross_Cr

trip_Cr

trip_Br

trip_Br

trip_Cr

PHASE A

PHASE B

PHASE C

SAMPLER

SAMPLER

SAMPLER

SAMPLER

SAMPLER

ia2

ic2

ib2

trip_Ar trip_Ar trip_A trip_A

e -sT

e -sT

e -sT

B1

SIGNAL

TRANSFORMATION

SIGNAL

TRANSMISSION

SIGNAL

PROCESSING

e

-sT

e

-sT

e

-sT cross_A

cross_A

cross_B

PHASE C

A

B

Ctrl

Ctrl = 1

1

EN_1 EN_1

SAMPLER

PHASE A

PHASE B

cross_B

cross_C

cross_C

trip_C

trip_B

tri p_B

tri p_C

SAMPLER

SAMPLER

trip_A tri p_A

B1

Idiffx

Qdiffxx

Inrush Restraint Ratio

MAXinrush peak

Inrush ON / OFF

1.76

Idiffx

3.52

Idiffxx

0.15

Inrush Restraint Ratio

16.33

MAXinrush peak

1

P1 3.3

P1

*

4.502

Idiffx2 3.52

Idiffx2

Qdiffxx2 7.04

Idiffxx2

*

4.502

Main: Controls

cross-blocking

0

OFF ON

ABC: Graphs

0.040 0.050 0.060 0.070 0.080 0.090 0.100 ...

...

...

0.0

1.0

2.0

y

XX

ABC: Graphs

0.040 0.050 0.060 0.070 0.080 0.090 0.100 ...

...

...

-0.40

-0.30

-0.20

-0.10

0.00

0.10

0.20

0.30

0.40

y

Ia11 Ia11_11 S3 S4 phasor_Ma1 phasor_Pa1 XX

Ia11_1

S / H

in

hol d

out Ia11 Ia11_2

S / H

in

hol d

out Ia11 Ia11_3

S / H

in

hold

out Ia11 Ia11_4

S / H

i n

hold

out Ia11 Ia11_5

S / H

i n

hold

out Ia11 Ia11_6

S / H

i n

hold

out Ia11 Ia11_7

S / H

in

hold

out Ia11 Ia11_8

S / H

in

hol d

out Ia11 Ia11_9

S / H

in

hol d

out Ia11 Ia11_10

S / H

in

hold

out Ia11

Ia11_11

S / H

in

hol d

out Ia11 Ia11_12

S / H

in

hol d

out Ia11 Ia11_13

S / H

in

hold

out Ia11 Ia11_14

S / H

i n

hold

out Ia11 Ia11_15

S / H

i n

hold

out Ia11 Ia11_16

S / H

i n

hold

out Ia11 Ia11_17

S / H

in

hold

out Ia11 Ia11_18

S / H

in

hol d

out Ia11 Ia11_19

S / H

in

hol d

out Ia11 Ia11_20

S / H

in

hold

out Ia11

Ia11_1

S / H

in

hold

out

Ia11

I

a

1

1

I

a

1

1

_

1

D11

D

1

1

Proposed protection scheme consists of following

components:

1) Current Transformers (CT): Devices responsible for

current signal transformation on the level applicable for

measuring instruments installed in protection relays. Table IV

shows current transformers specification used for computer

modelling purpose.

TABLE IV. TECHNICAL DATA OF CURRENT TRANSFORMERS (CT)

Parameter Value

CT manufacturers model ABB IMB 420

CT class 5P

Transfomation ratio (A/A) 1000/1

Accuracy Limit Factor ALF 100

Nominal Power (VA) 15

2) Mono-mode Fibre Optic Cables (FO): Communication

channels responsible for proper signal transmission between

relays. Due to significant length of the protected cable (58,5

km), signal attenuation phenomenon must be considered along

with time delay between sending and reaching signal from

both sides of the protected cable. Reference [2] explains

detailed solution methodology to stated issues. Channel time

delay is calculated based on datasheet provided by fibre optic

cables and relays manufacturers. Necessary data are gathered

in table V.

TABLE V. TECHNICAL DATA OF FIBRE OPTIC CABLES (FO)

Index Parameter Value

vB Bandwidth Data Speed (bits/s) 512

lFO FO Length (km) 58,5

vFO FO Speed of Light (km/s) 200000

lB HDLC Frame Length (bits) 200

Channel time delay T

delay

is 1,07 ms, calculated from

B

B

FO

FO

B

B

r t s delay

v

l

v

l

v

l

T T T T + + = + + = . (1)

where

T

s

time for sending signal by the local relay,

T

t

time for transmitting signal through FO cable,

T

r

time for receiving signal by the remote relay.

3) Line Differential Relays (DR): Most complex

components realizing signal measurement, signal comparison

and finally - fault detection principles. Relays analyzed in this

paper are Siemens SIPROTEC 4 7SD522. Detailed technical

specification, instruction on establishing proper configuration

parameter set are available in [1], [3] and [4].

D. EMTDC/PSCAD Model of Differential Protection Scheme

A general approach is introduced for protection scheme

modelling in PSCAD software.

Based on previous components description, their unique

characteristic functions are presented on Fig. 4. Each

component is responsible for:

Figure 4. EMTDC/PSCAD Representation of the Differential Protection

Scheme over Underground 420 kV Cable System.

Signal transformation, modelled by Current

Transformer Lucas model blocks with specified

parameter settings. Reference [6] provides more

information regarding CT Lucas model.

Signal transmission, modelled by time delay blocks

with specified and calculated time delay value from

(1).

Signal processing, modelled with complex block

combination, reflecting operation algorithm and

original features of real relays.

III. EMTDC/PSCAD RELAY MODELLING

Relay EMTDC/PSCAD computer model is created in a

shape of box with three phase modules included, so that all

operations are phase segregated as in real relays (see Fig. 7).

Input signals for modules are previously sampled with sampler

blocks, so that 20 sampled values appear each full cycle period

(fixed frequency) [3]. Output logic signal B1 is responsible for

controlling line circuit breaker in case of possible fault

occurrence. Following features are included in each phase

module:

1) Sample Acquisition: Operation necessary for further

phasor and charge computations. Sample values i

n

have to be

stored during full cycle. This operation is available by

implementing 20 Sample/Hold blocks each controlled by

logic pulse generator block, as presented on Fig. 5. Pulse

generator blocks give command D for each sample/hold block.

Generated pulses are shifted to each other by 18

degrees of

total cycle period.

Figure 5. EMTDC/PSCAD Representation of Sample Acquisition

Technique.

phasor_Ma1 D

+

F

+

Y

X

M X

P Y

M

P

Y

X

M X

P Y

M

P

phasor_Pa1

D

+

F

+ D

+

F

+

X

2

X

2 X

phasor_Ma2

phasor_Pa2 IopA_phasor dyta

Low pass

Butterwth

Order = 1

Sampler

a)

b)

B

+

D

+

F

+

*

*

IresA_phasor

phasor_Ma1

phasor_Ma2

A

B Compar-

ator

A

B Compar-

ator

Idiffx

P1

P1

[Main] Idiffx

[Main] Idiffx2

Edge

Detector

A

B

Ctrl

Ctrl = 1

Idiffx2

Idiffx2

Mono-

T

stable

A

B

Ctrl

Ctrl = 1

EN_1

[Main] EN_1

A

B Compar-

ator

P1

phasor_Ma2 P3

P1 phasor_Ma1 P1 < phasor_Ma1

A

B Compar-

ator

P1

phasor_Ma2 P2

2) Phasor Measurement: current phasor values I are

obtained in the shape of complex numbers through Discrete

Fourier Transform technique, based on

C S

I j I I + = . (2)

where

=

1

1

2

N

n

n S

i ) t n sin(

N

I . (3)

+ + =

=

1

1

0

2 2

2

N

n

n

N

C

i ) t n cos(

i i

N

I . (4)

Herein are

n = 1,2,,20 sample number,

i

n

current sample value corresponding to sample n,

= 2f cycle pulsation,

t = (f N)

-1

sample time interval,

f = 50 Hz frequency,

N = 20 number of samples over one cycle.

Equations (3) and (4) are realized by correlating sample

values with sine and cosine waveforms and summating them

each full cycle period [1].

3) Charge Measurement: Charge values Q are obtained

based on

i

n

n

n

n i

i

t i dt i Q

5

0

5

=

+

+

+

=

. (5)

Four charge values are calculated each full cycle period. By

applying signal switch block, final charge signal is switched

each quarter cycle. This corresponds to real relay feature,

where charge comparison is performed four times more often

than phasor comparison.

4) Phasor Comparison: based on relays principles given

in [1], values for operational phasor I

OP

and restraint phasor

I

RES

are obtained and relay operating criterion is

RES OP

I I > , (6)

for

>

>

+ =

>

1 3

1 2

1 3

1 2

2 2

2 2

1 1

1 1

P I : I P

P I : I P

P I : I P

P I : I P

I I

diff RES

. (7)

2 1

I I I

OP

+ = . (8)

Relay setting parameters P1, P2, P3 and I

diff>

are chosen

based on procedure given in [3] and [4]. Parameters I

1

and I

2

are current phasor values correspondingly measured by local

and remote relays. Operation of switching multiplying factors

for restraint phasor (determined by current signal value in

fault state or load state) is made with the usage of comparator

blocks, which output signal is multiplied by its corresponding

actual phasor current signal value, as shown on Fig. 6.

Based on information obtained from the position of line

circuit breaker installed on the same side as device, differential

relay can detect dead line state when no current flows

through the protected cable. Cable energization state when

circuit breaker is suddenly switched on is detected by Edge

Detector block by positive transition appearance of signal from

line circuit breakers. This allows generating digital impulse,

which is later extended to the specified time interval - Td

setting, which can be changed based on relay settings by

Monostable Multivibrator block.

Figure 6. EMTDC/PSCAD Representation of Phasor Comparison technique:

a) Restraint phasor IRES, b) Operational phasor IOP.

5) Charge Comparison: for this technique, the same

algorithm is used as for phasor comparison. I

diff>

parameter is

replaced with minimum threshold value for charges: I

diff>>

. In

addition, phasor signals are replaced with their corresponding

operational Q

OP

and restraint Q

RES

charge values.

6) Signal Filtering: operational and restraint values are

filtered using low-pass Butterworth filter block with

established frequency threshold corresponding to each

comparison technique.

7) Inrush Restraint: 2nd harmonic phasor currents I

2nd

are

measured by online frequency scanner blocks. If its values

exceed established ratio k

ratio

of 1st harmonic I

1st

, relay

prevents tripping operation. In EMTDC/PSCAD model this

feature can be switched OFF as in real relays. Condition

statement (9) has to be fulfilled in order to activate inrush

restraint blocking feature. Upper limit for non-tripping

operation is established with I

max_peak

parameter

( ) ( )

peak max_

st st

ratio

nd

I I I k I < >

1 1 2

. (9)

Comparison principles are obtained with a combination of

comparator blocks. Output signals from comparators can then

cross_A

cross_A

cross_B

PHASE C

A

B

Ctrl

Ctrl = 1

1

EN_1

EN_1

SAMPLER

PHASE A

PHASE B

cross_B

cross_C

cross_C

trip_C

trip_B

trip_B

trip_C

SAMPLER

SAMPLER

trip_A trip_A

B1

PHASE_C: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280 0.320 0.360 0.400 0.440 0.480 ...

...

...

0.0

3.0

6.0

9.0

12.0

15.0

A

IopC_phasor IresC_phasor IopC_charge IresC_charge

PHASE_B_1 : Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280 0.320 0.360 0.400 0.440 0.480 ...

...

...

0.0

3.0

6.0

9.0

12.0

15.0

A

IopB_phasor IresB_phasor IopB_charge IresB_charge

PHASE_A_1 : Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280 0.320 0.360 0.400 0.440 0.480 ...

...

...

0.0

3.0

6.0

9.0

12.0

15.0

A

IopA_phasor IresA_phasor QopA_charge QresA_charge

PHASE_C: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240

0.0

6.0

12.0

18.0

24.0

30.0

36.0

42.0

48.0

54.0

60.0

66.0

A

IopC_phasor IresC_phasor

PHASE_B_1: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240

0.0

6.0

12.0

18.0

24.0

30.0

36.0

42.0

48.0

54.0

60.0

66.0

A

IopB_phasor IresB_phasor

PHASE_A_1 : Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240

0.0

6.0

12.0

18.0

24.0

30.0

36.0

42.0

48.0

54.0

60.0

66.0

A

IopA_phasor IresA_phasor

r

e

s

t

r

a

i

n

t

p

h

a

s

o

r

I

R

E

S

o

p

e

r

a

t

i

o

n

a

l

p

h

a

s

o

r

I

O

P

C

p

h

a

s

e

(

A

)

B

p

h

a

s

e

(

A

)

A

p

h

a

s

e

(

A

)

r

e

s

t

r

a

i

n

t

c

h

a

r

g

e

Q

R

E

S

o

p

e

r

a

t

i

o

n

a

l

c

h

a

r

g

e

Q

O

P

C

p

h

a

s

e

(

A

s

)

B

p

h

a

s

e

(

A

s

)

A

p

h

a

s

e

(

A

s

)

a) b)

Time (s) Time (s)

IRES

IOP

QRES

QOP

PHASE_C: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280 0.320 0.360 0.400 0.440 0.480 ...

...

...

0.00

0.50

1.00

1.50

2.00

2.50

3.00

3.50

4.00

4.50

5.00

A

IopC_phasor IresC_phasor IopC_charge IresC_charge

PHASE_B_1: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280 0.320 0.360 0.400 0.440 0.480 ...

...

...

0.00

0.50

1.00

1.50

2.00

2.50

3.00

3.50

4.00

4.50

5.00

A

IopB_phasor IresB_phasor IopB_charge IresB_charge

PHASE_A_1 : Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280 0.320 0.360 0.400 0.440 0.480 ...

...

...

0.00

0.50

1.00

1.50

2.00

2.50

3.00

3.50

4.00

4.50

5.00

A

IopA_phasor IresA_phasor QopA_charge QresA_charge

PHASE_C: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280

0.0

5.0

10.0

15.0

20.0

25.0

30.0

35.0

40.0

A

IopC_phasor IresC_phasor IopC_charge

PHASE_B_1 : Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280

0.0

5.0

10.0

15.0

20.0

25.0

30.0

35.0

40.0

A

IopB_phasor IresB_phasor IopB_charge

PHASE_A_1: Graphs

0.000 0.040 0.080 0.120 0.160 0.200 0.240 0.280

0.0

5.0

10.0

15.0

20.0

25.0

30.0

35.0

40.0

A

IopA_phasor IresA_phasor QopA_charge

r

e

s

t

r

a

i

n

t

p

h

a

s

o

r

I

R

E

S

o

p

e

r

a

t

i

o

n

a

l

p

h

a

s

o

r

I

O

P

C

p

h

a

s

e

(

A

)

B

p

h

a

s

e

(

A

)

A

p

h

a

s

e

(

A

)

r

e

s

t

r

a

i

n

t

c

h

a

r

g

e

Q

R

E

S

o

p

e

r

a

t

i

o

n

a

l

c

h

a

r

g

e

Q

O

P

C

p

h

a

s

e

(

A

s

)

B

p

h

a

s

e

(

A

s

)

A

p

h

a

s

e

(

A

s

)

a) b)

Time (s) Time (s)

IRES

IOP QRES

QOP

be combined with logic gates so that tripping signal depends on

the resulting signal from the inrush restraint feature.

8) Cross-blocking: in order to prevent tripping signals

from all three phases when inrush feature is active in only

single phase, cross-blocking feature is introduced. Its PSCAD

representation is shown on Fig. 7.

Figure 7. EMTDC/PSCAD Representation of Cross-Blocking Technique.

In EMTDC/PSCAD computer model, cross-blocking

utilizes single phase tripping and inrush activation signals as

the output signals of each phase module. Combining them all

with logic gates gives final tripping signal decision B1. Hence,

described feature has to be implemented outside phase

modules. As in real relays, feature can be permanently

switched OFF during normal operation.

Original EMTDC/PSCAD files with fully established and

configured models of relays and protected cable system are

available at main author on request.

IV. EMTDC/PSCAD SIMULATION CASES

A. Two-Phase External Fault at KYV substation

External fault simulation in phases A and B allows analysis

on how relay computer model reacts when high currents flow

through the protected cable. Fault is cleared after 55 ms by

virtual bus protection installed in place where fault occurred.

All shunt reactors are disconnected (highest charging current).

Simulation graphs are presented on Fig. 8.

Figure 8. External Fault State at 10 ms: a) Phasor Comparison Technique, b)

Charge Comparison Technique.

Due to high currents flowing through phases A and B

which are higher than calculated P1 value [4], transition takes

place resulting in switching multiplying factors from P2 to P3

value. This means that transformed secondary current lies

within fault area and security margin is increased in

corresponding phases. On presented plots, restraint threshold is

higher for the time when external fault current flows. After

fault clearing, restraint values return to its normal threshold

levels since transformed current lies once again within load

area. An increase of operational values in phases with high

current appears after fault clearing, giving large safety margin

in order to prevent unwanted tripping. It is seen that during

whole simulation operational values do not exceed restraint

ones. As a result, relay properly does not detect any fault

within protected cable and does not send tripping signal.

B. Single-Phase Intenal Fault at KYV substation

Simulation test involves internal fault appearance in phase

A within protected cable. As the worst case scenario, single A-

phase fault is applied with high resistance R

fault

= 20 and all

shunt reactors are switched ON (lowest charging current).

Computer model with established setting parameters should be

able to properly detect and recognize fault state within phases.

Figure 9 presents described simulation case results .

Figure 9. Internal Fault State at 10 ms: a) Phasor Comparison Technique, b)

Charge Comparison Technique.

As expected, internal fault occurred in A phase and is

detected by relay computer model both with phasor and charge

comparison techniques. Operational values significantly exceed

restraint ones after 20 ms from fault occurrence for phasor and

15ms for charge comparison principles. Earlier fault detection

with charge technique results in sending tripping signal after

15ms in order to disconnect faulted cable.

V. RELAY TESTING

A. Description

Relay experimental testing is possible with the usage of

modern equipment and software capable of converting current

signals from EMTDC/PSCAD software into current

waveforms injected into real differential relays. Simplified

diagram of experimental test setup is presented on Fig. 10.

U

DC

supply

Ia11

Ib11

Ic11

FO cable

DIGSI 4.81

Advanced Transplay

UDC supply

Ia22

Ib22

Ic22

Figure 10. Experimental Test Setup.

Six current signals are sent: Ia11, Ib11, Ic11, Ia22, Ib22,

Ic22 from which three enter to each relay accordingly to the

side from which they were measured. Relays interconnected

together with fibre optic cable, respond based on delivered

signals with measured values and annunciation messages saved

as logs. These logs can then be sent to PC and read in DIGSI

software for further analysis and for comparison purposes.

B. Results

All tests from experimental analysis and EMTDC/PSCAD

simulations were performed with the same setting parameter

values. Relays operating speed and sensitivity have been

examined.

1) Operating Speed: Operating speed analysis gives idea

on how fast relay is able to detect fault states. By the analysis

of restraint/operational plots in EMTDC/PSCAD computer

software, time interval between exceeding threshold by

operational charge value Q

OP

and phasor value I

OP

can be

compared with the ones obtained from DIGSI logs. Analyzed

study case results are presented on table VI.

TABLE VI. VALIDATION RESULTS OF OPERATING SPEED FOR

EMTDC/PSCAD RELAY MODEL

Time interval (ms)

Case description

Experimental

Results

PSCAD

Simulation Results

Single-phase to ground internal

fault in the middle

8 14

Single-phase to ground internal

fault at KYV busbar

8 14

Two-phase to ground internal

fault at KYV busbar

14 14 15 15

Three-phase to ground internal

fault KYV busbar

18 12 18 15 10 15

2) Sensitivity: Relays sensitivity analysis is critical for

proper internal fault states recognition. For this reason,

internal faults with very high resistance values were analyzed.

Differential threshold parameter I

diff>

for phasor comparison

was adjusted in order to obtain its critical threshold values.

Results are listed and compared in table VII. Phasor

comparison is examined since it is more sensitive and

necessary for proper fault detection. Critical values are these

on which relay still detects fault and - if increased of a single

setting step - makes no reaction for the same fault conditions.

TABLE VII. VALIDATION RESULTS OF SENSITIVITY FOR EMTDC/PSCAD

RELAY MODEL

Differential phasor Idiff>

threshold for tripping

Differential phasor Idiff>

threshold for non-tripping

Internal

fault

resistance

()

Experimental

Results

PSCAD

Simulation

Results

Experimental

Results

PSCAD

Simulation

Results

55 4,02 4,05 4,03 4,06

70 3,23 3,25 3,24 3,26

145 1,72 1,73 1,73 1,74

210 1,31 1,32 1,32 1,33

VI. CONCLUSIONS

EMTDC/PSCAD relay computer model proves to be

reliable and efficient from taken simulation cases with

established parameter set. Apart from internal and external

fault states, analyzed simulation cases included transmission

cables energization and shunt reactors energization states,

giving overall 10 different study cases [2]. All simulation

results have been successfully compliant with the expected

ones.

According to simulation results, relay model is able to

accurately detect internal faults and differentiate them with

mentioned other states that may be misleading. Very high fault

resistances from which relay cannot detect faults marks

efficiency of specific algorithms implemented and used for

measurement and comparison purposes of the obtained signals.

VII. ACKNOWLEDGMENT

The first author gratefully acknowledges research support

from the Danish TSO - Energinet.dk, which delivered all

necessary technical data of the analyzed system along with

Siemens SIPROTEC 4 7SD522 relays.

VIII. REFERENCES

[1] G. Ziegler, Numerical Differential Protection: Principles and

Applications, Nuremberg, Germany: Siemens AG, Jul. 2005.

[2] M. Sztykiel, Protection philosophies for HVAC transmission network,

M.S. thesis, IET, Aalborg Univ., Aalborg, Denmark, 2009.

[3] SIPROTEC 4 Differential Protection 7SD52 V4.1 Manual, Siemens AG,

Nuremberg, Germany, 2002.

[4] T. Sezi at al., Field Experience Summary with a Line Differential

Relay Using Complex Communication Infrastructure, Siemens Energy,

Inc., Nuremberg, Germany, Sep. 2009.

[5] Applications of PSCAD/EMTDC Application Guide, Manitoba HVDC

Research Centre Inc., Winnipeg, Canada.

[6] J. Rohan Lucas, Representation of Magnetisation Curves over a wide

region using a non-integer power series, IJEEE: Manchester Univ.

Press, vol. 25, No 4, pp. 335-340, Oct. 1988.

You might also like

- 7PG15 TR Catalogue SheetDocument30 pages7PG15 TR Catalogue SheetRavishankar.Azad0% (1)

- Rej525 Tob 751205enc PDFDocument12 pagesRej525 Tob 751205enc PDFJayam KondanNo ratings yet

- Transformer Protection RET670: Exercise 3 - Differential Protection Open CT and OLTC AdjustmentDocument22 pagesTransformer Protection RET670: Exercise 3 - Differential Protection Open CT and OLTC AdjustmentRobert MihayoNo ratings yet

- GE Multilin T60 V6.0x Transformer PTT User Manual ENUDocument8 pagesGE Multilin T60 V6.0x Transformer PTT User Manual ENURaúlEmirGutiérrezLópezNo ratings yet

- 06 SEP674 RET670 Thermal Overload ProtectionDocument17 pages06 SEP674 RET670 Thermal Overload Protectionطه محمدNo ratings yet

- 86lor1 PDFDocument14 pages86lor1 PDFjunsana0% (1)

- Easergy Micom P544/P546: Current Differential Protection RelayDocument72 pagesEasergy Micom P544/P546: Current Differential Protection RelayNermina MalićevićNo ratings yet

- 7UT613 63xDocument514 pages7UT613 63xdenisseNo ratings yet

- OfflineOrderNumber Tool Ver15 50d 758059ENmDocument77 pagesOfflineOrderNumber Tool Ver15 50d 758059ENmEmir Kamberović100% (1)

- Epac 3000 Rev2 Hardware Manual Rev 1.0Document33 pagesEpac 3000 Rev2 Hardware Manual Rev 1.0Anonymous ouFzvkzNo ratings yet

- Ret670 Setting ManualDocument1,430 pagesRet670 Setting ManualAndrea MaurillaNo ratings yet

- 7SK80 Protection of Medium-Power Motors A1 PDFDocument11 pages7SK80 Protection of Medium-Power Motors A1 PDFpothirajNo ratings yet

- REL 531-1-0 Line Distance Protection TerminalDocument20 pagesREL 531-1-0 Line Distance Protection Terminalsenthil kumarNo ratings yet

- Line Distance Protection IED REL 670Document47 pagesLine Distance Protection IED REL 670kass_ecs100% (1)

- Siprotec 4, Siprotec Easy, SIPROTEC 600 Series, Communication, AccessoriesDocument878 pagesSiprotec 4, Siprotec Easy, SIPROTEC 600 Series, Communication, AccessoriesrsantanaNo ratings yet

- Ziv Oc Ef RelayDocument10 pagesZiv Oc Ef RelayAnonymous QRER3bsNr100% (1)

- 61850-9-2LE ConceptDocument65 pages61850-9-2LE ConceptrenegadeNo ratings yet

- Phased Out Products and Their ReplacementsDocument4 pagesPhased Out Products and Their ReplacementsGanesan SelvamNo ratings yet

- P34x Relay Documentation UpdateDocument616 pagesP34x Relay Documentation Updatewiyatno100% (1)

- Site Inspection and Test Record: Feeder/Bay: Ohl - 9013 1 General Data and InformationDocument15 pagesSite Inspection and Test Record: Feeder/Bay: Ohl - 9013 1 General Data and InformationMahmoud ShafieNo ratings yet

- 1MRB520006-BEN en XS92b Computer-Based 3-Phase Test SetDocument14 pages1MRB520006-BEN en XS92b Computer-Based 3-Phase Test SetFredrikNo ratings yet

- Transformer Protection RET670: Exercise 4 - Differential Protection Negative Sequence FeatureDocument17 pagesTransformer Protection RET670: Exercise 4 - Differential Protection Negative Sequence FeatureRobert MihayoNo ratings yet

- 1 DC System DC AC Circuit at The Sub StationDocument19 pages1 DC System DC AC Circuit at The Sub Stationapi-258852000% (1)

- P545+P546 GPSDocument24 pagesP545+P546 GPSDipankar MukherjeeNo ratings yet

- Relay Selection Chart1Document3 pagesRelay Selection Chart1Susil Kumar Khuntia100% (1)

- 115kV - E02 - 60R - ROC Feerder 1 - RED670 Differential Relay - at Glow SideDocument10 pages115kV - E02 - 60R - ROC Feerder 1 - RED670 Differential Relay - at Glow SideYongchayut WiratchatiNo ratings yet

- ABB - Across The Line Cont ActorsDocument136 pagesABB - Across The Line Cont ActorsdnaviauxNo ratings yet

- MiCOM IDMT Curves CalculatorDocument2 pagesMiCOM IDMT Curves CalculatorYigit SarıkayaNo ratings yet

- 1MRK504172-BEN - en Product Guide Transformer Protection RET650 Version 2.2Document80 pages1MRK504172-BEN - en Product Guide Transformer Protection RET650 Version 2.2Pavel DobiasNo ratings yet

- SIP5 7UT85-86-87 V09.20 Manual C094-1 en PDFDocument2,406 pagesSIP5 7UT85-86-87 V09.20 Manual C094-1 en PDFDanilo SilvaNo ratings yet

- 400 KV Bus Changeover &isolationDocument4 pages400 KV Bus Changeover &isolationSreekanthMylavarapuNo ratings yet

- Nepal hydropower generator protection relay specificationsDocument5 pagesNepal hydropower generator protection relay specificationsPritam SinghNo ratings yet

- Micom P540 Series Current Differential RelaysDocument24 pagesMicom P540 Series Current Differential Relaysdave chaudhuryNo ratings yet

- Relay Type / Make: GE T60 General Data:: SYS FmaxDocument6 pagesRelay Type / Make: GE T60 General Data:: SYS FmaxAntony JoeNo ratings yet

- P010501-Nml-70-Ele-Dts-005 TPG of 20KV NGR Rev A Nen1Document26 pagesP010501-Nml-70-Ele-Dts-005 TPG of 20KV NGR Rev A Nen1Lukky AdoeNo ratings yet

- 615 Series IEC 61850 Engineering Guide - GDocument68 pages615 Series IEC 61850 Engineering Guide - GHimdad TahirNo ratings yet

- Testing of BushingDocument8 pagesTesting of BushingAmir Ali khanNo ratings yet

- Current Differential Line Protection Setting ConsiderationsDocument28 pagesCurrent Differential Line Protection Setting ConsiderationskankokwahNo ratings yet

- Technical Instruction ABB RED670Document10 pagesTechnical Instruction ABB RED670Iqball ArdiyanNo ratings yet

- P14N TM en 6.1Document448 pagesP14N TM en 6.1Michael adu-boahenNo ratings yet

- 06 Sep-603b Ref Ret 670 PDFDocument13 pages06 Sep-603b Ref Ret 670 PDFm khNo ratings yet

- P633 - Test - Tools Farhad Rev 01Document4 pagesP633 - Test - Tools Farhad Rev 01Mosa Elnaid ElnaidNo ratings yet

- XS2 - Negative Sequence Relay: Original Technical Manual XS2 (Revision B)Document20 pagesXS2 - Negative Sequence Relay: Original Technical Manual XS2 (Revision B)Catrina FedericoNo ratings yet

- Type P8n, PQ8n, PN8n: Auxiliary RelayDocument7 pagesType P8n, PQ8n, PN8n: Auxiliary RelayDinesh ThevanNo ratings yet

- RED670 LDCM Module Communication IssuesDocument4 pagesRED670 LDCM Module Communication IssuesSellappan MuthusamyNo ratings yet

- 7UT6 Transformer Differential Protection: Vector Group, Io-Elimination, Io-CorrectionDocument11 pages7UT6 Transformer Differential Protection: Vector Group, Io-Elimination, Io-Correctionpraful varsadaNo ratings yet

- ProtectionDocument157 pagesProtectionsivaepeNo ratings yet

- Out-Of-step Protection For Generators GER-3179Document28 pagesOut-Of-step Protection For Generators GER-3179robertoseniorNo ratings yet

- Feeder Terminal Product Guide REF 542plusDocument28 pagesFeeder Terminal Product Guide REF 542plusRazvan MaresNo ratings yet

- Transformer Differential RelayDocument6 pagesTransformer Differential Relayabkrishnan100% (2)

- Configuring The P543 IEC61850 Device For Sicam CompatibilityDocument9 pagesConfiguring The P543 IEC61850 Device For Sicam CompatibilityAri SulistionoNo ratings yet

- Modeling of Conducted EMI (Model Motor Simulink Bun)Document8 pagesModeling of Conducted EMI (Model Motor Simulink Bun)Ioan ŢileaNo ratings yet

- Analysis and Assessment of STATCOM-based Damping Stabilizers For Power System Stability EnhancementDocument9 pagesAnalysis and Assessment of STATCOM-based Damping Stabilizers For Power System Stability EnhancementabubakarNo ratings yet

- Evaluation of The Transient Overvoltage Stresses On 132 KV Power Transmission NetworkDocument8 pagesEvaluation of The Transient Overvoltage Stresses On 132 KV Power Transmission NetworkIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNo ratings yet

- Distance Relay ModellingDocument10 pagesDistance Relay ModellingpavanrajhrNo ratings yet

- Analysis and Assessment of STATCOM-based Damping Stabilizers For Power System Stability EnhancementDocument9 pagesAnalysis and Assessment of STATCOM-based Damping Stabilizers For Power System Stability EnhancementsirageldeenNo ratings yet

- 221661A - QGX-CLP - Relay Coordination-Rev1Document78 pages221661A - QGX-CLP - Relay Coordination-Rev1HassenL100% (1)

- Pole Slip Protection On 400 KV Transsmision LineDocument4 pagesPole Slip Protection On 400 KV Transsmision Linestipe_curlin5242No ratings yet

- 1-S2.0-S1434841123001255-Maingood 1Document1 page1-S2.0-S1434841123001255-Maingood 1temp759No ratings yet

- Of in EGAT 500 Transinission System: An Analysis Switching Overvoltages KVDocument5 pagesOf in EGAT 500 Transinission System: An Analysis Switching Overvoltages KVKarina LozadaNo ratings yet

- 4-Jabr - A To Surra - M F2Document1 page4-Jabr - A To Surra - M F2Nirmal RajaNo ratings yet

- Neengalum GnaniaagalamDocument64 pagesNeengalum GnaniaagalamMohamed HNo ratings yet

- 1-Qurt - M To Qurt - N F1Document1 page1-Qurt - M To Qurt - N F1Nirmal RajaNo ratings yet

- 4-Jabr - A To Surra - M F2Document1 page4-Jabr - A To Surra - M F2Nirmal RajaNo ratings yet

- Anma Gnana RagasiyamDocument112 pagesAnma Gnana RagasiyamRajthilak_omNo ratings yet

- CESP Generators PD Monitoring Status OutlookDocument9 pagesCESP Generators PD Monitoring Status OutlookNirmal RajaNo ratings yet

- Maintenance and repair of oil filled cablesDocument2 pagesMaintenance and repair of oil filled cablesNirmal RajaNo ratings yet

- 4-Jabr - A To Surra - M F2Document1 page4-Jabr - A To Surra - M F2Nirmal RajaNo ratings yet

- Monthly Report of Faulty Pilot Cable Feeders JULY - 31-07-14Document49 pagesMonthly Report of Faulty Pilot Cable Feeders JULY - 31-07-14Nirmal RajaNo ratings yet

- MPD 600 White Paper PD Testing Makes Good Sense ENUDocument8 pagesMPD 600 White Paper PD Testing Makes Good Sense ENUcuntNo ratings yet

- A SP17 FlowONE PDFDocument6 pagesA SP17 FlowONE PDFAlaa M EladlNo ratings yet

- 01 Project Framewrok QDocument10 pages01 Project Framewrok QNirmal RajaNo ratings yet

- Sheath Fault Location TestDocument2 pagesSheath Fault Location TestNirmal RajaNo ratings yet

- Metallic-Shield TESTINGDocument45 pagesMetallic-Shield TESTINGNirmal RajaNo ratings yet

- Comparison of Results From Partial Discharge and Emi Tests oDocument7 pagesComparison of Results From Partial Discharge and Emi Tests oNirmal RajaNo ratings yet

- Neengalum GnaniaagalamDocument64 pagesNeengalum GnaniaagalamMohamed HNo ratings yet

- Square D Wiring Diagram BookDocument109 pagesSquare D Wiring Diagram BookVieruth Pascua Paet100% (10)

- Anma Gnana RagasiyamDocument112 pagesAnma Gnana RagasiyamRajthilak_omNo ratings yet

- Registration ServicesDocument159 pagesRegistration ServicesNirmal RajaNo ratings yet

- Curriculum Vitae: Christober Dhas.DDocument3 pagesCurriculum Vitae: Christober Dhas.DNirmal RajaNo ratings yet

- Square D Wiring Diagram BookDocument109 pagesSquare D Wiring Diagram BookVieruth Pascua Paet100% (10)

- Q A Reason: Project Framewrok PMBOK 6 Edition (Answers)Document5 pagesQ A Reason: Project Framewrok PMBOK 6 Edition (Answers)Nirmal RajaNo ratings yet

- Square D Wiring Diagram BookDocument109 pagesSquare D Wiring Diagram BookVieruth Pascua Paet100% (10)

- What Should Be The Value of Earthing Resistance For Minor SubstationsDocument22 pagesWhat Should Be The Value of Earthing Resistance For Minor SubstationsNirmal Raja100% (1)

- Cum Activezi Autocad 2014Document1 pageCum Activezi Autocad 2014Alexys100% (1)

- Energize feeder after cable repair FAX to directorDocument1 pageEnergize feeder after cable repair FAX to directorNirmal RajaNo ratings yet

- Aanandha SangamamDocument48 pagesAanandha SangamamNirmal RajaNo ratings yet

- Anatomic Therapy New English PDF Book (2014) PDFDocument262 pagesAnatomic Therapy New English PDF Book (2014) PDFGunalan Pasubathy100% (1)

- David Servan-Schreiber - Anticancer LeafletDocument16 pagesDavid Servan-Schreiber - Anticancer Leafletandrelins@excite100% (3)

- Job Risk Assessment: No. Job Steps Hazards Control ActionsDocument1 pageJob Risk Assessment: No. Job Steps Hazards Control ActionsNirmal RajaNo ratings yet

- Energy Analysis of Closed Systems BreakdownDocument31 pagesEnergy Analysis of Closed Systems Breakdownايات امجد امجدNo ratings yet

- STC Ratings PDFDocument3 pagesSTC Ratings PDFDiseño SonidoNo ratings yet

- Name: Amir Bin Rossaifuddin Id: 2016307153 Group: Emd2M2ADocument2 pagesName: Amir Bin Rossaifuddin Id: 2016307153 Group: Emd2M2AamirossaifuddinNo ratings yet

- Psychoacoustics: Art Medium SoundDocument3 pagesPsychoacoustics: Art Medium SoundTheodora CristinaNo ratings yet

- JKF8 Intelligent Reactive Power Compensation ControllerDocument4 pagesJKF8 Intelligent Reactive Power Compensation ControllerGuillermo Morales HerreraNo ratings yet

- Study Plan NCEPU PDFDocument2 pagesStudy Plan NCEPU PDFAhsan100% (1)

- ABB Price Book 714Document1 pageABB Price Book 714EliasNo ratings yet

- Prometheus BoundDocument10 pagesPrometheus BoundPhillip HosfeldtNo ratings yet

- Balfour Relocation Feasibility StudyDocument176 pagesBalfour Relocation Feasibility Studygreg32777No ratings yet

- Convection: Example 3.1Document5 pagesConvection: Example 3.1MChobind RivaldoNo ratings yet

- Basicline BL 21t9stDocument28 pagesBasicline BL 21t9stgabriel6276No ratings yet

- ArduinoDocument15 pagesArduinoAlvarez TomasNo ratings yet

- ECC Report: Mobile Coverage ObligationsDocument77 pagesECC Report: Mobile Coverage ObligationsRedamichael JemberuNo ratings yet

- October 14, 2011 Strathmore TimesDocument28 pagesOctober 14, 2011 Strathmore TimesStrathmore TimesNo ratings yet

- Spcr-TagbayaganDocument76 pagesSpcr-TagbayaganReycia Vic QuintanaNo ratings yet

- Toaz - Info Chemtech Reviewer PRDocument1 pageToaz - Info Chemtech Reviewer PRchristy janioNo ratings yet

- Using Graphs To Display Data R 2-12 PDFDocument2 pagesUsing Graphs To Display Data R 2-12 PDFShafika AidaNo ratings yet

- Cambridge International AS & A Level: Mathematics 9709/13Document20 pagesCambridge International AS & A Level: Mathematics 9709/13Justin OngNo ratings yet

- Chapter 14 The Communist Manifesto As International Relations TheoryDocument12 pagesChapter 14 The Communist Manifesto As International Relations TheoryLaurindo Paulo Ribeiro TchinhamaNo ratings yet

- Project Information for 2x660 MW Lube Oil PumpsDocument93 pagesProject Information for 2x660 MW Lube Oil PumpsghostamirNo ratings yet

- Elimination - Nursing Test QuestionsDocument68 pagesElimination - Nursing Test QuestionsRNStudent1100% (1)

- HTTP Verbs GET POST PUT PATCH DELETE (39Document12 pagesHTTP Verbs GET POST PUT PATCH DELETE (39Jefferson EducacionNo ratings yet

- WIP CaseStudyDocument3 pagesWIP CaseStudypaul porrasNo ratings yet

- Genius+ Ba Cu en 1113Document72 pagesGenius+ Ba Cu en 1113AlbertNo ratings yet

- The Anglican Digest - Winter 2022Document64 pagesThe Anglican Digest - Winter 2022The Anglican Digest100% (1)

- Xoro Hrs 8540 HD Sat ReceiverDocument33 pagesXoro Hrs 8540 HD Sat ReceiverPinoNo ratings yet

- Verbal ReasoningDocument8 pagesVerbal ReasoningyasirNo ratings yet

- Starter Unit Basic Vocabulary: Smart Planet 3Document21 pagesStarter Unit Basic Vocabulary: Smart Planet 3Rober SanzNo ratings yet

- Modeling of Soil-Structure Interaction as Finite Element Using SAP2000Document5 pagesModeling of Soil-Structure Interaction as Finite Element Using SAP2000Tariq MahmoodNo ratings yet

- Etabloc Technical DataDocument108 pagesEtabloc Technical Dataedward ksbNo ratings yet