Professional Documents

Culture Documents

A New Space-Vector PWM With Optimal Switching Selection For Multilevel Coupled Inductor Inverters

Uploaded by

Ajith Kumar GadasuOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A New Space-Vector PWM With Optimal Switching Selection For Multilevel Coupled Inductor Inverters

Uploaded by

Ajith Kumar GadasuCopyright:

Available Formats

2354

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 7, JULY 2010

A New Space-Vector PWM With Optimal Switching Selection for Multilevel Coupled Inductor Inverters

Behzad Vafakhah, Student Member, IEEE, John Salmon, Member, IEEE, and Andrew M. Knight, Senior Member, IEEE

AbstractMultilevel space vector pulsewidth modulation (SVPWM) control is shown to be a very useful tool for coupled inductor inverters as six independent pulsewidth modulation (PWM) signals are required, and there is additional complexity of meeting the performance requirements for the coupled inductor while balancing the winding common-mode dc current and generating high-quality multilevel PWM output voltages. A new multilevel SVPWM technique with a ve-segment switching sequence is described, where half-wave symmetrical PWM voltage waveforms are used to balance the inductor common-mode dc voltages and also to avoid all possible switching states with a high winding current ripple. The proposed SVPWM is shown to have better inverter performance, compared with traditional carrier-based and the original multilevel SVPWM schemes at low modulation depths. Inverter operation with the proposed SVPWM is validated through simulation and experimental results. Index TermsCoupled inductor inverter (CII), multilevel inverter, space vector pulsewidth modulation (SVPWM).

I. I NTRODUCTION ARIOUS converter topologies and modulation strategies have been investigated and implemented for drive applications. Commonly, a six-switch two-level inverter is used for low-to-medium-power applications, with the 12-switch multilevel NPC topology being more suitable at higher power levels. Inverter topologies have various advantages and disadvantages, including cost, complexity, and output quality [1][5]. If the application and power level justify the choice of multilevel topologies [1], [6], one recent alternative multilevel topology includes the use of coupled inductors in the output stage of a six-switch inverter [7], [8]. The use of an optimal modulation strategy is essential to assure high-performance operation of the multilevel coupled inductor inverter (CII) topology. Initial modulation methods used for the CII were based on interleaved sinusoidal pulsewidth modulation (SPWM) [9], [10] and space vector pulsewidth modulation (SVPWM) techniques adopted from two-level discontinuous pulsewidth modulation (PWM) schemes for standard inverters [10]. A modied interleaved DPWM1 scheme was applied to this topology in [7] and [8]. Compared with

Manuscript received March 17, 2009; revised July 19, 2006 and October 5, 2009; accepted November 9, 2009. Date of publication January 8, 2010; date of current version June 11, 2010. This work was supported in part by the Canadian Natural Science and Engineering Research Council. The authors are with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB T6G 2V4, Canada (e-mail: vafakhah@ece.ualberta.ca; salmon@ece.ualberta.ca; knight@ece.ualberta.ca). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TIE.2009.2038939

SPWM, DPWM1 can extend the linear modulation range for line-to-line voltages and generates a multilevel voltage with lower harmonic content. Successful operation of the CII topology over the full modulation range relies on selecting switching states where the coupled inductor presents a low winding current ripple and a high effective inductance between the upper and lower switches in each inverter leg (high inductance state). In standard SPWM schemes, using either space vector or carrier based, the switching states in each switching cycle are not arbitrarily selected but chosen by the reference waveform. Uncontrolled switching states can produce low effective inductance connections and produce a large high-frequency current ripple in the inductor windings, resulting in high winding Joule losses, core losses, and high-frequency leakage ux outside the magnetic core. In this case, even though the output voltage and current waveforms have low harmonic content, the inverter winding current contains high harmonic distortion. Thus, even with high-quality output signals, the overall performance of the CII may be poor, which is a fact that is particularly noticeable at low modulation depths, as will be shown in this paper. If switching states are uncontrolled, the coupled inductor must be oversized to provide sufcient effective inductance in all switching cases. As an alternative, a multilevel SVPWM scheme based on those described in [10][14] for multilevel inverters has been applied to the CII in [15]. With the elimination of some lowinductance states, the multilevel SVPWM is shown to produce lower harmonic winding currents. However, this improvement in winding current harmonic content was obtained at the expense of output current quality when compared with interleaved DPWM1. In this paper, it is shown that winding current harmonic distortion in a CII is not only dependent to the selection of switching states with a high effective inductance but also the switching sequence and the order of space voltage vectors in a switching period [10]. A new ve-segment multilevel space vector modulation approach is proposed to eliminate low-inductance switching states, minimizing the winding total harmonic distortion (THD) and providing quality outputs for a wide ma operating range. The switching sequence is designed in order to 1) minimize low effective inductance states; 2) select switching sequence with minimum effects on the inductor winding current deviation; 3) balance common-mode dc current; and 4) generate symmetrical voltage with no even harmonics. The performance of the CII topology with the proposed SVPWM is investigated with simulation and experimental validation. Comparison with

0278-0046/$26.00 2010 IEEE

VAFAKHAH et al.: NEW SVPWM WITH OPTIMAL SWITCHING SELECTION FOR MULTILEVEL CIIs

2355

and Vdc across the winding, respectively. Since the inductor winding is being shorted with the switching states O, no significant change in the common-mode winding current is directly produced. However, icm can change in these last two states due to a small droop caused by semiconductor voltage drops, but more signicantly, magnetic coupling with the windings in the other two inverter legs can cause large changes in icm . III. S PACE V ECTOR M ODULATION SVPWM can be used to choose appropriate switching states and dwell timing, so that net changes in icm in each phase are avoided using a switching scheme with a zero-average winding voltage in each phase over a switching cycle Ts while multilevel output voltages are generated. A space vector diagram for the three-phase CII is shown in Fig. 3 [15]. There are 64 switching states with 19 effective voltage space vectors, including a zero-voltage space vector. The three-level voltage space vectors are categorized to zero, small (Vdc /3), medium (Vdc / 3), and large vectors (2Vdc /3). This block diagram is similar to a conventional three-level inverter [10], [11]. However, to obtain the same voltage vector in each multilevel topology, the switching state is distinct. For instance, in this topology, the overlapping switching states are a unique feature, eliminating dead-time considerations. Based on the switching states available for each voltage vector in Fig. 3, combinations of possible inductor congurations for each size of voltage vector are given in Table II [15], which are grouped by the magnitude of the effective coil inductance. Analyzing Table II, the large and medium voltage vectors are only generated from specic winding congurations. Therefore, there is no freedom in choosing a switching state for voltage vectors 718, indicating that the winding conguration stays the same for large and medium voltage vectors. However, for small voltage vectors (vectors 16), using the conguration in Fig. 2(h) is in preference to Fig. 2(i) or 2(j), which are, in turn, preferable to those in Fig. 2(f) or 2(g). Considering the zero voltage vector (vector 0), using the conguration in Fig. 2(e) is in preference to Fig. 2(c) or 2(d), which are, in turn, preferable to those in Fig. 2(a) or 2(b): the largest effective inductance minimizes the winding current and common-mode dc current ripples. IV. P ROPOSED A PPROACH SVPWM with a ve-segment switching sequence is proposed in this paper. The switching sequences are selected to minimize the number of switching occurrences per switching cycle and the transitions required for Vref when moving from one sector to another. To choose the switching sequence, the general criteria are summarized as follows: 1) minimizing the effect of the switching state on the inductor winding common-mode current deviation. 2) selecting a high-inductance switching state wherever possible. 3) maintaining half-wave symmetry to cancel even line-toline voltage harmonics [11], [14].

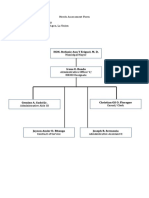

Fig. 1.

Three-phase multilevel coupled inductor inverter.

previous PWM schemes is included to provide broad insight to the range of PWM schemes available for the CII topology. II. CII T OPOLOGY The multilevel CII topology is shown in Fig. 1. The coupled inductors are placed between the upper and lower switches in each inverter leg and wound on a three-limb core to eliminate both fundamental frequency and common-mode dc ux in the core. This arrangement has a size benet as the fundamental frequency and common-mode dc uxes are largely canceled, and the total ux density becomes low [17]. In comparison with two-level inverters, a third voltage level of 1/2Vdc can be achieved when the upper and lower switches in an inverter leg are simultaneously turned on or off. As a result, three-level output voltages are possible, when using an appropriate PWM switching control of the upper and lower switches in an inverter leg. As depicted in Fig. 1, a common-mode current icm ows from the upper to the lower coupled inductor in an inverter leg. The common-mode current is the average of the upper and lower winding currents. To produce multilevel signals, optimal operation of the CII circuit relies on appropriate balancing of the common-mode current. Each of the basic connection options for the three-phase inductor in the CII are summarized in Fig. 2. It should be noted that the center tap output connection of each inductor is omitted from the diagram for clarity. Each connection shown in Fig. 2 can be mapped to a voltage vector in the SVPWM, as shown in Fig. 3. The effective inductance of a winding in each inverter leg and, hence, the ramping rate of the common-mode current icm depend on which of these switching states is being selected [7], [8], [15]. For example, the switching states (a) and (b) in Fig. 2 produce the lowest effective winding inductance and corresponds to all the inverter switches being either on or off. No ux is generated in the three-limb core, with the much smaller leakage inductance being the effective winding inductance. Switching states (a) and (b) frequently occur when using interleaved SPWM or conventional interleaved SVPWM but can be avoided using DPWM1 [7], [8]. However, the next low-inductance switching states, i.e., switching states (f) and (g) in Fig. 2, take place in DPWM1. The impact of the various switching states on the commonmode winding currents is shown in Table I for phase A. The switching state P increases the common-mode winding current icm , and N decreases this current by applying +Vdc

2356

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 7, JULY 2010

Fig. 2. Three-phase coupled inductor congurations for various switching states.

Fig. 3. CII space vector diagram including switching states. TABLE I C OMMON -M ODE DC C URRENT VARIATION FOR P HASE A (BASED ON P HASE B AND C W INDINGS THAT A RE O PEN C IRCUIT )

Fig. 4.

Proposed new switching sequence.

TABLE II R ANKED S WITCHING S TATES FOR E ACH VOLTAGE L EVEL BASED ON THE E FFECTIVE W INDING I NDUCTANCE (L ARGEST TO S MALLEST F ROM L EFT TO R IGHT )

A. Switching Sequence With Minimal Common-Mode DC Current Deviation To minimize the common-mode current deviation, the dwell time of a given p-type and n-type switching state in Table I can equally be distributed over a sampling period. In this paper, a new switching sequence is designed, as shown in Fig. 4. Common-mode current variations are balanced over two successive switching cycles, i.e., cycle A and B. In Fig. 4, a switching sequence is formed using three voltage vectors Vx , Vy , and Vz . dx, dy, and dz are allocated dwell time for voltage vectors of a given triangle (Fig. 3) with vertices Vx , Vy , and Vz , respectively. For both switching cycles A and B, the space vector voltages are applied in the same order x-y-z-y-x with the same dwell time. This approach ensures that the common-mode winding voltage is balanced over each pair of switching cycle in a given triangle.

The original SVPWM scheme for CII [15] eliminated the use of low-inductance congurations of Fig. 2(a), (b), (f), (g), (i), and (j) in small- and zero-voltage states. The newly proposed scheme in this paper also eliminates the need to use the congurations of Fig. 2(b) and (c) in zero-voltage states.

VAFAKHAH et al.: NEW SVPWM WITH OPTIMAL SWITCHING SELECTION FOR MULTILEVEL CIIs

2357

Fig. 5.

Coupled inductor winding voltage and phase voltage in each leg based on switching states in sector I-1 . (Common-mode voltages are Vdc .)

Fig. 6.

Coupled inductor winding voltage and phase voltage in each leg based on switching states in sector I-2 . (Common-mode voltages are either Vdc .)

B. Implementation Figs. 58 show the proposed ve-segment switching sequence with corresponding winding and phase voltages for each specic switching state in cycles A and B in sector I for 1 , 2 , 3 , and 4 . By observing the two cycles of ve-segment switching sequences in Figs. 58, the average winding voltage is balanced over cycles A and B. For example, in Fig. 5, consider the case when Vz1 is {11 00 01} in cycle A and Vz2 is {00 11 01} in cycle B: the two switching states generate the same voltage vector in each inverter leg with opposite effects on icm .

The switching sequences in Figs. 58 indicate that the proposed method is a continuous SVPWM when ma is lower than 0.5 and becomes discontinuous SVPWM when ma is higher than 0.5. (Note that the maximum ma is 1.0.) Continuous SVPWM is observed in triangle 1 and 3 while discontinuous SVPWM for phases A and C is observed in 2 and 4 , respectively. This transition from continuous SVPWM at low modulation indexes to discontinuous SVPWM at high modulation indices provides the optimal use of advantages of each modulation. Discontinuous SVPWM reduces the switching losses and improves the performance at high modulation

2358

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 7, JULY 2010

Fig. 7. Coupled inductor winding voltage and phase voltage in each leg based on switching states in sector I-3 . (Common-mode voltages are either Vdc .)

Fig. 8. Coupled inductor winding voltage and phase voltage in each leg based on switching states in sector I-4 . (Common-mode voltages are either Vdc .)

indices, whereas continuous SVPWM generates high-quality outputs at low modulation indices. The effect of alternating p-type and n-type switching sequences from cycles A and B can also be seen in the waveforms and switching tables, as shown in Figs. 58. It can also be seen that the output terminal voltages in every two successive switching cycles are identical. As mentioned earlier, not only do the high inductance states have signicant impacts on common-mode current ripple but also the sequence of switching states in each switching cycle is important. In the proposed switching, the order of the p-type and n-type vectors in each cycle has been chosen to minimize

the current ripple in each phase. As an example, if the switching state shown in Fig. 7 is rearranged, the new switching state is obtained, as shown in Fig. 9. When compared, the winding voltages for phases A and C are swapped; in Fig. 7, for the same switching frequency, the phase B winding voltage limits the current ramping rate in each cycle, whereas, in Fig. 9, the current ripple is the maximum and can be obtained by ipeakpeakmax = 1 Vdc L 2fc (1)

where fc is the switching frequency.

VAFAKHAH et al.: NEW SVPWM WITH OPTIMAL SWITCHING SELECTION FOR MULTILEVEL CIIs

2359

Fig. 9.

Alternate winding and phase voltage in sector I-3 , with poorly chosen switching sequence. (Common-mode voltages are either Vdc .)

Fig. 10. Proposed SVPWM: Upper and lower winding currents and output current in phase A (ma = 0.9).

Fig. 11. Original SVPWM: Upper and lower winding currents and output current in phase A (ma = 0.9).

V. S IMULATIONS R ESULTS Operation of the CII topology with SPWM, DPWM1, and SVPWM was simulated in Simulink for a range of modulation indices ma , using an inverter with 300-V dc-link voltage and 15-kHz switching frequency driving a 15- 1-mH three-phase load. The coupled inductor upper and lower winding inductances are 1.5 mH each, and the coupling factor is 0.45 between phases and 0.99 in each phase winding. Upper and lower winding currents and output current in phase A for SVPWM, SPWM, and DPWM1 are shown in Figs. 1017. Figs. 10 and 14 show these currents for the proposed SVPWM, and Figs. 11 and 15 show the currents for the original SVPWM [15] when ma are 0.9 and 0.4, respectively. The simulation results validate that the new proposed algorithm works over a wide range of modulation depths. Figs. 12 and 16 show these currents for SPWM; Figs. 13 and 17 show those for DPWM1. At ma = 0.9, the peak-to-peak current ripples in SPWM1 and DPWM1 are slightly lower, compared with those in SVPWM. However, it can be observed that, for ma = 0.4, the proposed SVPWM has a signicantly lower peak-to-peak current ripple. This has been achieved with further elimination

Fig. 12. SPWM: Upper and lower winding currents and output current in phase A (ma = 0.9).

Fig. 13. DPWM1: Upper and lower winding currents and output current in phase A (ma = 0.9).

2360

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 7, JULY 2010

Fig. 14. Proposed SVPWM: Upper and lower winding currents and output current in phase A (ma = 0.4).

Fig. 18. Proposed SVPWM: Harmonic spectrum of the (a) phase-A current, (b) upper winding current, and (c) lower winding current (ma = 0.9).

Fig. 15. Original SVPWM: Upper and lower winding currents and output current in phase A (ma = 0.4). Fig. 19. Proposed (ma = 0.9). SVPWM: lineline-voltage harmonic spectrum

Fig. 16. SPWM: Upper and lower winding currents and output current in phase A (ma = 0.4).

Fig. 20. Original SVPWM: Harmonic spectrum of the (a) phase-A current, (b) upper winding current, and (c) lower winding current (ma = 0.9).

Fig. 17. DPWM1: Upper and lower winding currents and output current in phase A (ma = 0.4).

of switching states (c) and (d) for a zero-voltage vector at low modulation depths in the proposed SVPWM. Additional simulations compare the harmonic spectra of the phase-A current, upper and lower winding currents, and Vab line-to-line voltage for all PWM schemes (ma = 0.9), as shown in Figs. 1825. It can be seen that, for a nominal switching frequency of 15 kHz, the effective switching frequency is seen in the output of interleaved SPWM. In addition, DPWM1 is doubled (to 30 kHz) in Figs. 2225. In contrast, the spectra of the original SVPWM scheme shown in Figs. 18 and 19 indicate

Fig. 21. Original (ma = 0.9).

SVPWM:

lineline-voltage

harmonic

spectrum

that the switching frequency seen in the output signal is half of the nominal frequency (7.5 kHz). In the spectra for the proposed SVPWM scheme in Figs. 20 and 21, the switching harmonics seen in the output are at the nominal switching frequency (15 kHz). Considering the winding current spectra, it can be seen that the effective average switching frequency for the SVPWM schemes is only 7.5 kHz:

VAFAKHAH et al.: NEW SVPWM WITH OPTIMAL SWITCHING SELECTION FOR MULTILEVEL CIIs

2361

Fig. 26. SVPWM, DPWM1, and SPWM lineline-voltage THD.

Fig. 22. SPWM: Harmonic spectrum of the (a) phase-A current, (b) upper winding current, and (c) lower winding current in the proposed SVPWM (ma = 0.9).

Fig. 27. SVPWM, DPWM1, and SPWM phase-A current THD.

Fig. 23. SPWM: lineline-voltage harmonic spectrum (ma = 0.9).

Fig. 28. SVPWM, DPWM1, and SPWM phase-A lower winding current THD.

Fig. 24. DPWM1: Harmonic spectrum of the (a) phase-A current, (b) upper winding current, and (c) lower winding current in the proposed SVPWM (ma = 0.9).

Fig. 25. DPWM1: lineline-voltage harmonic spectrum (ma = 0.9).

the choice of switching state to minimize switching losses is such that the SVPWM schemes are, on average, switching at half the nominal frequency. It can be seen that, unlike the original SVPWM scheme [15], the new proposed SVPWM scheme is capable of providing an output signal with the lowest switching harmonics at twice the average actual switching frequency. This performance is similar to the SPWM and DPWM1

schemes, although, in these schemes, the effective switching frequency is equal to the nominal value. Increasing the nominal switching frequency of the SVPWM scheme, it may be possible to produce a signal with winding harmonics at 15 kHz and output harmonics at 30 kHz, if that is desired. To compare the performance of SVPWM with SPWM and DPWM1, the harmonic spectra of the output lineline voltage and output current are illustrated as a function of ma in Figs. 26 and 27, respectively. By considering lineline-voltage THD, it can be seen that the SVPWM THD is superior over the full range of ma . However, the phase current THD in DPWM1 is superior over the full range of ma . The SVPWM current THD is low at higher values of ma . However, at low ma , SVPWM THD is higher than that in DPWM1 and SPWM THD. Similar to [15], the THD results show that the selection of different switching states does not change the output current and voltage prole in SVPWM, and the current and voltage spectra for the original and proposed SVPWMs are coincident in Figs. 26 and 27. However, it is shown in Figs. 28 and 29 that the newly proposed SVPWM with the elimination of all possible low-inductance switching states has an overall lower winding THD. The switching states with the effective high inductance can reduce the THD in the winding current but do not signicantly affect the output current or voltage THD. A comparison of the upper and lower winding current THDs in Figs. 28 and 29 veries that the overall performance of the proposed SVPWM is better than that of the original SVPWM. The

2362

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 7, JULY 2010

Fig. 29. SVPWM, DPWM1, and SPWM phase-A upper winding current THD.

Fig. 31. Experimental SVPWM line-to-line voltage (Vab ) with (a) ma = 1.0, (b) ma = 0.8, (c) ma = 0.5, and (d) ma = 0.2.

Fig. 30. Experimental setup of the CII inverter, combined three limb core, interface boards, and a TI DSP controller.

major harmonic reduction occurs in lower ma (ma < 0.5) due to additional elimination of the low-inductance switching states of (c) and (d) in Fig. 2 for a zero-voltage space vector. Since these switching states occur in modulation depths lower than 0.5, THD is also reduced in this modulation range. Winding THDs in the proposed SVPWM, as shown in Figs. 28 and 29, are signicantly lower, compared with those in DPWM1 and SPWM. VI. E XPERIMENTAL R ESULTS In order to validate the simulation results, the SVPWM, SPWM, and DPWM1 algorithms are implemented using a TI TMS320F2812 digital signal processor (DSP). The experimental tests are carried out using a small power converter system, as shown in Fig. 30, with the following parameters: Vdc = 300 V, fc = 15 kHz switching frequency, Ls = 1 mH lter inductance, and Lt = 4.7 mH couple inductor inductance. Figs. 31 and 32 show the lineline voltage Vab and phase-A current waveforms with ma at 1.0, 0.8, 0.5, and 0.2 with 60 Hz, respectively. Multilevel voltage output waveforms can clearly be seen in Fig. 31. Upper and lower winding currents and phase-A currents for the proposed SVPWM, the original SVPWM, DPWM1, and SPWM are plotted in Figs. 3336, respectively, when ma is 0.4. These winding current waveforms are close to the simulation results for ma = 0.4 given in Figs. 1417. Comparing the proposed SVPWM current waveforms with SPWM, DPWM1, and original SVPWM, the peak-to-peak winding current ripple is signicantly reduced at lower modulation depths. In addition, the simulation results clearly showed that the SVPWM schemes compare well with SPWM and DPWM1 at high modulation depths. Thus, when the full operating range is required, the proposed SVPWM provides superior inverter performance.

Fig. 32. Experimental SVPWM phase-A current with (a) ma = 1.0, (b) ma = 0.8, (c) ma = 0.5, and (d) ma = 0.2.

Fig. 33. Experimental proposed SVPWM upper and lower winding currents and phase-A current (ma = 0.4, fc = 15 kHz).

Fig. 34. Experimental original SVPWM: upper and lower winding currents and phase-A current (ma = 0.4, fc = 15 kHz).

Analysis of the experimental waveforms is carried out to evaluate the THD of the proposed SVPWM, original SVPWM, SPWM, and DPWM1. Analysis is presented in plots in Figs. 3740 for different modulation indices to validate the THD simulation results presented in Figs. 2629. The harmonic

VAFAKHAH et al.: NEW SVPWM WITH OPTIMAL SWITCHING SELECTION FOR MULTILEVEL CIIs

2363

Fig. 35. Experimental SPWM upper and lower winding currents and phase-A current (ma = 0.4, fc = 15 kHz).

Fig. 39. Experimental SVPWM, DPWM1, and SPWM phase-A lower winding current THD.

Fig. 36. Experimental DPWM1 upper and lower winding currents and phase-A current (ma = 0.4, fc = 15 kHz).

Fig. 40. Experimental SVPWM, DPWM1, and SPWM phase-A upper winding current THD.

upper winding current THDs are plotted in Figs. 39 and 40, respectively. The experimental data show good agreement with the simulation results shown in Figs. 28 and 29, and validate the superiority of the proposed SVPWM at low modulation depths. Winding current THD is limited by the voltage waveform and coupled inductor magnetizing inductance; hence, any discrepancy in leakage inductance between simulations and experimental results will not impact these results.

Fig. 37. Experimental voltage THD. SVPWM, DPWM1, and SPWM lineline-

VII. C ONCLUSION SVPWM with a new selection of switching sequences method for three-level coupled inductor inverters has been presented. The proposed method eliminates all low-inductance switching states that contribute to common-mode current harmonic distortion while balancing common-mode winding dc voltages and reducing winding harmonic distortion. As the winding current harmonic content affects both copper losses and core losses in the coupled inductor, the proposed optimal switching sequence can allow reduction to the size of the coupled inductor core due to lower harmonic content and lower winding root-mean-square current. In addition, concentrating on high-inductance states may allow redesign of the inductor to have a lower overall inductance, as the coupled inductor need not be designed to enable operation at the low effective inductance states. A comprehensive performance comparison between SPWM, DPWM1 carrier-based modulations, and SVPWM for coupled inductor inverters has been given. The result shows that the proposed SVPWM with selection of all high-inductance switching states can improve the quality of the winding current prole, particularly at low modulation depths. Providing high-quality outputs, the proposed multilevel SVPWM strategy is shown to have great potential as variable-speed drives. Computer simulations and laboratory results have validated the effectiveness of the approach. Future work may focus on interleaved multilevel

Fig. 38.

Experimental SVPWM, DPWM1, and SPWM phase-A current THD.

spectra of output lineline voltage and output current are shown as a function of ma in Figs. 37 and 38, respectively. The experimental THD results verify that the output current and voltage spectra for the original and proposed SVPWMs are coincident. The experimental lineline-voltage THD closely agrees with the simulated voltage THD shown in Fig. 26. Experimental output line current THD plots in Fig. 38 have similar proles to the simulations in Fig. 27, but the output current THD is higher for all modulation strategies. Given the agreement in output voltage THD, it appears that the total output inductance seen by the system is lower than expected. The likely cause for the discrepancy in the results is the fact that the experimental inductor was built with a lower than expected leakage inductance. The experimental lower and

2364

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 7, JULY 2010

SVPWM in the attempt to further increase the effective output frequency, reducing the magnitude of the output current ripple while providing low winding current THD. R EFERENCES

[1] J. Rodriguez, J.-S. Lai, and F. Z. Peng, Multilevel inverters: A survey of topologies, controls, and applications, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724738, Aug. 2002. [2] T. P. Chen, Circulating zero-sequence current control of parallel threephase inverters, Proc. Inst. Elect. Eng.Elect. Power Appl., vol. 153, no. 2, pp. 282288, Mar. 2006. [3] F. Ueda, K. Matsui, M. Asao, and K. Tsuboi, Parallel-connections of pulse width modulated inverters using current sharing reactors, IEEE Trans. Power Electron., vol. 10, no. 6, pp. 673697, Nov. 1995. [4] K. Matsui, Y. Kawata, and F. Ueda, Application of parallel connected NPCPWM inverters with multilevel modulation for ac motor drive, IEEE Trans. Power Electron., vol. 15, no. 5, pp. 901907, Sep. 2000. [5] N. Celanovic and D. Boroyevich, A comprehensive study of neutral-point voltage balancing problem in three level neutral-point-clamped voltage source PWM inverters, IEEE Trans. Power Electron., vol. 15, no. 2, pp. 242249, Mar. 2000. [6] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, The age of multilevel converters arrives, IEEE Ind. Electron. Mag., vol. 2, no. 2, pp. 2839, Jun. 2008. [7] J. Salmon, J. Ewanchuk, and A. M. Knight, PWM inverters using split-wound coupled inductors, IEEE Trans. Ind. Appl., vol. 45, no. 6, pp. 20012009, Nov./Dec. 2009. [8] J. Ewanchuk, J. Salmon, and A. M. Knight, Performance of a high-speed motor drive system using a novel multilevel inverter topology, IEEE Trans. Ind. Appl., vol. 45, no. 5, pp. 17061714, Sep. 2009. [9] K. Xing, F. C. Lee, and B. Borojevic, Interleaved PWM with discontinuous space-vector modulation, IEEE Trans. Power Electron., vol. 14, no. 5, pp. 907917, Sep. 1999. [10] D. G. Holmes and T. A. Lipo, Pulse Width Modulation for Power Converters. Piscataway, NJ: IEEE Press, 2003. [11] W. Bin, High-Power Converters and AC Drives. Hoboken, NJ: Wiley, 2006. [12] N. Celanovic and D. Boroyevich, A fast space-vector modulation algorithm for multilevel three-phase converters, IEEE Trans. Ind. Appl., vol. 37, no. 2, pp. 637641, Mar./Apr. 2001. [13] B. Kaku, I. Miyashita, and S. Sone, Switching loss minimized space vector PWM method for IGBT three-level inverter, Proc. Inst. Elect. Eng.Elect. Power Appl., vol. 144, no. 3, pp. 182190, May 1997. [14] A. Rahiman, G. Narayanan, and V. T. Ranganathan, Modied SVPWM algorithm for three level VSI with synchronized and symmetrical waveforms, IEEE Trans. Ind. Electron., vol. 54, no. 1, pp. 486494, Feb. 2007. [15] B. Vafakhah, M. Masiala, J. Salmon, and A. M. Knight, Space-vector PWM for inverters with split-wound coupled inductors, in Proc. IEEE Int. Elect. Mach. Drives Conf., May 36, 2009, pp. 724731. [16] C. Chapelsky, J. Salmon, and A. M. Knight, High-quality single-phase power conversion by reconsidering the magnetic components in the output stageBuilding a better half-bridge, IEEE Trans. Ind. Appl., vol. 45, no. 6, pp. 20482055, Nov./Dec. 2009. [17] A. M. Knight, J. Ewanchuk, and J. C. Salmon, Coupled three-phase inductors for interleaved inverter switching, IEEE Trans. Magn., vol. 44, no. 11, pp. 41194122, Nov. 2008.

Behzad Vafakhah (S07) received the B.Sc. degree in electrical engineering from K. N. Toosi University of Technology, Tehran, Iran, in 1998 and the M.Sc. degree in electrical engineering from Sharif University of Technology, Tehran, in 2000. He is currently working toward the Ph.D. degree in the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB, Canada. From 2001 to 2004, he was a Research Assistant with the Power Electronics Laboratory, University of Tehran, Tehran. At the same time, he was a Design Engineer with the Abrizan Pump Company, Iran. His current research interests include multilevel power converters, electric drives, pulsewidth modulation techniques, power electronics in renewable energy applications, and hybrid electric vehicles. Mr. Vafakhah is a member of the Association of Professional Engineers of Alberta.

John Salmon (S86M86) received the B.Sc. degree in engineering from Imperial College, London, U.K., in 1982, the M.Eng. degree from McGill University, Montreal, QC, Canada, in 1984, and the Ph.D. degree from Imperial College in 1987. In 1987, he joined the Department of Electrical Engineering and Computer Engineering, University of Alberta, Edmonton, AB, Canada, as an Assistant Professor, and has been a Full Professor since 1996. He has conducted industrially funded powerelectronics research projects covering a wide range of applications, such as electronic ballasts for uorescent lamps and metalhalide HID lamps, utility interface of microturbine generators using high-speed permanent-magnet generators, medium-voltage industrial drive systems, and soft starters for medium-voltage induction motors. His current research interests include industrial drive systems and their utility interface multipulse utility rectiers, multilevel voltage-source converters, high-speed ac drive systems, and multifunctional pulsewidth-modulated converters.

Andrew M. Knight (S95A98M99SM06) received the B.A. degree in electrical and information sciences and the Ph.D. degree in electrical power from the University of Cambridge, Cambridge, U.K., in 1994 and 1998, respectively. In 1999, he joined the University of Alberta, Edmonton, AB, Canada, as an Assistant Professor, and is currently an Associate Professor with the Department of Electrical and Computer Engineering. His research interests include efcient utilization of electrical energy, including energy conversion and storage, particularly renewable energy and electrical machines and drives. In addition to his interest in the practical aspects of analysis and design of electric machines, he carried out research on the modeling of nonlinear electromagnetic systems and losses in those systems. Dr. Knight was a recipient of the IEEE Power and Energy Society Prize Paper Award 2008 and two prize papers from the IAS 2008 Annual Meeting.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Freelance Contract AgreementDocument10 pagesFreelance Contract AgreementGayathri Prajit100% (1)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Presentation 2Document32 pagesPresentation 2Jackie LeeNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- ESAT FormulaDocument11 pagesESAT FormulaSKYE LightsNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Calculation of Work IndexDocument5 pagesCalculation of Work IndexEnryan Oreski RiyadiNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Color Coding - 2018Document28 pagesColor Coding - 2018Aris MunandarNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Global Competitiveness ReportDocument7 pagesGlobal Competitiveness ReportSHOIRYANo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- A Review of The Accounting CycleDocument46 pagesA Review of The Accounting CycleRNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Outsourced New Product DevelopmentDocument5 pagesOutsourced New Product Developmentvinnakota5No ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Activity 3 Data SheetDocument9 pagesActivity 3 Data SheetEli GabuatNo ratings yet

- Review Accounting NotesDocument9 pagesReview Accounting NotesJasin LujayaNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Industrial Training HandbookDocument26 pagesIndustrial Training HandbookChung tong Betty wongNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Sop ECUDocument5 pagesSop ECUSumaira CheemaNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Types of IndexDocument4 pagesTypes of IndexKantha EnduriNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Needs Assessment Form Company Name: HRMO Address: Sta. Barbara Agoo, La UnionDocument2 pagesNeeds Assessment Form Company Name: HRMO Address: Sta. Barbara Agoo, La UnionAlvin LaroyaNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Reinforcement Project Examples: Monopole - Self Supporter - Guyed TowerDocument76 pagesReinforcement Project Examples: Monopole - Self Supporter - Guyed TowerBoris KovačevićNo ratings yet

- Sajjad Ali: API Mechanical Tank Inspector, QCI Welding (Aramco Approved)Document5 pagesSajjad Ali: API Mechanical Tank Inspector, QCI Welding (Aramco Approved)Owais MalikNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Hospital DocumentsDocument17 pagesHospital DocumentsRaviraj PisheNo ratings yet

- Improving The Passenger Experience: Monitoring Airport Quality of ServiceDocument6 pagesImproving The Passenger Experience: Monitoring Airport Quality of ServiceParisa HadidianNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Helicopter MaintenanceDocument347 pagesHelicopter MaintenanceJai Deep88% (24)

- 1.doosan D1146Document1 page1.doosan D1146Md. ShohelNo ratings yet

- Insular Bank of Asia vs. InciongDocument11 pagesInsular Bank of Asia vs. InciongChristiane Marie BajadaNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Chats: Dini-Ay TriciaDocument1 pageChats: Dini-Ay Triciaaiyana sopiaudaundoNo ratings yet

- Mba Mini Project ReportDocument32 pagesMba Mini Project ReportAvneesh KumarNo ratings yet

- MCQ Criminal Law 1Document18 pagesMCQ Criminal Law 1Clark Vincent Ponla0% (1)

- Assignment 2Document4 pagesAssignment 2LaDonna WhiteNo ratings yet

- The History of The Evening NewsDocument14 pagesThe History of The Evening NewsWaqas MahmoodNo ratings yet

- SIFI-131 Fire Protection in Electrical Equipment RoomsDocument8 pagesSIFI-131 Fire Protection in Electrical Equipment RoomsemiljanlazeNo ratings yet

- 2023-04-28 NMSU Executive SummaryDocument2 pages2023-04-28 NMSU Executive SummaryDamienWillisNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Union Class Dropship 3025Document1 pageUnion Class Dropship 3025A KNo ratings yet

- Decisions Made by The DecisionDocument2 pagesDecisions Made by The Decisionneil arellano mutiaNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)