Professional Documents

Culture Documents

VLSI

Uploaded by

Siva Krishna Reddy NallamilliOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI

Uploaded by

Siva Krishna Reddy NallamilliCopyright:

Available Formats

ABSTRACT

VLSI fabrication augmented its aggrandizement for its insatiable demand for higher operating speeds and device packing densities. The circuits fabricated on bulk Si wafer could not satisfy these requirements. The present paper seeks to ameliorate this area through Silicon-On-Insulator (SOI) technology. It elucidates a novel technology using atomic layer cleavage, which allows SOI processing to be available for many substrate materials. It also presents various other fabrication methods for SOI technology. Using the same transistor dimensions, SOIs global dielectric isolation enables IC manufacturers to pack more die on a wafer without direct transistor scaling through reduction in the wafer area needed for the device isolation. The SOI process exploits Nano cleaving, which reduces cost and creates SOI wafers with exceptional material quality and high yield. Nano cleave is highly efficient for chipmakers, relying on standard IC fabrication technologies. This paper encompasses Nano cleave process fabrication steps in a lucid manner. It also accrues major advantages of devices built on SOI wafers.

ABSTRACT

AABSTRACT A 1. PREAMBLE Silicon-on-insulator (SOI) technology provides opportunities to increase transistor switching and at the same time to improve performance for low-power, batterydriven electronics. With its ability to increase device density through reduction in isolation area, SOI can postpone the need to shift to smaller scale transistors. SOI can contribute to reduced manufacturing costs by simplifying IC fabrication processes, through the elimi-nation of high-energy implantation for well doping and simplification of device isolation. SOI also provides opportunities beyond conventional semiconductor devices. SOI is a key method for fabricating Silicon-on-Anything devices, which have the potential to integrate communications, smart cards, sensors and displays with portable, low-power memory and logic devices, as in Figure 1.

Figure 1. SOI technology enables major performance advances in numerous applications

Using a fully-integrated, proprietary SOI manufacturing process, called NanoCleave, advanced corporations have recently begun production of SOI wafers which

offers lower cost and higher wafer quality than earlier generations of SOI fabrication methods.

2. SOI ADVANTAGES The major advantage of devices built on SOI wafers are: 1) 20 to 30% higher operating speeds compared to similar devices on bulk Si 2). higher device packing density for logic and analog circuits and 3). greatly increased immunity to soft-error events generated by decay products of cosmic ray showers.

Using the same transistor dimensions, SOIs global dielectric isolation enables IC manufacturers to pack more die on a wafer without direct transistor scaling, through reduction in the wafer area needed for device isolation, as shown in Figure 2. This increase in the die per wafer yield is especially valuable in logic and I/O-dominated layouts such as in system-on-a-chip (SOC) devices. In addition to speed gains in mainstream applications, the negligible current leakage and lower power requirements of SOI-based chips can dramatically improve the performance of battery-powered communication and computing devices for mobile electronics.

3. SOI: AN EMERGING MARKET FOR GIGAHERTZ-SPEED, LOW POWER DEVICES The need for lower cost IC devices which operate in the Gigahertz frequency range used for mobile communications is driving the switch to SOI wafers. Broadband communication networks, operating on battery or solar cell power, need the low-power, small die size and global Isolation of SOI designs. The lower cost of Silicon device processing on large area wafers provides a key advantage for SOI over communication and computing devices fabricated with more exotic materials, such as GaAs. Todays standard processes fabricate transistors directly onto a bulk silicon wafer surface. These transistors operate at relatively low switching speed because large volumes of semiconductor material require more energy to turn on and off. For SOIbased processes, transistors are built on a thin silicon surface layer isolated from the wafer by a layer of oxide, and chips run 20% to 35% faster because less charge is needed to switch the transistor state. This speed gain is equivalent to the advantage gained by a full generation of device scaling on bulk-Silicon. 4. MAKING SOI A PRODUCTION TECHNOLOGY Despite its many benefits, SOIs acceptance has been slowed by the high cost and low production-maturity of first-generation SOI manufacturing methods. These various methods were complex and often produced wafers of low or variable quality. Currently, there are five methods to produce commercially available SOI, based on either direct oxygen implantation or bonded layer transfer technologies, as shown in Table. The two commercial ways to fabricate SOI wafers, namely, SIMOX (separation by implantation of oxygen) and BESOI (bonded and etch-back) SOI, are quite expensive because of the long implantation time for the SIMOX process and the need to use two wafers to form a single SOI wafer in BESOI. Recently, a method called SMART-CUT or ion cut was proposed by SOITEC, making use of wafer cleavage after hydrogen implantation and subsequent wafer bonding. This technique is potentially cheaper than the conventional BESOI process because one of the wafers can be recycled.

The materials cost of SOI can be further reduced if an alternative way can be found to reduce the time required to implant a high enough dose of oxygen (SPIMOX) or

hydrogen (ion-cutting). Plasma immersion ion implantation (PIII) is a burgeoning technique offering many applications in materials and semiconductor processing. In PIII, the sample is immersed in a plasma shroud from which ions are extracted and accelerated through a high-voltage sheath into the target. The dose rate can be as high as ions cm s which is equivalent to ten monolayers of implanted atoms per second and at least an order of magnitude higher than that of a conventional ion implanter.

Since the entire wafer is implanted simultaneously, the implantation time is independent of wafer size, thereby offering an extremely attractive approach for 300-mm wafers. The use of PIII to synthesize SOI materials has been investigated, and the results are very encouraging. In spite of the tremendous potential, the development of commercial PIII instrumentation has not caught up. The newest of these technologies, NanoCleave, represents a unique, second generation, approach that offers a streamlined process flow and the potential for significantly lower SOI manufacturing costs. One of the earlier barriers to the use of SOI for mainstream chipmaking was the higher cost of SOI wafers, up to 5 times the cost of bulk silicon wafers. With advanced SOI fabrication technology, such as NanoCleave, the cost of SOI wafers can be substantially reduced. It is expected that the price of 200 mm SOI wafers, which is currently in the range of $500 per wafer, will drop by as much as 40% in the coming year as production volumes and consumption of SOI wafers increase. 5. THE NANOCLEAVE PROCESS SOI process uses NanoCleave and other novel manufacturing methods that reduce cost and create SOI wafers with exceptional material quality and high yield. Unlike most other competing technologies, the critical layer transfer and wafer bonding steps are accomplished at room temperature. NanoCleave is highly efficient for chipmakers, relying on standard IC fabrication technologies for most of the process steps, supplemented with fully automated tools for the critical wafer bonding and separation steps. Surface roughness of the finished SOI wafer exhibits RMS roughness below 1nm, which is already within specification for use by most IC processes. As a measure of its process simplicity, this is accomplished without the CMP and post-CMP damage removal steps required in earlier generation bonded SOI wafer fabrication processes. 6. NANOCLEAVE PROCESS FABRICATION STEPS SOI layer transfer techniques involve creating a dual-layer of device-silicon and an insulator layer) (the Buried OXide or BOX) grown on a donor wafer and bonded to a handle wafer. These silicon and buried oxide layers are then separated (cleaved)

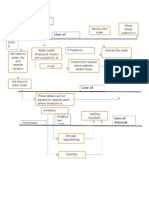

from the donor wafer, producing a finished SOI wafer. The NanoCleave process greatly simplifies this layering sequence compared to earlier processes, resulting in the potential for major cost reductions in SOI production, Figure 3.

FIGURE 3. THE NANO CLEAVE PROCESS FLOW

The NanoCleave process includes four main steps: 1. A donor wafer is formed by forming a high-quality silicon layer (which will become the device layer in the final SOI wafer). A cleave plane situated beneath this layer acts as a guide for the cleave front during the separation process. The

silicon layer does not contain the yield-limiting crystal defects and oxygen precipitates present in bulk silicon grown by CZ methods. A thermal oxide is grown on the silicon layer that becomes part of the buried oxide layer in the finished SOI wafer, Figure 4. The thermal oxide growth process produces a buried oxide layer that is free of pinholes and silicon inclusions. The NanoCleave silicon/oxide interface, Figure 5, has the low interface trap and fixed charge densities that are required to control the signal frequency dependence of transistor threshold voltage.

2. The NanoCleave process uses implantation in combination with other proprietary process steps to promote low-energy cleaving along the desired wafer separation plane. A standard beam line implanter is presently used for 200mm production in the SiGen pilot line. However, looking ahead towards the needs of high-volume 200mm and 300 mm SOI wafer production, the implant step can be more cost-effectively performed by Plasma Immersion Ion Implantation (PIII) using tools, such as the SiGen PIII implanter. 3. Plasma treatment of the wafer surfaces enables the donor wafer to be bonded to a bare or oxidized handle wafer with a bond interface far stronger than the cleave plane. Because the device silicon layer is separated by the buried oxide layer, a handle wafer with considerably relaxed electrical and chemical specifications, and therefore lower cost, can be used in this process.

4. Using Controlled Cleave Process (CCP), the donor and handle are separated at room temperature. Using a controlled propagation along a single cleave front, as in Figure 6, this atomic layer cleaving process results in an as-cleaved surface roughness less than 1nm (typically 2-5 Angstroms). This is an order of magnitude smoother than the 80 Angstroms of typical hydrogen-induced thermal cleaving, Figure 7. Such a smooth surface is acceptable for many IC applications with no additional surface polishing.

Figure 7 AFM images of as-cleaved surfaces of NanoCleave and Hydrogeninduced thermal separation methods

The edge of the SOI layer has a smooth and regular character without the need for edge polishing, Figure 8.

7. USING A STANDARD TOOL SET FOR SOI The fabrication sequence has 20- 40% fewer steps than other bonded wafer SOI fabrication methods and uses widely available IC fabrication tools, such as ion implantation, thermal furnace and wet benches, for most of the process steps. The key wafer bonding and atomic layer cleaving steps are done by fully-automated tools which have been developed to be easily integrated into a high-volume SOI wafer fabrication environment. 8. CONCLUSION The advances in SOI wafer manufacturing technology are lowering the cost of SOI wafers through a simpler, more cost-effective process flow. The NanoCleave process accomplishes this productivity breakthrough by using conventional semiconductor manufacturing tools for most of the process flow and by accomplishing the wafer bonding and cleaving steps at room temperature. The as-cleaved SOI wafer surface is smooth to sub-nanometer dimensions and can be used directly without any post-cleave mechanical polishing or edge treatment.

REFERENCES: 1. Se-Jeong Park, Jeong-Su Kim, Ramchan Woo, Se-Joong Lee,Kang-Min Lee, TaeHum Yang, Jin-Yong Jung and Hoi-Jun Yoo, A Reconfigurable Multilevel ParallelGraphics Memory with 75GB/s Parallel Cache Replacement Bandwidth, Symposium on VLSI Circuits 2001, C21p3, in press, Jun. 2001. 2. Sean P.Cunningham and J. George Shanthikumar, Empirical Results on the Relationship Between Die Yield and Cycle Time in Semiconductor Wafer Fabrication, In IEEE Transactions on Semiconductor Manufacturing, 9: 273-277, 1996. 3. J.Kook, et al, A Low Power Reconfigurable I/O DRAM Macro with Single Bit line Writing Scheme, 26th European Solid-State Circuits Conference, pp.384-387,Sept., 2000. 4. T. Nishikawa, et al., A 60 MHz 240 mW MEPG-4 Video-Phone LSI with 16 Mb Embedded DRAM, ISSCC Digest of Technical Papers, pages 230-231, 2000.

You might also like

- Atherosclerosis - Causes, Symptoms & TreatmentDocument4 pagesAtherosclerosis - Causes, Symptoms & TreatmentSiva Krishna Reddy NallamilliNo ratings yet

- Control Charts For ClassDocument10 pagesControl Charts For ClassSiva Krishna Reddy NallamilliNo ratings yet

- Toyota Global Site - The Origin of The Toyota Production SystemDocument2 pagesToyota Global Site - The Origin of The Toyota Production SystemSiva Krishna Reddy NallamilliNo ratings yet

- Indian Exports DataDocument2 pagesIndian Exports DataSiva Krishna Reddy NallamilliNo ratings yet

- Lean Manufacturing The Maruti Way - Business LineDocument2 pagesLean Manufacturing The Maruti Way - Business LineSiva Krishna Reddy NallamilliNo ratings yet

- Medplus Service BlueprintDocument1 pageMedplus Service BlueprintSiva Krishna Reddy NallamilliNo ratings yet

- Toyota Global Site - The Origin of The Toyota Production SystemDocument2 pagesToyota Global Site - The Origin of The Toyota Production SystemSiva Krishna Reddy NallamilliNo ratings yet

- SPC Examples with SolutionsDocument4 pagesSPC Examples with SolutionsSiva Krishna Reddy Nallamilli100% (1)

- QUALITY Focus Key to Transforming Management EducationDocument8 pagesQUALITY Focus Key to Transforming Management EducationSiva Krishna Reddy NallamilliNo ratings yet

- Pharmaceuticals August 2014Document55 pagesPharmaceuticals August 2014Siva Krishna Reddy NallamilliNo ratings yet

- Pharmaceuticals August 2014Document55 pagesPharmaceuticals August 2014Siva Krishna Reddy NallamilliNo ratings yet

- Topics on Quality, Lean Manufacturing and Productivity ImprovementDocument16 pagesTopics on Quality, Lean Manufacturing and Productivity ImprovementSiva Krishna Reddy NallamilliNo ratings yet

- Performance ManagementDocument1 pagePerformance ManagementSiva Krishna Reddy NallamilliNo ratings yet

- Factors Hindering Indian Export Growth and Potential SolutionsDocument16 pagesFactors Hindering Indian Export Growth and Potential SolutionsSiva Krishna Reddy NallamilliNo ratings yet

- Atchyuta Rao ResumeDocument2 pagesAtchyuta Rao ResumeSiva Krishna Reddy NallamilliNo ratings yet

- Anaparthi Servies Softwares Hardwares Computer ServicesDocument1 pageAnaparthi Servies Softwares Hardwares Computer ServicesSiva Krishna Reddy NallamilliNo ratings yet

- Prime Minister Narendra Modi Favourite To Win 'Time Person of The Year' PollDocument2 pagesPrime Minister Narendra Modi Favourite To Win 'Time Person of The Year' PollSiva Krishna Reddy NallamilliNo ratings yet

- Rani TextilesDocument2 pagesRani TextilesSiva Krishna Reddy NallamilliNo ratings yet

- PM Modi Wants This Bihar Success Story Replicated - NDTVProfitDocument3 pagesPM Modi Wants This Bihar Success Story Replicated - NDTVProfitSiva Krishna Reddy NallamilliNo ratings yet

- Qatar Airways Takes Delivery of Its First Airbus A380 - The Economic TimesDocument2 pagesQatar Airways Takes Delivery of Its First Airbus A380 - The Economic TimesSiva Krishna Reddy NallamilliNo ratings yet

- Bharti Airtel Announces New Organization Structure For India OperationsDocument1 pageBharti Airtel Announces New Organization Structure For India OperationsSiva Krishna Reddy NallamilliNo ratings yet

- Creative Briefs 51Document15 pagesCreative Briefs 51Siva Krishna Reddy NallamilliNo ratings yet

- Biolab TestDocument2 pagesBiolab TestSiva Krishna Reddy NallamilliNo ratings yet

- HP Deskjet - Supply ChainDocument15 pagesHP Deskjet - Supply Chainsaurabhku12100% (4)

- Amazon Hires 80,000 Seasonal Holiday Workers - ET RetailDocument3 pagesAmazon Hires 80,000 Seasonal Holiday Workers - ET RetailSiva Krishna Reddy NallamilliNo ratings yet

- Customer Profitability AnalysisDocument5 pagesCustomer Profitability AnalysisSiva Krishna Reddy NallamilliNo ratings yet

- Sales and Distribution Process of Itc Vivel SoapsDocument7 pagesSales and Distribution Process of Itc Vivel SoapsPrateek Goel100% (1)

- PediasureDocument4 pagesPediasureSiva Krishna Reddy NallamilliNo ratings yet

- Management Case: Blue Dart Express LimitedDocument8 pagesManagement Case: Blue Dart Express LimitedAravind MaitreyaNo ratings yet

- Customer Profitability Analysis With Time-Driven Activity-Based Costing: A Case Study in A HotelDocument30 pagesCustomer Profitability Analysis With Time-Driven Activity-Based Costing: A Case Study in A HotelSiva Krishna Reddy NallamilliNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Datasheet 2sc3052 SMDDocument1 pageDatasheet 2sc3052 SMDed pwtNo ratings yet

- 2 Mark (ED Questions)Document26 pages2 Mark (ED Questions)Pradeep ravichanderNo ratings yet

- Microelectronic Circuits Analysis and Design 3rd Edition Rashid Solutions Manual 1Document92 pagesMicroelectronic Circuits Analysis and Design 3rd Edition Rashid Solutions Manual 1heather100% (48)

- Optoelectronics SyllabusDocument4 pagesOptoelectronics SyllabusabdulbabulNo ratings yet

- Topic 1 Introduction To SemiconductorDocument32 pagesTopic 1 Introduction To SemiconductoridasyarmilaNo ratings yet

- SiC MOS UIS Failure Mechanism of SiC Power MOSFETsDocument5 pagesSiC MOS UIS Failure Mechanism of SiC Power MOSFETsterry chenNo ratings yet

- Honours Project - Switched Capacitor Filter Design For Mixed Signal ApplicationsDocument46 pagesHonours Project - Switched Capacitor Filter Design For Mixed Signal ApplicationsNaveen Gowdru ChannappaNo ratings yet

- 2301 DsDocument5 pages2301 DsDexter DanielNo ratings yet

- Bulk 32nmDocument4 pagesBulk 32nmthesovereignmoonloveNo ratings yet

- N-Channel Enhancement Mode MOSFET Features and ApplicationsDocument12 pagesN-Channel Enhancement Mode MOSFET Features and ApplicationsK57 KTDTTHCNNo ratings yet

- BL Galaxy 2SA1204 Transistor SpecDocument4 pagesBL Galaxy 2SA1204 Transistor Specmhmd193No ratings yet

- Digital Logic Families: TTL vs CMOS ComparisonDocument32 pagesDigital Logic Families: TTL vs CMOS ComparisonSaiKanthG100% (1)

- Semiconductors: Why Si and Ge Adopt Tetrahedral StructureDocument10 pagesSemiconductors: Why Si and Ge Adopt Tetrahedral StructureAfra AlethianaNo ratings yet

- Analysis of The Gate-Source/Drain Capacitance Behavior of A Narrow-Channel FD SOI NMOS Device Considering The 3-D Fringing Capacitances Using 3-D SimulationDocument5 pagesAnalysis of The Gate-Source/Drain Capacitance Behavior of A Narrow-Channel FD SOI NMOS Device Considering The 3-D Fringing Capacitances Using 3-D SimulationSunil KumarNo ratings yet

- MOSFET - The Most Widely Manufactured DeviceDocument16 pagesMOSFET - The Most Widely Manufactured DeviceThu ReinNo ratings yet

- Chapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesDocument1 pageChapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesCarlos SaavedraNo ratings yet

- PN Junction Diode Characteristics ExperimentDocument6 pagesPN Junction Diode Characteristics ExperimentAbdullah ShahNo ratings yet

- 1) Ferrites Are A) Ferromagnetic B) Ferrimagnetic C) Antiferromagnetic D) Paramagnetic Ans: B) FerrimagneticDocument7 pages1) Ferrites Are A) Ferromagnetic B) Ferrimagnetic C) Antiferromagnetic D) Paramagnetic Ans: B) FerrimagneticPrasad Govind KumbharNo ratings yet

- What Are The Pros and Cons of BJT Versus FET Transistor - QuoraDocument2 pagesWhat Are The Pros and Cons of BJT Versus FET Transistor - Quorasunilkmch505682No ratings yet

- DiodesDocument25 pagesDiodesADEFRIS BELACHEWNo ratings yet

- Basic Electronics With Measurements: The Diode Diode Operation Voltage To Current Characteristics Diode ModelsDocument34 pagesBasic Electronics With Measurements: The Diode Diode Operation Voltage To Current Characteristics Diode Modelsarondaniel ocampoNo ratings yet

- 3 Zener DiodeDocument16 pages3 Zener DiodeGurudevNo ratings yet

- (13b) Diode Sambungan P-NDocument27 pages(13b) Diode Sambungan P-NUlfie Kusuma WardhaniNo ratings yet

- Verilog-A Implementation of SOI MOSFET-Based Amplifier and RingDocument9 pagesVerilog-A Implementation of SOI MOSFET-Based Amplifier and RingAdib ShadmanNo ratings yet

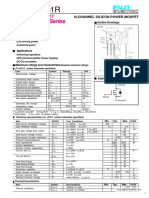

- Super FAP-G Series: Fuji Power MosfetDocument4 pagesSuper FAP-G Series: Fuji Power MosfetsaikumarNo ratings yet

- CMOS VLSI Design 92Document1 pageCMOS VLSI Design 92Carlos SaavedraNo ratings yet

- 1-VLCI ItrodutionDocument15 pages1-VLCI Itrodutionbhieestudents100% (1)

- Review of Different Types of Solar Cells and Future TrendsDocument17 pagesReview of Different Types of Solar Cells and Future TrendsLokesh LokuNo ratings yet

- Normal PCB Footprint Conventions: ThanhtuphamDocument28 pagesNormal PCB Footprint Conventions: ThanhtuphamĐiện Tử Song PhúNo ratings yet

- 1N5820, 1N5821, 1N5822 Silicon Rectifier Diodes Schottky Barrier, Fast SwitchingDocument1 page1N5820, 1N5821, 1N5822 Silicon Rectifier Diodes Schottky Barrier, Fast SwitchingEliecer MenesesNo ratings yet