Professional Documents

Culture Documents

Simultaneous Switching Noise

Uploaded by

xeratuleOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Simultaneous Switching Noise

Uploaded by

xeratuleCopyright:

Available Formats

ELE863/EE8501 VLSI Systems

Simultaneous Switching Noise (SSN)

B0

B1

B63

V

DD

V

SS

V

DD

V

DD,on-chip

V

SS,on-chip

0

1

63

C

C

C

0

0

1

63

63

Fei Yuan, Ph.D, P.Eng.

Professor

Department of Electrical and Computer Engineering

Ryerson University

Toronto, Ontario, Canada

Copyright c Fei Yuan, 2011

Copyright (c) F. Yuan 2011 (1)

Preface

This chapter deals with simultaneous switching noise (SSN). The

reduction of SSN is critical for mixed-mode circuits. In this chapter,

we investigate the sources of SSN and the eect of SSN. Techniques

that reduce the eect of SSN are examined in detail. The design

criteria for SSN are studied. The grounding schemes of analog and

digital circuits are investigated.

Copyright (c) F. Yuan 2011 (2)

OUTLINE

Simultaneous Switching Noise (SSN)

Eect of SSN

Analysis of SSN

SSN Reduction Techniques

Design Criteria for SSN

Analog and Digital Grounding

Copyright (c) F. Yuan 2011 (3)

SSN

Figure 1: Bonding wires, bonding pads, traces, and pins.

Bonding wires, bonding pads, traces, and pins form the interface

path between circuits on the chip and circuits on boards.

The resistance, capacitance, and inductance of the interface paths

largely determine the performance of systems.

Copyright (c) F. Yuan 2011 (4)

SSN (contd)

Figure 2: Bonding wires, bonding pads, traces, and pins.

Bonding wires at the corners are the longest - These wires have the

largest resistance and inductance.

The use of the bonding pads at the corners and the bonding wires

connected to these pads should be avoided.

The design rules of most CMOS technologies typically prohibit the

use of the bonding pads at the corners. These pads should be used

as dummy, i.e. no electrical connections to these pads.

Copyright (c) F. Yuan 2011 (5)

SSN (contd)

Figure 3: Bond pads and bond wires.

Bond Pads

Bond pads are on-chip metal rectangles large enough to be soldered

to leads, typically 70x70 m

2

- 100x100 m

2

.

Each pad is typically formed by the two top-most metal layers

connected to each other by many vias on the perimeter in order to

avoid the lift-o of the top metal layer during bonding.

Some CMOS processes require that all metal layers to be connected

together for bond pads. Because the top metal layer has a smaller

capacitance to the substrate as compared with the bottom metal

layer, connecting all bond-pad metal layers together will

dramatically increase the capacitance of the pad to the substrate.

Do not lay pads at the corners of the chip. Add dummy pads at the

corners instead.

Copyright (c) F. Yuan 2011 (6)

SSN (contd)

The capacitance of bond pads consists of two components : (i) the

area capacitance and (ii) the fringe capacitance

C

Pad

ox

1.15

A

H

+ 2.8

T

H

0.222

P

, (1)

where A=pad area, P=pad periphery, H=height of pad above

conductive silicon substrate, T=thickness of pad,

ox

=dielectric

constant of silicon dioxide. The rst term gives the area capacitance

whereas the second term quanties the fringe capacitance (Ref. T.

Sakurai and K. Tamaru, Simple formulas for two- and

three-dimensional capacitances, IEEE Trans. Electron Devices,

Vol.30, No. 2, pp.183-185, Feb. 1983.)

H increases C

pad

decreases. For high-speed applications, only

the top metal layers, such as top two metal layers, should be used

for signal pads. For V

DD

and V

DD

pads, all metal layers can be

connected together to form pads.

w

h1

h2

t1

t2

w

Ca

C

f1

C

f2

Substrate

Topmetallayers

Vias

Figure 4: Bonding pads are formed by topmost metal layers.

Typically C

pad

= 0.2 0.4 pF for a 100 100m pad.

Copyright (c) F. Yuan 2011 (7)

SSN (contd)

Inductance of Package

Self-Inductance:

L

ij

=

ij

I

j

=

B

ij

ds

ij

I

j

, (2)

ij

and B

ij

are the ux and intensity of the magnetic eld that is

generated by I

j

and passes through loop i. L

jj

, is called the

self-inductance quantifying the relation between the magnetic ux

of loop j and the current of loop j, L

ij

, i=j is called mutual

inductance.

I

Loop

Returnpath

B

Groundplane

Figure 5: Self-inductance denition.

Copyright (c) F. Yuan 2011 (8)

SSN (contd)

Inductance of Package (contd)

Self inductance of a round bond wire

R

H

Figure 6: Self-inductance of a round wire.

L

o

l

2

ln

2H

R

0.75

, (3)

where L=inductance per unit length, R=radius of the conductor, H

distance from the conductive substrate, and

o

=permittivity of free

space. Typically, L1nH/mm for bond wires. (Ref. T. Lee, The

Design of COS Radio-Frequency Integrated Circuits, 2nd ed.,

Cambridge University Press, 2004).

Self-Inductance of a rectangular trace

H

Figure 7: Self-inductance of a rectangular trace.

Copyright (c) F. Yuan 2011 (9)

L

1.6

K

f

H

W

, (4)

where L= inductance per unit length, K

f

0.72(

H

W

) + 1 (fringe

factor), W=width of the trace and H=distance from the trace to

the conductive substrate.

Copyright (c) F. Yuan 2011 (10)

SSN (contd)

Mutual Inductance of two round wires of equal length

I

Returnpath

I

Loop

Returnpath

B

Groundplane

Conductor1 Conductor2 1 2

1

Figure 8: Mutual-inductance denition.

H

d

Figure 9: Mutual-inductance of two round wires.

M =

o

l

2

ln

2l

d

1 +

d

l

, (5)

where L=inductance per unit length, l=length of bond wires,

d=distance between bond wires

For 10-mm length and 1-mm spacing, M4 nH. Since L10 nH,

the coupling coecient is 40% approximately.

Copyright (c) F. Yuan 2011 (11)

SSN (contd)

The Max. Frequency of Interfaces

The capacitance of band pads and the inductance of bond wires

form a 2nd-order low-pass. The upper limit of I/O frequency is set

by the cuto frequency of the low-pass. From

H(s) =

V

o

(s)

V

in

(s)

=

1

s

2

L

wire

C

total

+ 1

, (6)

where V

in

and V

o

are the voltage at the pin and the pad of the

interface, respectively, we have

6dB

=

1

L

wire

C

total

, (7)

where C

total

= C

pad

+C

pkg

.

When choosing packages, the highest design frequency of your

design must not exceed the cuto frequency of the I/O package.

Copyright (c) F. Yuan 2011 (12)

SSN (contd)

Lumped Model of Bond Wires

vin

vo

Lss

Rss

Css

Ldd

Rdd

dd C

vin

v

o

Cpad

Cpad Cpad

Cpad

V

DD,off-chip

V

DD,off-chip

V

SS,off-chip

V

SS,off-chip

Bondingwire

s

s s

s

Substrate

ground

Bondingpad

Figure 10: Lumped model of bond wires.

R

ss

=series resistance of bonding wires, L

ss

=self and mutual

inductances of bonding wires, C

ss

=package capacitance.

Bond wires are mainly inductive at high frequencies. Typical

L

ss

5nH, and are usually modeled as an inductor.

If a high-frequency current ows through a bonding wire, a voltage

drop across the bonding wire quantied by V

L

(t) = L

ss

di(t)

dt

is

generated.

This voltage drop aects on-chip V

DD

and V

ss

for V

DD

and V

ss

pads

and on-chip signals for signal pads.

Copyright (c) F. Yuan 2011 (13)

SSN (contd)

Output Buers

V

DD,off-chip

V

SS,off-chip

C

L

V

L

V

L

V

DD,on-chip

V

SS,on-chip

Cleanground

Chipboundary

Cleansupplyvoltage

Bondingpad

v

in

Bondingwire

vo

i

C

L

Lss

dd dd

ss

Figure 11: On-chip V

DD

& V

ss

uctuate due to switching noise.

Load capacitance of the inverter includes (1) Output capacitance of

output buer, (2) Capacitance of bond pads, (3) Capacitance of

package, and (4) Capacitance of o-chip printed-circuit-board

(PCB) traces.

O-chip capacitances are typically much larger than on-chip

capacitances.

To meet timing constraints, large output buers (wide inverters) are

needed to drive o-chip capacitive loads.

W/L R

on

.

W/L C

out

C

L

.

Copyright (c) F. Yuan 2011 (14)

SSN (contd)

Output Buers (contd)

The load capacitance is typically 1 30 pF. Typical size of output

buers 500 1000m.

The size of inverter should be increased by a factor of e = 2.71828.

The optimal number of inverters is such that the input capacitance

of the last inverter should be 1/e that of the load capacitance (Ref.

C. Mead and L. Conway, Introduction to VLSI systems,

Addison-Wesley, 1980).

Typical ratio of 4 5 is used in sizing output buers in order to

save silicon area.

Static inverter-based output buers can be used for clock speed up

to a few hundred MHz. These output buers can not be used for

very high-speed clock speeds.

Copyright (c) F. Yuan 2011 (15)

SSN (contd)

Charging/discharging Currents of Output Buers

Large charging/discharging current spikes

1) C

L

is large, because i

C

(t) = C

L

v

C

(t)

dt

i

C

(t) is large.

2) Sharp rising/falling edges

v

C

(t)

dt

is large i

C

(t) is large.

v

t

t

t

i

C

V

OH

V

OL

in

v

V

OH

V

OL

o

t

V

DD,on-chip

t

V

SS,on-chip

V

L

V

L

V

DD

0

dd

ss

Figure 12: Large charging/discharging current spikes and the uctuation of on-chip V

DD

and V

ss

.

Copyright (c) F. Yuan 2011 (16)

SSN (contd)

Switching Noise

V

DD

V

ss

C

L

V

L,DD

V

L,ss

V

DD,on-chip

V

ss,on-chip

Cleanpower

Cleanground

Output

buffer

Chip

Off-chip

capacitive

load

Noisypower

Noisyground

Figure 13: Noisy on-chip V

DD

& V

ss

.

When sharp charging/discharging currents of output buers ow

through the bond wires of V

DD

and V

ss

, large voltage drops v

L,DD

and v

L,ss

across the bond wires are generated

On-chip V

DD

and V

ss

vary with switching power uctuation and

ground bouncing:

v

DD,onchip

= V

DD

v

L,DD

v

SS,onchip

= V

ss

v

L,ss

(8)

Copyright (c) F. Yuan 2011 (17)

SSN (contd)

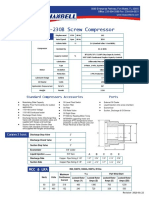

Simultaneous Switching Noise (SSN)

B0

B1

B63

V

DD

V

SS

V

DD

V

DD,on-chip

V

SS,on-chip

0

1

63

C

C

C

0

0

1

63

63

Figure 14: Simultaneous switching noise.

Large switching noise at power and ground rails exist if multiple

buers switch simultaneously Simultaneous switching noise (the

Worst Case).

.

V

DD,onchip

= V

DD

v

L,DD

,

v

L,DD

= L

DD

i

DD

dt

= L

DD

63

n=0

di

C,n

dt

.

(9)

Copyright (c) F. Yuan 2011 (18)

Eects of SSN

Fluctuation of on-chip V

DD

and V

ss

.

V

DD,onchip

= V

DD

v

L,DD

,

V

ss,onchip

= v

L,ss

.

(10)

Reduce noise margins of digital circuits

v

in

v

o

V

OH

V

OL

V

OH

V

OL

V

IL

V

IH

NM NM

H L

Noisemarginswith

switchingnoiseconsidered

V

L

V

L

NM NM

H L

Noisemarginswithout

switchingnoiseconsidered

ss

dd

Figure 15: Reduction of noise margins due to switching noise.

NM

L

= (V

OH

V

L

dd

) V

IH

,

NM

H

= V

IL

(V

OL

+ V

L

ss

).

(11)

Copyright (c) F. Yuan 2011 (19)

Eects of SSN

Change the Operating Point of Analog Circuits

Consider a MOSFET biased in saturation, the transconductance g

m

is given by g

m

=

i

D

v

GS

2I

D

V

GS

V

T

, where I

D

and V

GS

are channel

current and gate-source voltage at dc biasing point. Both I

D

and

V

GS

are functions of V

DD,onchip

.

SSN imposes stringent requirements on analog circuits. Analog

circuits need to be dierentially congured in mixed analog/digital

circuits increased circuit complex.

C

L

V

L

V

L

V

DD,on-chip

V

SS,on-chip

v

in

vo

V

B

V

B

v

in

v+

in

v-

in

v+ v-

o o

M1

M2

vo

J

dd

ss

Analogportion Digitalportion

Figure 16: Mixed analog/digital circuits.

Copyright (c) F. Yuan 2011 (20)

Eects of SSN (contd)

Change of Operating Point of Analog Circuits

(contd)

High power noise rejection dicult to design. If V

DD

uctuation is of a critical concern, Fig.17(a) should be used. The

head biasing current source behaves as an OPEN-CIRCUIT for V

DD

switching noise and isolates the circuit from V

DD

rail.

If V

ss

uctuation is of a critical concern, Fig.17(b) should be used.

The tail biasing current source behaves as an OPEN-CIRCUIT for

V

ss

switching noise and isolates the circuit from V

ss

rail.

Cascodes and regulated cascodes are widely used in realizing these

biasing current sources to maximize the resistance of the current

sources.

(a) (b)

Fluctuating VDD

Fluctuating Vss

Figure 17: Dierential congurations.

Copyright (c) F. Yuan 2011 (21)

Eects of SSN (contd)

Increase the Timing Jitter of Oscillators/Clocks

V

DD,on-chip

V

ss,on-chip

C

Vo1

t

Vo1

Vo2

t

V

TH

t

V

TH

t

V

TH

Clean VDD Noisy VDD

Dt

Figure 18: Timing jitter due to switching noise.

The threshold crossing points of ring oscillators vary due to the

noise (thermal and icker noise) of the transistors. Such a variation

is quantied by

2

- the timing jitter.

Assume threshold voltage V

TH

= V

DD,onchip

/2. For rising edge,

V

DD,onchip

= v

C

+ R

p

C

dv

C

dt

, (12)

where R

p

is the equivalent channel resistance of pMOS. It is seen

that v

C

, subsequently, the threshold-crossing point, vary with

V

DD,onchip

, which is a function of switching noise.

Copyright (c) F. Yuan 2011 (22)

Analysis of SSN

Simplied Analysis of SSN

SSN in Sub-micron CMOS Circuits

Copyright (c) F. Yuan 2011 (23)

Simplied Analysis of SSN

Assumptions

Triangle waveform of charging/discharging current.

Neglect channel resistance of transistors.

v

v

i

L

DD

i

L

SS

I

max

I

max

t/2

s

t

s

0

t

t

t

t

out

in

Figure 19: Simplied analysis of SSN.

Copyright (c) F. Yuan 2011 (24)

Simplied Analysis of SSN (contd)

Analysis

Total charge stored in C

L

before discharging Q = C

L

V

DD

.

Total charge through L when C

L

is completely discharged

Q =

t

s

0

i

L

(t)dt = I

avg

t

s

=

I

max

2

t

s

.

Charge conservation : C

L

V

DD

=

I

max

2

t

s

Because

i

L

(t)

dt

max

=

I

max

0

t

s

/20

=

2I

max

t

s

, we have

di

L

dt

max

=

4C

L

V

DD

t

2

s

(13)

Example: L = 5nH, t

s

= 5ns, C

L

= 10pF, V

DD

= 5V, L

di

L

dt

max

=40

mV.

SSN is extremely sensitive to t

s

. Trade-os between speed (t

s

) and

SSN are made in design of output buers. The speed of output

buers should be set to the lowest possible value to minimize

switching noise.

Copyright (c) F. Yuan 2011 (25)

SSN in Sub-micron CMOS Circuits

Sub-micron MOSFETs

Sub-micron : channel length is less than 1m.

Sub-micron MOS transistors exhibit velocity saturation due to

excessive lateral electric eld and mobility degradation due to

excessive vertical electric eld.

E(V/um)

Velocity(cm/s)

Vsat=10

7

E(V/um)

Velocity(cm/s)

Esat=1.5

Vsat=10

7

Et(V/um)

Mobility(cm^2/Vs)

700

250

0

0 0

Figure 20: Velocity saturation and mobility degradation.

Square-law does not hold for sub-micron MOS transistors. Instead,

-power law applies.

i

D

=

0 ifv

GS

< V

T

(cuto)

k

l

(v

GS

V

T

)

/2

ifv

DS

< v

DS,sat

(Triode)

k

s

(v

GS

V

T

)

ifv

DS

> v

DS,sat

(Saturation)

(14)

where k

l

=

n

C

ox

(W/L), k

s

=

1

2

n

C

ox

(W/L). Typically, 1 < < 1.2

Copyright (c) F. Yuan 2011 (26)

SSN in Sub-micron CMOS Circuits (contd)

Analysis

For a total of n output drivers that switch simultaneously, the total

current

i

DS,total

= ni

DS

= nk

s

(v

in

V

T

v

n

)

(15)

SSN

v

n

= L

ss

di

DS,total

dt

= L

ss

nk

s

(v

in

V

T

v

n

)

1

d(v

in

v

n

)

dt

(16)

Because a1, (v

in

V

T

v

n

)

1

1 We therefore have

v

n

= L

ss

nk

s

(dv

in

v

n

)

dt

= L

ss

nk

s

dv

in

dt

L

ss

nk

s

dv

n

dt

(17)

This gives

dv

n

dt

+

v

n

nL

ss

k

s

=

dv

in

dt

(18)

Copyright (c) F. Yuan 2011 (27)

SSN in Sub-micron CMOS Circuits (contd)

Input waveform

VDD

V

T

t

n

t

r

t

f

Vin

Figure 21: SSN analysis.

Slopes

Slope of the rising section of the input

dv

in

dt

= S

r

=

V

DD

t

r

(19)

Equation for the rising section

Substituting the slope (the rising section of the input)

dv

n

dt

+

v

n

nL

ss

k

s

= S

r

, v

n

(t

n

) = 0, t

n

=

V

T

S

r

, t

n

tt

r

(20)

This is a rst-order ODE.

Copyright (c) F. Yuan 2011 (28)

SSN in Sub-micron CMOS Circuits (contd)

Solution

Homogeneous ODE - general solution

dv

n

dt

=

v

n

nL

ss

k

s

(21)

v

n

= Ae

(ttn)

nksLss

, tt

n

(22)

Special solution (v

n

= C (constant))

C

nk

s

L

ss

=

V

DD

t

r

(23)

which gives

C =

V

DD

t

r

nk

s

L

ss

(24)

Complete solution

v

n

(t) =

V

DD

t

r

nk

s

L

ss

+Ae

(ttn)

nksLss

(25)

Match the initial condition at t

n

=

V

T

S

r

, v

n

(t

n

) = 0

A =

V

DD

nk

s

L

ss

t

r

(26)

Copyright (c) F. Yuan 2011 (29)

SSN in Sub-micron CMOS Circuits (contd)

Complete solution

v

n

(t) =

V

DD

nk

s

L

ss

t

r

1 e

(tt

n

)

nk

s

L

ss

, t

n

tt

r

. (27)

Remarks:

v

n

(t) is proportional to

n (number of switching buers)

L

ss

(bond wire inductance)

k

s

=

1

2

n

C

ox

(W/L)

n

(buer size)

1/t

r

(switching time)

The maximum SSN

V

n,max

=

V

DD

nk

s

L

ss

t

r

(28)

For a reliable operation, V

n,max

V

T

is generally required. This

yields the limiting condition

V

DD

nkL

ss

t

r

= V

T

(29)

from which n and W can be determined for given V

T

and t

r

.

Copyright (c) F. Yuan 2011 (30)

SSN Reduction Techniques

Separate power and ground pins and pads for analog

and digital circuits whenever possible

VDD

Chip

Bondwires

VDD

Toanalogcircuits

Todigitalcircuits

Bondwires

Analogpad

Digitalpad

Digitalpin

Analogpin

Figure 22: Separate analog and digital pins and pads.

Switching noise generated by the digital portion of the system will

not aect the operation of the analog portion of the systems.

Copyright (c) F. Yuan 2011 (31)

SSN Reduction Techniques (contd)

Multiple pads and pins for power and ground

V

Chipboundary

Bondwires

Tocircuits

DD

Off-chip

decoupling

capacitor

PAD

Figure 23: Multiple pins and pads.

Increase the number of pins smaller inductance lower SSN.

Copyright (c) F. Yuan 2011 (32)

SSN Reduction Techniques (contd)

Multiple pads and pins for power and ground

(contd)

Pin=1

Pin=2

Pin=5

Pin=10

NumberofDrivers

SSN

Figure 24: Eect of multiple pins.

Increase the number of pins better linearity of SSN.

Copyright (c) F. Yuan 2011 (33)

SSN Reduction Techniques (contd)

Avoid using corner pads

Corner pads have long bonding wires large self-inductances.

Most design rules require dummy pads (pads with no connection) at

corners.

Use center pads for V

DD

and V

ss

smaller

inductance, smaller SSN.

Short bond wires, small self-inductances.

Copyright (c) F. Yuan 2011 (34)

SSN Reduction Techniques (contd)

Pre-driver skewing

To prevent the entire buer (multi-nger layout - multiple

smaller inverters connected in parallel) to switch at the same

time.

Use RC Delay Lines

G

S

D

n+

1 2 3 4

Metal-1 Metal-2

Contact/via

Figure 25: Multi-nger layout of output buers. Both drain and source are shared by neighboring

ngers.

M1 M2 M3

M4

G

D

S

Figure 26: Schematic of the equivalent circuit of output buers with a multi-nger layout.

Copyright (c) F. Yuan 2011 (35)

SSN Reduction Techniques (contd)

Pre-driver skewing (contd)

C

L

v

o

C

n

C

p

C

n

C

p

R

n

R

p v

in

L

dd

L

ss

V

DD

Figure 27: Output buer with pre-skew.

R

n

, R

p

= lumped n-well or poly resistors, C

n

, C

p

= gate-source

capacitance. P

1

/N

1

turn on rst, P

1

/N

1

turn on second, and

P

M

/N

M

turn on the last.

Drawback - reduced speed. Compromise between SSN and speed

must be made.

Copyright (c) F. Yuan 2011 (36)

SSN Reduction Techniques (contd)

Pre-driver skewing (contd)

Use Gate Series Resistance for skewing

G

S

D

n+ diffusion

Gate series resistances

Figure 28: Pre-driver skewing using the gate series resistance.

Less eective for silicide processes because the sheet resistance of

gate ploy is small (approximately 7/2).

Copyright (c) F. Yuan 2011 (37)

SSN Reduction Techniques (contd)

On-chip decoupling (bypass) capacitors

V

DD

C

L

L

L

ss

V

DD,on-chip

V

SS,on-chip

Digital

circuits

On-chip

decoupling

capacitor

dd

Figure 29: On-chip decoupling (bypass) capacitors.

On-chip decoupling capacitors are eective in reducing SSN

generated by internal logic circuits because they prevent current

spikes generated by the internal logic circuits from going to L

ss

and

L

DD

by providing a local AC path. On-chip decoupling capacitors

serve as local charge reservoirs.

On-chip decoupling capacitors must be very large in order to be

eective, usually comparable to the total area of all transistors on

chip (10-20% of total silicon area) - very expensive !

Resistance is needed to avoid the self resonance formed by the

on-chip decoupling capacitors and bond wires on-chip

decoupling capacitors are typically implemented using MOS

capacitors. The channel resistance of MOS capacitors are benecial

in minimizing the self resonance of the preceding LC networks.

Copyright (c) F. Yuan 2011 (38)

Most CMOS fabrication processes require certain percentage of

metal ll ratio for each metal layers (required for minimizing

mechanical stress reasons). Dummy metal sections are often

employed in each metal layer to fulll this requirement. These

dummy metal sections can be arranged in such a way that they

form on-chip decoupling capacitors to improve the performance of

designed chips.

Copyright (c) F. Yuan 2011 (39)

SSN Reduction Techniques (contd)

Hierarchy of decoupling capacitors (contd)

PCBboard

boundary

Chipboundary

On-board

decoupling

capacitor

On-chip

decoupling

capacitor

External

supply

voltage

Local

logic

Local

logic

Local

logic

Transientcurrent

Figure 30: Hierarchy of on-chip de-coupling capacitors.

Both o-chip and on-chip decoupling capacitors are required

to minimize switching noise.

Decoupling capacitors must be placed as close as possible to

hot spots (noise sources) to eliminate generated switching

noise locally.

Traces and interconnects for decoupling capacitors must have

a low impedance at high frequencies such that a

low-impedance path exists to eliminate switching noise.

Copyright (c) F. Yuan 2011 (40)

SSN Reduction Techniques (contd)

Fully-balanced buers

D

1

D

2

D

N

R

L

R

L

R

L

L

dd

L

ss

Figure 31: Balanced buers.

Each buer conveys a fully dierential current to the channel. Each

buer draws a constant current from the supply and injects a

constant current to the ground. No net rate change of the current

owing through V

DD

and ground pins - no switching noise.

Copyright (c) F. Yuan 2011 (41)

SSN Reduction Techniques (contd)

Fully-balanced buers (contd)

D D

Channel

I

D D

I

D D

Channel

I

z

T

z

T

Figure 32: Balanced buers.

In the left gure, low-voltage-dierential-signaling (LVDS) is used.

The logic state of the output is represented by the direction of the

output current. The channel is terminated at the far end by the

termination resistor. The resistor also converts the current into a

voltage.

In the right gure, the channel is terminated with the line

characteristic impedance at the near end of the channel.

Copyright (c) F. Yuan 2011 (42)

SSN Reduction Techniques (contd)

Current-mode logic circuits

Use logic circuits that draw a constant current from V

DD

and inject

a constant current to V

ss

. Current-mode logic (CML) circuits, fully

dierential logic circuits belong to this category.

I

V

b

J

V

b

V

b M7 M8

A A

B B A A

AB AB

J

V

b

V

b

B B

B B A A

A+B A+B

A A

A A

Figure 33: Current-mode logic gates.

CML circuits draw a constant static current from V

DD

regardless of

its logic states C

L

di

L

dt

= 0, resulting in zero switching noise.

CML circuits consume static power. They are typically used for

I/Os or in applications where switching noise is critical.

CML circuits consume less power as compared with static logic

circuits at very high frequencies. This is because the dynamic power

consumption of static circuits is governed by P

d

= aCfV

2

DD

, where

a=switching activity parameter, f=frequency. It is evident that P

d

is directly proportional to f. The power consumption of CML

circuits is independent of f!

Copyright (c) F. Yuan 2011 (43)

Design Criteria for SSN

SSN must less than Threshold Voltages

For a reliable operation, V

n,max

< V

T

is generally required.

Switching noise derived before

v

n

(t) =

V

DD

nk

s

L

ss

t

r

1 e

(ttn)

nksLss

, t

n

tt

r

. (30)

This yields

V

DD

nkL

ss

t

r

= V

T

, (31)

from which n and W can be determined for given V

T

, f, and t

r

.

Copyright (c) F. Yuan 2011 (44)

Analog and Digital Grounding

Substrate Modeling

Resistive paths exist from p+ contacts to p-substrate. A voltage

change of p+ contacts aects the voltage of substrate.

Capacitive paths exist from p+/n-well, n+/p-substrate, and

n-well/p-substrate junctions.

p+ p+ n+

R

p+

C

J

12

R

11

R

22

R

11

R

22

R

12

Backplane

Figure 34: Lumped models of heavily doped substrates.

R

12

R

11

, R

22

. R

12

= resistance between contacts, R

11

,

R

22

=resistance from contacts to the backplane. Most of substrate

noise will travel vertically down to the backplane. The backplane

must be grounded properly to avoid the distribution of substrate

noise to the entire chip. (Ref.: B. Owens et al. Simulation and

measurement of supply and substrate noise in mixed-signal ICs,

IEEE J. Solid-State Circuits, Vol.40, No.2, pp. 382-391, Feb. 2005).

Copyright (c) F. Yuan 2011 (45)

Analog and Digital Grounding (contd)

Separate analog and digital power pads and bonding

wires for analog and digital circuits.

V

Chipboundary

Bondwires

Analogpad

Digitalpad

DD

Off-chip

decoupling

capacitor

o

v

in

v

v

in

o

v

Figure 35: Separate analog and digital V

DD

pads and bonding wires for analog and digital circuits.

Digital V

DD

rails are much more noisy as compared with analog

V

DD

.

Copyright (c) F. Yuan 2011 (46)

Analog and Digital Grounding (contd)

Separate analog and digital ground pads and

bonding wires for analog and digital circuits.

Chipboundary

Bondwires

Analog

groundpad

Digital

groundpad

o

v

in

v

v

in

o

v

Figure 36: Separate analog and digital V

ss

pads and bonding wires for analog and digital circuits.

Digital V

ss

rails are much more noisy as compared with analog V

ss

.

Copyright (c) F. Yuan 2011 (47)

Analog and Digital Grounding (contd)

Separate analog and digital substrate connections.

Chipboundary

Analog

groundpad

Digital

groundpad

o

v

in

v

v

in

o

v

Substrate

pad

Figure 37: Separate analog and digital substrate connections.

Analog substrates are typically protected by guard rings. They are

less noisy as compared with digital substrates.

Connecting analog substrate to the outside ground directly can

lower the voltage uctuation of the analog substrate. Downside:

body eect occurs as V

T

= V

To

+

V

sb

+|2

F

|

|2

F

|), where

is body-eect coecient and

F

0.6V is the Fermi potential.

If analog substrates are well protected, then the source of

MOSFETs and analog substrates can be tied together to eliminate

the body eect. Example - dierential pairs.

Copyright (c) F. Yuan 2011 (48)

Analog and Digital Grounding (contd)

Figure 38: Dierential conguration.

Single-ended conguration - v

GS

is directly aected by ground

bouncing.

The output of dierential-mode congurations is insensitive of SSN

as the biasing circuitry provides a constant biasing current to the

dierential pair regardless of ground bouncing.

Deep sub-micron MOS transistors have a small output impedance,

reducing the eectiveness of the biasing circuitry. Cascode is

generally mandatory in biasing circuits to minimize the eect of

ground bounding.

Copyright (c) F. Yuan 2011 (49)

Analog and Digital Grounding (contd)

Passive Guard-Rings

Use passive guard-rings to isolate sensitive circuits from noisy

digital circuits.

p+ guard rings - p+ diusion contacts on p-substrate to collect

holes. n+ guard rings - n+ diusion contacts in n-wells to collect

electrons.

Guard ring resistance should be made as low as possible guard

rings should be made as wide as possible.

Guard rings should be placed as close as possible to noise sources.

Analogcircuits

p+

Metallayer

Contact

Analogcircuits

p+ p+

p-substrate

Metallayer

Contact

Chipboundary

Bonding

pad

Bondingwire

(a) Topview

(b)Sideview

Off-chip

ground

Figure 39: p-type passive guard rings.

Copyright (c) F. Yuan 2011 (50)

Analog and Digital Grounding (contd)

Active Guard Rings

p-substrate

Activeguardring

Dv

v

o

p+ p+

Digital

circuits

Analog

circuits

v

o

v

n

Substratenoiseis

representedby Vn

R R

R

R

Figure 40: Active passive guard rings (Ref. K. Fukuda et al., Substrate noise reduction using active

grant band lters in mixed-signal integrated circuits, IEICE Trans. Fundamentals of Electronics,

Communications and Computer Sciences, Vol. E80-A, pp.313-320, Feb. 1997).

Use active guard-rings to ACTIVELY isolate sensitive circuits from

noisy digital circuits. Active guard rings perform better as

compared with passive guard rings.

The inverting voltage buer must have a large bandwidth in order

to be eective in suppressing substrate noise. This is because v

n

contains a signicantly large number of high-frequency components

and these components must appear at the output of the buer in

order to suppress substrate noise.

Copyright (c) F. Yuan 2011 (51)

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- TLEd 201 - Module 3 Lesson 1Document5 pagesTLEd 201 - Module 3 Lesson 1charmen rogandoNo ratings yet

- Kempomat: EN FI SV NO DA DE NL FR ES PL RUDocument26 pagesKempomat: EN FI SV NO DA DE NL FR ES PL RUmcombaleNo ratings yet

- Op AmpDocument42 pagesOp AmpJyotiSharmaNo ratings yet

- A029x163 I7 201902 PDFDocument106 pagesA029x163 I7 201902 PDFFri LayNo ratings yet

- Hanbell Spec Sheet RC2-230B PDFDocument1 pageHanbell Spec Sheet RC2-230B PDFDaniel Naoe FestinNo ratings yet

- Brinkmann: Manual For Integrated AmplifierDocument4 pagesBrinkmann: Manual For Integrated AmplifierFabrice DotzlerNo ratings yet

- 45 60055 Ee416 2017 5 2 1 Ee413 Laboratory Experiments GroupDocument80 pages45 60055 Ee416 2017 5 2 1 Ee413 Laboratory Experiments Groupraghad zuhair yousifNo ratings yet

- Design of IEC 61850 Based Substation Automation SyDocument9 pagesDesign of IEC 61850 Based Substation Automation SyBravery DamanikNo ratings yet

- Rochester Gauges DLCCDocument20 pagesRochester Gauges DLCCx01001932100% (1)

- Thuraya RepeatersDocument2 pagesThuraya RepeatersFredrick MuigaiNo ratings yet

- Load Schedule Calculation SheetDocument6 pagesLoad Schedule Calculation SheetlakshminarayananNo ratings yet

- Ebs-6200 User's ManualDocument124 pagesEbs-6200 User's ManualDavid MiguelNo ratings yet

- Est3 Remote Annunciators: 3-Anncpu3, 3-Lcdann, 3-6ann, 3-10ann, 3-Evxxx, 3-4annDocument4 pagesEst3 Remote Annunciators: 3-Anncpu3, 3-Lcdann, 3-6ann, 3-10ann, 3-Evxxx, 3-4annrupali patilNo ratings yet

- CTMM RelayDocument3 pagesCTMM RelayshiyasNo ratings yet

- Lecture11 EE101A W16Document13 pagesLecture11 EE101A W16ankitgoyal100No ratings yet

- Unit 2Document16 pagesUnit 2danishmaniNo ratings yet

- Diesel Engine Fire Pump Controller (GPD Model)Document9 pagesDiesel Engine Fire Pump Controller (GPD Model)haryNo ratings yet

- Ch11 6628089Document54 pagesCh11 6628089khaled99No ratings yet

- JNTUA - B Tech - 2018 - 3 2 - Dec - R15 - EEE - 15A02603 POWER SYSTEM ANALYSISDocument2 pagesJNTUA - B Tech - 2018 - 3 2 - Dec - R15 - EEE - 15A02603 POWER SYSTEM ANALYSISVinay ChinthaNo ratings yet

- Pathfinder Manual 2012Document192 pagesPathfinder Manual 2012shawqiNo ratings yet

- Catalogo Schneider 2019Document33 pagesCatalogo Schneider 2019vjdmNo ratings yet

- Module 1Document54 pagesModule 1TALLAH CHOWHANNo ratings yet

- AS4000 Installation Manual 925600Document142 pagesAS4000 Installation Manual 925600Brandon100% (1)

- Crane Scale CS-2000ManualDocument18 pagesCrane Scale CS-2000ManualMauricio Rodolfo Cuevas DonaireNo ratings yet

- 667 HB 32750 000Document220 pages667 HB 32750 000MadhuNo ratings yet

- Cri-1000 2Document5 pagesCri-1000 2Zeeshan AhmadNo ratings yet

- Mentor PADSVX ODA Starter Library Guidelines Rev1a-558Document48 pagesMentor PADSVX ODA Starter Library Guidelines Rev1a-558Zeynep Emirhan ŞenyüzNo ratings yet

- Brushless DC MotorDocument19 pagesBrushless DC MotorSanjeet KumarNo ratings yet

- C&I in Water Treatment PlantsDocument28 pagesC&I in Water Treatment PlantsSunil PanchalNo ratings yet

- Module On Electrical Circuits and Electrical SafetyDocument17 pagesModule On Electrical Circuits and Electrical SafetyJomel HerrasNo ratings yet