Professional Documents

Culture Documents

7490

Uploaded by

jakaroboOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

7490

Uploaded by

jakaroboCopyright:

Available Formats

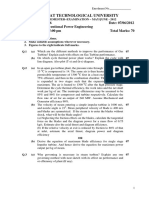

DM7490A Decade and Binary Counter

August 1986 Revised July 2001

DM7490A Decade and Binary Counter

General Description

The DM7490A monolithic counter contains four masterslave flip-flops and additional gating to provide a divide-bytwo counter and a three-stage binary counter for which the count cycle length is divide-by-five. The counter has a gated zero reset and also has gated setto-nine inputs for use in BCD nines complement applications. To use the maximum count length (decade or four-bit binary), the B input is connected to the QA output. The input count pulses are applied to input A and the outputs are as described in the appropriate Function Table. A symmetrical divide-by-ten count can be obtained from the counters by connecting the QD output to the A input and applying the input count to the B input which gives a divideby-ten square wave at output QA.

Features

s Typical power dissipation 145 mW s Count frequency 42 MHz

Ordering Code:

Order Number DM7490AN Package Number N14A Package Description 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Connection Diagram

2001 Fairchild Semiconductor Corporation

DS006533

www.fairchildsemi.com

DM7490A

Function Tables

BCD Count Sequence (Note 1) Outputs QD L L L L L L L L H H QC L L L L H H H H L L QB L L H H L L H H L L QA L H L H L H L H L H

Logic Diagram

Count 0 1 2 3 4 5 6 7 8 9

BCD Bi-Quinary (5-2) (Note 2) Outputs QA L L L L L H H H H H QD L L L L H L L L L H QC L L H H L L L H H L QB L H L H L L H L H L

Count 0 1 2 3 4 5 6 7 8 9

Reset/Count Function Table Reset Inputs R0(1) H H X X L L X

H = HIGH Level L = LOW Level X = Dont Care Note 1: Output QA is connected to input B for BCD count. Note 2: Output QD is connected to input A for bi-quinary count

Outputs R9(2) X L H L X L X QD L L H QC L L L QB L L L QA L L H

R0(2) H H X L X X L

R9(1) L X H X L X L

The J and K inputs shown without connection are for reference only and are functionally at a HIGH level.

COUNT COUNT COUNT COUNT

www.fairchildsemi.com

DM7490A

Absolute Maximum Ratings(Note 3)

Supply Voltage Input Voltage Operating Free Air Temperature Range Storage Temperature Range 7V 5.5V 0C to +70C

Note 3: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions table will define the conditions for actual device operation.

65C to +150C

Recommended Operating Conditions

Symbol VCC VIH VIL IOH IOL fCLK tW Supply Voltage HIGH Level Input Voltage LOW Level Input Voltage HIGH Level Output Current LOW Level Output Current Clock Frequency (Note 4) Pulse Width (Note 4) tREL TA Reset Release Time (Note 4) Free Air Operating Temperature A B A B Reset 0 0 15 30 15 25 0 70 ns ns Parameter Min 4.75 2 0.8 Nom 5 Max 5.25 Units V V V mA mA MHz

0.8

16 32 16

Note 4: TA = 25C and VCC = 5V.

DC Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted) Symbol VI VOH VOL II IIH Parameter Input Clamp Voltage HIGH Level Output Voltage LOW Level Output Voltage HIGH Level Input Current IIL LOW Level Input Current IOS ICC Short Circuit Output Current Supply Current Conditions VCC = Min, II = 12 mA VCC = Min, IOH = Max VIL = Max, VIH = Min VCC = Min, IOL = Max VIH = Min, VIL = Max (Note 6) VCC = Max VI = 2.7V VCC = Max VI = 0.4V VCC = Max (Note 7) VCC = Max (Note 8) A Reset B A Reset B 18 29 2.4 3.4 0.2 0.4 1 80 40 120 3.2 1.6 4.8 57 42 mA mA mA A Min Typ (Note 5) Max 1.5 Units V V V mA

Input Current @ Max Input Voltage VCC = Max, VI = 5.5V

Note 5: All typicals are at VCC = 5V, TA = 25C. Note 6: QA outputs are tested at I OL = Max plus the limit value of IIL for the B input. This permits driving the B input while maintaining full fan-out capability. Note 7: Not more than one output should be shorted at a time. Note 8: ICC is measured with all outputs open, both RO inputs grounded following momentary connection to 4.5V, and all other inputs grounded.

www.fairchildsemi.com

DM7490A

AC Switching Characteristics

at VCC = 5V and TA = 25C Symbol fMAX tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL tPHL Parameter Maximum Clock Frequency Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time HIGH-to-LOW Level Output From (Input) To (Output) A to QA B to QB A to QA A to QA A to QD A to QD B to QB B to QB B to QC B to QC B to QD B to QD SET-9 to QA, QD SET-9 to QB, QC SET-0 Any Q RL = 400, CL = 15 pF Min 32 16 16 18 48 50 16 21 32 35 32 35 30 40 40 Max MHz ns ns ns ns ns ns ns ns ns ns ns ns ns Units

www.fairchildsemi.com

DM7490A Decade and Binary Counter

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 5 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

www.fairchildsemi.com

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Law of NationsDocument667 pagesThe Law of NationsJo Jo100% (1)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Maintenance Manual: Models 8300, 8400, and 8500 Pallet Trucks and Model 8600 Tow TractorDocument291 pagesMaintenance Manual: Models 8300, 8400, and 8500 Pallet Trucks and Model 8600 Tow TractorJosé Luis Ang Soto92% (13)

- F5 TcpdumpDocument14 pagesF5 TcpdumpNETRICH IT SolutionsNo ratings yet

- Default passwords for 3COM network devicesDocument42 pagesDefault passwords for 3COM network devicesJamey ParkerNo ratings yet

- Online Shopping RequirementsDocument19 pagesOnline Shopping Requirementsbruh tesheme100% (1)

- Electrolysis Cell Student ActivityDocument3 pagesElectrolysis Cell Student ActivityPersonnumberunoo0% (2)

- Basic Education Research AgendaDocument41 pagesBasic Education Research AgendaKristine Barredo100% (1)

- Industry 4.0 CourseDocument49 pagesIndustry 4.0 CourseThiruvengadam CNo ratings yet

- مساهمة البرمجيات المدمجة في تحسين جودة خدمات الإدارة الجبائية (عرض برمجية جباية -تيك نموذجا) PDFDocument18 pagesمساهمة البرمجيات المدمجة في تحسين جودة خدمات الإدارة الجبائية (عرض برمجية جباية -تيك نموذجا) PDFAnis AnisNo ratings yet

- Tommy Matsumoto, AT&T Jens Co. Yoshitaka Senoo, Daiichi Co.,LtdDocument7 pagesTommy Matsumoto, AT&T Jens Co. Yoshitaka Senoo, Daiichi Co.,Ltdpostscript100% (1)

- Dell Wireless Card Guide AddendumDocument6 pagesDell Wireless Card Guide AddendumwazupecNo ratings yet

- Army C-sUAS Systems AssessmentDocument4 pagesArmy C-sUAS Systems AssessmentArthur WongNo ratings yet

- GTU BE- Vth SEMESTER Power Engineering ExamDocument2 pagesGTU BE- Vth SEMESTER Power Engineering ExamBHARAT parmarNo ratings yet

- Jarme 3 1 2010Document8 pagesJarme 3 1 2010kannanmech87No ratings yet

- Specification (General) Road Concreting ProjectDocument66 pagesSpecification (General) Road Concreting ProjectMARK RANEL RAMOSNo ratings yet

- BentleyDocument27 pagesBentleycipele12No ratings yet

- Underground Cable Ampacity With Neher McGrathDocument7 pagesUnderground Cable Ampacity With Neher McGrathJesus RodriguezNo ratings yet

- Bca Oct2010Document118 pagesBca Oct2010lalitmunawat100% (1)

- ASME Piping Standards and Material Selection GuideDocument36 pagesASME Piping Standards and Material Selection Guideتدریس زبان ESLNo ratings yet

- Vxlan White Paper c11 729383Document10 pagesVxlan White Paper c11 729383steve stevensonNo ratings yet

- Sumit Pandey CVDocument3 pagesSumit Pandey CVSumit PandeyNo ratings yet

- M433 Center of Mass Location Throughout Fuze Arming CycleDocument17 pagesM433 Center of Mass Location Throughout Fuze Arming CycleNORDBNo ratings yet

- Seismic Gripple Cable BracingDocument6 pagesSeismic Gripple Cable BracingThanh HuyNo ratings yet

- Southwire Mining Product CatalogDocument32 pagesSouthwire Mining Product Catalogvcontrerasj72No ratings yet

- Willy Chipeta Final Thesis 15-09-2016Document101 pagesWilly Chipeta Final Thesis 15-09-2016EddiemtongaNo ratings yet

- APR Lntegrus Singapore TechnicalDocument148 pagesAPR Lntegrus Singapore Technicaldom007thyNo ratings yet

- Noise Barriers Standards FrameworkDocument50 pagesNoise Barriers Standards FrameworkanandalaharNo ratings yet

- PCBA MachineDocument62 pagesPCBA MachineSahara MalabananNo ratings yet

- Gas Pressure Regulator Installation InstructionsDocument10 pagesGas Pressure Regulator Installation Instructionssayem biswasNo ratings yet

- PRISM Proof Cloud Email ServicesDocument11 pagesPRISM Proof Cloud Email ServiceshughpearseNo ratings yet