Professional Documents

Culture Documents

CSC159 Ch4 Interrupt - Stack

Uploaded by

Mohd FaizrulOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CSC159 Ch4 Interrupt - Stack

Uploaded by

Mohd FaizrulCopyright:

Available Formats

Topic 4 INTERRUPT AND STACK Introduction Peripheral devices demand the attention of microprocessor at various and predictable times

during normal program execution. The best example of the random need for attention is the use of the keyboard on a computer. Every time a key is pressed, the microprocessor must deal with an activity. Other peripheral devices such as disk drives, CRTs and printers also need to interact with the microprocessor. Just how the microprocessor accomplishes the task of working these devices is the subject of this device. 4.1 Polling Technique/approach to taking care of peripheral devices. Microprocessor checking each device in rotation at frequent intervals to see if it need service. The computer time spent in polling is largely wasted. Not efficient when the processor needs to perform other tasks. Need better system that allow processor to be free to continue normal sequential execution and only stop to deal with a peripheral when it specially needed attention. So that, interrupt system has been design to satisfy the requirement for external input control and freeing the CPU from waiting for events to occur. 4.1.1 Concept hardware interrupt INTERRUPT

1. What is interrupt? Interrupt is a call for the microprocessor to interact or service the interrupting unit. The interrupt will cause the computer to suspend the program being executed and jump into a special interrupt processing program. There are many circumstances under which it would be desirable to interrupt the normal flow of a program in the computer to react to special event. Example: User command from keyboard Command from other external input Abnormal situation power failure Execution of an illegal instruction Completion signaling of an I/O task 2. Interrupt capability lines. Allow computer to take special actions when required. Used to time-share the CPU between several different programs at once. Satisfy the requirement for external input control. Provides the desirable feature of freeing the CPU from waiting for events to occur. Provides one or more special control lines to the central processor know as interrupt

Printer

Mouse IRQ CPU IRQ

Disk Drive

IRQ

IRQ

Keyboard IRQ Interrupt ReQuest

- The messages sent to the computer on these IRQ lines also known as interrupt.

4.1.2

Interrupt service

The interrupt will cause the computer to suspend the program being executed and jump to a special interrupt processing program. Interrupt handler program action taken by the processor when an interrupt occurs. Also known as interrupt routine. When interrupt occurs, the processor will then execute the interrupt routine called for. The process of determining the appropriate course of action by the interrupt handler program (interrupt routine) is known as servicing the interrupt. There are 4 distinct steps that microprocessor takes after an interrupt. 1) The microprocessor finished the current instruction, until the end of an instruction cycle. The interrupt signal will not be acknowledge until the current instruction is carried out.

2) Normal operation is suspended. i. All the pertinent information about the program being suspended is saved/preserved in a known part of memory. Either in a special area associated with the program (process control block) or in a part of memory known as stack area. Pertinent information including: Location of the last instruction executed. Values of data in various registers that contain pieces of information relate to the algorithm being carried out when the interrupt occurred. The contents of the registers and the status of microprocessor in general must be preserved so that it can again resume operation when the interrupt has been serviced.

ii.

iii.

3) The microprocessor jumps to the location in memory where the interrupt service routine has been stored and executes the routine. The address of the routine may be fixed in the microprocessor design. 4) When interrupt routine complete its task, it would return control to the interrupted program. i. The processor returns from an interrupt. The return includes restoring the microprocessor to its exact condition before the interrupt occurred.

ii.

All registers were restored to their original values. The information they contained must be retrieved from memory and placed back in their respective registers. Finally, the program counter (PC) is loaded with retrieval address of instruction that would have been executed if an interrupt had not occurred. The original program would resume execution exactly where it left off.

iii. iv.

Figure 4.1: Servicing an interrupt

Interrupt

Normal Execution Finish Current Instruction

Suspend Operation Store registers Jump to Subroutine and Execute Return to Normal Operation Restore Microprocessor Status

Contents of registers stored in stack

Contents of registers returned from stack

Normal Execution Continues

Figure 4.2: Sequence of event during interrupt

4.1.3

Usage of interrupt

The way in which an interrupt is used depends on the nature of the device. There are several different ways in which interrupt are used: i) As an external event notifier. ii) As a completion signal. iii) As a means of allocating CPU time. iv) As an abnormal event indicator.

i)

The interrupts as an external event notifier require action. Interrupt are useful as notifiers to the CPU of external events that Frees the CPU from necessity of performing polling. Example: Keyboard input.

Figure 4.3 shows the steps in processing a keyboard input interrupt.

Figure 4.3: Using a keyboard handler interrupt

Keyboard input can be processed using a combination of programmed I/O and interrupt. Suppose a key is struck on the keyboard. This causes an interrupt to occur. The current program is suspended, and control is transferred to the keyboard interrupt handler program. The keyboard interrupt handler first inputs the character, using programmed I/O, and determines what character has been received. It would next determine if the input is one that requires special action. If so, it would perform the required action, for example, suspending the program or freezing the data on the screen. Otherwise, it would pass data to the program expecting input from that keyboard. Normally, the input character would be stored in a known memory location; ready for the program to use when it is reactivated. When the action is complete, that is, when the interrupt has been serviced, the computer normally restores the register values and returns control to the suspended program, unless the interrupt specifies a different course of action. This program would be case, for example, if the user typed a command to suspend the program being run. ii) The interrupt as a completion signal Controlling the flow of data to an output device.

Interrupt serves to notify the computer of completion of a particular course of action. Example: Printer Printer is a slow output device. The computer capable of outputting characters to the printer much faster than the printer can handle them. Interrupt can be used to control the flow of characters to the printer in an efficient way. Interrupt capability prevents the loss of output and allows the printer to control the flow of characters to a rate that printer can accept. Allows the CPU to perform other tasks while it waits for the printer to complete its printing. Figure 4.4 shows this application.

Figure 4.4: Using a print handler interrupt

The computer sends one or more characters at a time to the printer, depending on the type of printer. When the printer is ready to accept more characters, it sends an interrupt to the computer. This interrupt indicates that the printer has completed printing the characters previously received and is ready for more characters. In this case, the interrupt capability prevents the loss of output, since it allows the printer to control the flow of characters to a rate that the printer can accept. Without the interrupt capability, it would be necessary to output characters at a very slow rate to assure that the computer did not exceed the ability of the printer to accept output. The use of an interrupt also allows the CPU to perform other tasks while it wait for the printer to complete its printing. iii) The interrupt as a means of allocating CPU time Interrupt is used as a method of allocating CPU time to different programs that are sharing the CPU. The CPU can only execute one program at a time. Time share multiple programs implies that the computer system must share the CPU by allocating small segments of time to each program, in rapid rotation among them. Each program is allowed to execute some instructions. After a certain period of time, that program is interrupted and relinquishes control to a dispatcher program within the operating system (OS) that allocates the next block of time to another program. Figure 4.5 shows this application.

Figure 4.5: Using an interrupt for time sharing

The computer system provides an internal clock that sends an interrupt periodically to the CPU. The time between interrupt pulses is known as a quantum. When the interrupt clock occurs, the interrupt routine returns control to the OS. OS determines which program will receive CPU time next. This is effective method for allowing the OS to share CPU resources among several programs at once. iv) The interrupt as an abnormal event indicator Interrupt used to handle abnormal events that effect operation of the computer system. The events are directed at the problems within the computer system itself. Example: Execution of an illegal instruction. i) Divide by zero ii) Nonexistent op code iii) Hardware error detected One obvious example of an external event requiring special computer action is power failure. Most computers provide enough internal power storage to save the work that being performed and to shut down gracefully, provided that the computer has quick notification of the power failure. A power line monitor that connects to the interrupt facility provides this capability. The interrupt routine will save the status of programs that are in memory, close open files, and perform other housekeeping operations that will allow the computer to restart without loss any data. It will then halt the computer. Another important application is when a program attempt to execute an illegal instruction such as a divided by 0 or a nonexistent op code or when a hardware error is detected, such as parity error. When the error occurs it is not possible to complete the executing program. System will attempt to recover from the error and that the appropriate personnel be notified. Interrupt routine can notify the user of the error and return control of the CPU to the operating system program. You should notice that these interrupt are actually generated from inside the CPU, whereas the other interrupt that we have discussed so far are generated externally. Internal interrupts are sometimes called traps or exceptions. 4.1.4 Multiple interrupt and prioritization

There are many different input and output devices and event indicators connected to interrupt lines. Multiple interrupts will occur from time to time. Two different processing method used for determining which device initiated interrupt: i) Vectored interrupt ii) Polling Multiple interrupt can be handled by assigning priorities to each interrupt handle top priority first. A higher priority interrupt will be allowed to interrupt an interrupt of lower priority. Lower priority interrupt will have to wait until a higher priority interrupt is completed. This leads to hierarchy of interrupts, in which higher-priority interrupts can interrupt other interrupts of lower priority, back and forth, eventually returning control to the original program that was running. Figure 4.6 shows a simple example of this situation. In this figure, interrupt routine C is the highest priority, followed by B and A.

Figure 4.6: Multiple interrupts

Most computer system allows the system manager to establish priorities for various interrupt. There are three methods used to establish priorities: i) Logical way ii) Hardware or software iii) Assigning a priority number to each interrupts.

i)

Logical way Highest priority are reserved for time sensitive situation. - Power failure, external event. Lower priority usually for task completion interrupts.

ii) Hardware or software Highest priority devices are placed closest to the CPU. Connecting most critical devices to the interrupt pin with the highest priority. Used chips that perform a prioritizing function.

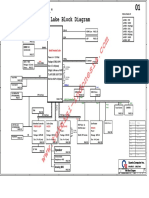

All peripheral devices are connected to the interrupt controller chip. Sends the interrupt on to the microprocessor along with the address of the interrupt routine to execute. Vectored Interrupt Address of the interrupting device is included as a part of the interrupt. When the interrupt request occurs, the microprocessor will automatically load the program counter with the assigned address. Assigned address contains the address of the routine to be executed. The interrupt will then check the assigned address to get the interrupt routine. Example: Assume that assigned interrupt address is FFFAH and FFFBH

Hex Address

Program Counter 1003 Interrupt 1 occurs

1000 1001 1002 1003 1004 2000 2001 2002

2030 FFFA 0 0 1 0 0 0 0 0 20 (Hi) FFFB 0 0 0 0 0 0 0 0 00 (Lo) FFFC FFFD FFFE Address Hex FFFF Figure 4.7(a): Program is interrupted while working at location 1003h

Program Counter The microprocessor is executing the normal program sequence.

2000

On the instruction located at 1003, interrupt 1 is received. Interrupt caused the microprocessor to check assigned address. Vectored address FFFA and FFFB contains the address of interrupt routine. Address routine, 2000h loaded into program counter address register and routine is executed.

Vectored to new location

1000 1001 1002

8

20 (Hi) 00 (Lo)

1003 1004 2000 2001 2002

2030 FFFA 0 0 1 0 0 0 0 0 FFFB 0 0 0 0 0 0 0 0 FFFC FFFD FFFE FFFF Figure 4.7(b): Vectored interrupt has sent program to execute at new location

Interrupt caused the microprocessor to check the assigned address for vector. Vectored address FFFA and FFFB contains the address of interrupt routine. Address routine, 2000h loaded into program counter address register and routine is executed.

Hex Address

Program Counter 1004

1000 1001 1002 1003 1004 2000 2001 2002

2030

RETURN

20 (Hi) FFFA 0 0 1 0 0 0 0 0 FFFB 0 0 0 0 0 0 0 0 00 (Lo) FFFC FFFD FFFE FFFF Figure 4.7(c): After the routine is finished at location 2030h, the program is returned from interrupt

At the end of subroutine, processor returns to the next sequential address in the normal routine. Types of interrupt

Interrupt can be divided into TWO categories: i) Maskable ii) Non-maskable Maskable interrupt that can be selectively disabled. - interrupt that not be accepted. Non-maskable - interrupt that never disabled. - interrupt that will always be acknowledged and accepted. - example: power failure.

Most interrupt can be temporary disable by program instruction when a program is performing a critical task that would be negatively affected if an interrupt were to occur. These interrupt can then be disabled or masked, so the microprocessor does not accept them. The various interrupts can be masked by assigning each interrupt possible a bit position in an interrupt mask register.

4.1.5 Software interrupt Behave much like hardware interrupt, except that software interrupt are written into the main program and executed in the course of sequential operation. Similar to a known fixed location. Often used to jump to other programs in memory. Software interrupt are vectored interrupt if the processor has such instruction. The instruction will send the processor to create the assigned address for vectored location of the interrupt service routine. Many interrupt use fixed locations for vector address. These locations in memory are specified by manufacturer of the microprocessor chip. Software interrupt make the interrupt routine available for use by other programs. Program can access these routine simply be executing the INT instruction with appropriate parameter. Application of software interrupt is to centralize I/O operations. - Used by each program to request I/O from the operating system software. 4.2 STACK

During an interrupt routine, some or all of the microprocessor registers may be used. This would destroy data previously in the registers if their contents were not saved in some way. Obviously, to return the microprocessor to its pre-interrupt status requires a procedure to accomplish this. What is stack? The location where the contents of the registers in the microprocessor are temporary stored.

Hardware stack A number of registers set aside within the processor to serve as the stack location. The advantage of hardware stack is rapid access and therefore, speed. But the size of the stack is limited by the number of registers that can be provided. Restrict the flexibility of a microprocessor.

10

Software stack An area in RAM for temporary storage of data and registers contents. Building this stack is an inherent part of the interrupt signal. However, stack can also be built independently of an interrupt request. In fact, stacks are used just about any time a subroutine is called. The software stack is almost unlimited in size and can reside anywhere in memory. This implementation causes the need for a special register in the microprocessor called the stack pointer register. Stack pointer Hold the address of the stack. Whenever a stack is required; the stack pointer register will track its location by holding the 16-bit stack address.

4.2.1 i)

Function of stacks interrupt, subroutine There are a lot of situations that need the used of interrupt: When a subroutine is called. - Stack is an excellent method for storing the return address and arguments for subroutine calls. When interrupt occurs. When stack instruction occurs. To store data when the most recently used data will also be the first need. Efficient way of storing intermediate data values during complex calculations. Stack operation push, pop

ii) iii) iv) v) 4.2.2

The stack address is built, one byte at a time, each entered or stacked on the last entry. It is analogous to the way plates are stack at a salad bar. Figure 4.8.

Plate stacked

Figure 4.8 (A): Stack of plate illustrating First In Concept

First plate in

Plate taken off stacked

First plate in will be last plate out

11

Figure 4.8 (B): Stack of Plate Last Out Concept

The first plate put on the stack is at the bottom. The last plate off the stack is the last plate placed of the stack. Stack operate by LIFO (Last In First Out) The last byte put on the stack will be the first byte retrieved from the stack, when an interrupt is completed, for instance. Stack instructions use assembly language mnemonics like PUSH, to push byte onto the stack and PULL or POP to take a byte off the stack. The stack builds downward. - Directions of occupied address are moving toward lower address. 4.2.3 Stack building

Most stack operations are however automatic. That is, the entire process of saving the contents of registers is done automatically whenever a subroutine call is encountered. The individual stack instructions, however do sometimes allow a choice as to which register to save. For some operations, only those register whose content is important are saving in the stack save valuable processor time. Naming the registers to be saved is accomplished within the byte following a PUSH instruction. Each bit position can be assigned to a register. If a bit is set, the register is saved. If a bit position is clear, the register is not saved.

For example, if the byte XXX10011 follow the PUSH instruction. BYTE X X

1 Flag Register Accumulator B Accumulator A

D Register PC Register

The D register, accumulator B and the flag register would be push or saved to the stack. This is because the bit corresponding to those registers is set. The others are clear, indicating that the registers they are represent will not be saved to stack. 4.2.4 Examples multiple interrupts & subroutine

Subroutine Calls A subroutine is an out-sequence part of the program that can be accessed by the jump to subroutine (JSR) or a call instruction. The call or JSR instruction always saves the contents of the program counter.

12

Figure 4.10 shows the main program loaded in memory from location 0200H to 0350H. As the program executes, it encounters a JSR instruction at location 0210H. The instruction occupies three bytes of memory, one for the instruction and two for the address of the subroutine to be executed. The next instruction that would have been executed is at location 0213H. The micro program knows that the JSR instruction requires 3 bytes and, therefore, places address 0213H on the stack. The JSR instruction then cause the program counter address register to be loaded with the address of the subroutine. The top address of the stack is F00AH and will contain the high byte 02H and F009H will contain the low byte, 13H. The microprocessor then begins executing instruction at location 1000H. At location 1015H, another subroutine is required, this time at location 2000H. The JSR instruction occupies 3 bytes as before. Again the, microprocessor places the address of the next instruction to be execute on the stack. Note that the top of the stack is now addressing F009h, where the last in address is stored. Now the microprocessor begins executing the second subroutine. If another subroutine is required, it is also possible to call it. When subroutines call on other subroutine, the programs are said to be nested. One routine is nested in another. The second routine finishes at location 2010H when the RETURN instruction is reached. The RETURN instruction does not need an address because the address to return to has stored on the stack. The return instruction POPs the address off the top of the stack and loads it into the register of program counter. JSR @ 1000 The address on the top of the stack, location F007h, is 1018H. This where the program was Main executing the first subroutine when the second call instruction was encountered. Program The first routine then continues until the RETURN instruction is found. Now the top address in the stack is 0213H. This address is loaded into the program counter register. 0213H is the address of the next instruction in the main program. Return to Main Subroutines can be called at any time and as often as needed. One subroutine can call another and this routine can call a third, etc.

0000

1 Subroutine

st

0200 0210 0211 0212 0213 0350 Jump Instruction 10 Hi Byte 00 Lo Byte Continue Main

JSR @ 2000

Return to 1st

2nd Subroutine

1000

Stack Storing Address to Return to

13

1015 1016 1017 1018 1019 102A

Jump Instruction 20 Hi Byte 00 Lo Byte Return

2000 2nd Subroutine 2010 Return

F007 F008 F009 F00A

18 Lo 10 Hi 13 Lo 02 Hi

Figure 4.10: Sequence of Events and Memory Locations

14

You might also like

- Chp6 Interrupt - StacknewDocument11 pagesChp6 Interrupt - Stacknewheyfiez12No ratings yet

- CSC159 Ch5 Interfacing and CommunicationDocument19 pagesCSC159 Ch5 Interfacing and CommunicationmaiyonisNo ratings yet

- Real Time Computing and Programming - IntroDocument19 pagesReal Time Computing and Programming - IntroNon ArtistsNo ratings yet

- Chp6 Interrupt - StackDocument12 pagesChp6 Interrupt - StackNur AfiqahNo ratings yet

- CSC 205 - 2 Instruction Processing 2023-2024Document35 pagesCSC 205 - 2 Instruction Processing 2023-2024hahnonimusNo ratings yet

- Interrupt ChapterDocument24 pagesInterrupt ChapterBTS Army 방탄소년단No ratings yet

- Top Level View of Computer Function and InterconnectionDocument38 pagesTop Level View of Computer Function and Interconnectionhsi3No ratings yet

- OS notes.docxDocument39 pagesOS notes.docxpalkisbeevi25No ratings yet

- CPU Organization ModifiedDocument68 pagesCPU Organization ModifiedAbdalrhman juberNo ratings yet

- InterruptsDocument49 pagesInterrupts1099 Pari BodanaNo ratings yet

- AyilaraDocument13 pagesAyilaraAremu FaisalNo ratings yet

- Interrupt Handling ExplainedDocument8 pagesInterrupt Handling ExplainedSreekanth PagadapalliNo ratings yet

- Lec 3 - Top View of SystemDocument11 pagesLec 3 - Top View of SystemKimani MaithyaNo ratings yet

- InterruptsDocument27 pagesInterruptsanayaNo ratings yet

- Chapter 1: Intro: 1.1 What Operating Systems DoDocument10 pagesChapter 1: Intro: 1.1 What Operating Systems DoBraiden MaggiaNo ratings yet

- Lesson6 Input and Output Devices and InterruptsDocument3 pagesLesson6 Input and Output Devices and Interruptsleonard thuoNo ratings yet

- Unit 2Document48 pagesUnit 2Rohan MehraNo ratings yet

- CSVTU Operating System Unit 1Document43 pagesCSVTU Operating System Unit 1Kapil NagwanshiNo ratings yet

- Computer Function: 1. Reading (Fetching) Instruction From Memory by CPU 2. Execution of Each Fetched InstructionDocument19 pagesComputer Function: 1. Reading (Fetching) Instruction From Memory by CPU 2. Execution of Each Fetched Instructiondomainname9No ratings yet

- Operating SystemDocument103 pagesOperating SystemYUVRAJ WAGH100% (1)

- Interrupts PDFDocument8 pagesInterrupts PDFFarhan SamsuddinNo ratings yet

- Module 1 - OSDocument79 pagesModule 1 - OSSAI PRATHEESH R JUNo ratings yet

- Operating Systems 8th Edition Cheat Sheet (Up To Chapter 6)Document5 pagesOperating Systems 8th Edition Cheat Sheet (Up To Chapter 6)Michael Beswick0% (1)

- OS Introduction - Part 2Document44 pagesOS Introduction - Part 221PC12 - GOKUL DNo ratings yet

- Operating System Module 5-Lecture 8: I/O HardwareDocument10 pagesOperating System Module 5-Lecture 8: I/O HardwareBiswas LecturesNo ratings yet

- Chapter - 1Document11 pagesChapter - 1Harshada BavaleNo ratings yet

- Interrupt vs Exception: Key DifferencesDocument12 pagesInterrupt vs Exception: Key DifferencesBAL KRISHNA PANDEYNo ratings yet

- Os Ut1 QaDocument7 pagesOs Ut1 QaVignesh RaghavareddyNo ratings yet

- Scheduling Is A Fundamental Operating System FunctionDocument6 pagesScheduling Is A Fundamental Operating System FunctionRaja RamNo ratings yet

- Lecture # 03Document18 pagesLecture # 03unzilarauf39No ratings yet

- Interrupts: For Example Let Us Take A Task That Involves Two ActivitiesDocument6 pagesInterrupts: For Example Let Us Take A Task That Involves Two ActivitiesAMAN NIKHRANo ratings yet

- Good Material OSDocument103 pagesGood Material OSKarthik SekharNo ratings yet

- Pavitran A/L Pupathe (A170632) Assignment 2: Functions of Device DriversDocument7 pagesPavitran A/L Pupathe (A170632) Assignment 2: Functions of Device DriversPavitran NeymarNo ratings yet

- EvolutionDocument8 pagesEvolutiontomasinaNo ratings yet

- Purva Gautam 20184014 CS-B: OS Assignment 1 (Theory)Document5 pagesPurva Gautam 20184014 CS-B: OS Assignment 1 (Theory)Jay ZNo ratings yet

- UntitledDocument5 pagesUntitledritikNo ratings yet

- Co Notes Module 1Document42 pagesCo Notes Module 1Vinyas M SNo ratings yet

- Unit 5 ErtosDocument28 pagesUnit 5 ErtosAbhi VarmaNo ratings yet

- OS I/O Systems OverviewDocument24 pagesOS I/O Systems OverviewKapil NagwanshiNo ratings yet

- CS 303 Chapter 1, Lecture 2Document16 pagesCS 303 Chapter 1, Lecture 2HARSH MITTALNo ratings yet

- InterruptDocument13 pagesInterruptاسيا عكاب يوسف زغير صباحيNo ratings yet

- OS Support Functions and ServicesDocument65 pagesOS Support Functions and ServicesSadiholicNo ratings yet

- CS1253 2,16marksDocument24 pagesCS1253 2,16marksRevathi RevaNo ratings yet

- STW120CT Computer Architecture and Networks: (Instruction Pipelining)Document24 pagesSTW120CT Computer Architecture and Networks: (Instruction Pipelining)BJ AcharyaNo ratings yet

- 1 OS LectureDocument33 pages1 OS LectureHabtie TesfahunNo ratings yet

- Module 3, Notes PDFDocument17 pagesModule 3, Notes PDFShankar MNo ratings yet

- OS LEcture 2Document39 pagesOS LEcture 2edwardalonzo0723No ratings yet

- Exceptional Control FlowDocument45 pagesExceptional Control Flowabdulkerimaragaw936No ratings yet

- Chapter 2Document20 pagesChapter 2esubalew sintieNo ratings yet

- Everything about Hardware and Software InterruptsDocument14 pagesEverything about Hardware and Software InterruptsC H A R A NNo ratings yet

- OS Evolution Batch ProcessingDocument20 pagesOS Evolution Batch ProcessingJeet NakraniNo ratings yet

- Unit 1Document38 pagesUnit 1Bijal patelNo ratings yet

- Lecture1 2 3Document40 pagesLecture1 2 3Prince AliNo ratings yet

- Mohamed Abdelrahman Anwar - 20011634 - Sheet 2Document15 pagesMohamed Abdelrahman Anwar - 20011634 - Sheet 2mohamed abdalrahmanNo ratings yet

- Computer System OrganizationDocument61 pagesComputer System OrganizationRonald DomingoNo ratings yet

- Unit 3Document15 pagesUnit 3SIT127- TIWARI KUNALNo ratings yet

- Operating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesFrom EverandOperating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo ratings yet

- 68000 ISA Lecture and Instruction SetDocument25 pages68000 ISA Lecture and Instruction SetFaisal MahmoodNo ratings yet

- Amoozesh Mabani PLCDocument79 pagesAmoozesh Mabani PLCحمیدرضا حاجی علیانیNo ratings yet

- Make Voice Calls with Arduino and GSM ModuleDocument14 pagesMake Voice Calls with Arduino and GSM ModuleAnil RaghuvaranNo ratings yet

- Vivo AiO V221ID - All-in-One PCs - ASUS GlobalDocument4 pagesVivo AiO V221ID - All-in-One PCs - ASUS GlobalJuan Carlos HernandezNo ratings yet

- Lsm9Ds1: iNEMO Inertial Module: 3D Accelerometer, 3D Gyroscope, 3D MagnetometerDocument72 pagesLsm9Ds1: iNEMO Inertial Module: 3D Accelerometer, 3D Gyroscope, 3D MagnetometernomansnNo ratings yet

- Assignment 10Document6 pagesAssignment 10dasari_reddyNo ratings yet

- Oracle X86 Server Installation Specialist Online Assessment (2022)Document7 pagesOracle X86 Server Installation Specialist Online Assessment (2022)uj stevNo ratings yet

- Sample Resume Skills For Computer Hardware and Networking ProfessionalDocument5 pagesSample Resume Skills For Computer Hardware and Networking ProfessionalDeena Dayalan100% (1)

- Dell Latitude 7420 14 InchDocument3 pagesDell Latitude 7420 14 InchAto AnsoriNo ratings yet

- SG TravelMate 8471 8431 200908131Document94 pagesSG TravelMate 8471 8431 200908131oralbnetworkNo ratings yet

- Abhishek ResumeDocument3 pagesAbhishek Resumesantosh_maniNo ratings yet

- Truechip AMBA 2AHB3 Verification IPDocument2 pagesTruechip AMBA 2AHB3 Verification IPNaveed BeighNo ratings yet

- 5890 X ManualDocument8 pages5890 X ManualZener Garcia CedroNo ratings yet

- 3v3 ArduinoDocument1 page3v3 ArduinoLalmuanpuiaRalteNo ratings yet

- HUAWEI Tecal E6000 ServerDocument2 pagesHUAWEI Tecal E6000 ServerEmmanuel ArenasNo ratings yet

- Elements of A Computer and Communication SystemDocument3 pagesElements of A Computer and Communication SystemArmando Mendoza JrNo ratings yet

- Computer Components and ItDocument8 pagesComputer Components and ItIzzarat AliNo ratings yet

- Computer-Basics - Computer Basics2Document43 pagesComputer-Basics - Computer Basics2api-216226726No ratings yet

- DX DiagDocument48 pagesDX DiagÁlefe TorquatoNo ratings yet

- Intel Gemini Lake Block Diagram EJ-11 ZHE 11"Document37 pagesIntel Gemini Lake Block Diagram EJ-11 ZHE 11"Tomy Aditya PratamaNo ratings yet

- b200-b210 Spec SheetDocument2 pagesb200-b210 Spec SheetHolger GäblerNo ratings yet

- Assembly and Disassembly of A Personal ComputerDocument18 pagesAssembly and Disassembly of A Personal Computerkimidors14356% (9)

- E560 CMG10 CSDocument8 pagesE560 CMG10 CSYasser RagabNo ratings yet

- ASKVideo Cubase 5 Tutorial DVDDocument6 pagesASKVideo Cubase 5 Tutorial DVDjonathan100% (1)

- Introduction To PLC: Experiment NoDocument9 pagesIntroduction To PLC: Experiment NoAkram AzharNo ratings yet

- Embedded Design TradeoffsDocument88 pagesEmbedded Design Tradeoffsabbazh rakhondeNo ratings yet

- Computer Plus CableDocument1 pageComputer Plus CableNETWORK ADMINNo ratings yet

- Technical Specifications of an Industrial DCS SystemDocument12 pagesTechnical Specifications of an Industrial DCS SystemMahesh ChaudhariNo ratings yet

- A400CG EE Trouble ShootingDocument40 pagesA400CG EE Trouble ShootingFreddy ArmstrongNo ratings yet

- RTC-based digital calendar in 40 charactersDocument6 pagesRTC-based digital calendar in 40 charactersSalman HaiderNo ratings yet