Professional Documents

Culture Documents

(EN208) Technologie Des Circuits Num Riques - Corrig - 2008

Uploaded by

May MayoutaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

(EN208) Technologie Des Circuits Num Riques - Corrig - 2008

Uploaded by

May MayoutaCopyright:

Available Formats

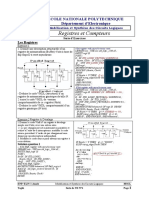

ENSEIRB E2 Janvier 2008 - SR Correction Examen TCIN (avec documents)

Partie II TCIN - (20 points) Un composant compteur doit tre implant sur circuit intgr. Ses spcifications fonctionnelles sont les suivantes : il compte sur front montant de son horloge CLK, de 0 9. Le bus de sortie sur 4 bits volue donc de 0000 1001 . Un signal RESET, actif niveau bas, effectue de manire asynchrone la remise 0 du compteur. Un signal ENABLE, actif niveau haut, autorise le comptage, qui est donc inhib lorsque ENABLE est niveau bas. Un signal OVERFLOW synchrone, actif 1, signale le passage de 1001 0000 . 1) La premire solution dimplantation est un FPGA. Quel est le nombre approximatif de CLB qui seront utiliss par le composant compteur ? Un compteur 4 bits utilise 4 bascules et un peu de logique. Il faut ajouter une bascule par signal de contrle. Sur in Xilinx, un CLB contient 4 slices donc 8 bascules. Le compteur utilisera entre 1 et 2 CLB, selon que des bascules seront reportes ou non sur des IOBs. Pourquoi la solution dimplantation sur FPGA est-elle gnralement la premire envisage ? Dveloppement rapide et peu couteux, permet de vrifier le fonctionnalits Au vu des technologies classiquement utilises pour les FPGA, donnez en le justifiant un ordre de grandeur le la frquence maximale dutilisation de compteur . Un FPGA standard fonctionne avec une CLK max entre 200 MHz et 1 GHz. En incluant le retards de la partie combinatoire (LUT) du compteur, on atteindra de 100 300 Mhz. 2) La deuxime solution est limplantation de compteur sur un ASIC du fabricant MIETEC. Vous disposez pour cela de la bibliothque de cellules numriques MIETEC_Cadence, et de loutil de CAO Cadence. Quels sont pour vous les 3 principaux avantages et 3 principaux inconvnients de cette solution dimplantation par rapport la solution du 1) ? Avantages de la solution ASIC : 1) optimisation de lintgration silicium (seulement les fonctions utiles sont implantes) donc meilleures performances; 2) cot de fabrication faible pour des grandes quantits ; 3) Suit lvolution des technologies de fabrication (indpendamment des fabricants de FPGA). Inconvnients de la solution ASIC : 1) temps de dveloppement ; 2) prototypes non modifiables ; 3) conception bas niveau (comptences microlectronique) 3) Le fabricant MIETEC propose des technologies de fabrication CMOS, SiGe et BiCMOS. Lequel de ces 3 types de technologies choisirez-vous pour le compteur ? Justifiez votre rponse en classant ces technologies selon les 5 critres les plus pertinents pour votre composant. Densit dintgration : 1) CMOS ; 2) BiCMOS ; 3) SiGe Consommation: 1) CMOS ; 2) BiCMOS ; 3) SiGe Rapidit : 1) SiGe; 2) BiCMOS ; 3) CMOS Cot : 1) CMOS ; 2) BiCMOS ; 3) SiGe Marge de bruit : 1) CMOS ; 2) BiCMOS ; 3) SiGe

Choix : CMOS sauf si contrainte de rapidit ( partir de 1 GHz) 4) Afin de rendre votre composant testable aprs sa fabrication, il vous est demand de remplacer les bascules D du compteur par des bascules D scan. Donner la description VHDL dune bascule D scan, en prcisant le nom et la fonction des signaux dentre/sortie supplmentaire dune bascule D scan. Description VHDL : idem bascule D avec entres Sin (scan in) et SC (scan control) en plus ; lorsque SC est activ, la sortie Q recopie Sin au lieu de D. dans le process : Wait until CLKevent and CLK=1 ; If SC=1 then Q<=Sin Else Q<= D ; End if ; 5) Expliquez lutilisation et lagencement des bascules D scan pour le test du composant compteur. Quels seront les signaux dentre/sortie supplmentaires pour compteur et comment seront-ils utiliss ? Les bascules D scan remplacent les bascules D du compteur sur les 4 bits de comptage. Les 4 bascules sont connectes en srie pour le mode scan (entres Sin sont connectes sur les sorties Q). Lorsque SC est activ 1, les bascules fonctionnent en registre dcalage et font circuler les donnes de test. Lorsque SC est 0, le compteur fonctionne normalement. 6) Pour fabriquer lASIC compteur, vous devrez fournir MIETEC ses vecteurs de test. Dessinez les chronogrammes des signaux dentre du composant compteur (y compris les signaux de test) vous permettant dobtenir une couverture de test de 100% sur un nombre minimal de priodes dhorloges. Quel est ce nombre ? Dans les chronogrammes : RESET 0, puis 1, puis 0. ENABLE 0 puis 1. Circuit en mode normal (SC =0) puis test (SC=1). Appliquer 0 sur SIN, puis 1 (afin de faire circuler un 0 puis un 1 dans les bascules du compteur connectes en srie en mode test). Finir par un RESET. Environ 10 priodes dhorloge. 7) Votre client vous demande de fournir le composant compteur avec le test intgr sur puce (BIST). Votre choix est de stocker les vecteurs de test (1 vecteur = 1 donne de N bits) sur un module EEPROM intgr sur la puce. Expliquez qualitativement le fonctionnement du BIST dans ce cas-l. Selon les chronogrammes de la question 6, il y aura un vecteur de test par front dhorloge (1 vecteur de test = liste des bits des entres appliques). Ces donnes seront stockes sur lEEPROM par mots de 4 bits dentre (RESET, OVERFLOW, SC, SIN) + 5 bits de sortie (DOUT/4bits, OVERFLOW). A chaque front dhorloge lorsque le BIST sera active, ladresse de lecture de lEEPROM sera incrmente et les 4 premiers bits du vecteur de test appliqu sur les entres du compteur. Les sorties du compteur seront compares bit par bit aux 5 bits restant du vecteur de test. Sil il y a une diffrence, un drapeau (FLAG) sera activ en sortie du BIST 8) Dessinez le schma lectrique ( base de transistors NMOS) des cellules mmoires de lEEPROM contenant les 2 premiers vecteurs (N bits) de votre protocole de test dfini en 6). Comment effectuerez-vous la programmation de lEEPROM ? Voir le TD sur les EEPROM. Ici, la taille des mots stocks est de 9 bits selon la question 7. 9) Quelle alternative pouvez-vous proposer la solution EEPROM pour le BIST ?

Lunique alternative est de synthtiser un circuit squentiel synchrone de CLK ( base de bascules et de portes logiques) qui gnre sur 9 sorties les vecteurs de test demands. Il est probable que la surface silicium consomme sera plus importante, mais il ny aura pas les contraintes du protocole de programmation de lEEPROM, qui oblige utiliser une technologie spcifique.

VHDL TCIN : Question Bonus Que dduisez-vous en comparant vos rponses aux questions I-6) et II-6) ? Le test en utilisant des bascules SCAN est plus court (nombre infrieur de priodes dhorloge). Essentiellement parce que les bascules SCAN sont connectes en srie en mode SCAN, et donc pour faire commuter le poids fort du compteur il suffit de 4 priodes dhorloge. Limplantation de SCAN sur un circuit est donc coteuse en silicium, mais facilite le test industriel des puces.

You might also like

- Groupe 12 Exposé Logique SéquentielDocument18 pagesGroupe 12 Exposé Logique Séquentieledi adjaroNo ratings yet

- Cour PDF Comptage GratuitDocument9 pagesCour PDF Comptage GratuitValisoa AndriamifidyNo ratings yet

- Monographie FP ELNDocument9 pagesMonographie FP ELNHanane GherramNo ratings yet

- Serie TD4 BisDocument7 pagesSerie TD4 BisSarah NourNo ratings yet

- Cours Sur Les Bascules PDFDocument4 pagesCours Sur Les Bascules PDFAmineAb100% (1)

- Circuits Logiques Séquentiels - LicDocument25 pagesCircuits Logiques Séquentiels - LicHoucem B HsnNo ratings yet

- TD3 - Oscillateurs: A - Travaux DirigésDocument3 pagesTD3 - Oscillateurs: A - Travaux DirigésDavid VHOUMBYNo ratings yet

- TD 03 CorrigeDocument14 pagesTD 03 CorrigerabehNo ratings yet

- Bts TRfiltrageDocument14 pagesBts TRfiltrageamidi5555913No ratings yet

- 2012 2013 ExamenDocument4 pages2012 2013 ExamenFadelNo ratings yet

- Elect 4Document3 pagesElect 4Mario DelviraNo ratings yet

- Chap 4Document51 pagesChap 4MERYEM LAHBOUBNo ratings yet

- EI21 - Corrigé TD1 - Les Amplificateurs Opérationnels LinéairesDocument4 pagesEI21 - Corrigé TD1 - Les Amplificateurs Opérationnels LinéairesAla MassoudiNo ratings yet

- Devoir 1Document2 pagesDevoir 1Majid Nait LyasseNo ratings yet

- EXAOLinDocument7 pagesEXAOLinmed100% (2)

- Exercices de CompteursDocument22 pagesExercices de CompteursRad PAMBUNo ratings yet

- LES CIRCUITS LOGIQUE ProgrammableDocument71 pagesLES CIRCUITS LOGIQUE ProgrammableAhmed DoghmiNo ratings yet

- TPDocument12 pagesTPAhmed AttaouiNo ratings yet

- Solution Exercices de Preparation ELNDocument7 pagesSolution Exercices de Preparation ELNhouda bensalahNo ratings yet

- P514 P523 Corrige td3 Fste ElhanaouiDocument12 pagesP514 P523 Corrige td3 Fste ElhanaouiZaza RatsiNo ratings yet

- Présentation de La Plateforme NI-ELEVIS II+Document15 pagesPrésentation de La Plateforme NI-ELEVIS II+Hamza HachimNo ratings yet

- Cahier TP en Ensip 2aDocument25 pagesCahier TP en Ensip 2aN'GOLO MAMADOU KONENo ratings yet

- MASTER - I - ESE13 - CAPTEURS INTELLIGENTS - COURS - N1 - INTRODUCTION GENERALE AUX CAPTEURS-convertiDocument45 pagesMASTER - I - ESE13 - CAPTEURS INTELLIGENTS - COURS - N1 - INTRODUCTION GENERALE AUX CAPTEURS-convertiDora DouaaNo ratings yet

- Compte UrsDocument11 pagesCompte Ursmaiga mohamedNo ratings yet

- C4 CombinatoireDocument76 pagesC4 CombinatoireMøzm FLNo ratings yet

- Chapitre 3 Amplificateur Différentiel PDFDocument29 pagesChapitre 3 Amplificateur Différentiel PDFmed50% (2)

- Regitre - Dec Ex TpfpgaDocument8 pagesRegitre - Dec Ex TpfpgaZenache AhlemNo ratings yet

- TD2 LP Semestre5Document7 pagesTD2 LP Semestre5Fatima AoujilNo ratings yet

- Circuit Electrique Et Electronique WWW Cours-Electromecanique ComDocument74 pagesCircuit Electrique Et Electronique WWW Cours-Electromecanique ComCheikh Brahim Elkhadar100% (1)

- Electronique 2Document4 pagesElectronique 2Zain GaradiNo ratings yet