Professional Documents

Culture Documents

Electrical, Digital and Industrial Circuits: IT IL Ic

Uploaded by

NGOUNEOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrical, Digital and Industrial Circuits: IT IL Ic

Uploaded by

NGOUNECopyright:

Available Formats

REPUBLIC OF CAMEROON Peace Work Fatherland GTHS KUMBO/ ELECT DPT

MOCK EXAMINATIONS 2011 Series: F3 Option: Electrotechnology Duration: 4H Coefficient: 4

ELECTRICAL, DIGITAL AND INDUSTRIAL CIRCUITS

No document is allowed except the one given to the candidates by the examiners Parts of the paper: 03 Number of pages: 04 I TECHNOLOGY

1.1 Describe the functioning principle of a thyristor. 1.2 Give the difference between a diode and a thyristor. 1.3 On the same axis, sketch the forward and the reverse characteristic of a Zener diode. 1.4 Give an example of a passive and active element (component). 1.5 How many flip-flops are necessary to realise an asynchronous counter needed to count 60 seconds of a clock. 1.6 Give the difference between synchronous counter and asynchronous counter. 1.7 Give the meaning of the following abbreviations used in electronic field and precise the normalised supplying voltage for each of them: TTL, CMOS. 1.8 Show with the aid of a diagram how a D flip-flop can be obtained from RS and JK flip-flops.

II

IT

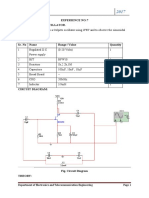

ANALOGIC CIRCUITS Study of a voltage regulation

R

Exercise 1:

R = 200 ; RL = 150 .

IZ Ic

DZ T

IL

RL

For the transistor: = 50 ; VBE = 0.6V.

Vo

Vi 26V

For the Zener diode, Vz = 10V. 1.1 Explain the operation of the circuit. 1.2 Calculate: a) The output voltage Vo. b) The currents IL, IT and IZ.

Figure 1

c) The maximum power dissipated in the transistor.

GTHS KUMBO-MOCK Examinations-Electrical, Digital and Industrial Circuits- 2011 Session..

Exercise 2:

Bipolar junction transistor

Vcc

This circuit has the following characteristics: R1 = 1k ; RE = 100 ; UZ = 6.6V;

=100;

I1

R1

RC

VBE = 0.6V; Vcc = 24 V and VCESat = 0.3V. 2.1 Find the current I1 in R1 and the power dissipated in R1. 2.2 Calculate the current IE in RE. 2.3 Calculate the current IC in RC. 2.4 Calculate the power that the transistor and the Zener diode should be able to dissipate.

C B E

DZ

VCE IE

RE

M Figure 2

Exercise 3:

AC circuit

A

The circuit of figure 3 has the following characteristics: C = 50 F , L = 12.8mH,

K

Z

e(t ) = 120 2 cos(100t ) .

3.1 Calculate the Thevenins parameters at the points A and B.

e B Figure 3

3.2 Deduce the Norton module. 3.3 Calculate the current across Z when K is closed knowing that Z = 5 + 4j Using Millman and voltage divider theorem (Figure 4): 4.1 Determine the voltage at the points

5R

Exercise 4:

V1

Operational amplifier.

C

R R

A, B, E and F. 4.2 Determine: a) The voltage V1 as function of VC

VS

A

R

B

5R

and V2. b) The voltage V2 as function of VD and V1

F

R

D V2

c) The voltage VS as function of VD and VC d) Deduce the voltage VS as a function of V1 and V2.

Figure 4

GTHS KUMBO-MOCK Examinations-Electrical, Digital and Industrial Circuits- 2011 Session..

III

DIGITAL CIRCUITS Study of a seven segments display.

Exercise 1:

The circuit below is used to display the first 8 symbols of the digital system of numeration. The system is composed of: A modulo 8 JK flip flop asynchronous binary counter; A 3/7 (3 inputs and 7 outputs) decoder; A seven segments display used to display used to display the first 8 symbols as shown below.

01234567

a a b c d e f g

Q3 COUNTER Q2 Q1

f g

e d

3/7 Decoder

Display

a, b, c, d, e, f, g are the seven segments of the display. Q3, Q2 and Q1 are the outputs of the asynchronous counter (Q3 is the most significant bit while Q1 is the least significant bit). 1. Draw the truth table of the JK flip flop. 2. Draw the complete electric diagram of the asynchronous counter using the JK flip flops. 3. Draw the truth table of the decoder following the model given below. Q3 0 0 Inputs Q2 0 0 Q1 0 1 a 1 b 1 c 1 Outputs d 1 Display e 1 f 1 g 0 0 1

4. Using the Karnaughs map, give the simplified logic expression of each output of the decoder. 5. Draw the logigram of the display 0 using NAND gates of two inputs, taking Q1, Q2 and Q3 as inputs variables.

GTHS KUMBO-MOCK Examinations-Electrical, Digital and Industrial Circuits- 2011 Session..

Exercise 2:

Study of a JK flip-flop

According to the JK flip-flop truth table established in the previous exercise, complete the following chronogram. Initially, Q = 0.

Clk

t J 1 0 K 1 0 Q t t

Exercise 3: Counter The circuit of the figure 5 below represents a counter. The flip-flops are positive edge triggered.

D H

Q3

D H

Q2

D H

Q1

D H

Q0

/Q3 Clock

/Q2

/Q1

/Q0

Figure 1. Figure 5 1. Precise the nature of this counter (synchronous or asynchronous). 2. State the difference between series transfer and parallel transfer. 3. Draw the wave forms of Q3, Q2, Q1, Q0 knowing the initial state Q3 = 1, Q2 = Q1= Q0 = 0.

Subject Masters: Mr. ETCHU; Mr. NGOUNE, Electrical Department, GTHS Kumbo.

GTHS KUMBO-MOCK Examinations-Electrical, Digital and Industrial Circuits- 2011 Session..

You might also like

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Electrical, Digital and Industrial Circuits: Second Sequence ExamDocument4 pagesElectrical, Digital and Industrial Circuits: Second Sequence ExamNGOUNENo ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Digi Anal5Document4 pagesDigi Anal5NGOUNENo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Courses in Electrical Engineering: Digital Electronics First Sequence Exam With SolutionDocument9 pagesCourses in Electrical Engineering: Digital Electronics First Sequence Exam With SolutionNGOUNENo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Ec 303Document2 pagesEc 303jeetendrasidhiNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Universiti Teknologi Mara Final Examination: Confidential EE/OCT 2008/KJE609/ECE590/KJE416Document9 pagesUniversiti Teknologi Mara Final Examination: Confidential EE/OCT 2008/KJE609/ECE590/KJE416nazhakimNo ratings yet

- Electronics Explained: Fundamentals for Engineers, Technicians, and MakersFrom EverandElectronics Explained: Fundamentals for Engineers, Technicians, and MakersRating: 5 out of 5 stars5/5 (5)

- BEE (Electronics) Assignment 2 QPDocument1 pageBEE (Electronics) Assignment 2 QPbala krishnaNo ratings yet

- Final Fall 2020Document2 pagesFinal Fall 2020Zeyad AymanNo ratings yet

- Final Fall 2020Document2 pagesFinal Fall 2020Zeyad AymanNo ratings yet

- Lesson 1 - ECG Theory - SimulationDocument10 pagesLesson 1 - ECG Theory - SimulationThanh TúNo ratings yet

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Document3 pagesFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8No ratings yet

- Research Inventy: International Journal of Engineering and ScienceDocument8 pagesResearch Inventy: International Journal of Engineering and ScienceinventyNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- Sura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkDocument2 pagesSura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkSaurabh SinghNo ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- Electronics: June/July, 2010Document7 pagesElectronics: June/July, 2010Prasad C MNo ratings yet

- Introduction To Logic Design Experiments 1 Thru 10Document36 pagesIntroduction To Logic Design Experiments 1 Thru 10George Kokkinias100% (1)

- ENEL2EEH1 - Electrical & Electronic EngineeringDocument7 pagesENEL2EEH1 - Electrical & Electronic EngineeringqanaqNo ratings yet

- Ic Lab AllDocument45 pagesIc Lab AllRaghu KasulaNo ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- Ect301 Linear Integrated Circuits, December 2021Document4 pagesEct301 Linear Integrated Circuits, December 2021Dinil DhananjayanNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat No58 EX Ramawat PankajNo ratings yet

- B. Tech: Roll NoDocument5 pagesB. Tech: Roll NoRavindra KumarNo ratings yet

- Univ Question Paper LICDocument8 pagesUniv Question Paper LICVishnu Priya A KNo ratings yet

- MQP Electronics Physics Pep TalkDocument5 pagesMQP Electronics Physics Pep TalkGundu RekhaNo ratings yet

- Timing Circuits Using Timer Ic 555 ProblemDocument7 pagesTiming Circuits Using Timer Ic 555 ProblemDevi Sree JeevanandhamNo ratings yet

- MODEL-dlc Eeee RmkcetDocument2 pagesMODEL-dlc Eeee RmkcetreporterrajiniNo ratings yet

- Ee2255 Digital Logic CircuitsDocument3 pagesEe2255 Digital Logic CircuitsecessecNo ratings yet

- 06CS32 May - June 2010Document2 pages06CS32 May - June 2010Rafael BarriosNo ratings yet

- Date Session Subject IC's & Instrumentation Clas S SectionDocument3 pagesDate Session Subject IC's & Instrumentation Clas S Sectionselva33No ratings yet

- Activity 3B Impedance of RC Circuits: Parallel RC Circuits 3B.1 Program Outcomes (Pos) Addressed by The ActivityDocument8 pagesActivity 3B Impedance of RC Circuits: Parallel RC Circuits 3B.1 Program Outcomes (Pos) Addressed by The ActivityNicoNo ratings yet

- Lab D4 CounterDocument8 pagesLab D4 Counterdhanabadee.kNo ratings yet

- ET1310 Lab 2.1 LabReportHandout OLDocument8 pagesET1310 Lab 2.1 LabReportHandout OLIreri MwanikiNo ratings yet

- Logic Lab 1 - Digital Abstraction (5 Gates)Document16 pagesLogic Lab 1 - Digital Abstraction (5 Gates)ram010No ratings yet

- EE803ElectronicInstrumentation April2010Document1 pageEE803ElectronicInstrumentation April2010Anith KrishnanNo ratings yet

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocument15 pagesUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanNo ratings yet

- EEC501Document2 pagesEEC501raviNo ratings yet

- Frequency Dividers: Device Modelling Mini-ProjectDocument24 pagesFrequency Dividers: Device Modelling Mini-Projectjoshuacool4No ratings yet

- Lab Manual ElectronicsDocument57 pagesLab Manual ElectronicsNaveen Rockzz Bhavans100% (2)

- 9A04604 Electronic Measurements and InstrumentationDocument4 pages9A04604 Electronic Measurements and InstrumentationsivabharathamurthyNo ratings yet

- Lab 3 Clipping and Clamping Circuits 2 1112Document10 pagesLab 3 Clipping and Clamping Circuits 2 1112Mei GuanNo ratings yet

- 09 - Logic CircuitsDocument5 pages09 - Logic CircuitsStaś DutkiewiczNo ratings yet

- Electronic Assignment QuestionsDocument6 pagesElectronic Assignment QuestionsCalculus Chong Wei ChoonNo ratings yet

- Lab 1: Introduction To Combinational Design: EquipmentsDocument42 pagesLab 1: Introduction To Combinational Design: EquipmentsnarpatzaNo ratings yet

- Exp 3Document5 pagesExp 3MariaNo ratings yet

- Lab 8 Synchronous Sequential CircuitsDocument9 pagesLab 8 Synchronous Sequential Circuitsapi-385689610No ratings yet

- Project ReportDocument36 pagesProject ReportThanh TúNo ratings yet

- Colpitts OscillatorDocument3 pagesColpitts OscillatorSakshi GosaviNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- EEE312 EEE282 Lab4 Spring2015 PDFDocument5 pagesEEE312 EEE282 Lab4 Spring2015 PDFvognarNo ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- Activity 3Document11 pagesActivity 3Peter AndrewNo ratings yet

- Elect2 2014Document2 pagesElect2 2014NGOUNENo ratings yet

- Electrical, Digital and Industrial Circuits: First Sequence TestDocument2 pagesElectrical, Digital and Industrial Circuits: First Sequence TestNGOUNENo ratings yet

- Power Electronics: Fourth Sequence TestDocument2 pagesPower Electronics: Fourth Sequence TestNGOUNENo ratings yet

- Electrical, Digital and Industrial Circuits: Second Sequence TestDocument4 pagesElectrical, Digital and Industrial Circuits: Second Sequence TestNGOUNENo ratings yet

- Power Electronics: First Sequence TestDocument2 pagesPower Electronics: First Sequence TestNGOUNENo ratings yet

- CV 2013 NgouneDocument4 pagesCV 2013 NgouneNGOUNENo ratings yet

- Electrical Installations: Theme: Electrical Installation of A WorkshopDocument2 pagesElectrical Installations: Theme: Electrical Installation of A WorkshopNGOUNENo ratings yet

- Electrical TechnologyDocument2 pagesElectrical TechnologyNGOUNENo ratings yet

- Machine Lesson Final1Document94 pagesMachine Lesson Final1anon_156286001100% (8)

- First Sequence Test in Digital and Analog ElectronicsDocument4 pagesFirst Sequence Test in Digital and Analog ElectronicsNGOUNENo ratings yet

- Power Elect1 2012Document3 pagesPower Elect1 2012NGOUNENo ratings yet

- First Sequence Test in Digital and Analog ElectronicsDocument4 pagesFirst Sequence Test in Digital and Analog ElectronicsNGOUNENo ratings yet

- Power Elect Total 2012Document34 pagesPower Elect Total 2012NGOUNENo ratings yet

- Elect Machine Total 2012Document22 pagesElect Machine Total 2012NGOUNENo ratings yet

- Electrical Machines 5Document3 pagesElectrical Machines 5NGOUNENo ratings yet

- Digi-Ana Total 2012Document46 pagesDigi-Ana Total 2012NGOUNENo ratings yet

- Electrical Tech Total 2012Document24 pagesElectrical Tech Total 2012NGOUNENo ratings yet

- Elect Machine Total 2012Document22 pagesElect Machine Total 2012NGOUNENo ratings yet

- Digi-Anal3 CorrectpubDocument17 pagesDigi-Anal3 CorrectpubNGOUNENo ratings yet

- Atomation - CI6/ Mock 2012 GTHS KUMBODocument4 pagesAtomation - CI6/ Mock 2012 GTHS KUMBONGOUNENo ratings yet

- Electrical Machines 5Document3 pagesElectrical Machines 5NGOUNENo ratings yet

- Power Electronics MockDocument4 pagesPower Electronics MockNGOUNENo ratings yet

- Electrical Machines MockDocument3 pagesElectrical Machines MockNGOUNENo ratings yet

- Mock Ion 2012 BonDocument6 pagesMock Ion 2012 Bonanon_819404681No ratings yet

- Electrical Machines 3 Correct PubDocument10 pagesElectrical Machines 3 Correct PubNGOUNENo ratings yet

- Drawing and Technnology - MockDocument3 pagesDrawing and Technnology - MockNGOUNENo ratings yet

- Electrical Technology MockDocument3 pagesElectrical Technology MockNGOUNENo ratings yet

- Power Electronics MockDocument4 pagesPower Electronics MockNGOUNENo ratings yet

- Automation 3Document3 pagesAutomation 3NGOUNENo ratings yet

- Digital Electronics: Question and Answers (Question Bank)Document12 pagesDigital Electronics: Question and Answers (Question Bank)api-297153951100% (1)

- Lec 3 - Module 3Document37 pagesLec 3 - Module 3vopoc21212No ratings yet

- Bus Serial EEPROMDocument12 pagesBus Serial EEPROMMatiasNo ratings yet

- 2.1 Timing Paths (STA) Basic (Part 1)Document14 pages2.1 Timing Paths (STA) Basic (Part 1)Sudheer GangisettyNo ratings yet

- Lecture Slides Week 14Document21 pagesLecture Slides Week 14ghd hfgsd hgfsNo ratings yet

- FT3000-Configuration - A7 (2) PT AIPEDocument20 pagesFT3000-Configuration - A7 (2) PT AIPEArik Prasetyo UtomoNo ratings yet

- Fastest Finger Press Quiz Buzzer: Block DiagramDocument1 pageFastest Finger Press Quiz Buzzer: Block DiagramShreerama Samartha G BhattaNo ratings yet

- P3 - 19 - Boolean Algebra and Logic CircuitsDocument27 pagesP3 - 19 - Boolean Algebra and Logic CircuitsDhruv SNo ratings yet

- NA016 Manual 08 2010 PDFDocument68 pagesNA016 Manual 08 2010 PDFMarian AriciucNo ratings yet

- JOELDocument20 pagesJOELArun KumarNo ratings yet

- Service Manual: This Document Is Printed On Chlorine Free (ECF) Paper With Soy InkDocument106 pagesService Manual: This Document Is Printed On Chlorine Free (ECF) Paper With Soy InkManuel Gomez MerquezNo ratings yet

- Applications of Flip FlopsDocument2 pagesApplications of Flip FlopsThomas JinduNo ratings yet

- DLD Chapter 6 Shifte Registers and CountersDocument82 pagesDLD Chapter 6 Shifte Registers and CountersLalisa RegassaNo ratings yet

- 22323-2019-Winter-Model-Answer-Paper (Msbte Study Resources)Document21 pages22323-2019-Winter-Model-Answer-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- VHDL - 1100 Sequence Detector - Electrical Engineering Stack ExchangeDocument3 pagesVHDL - 1100 Sequence Detector - Electrical Engineering Stack ExchangeMaddy TrichyNo ratings yet

- End-SemEC101 22Document4 pagesEnd-SemEC101 22PLAY LYRICSNo ratings yet

- 8051Document72 pages8051Arjun Aj100% (1)

- STR G 6653Document8 pagesSTR G 6653Saif RehmanNo ratings yet

- Clock DistributionDocument52 pagesClock Distributiontejanossam100% (1)

- Flip Flops, R-S, J-K, Clocked R - DAEnotesDocument9 pagesFlip Flops, R-S, J-K, Clocked R - DAEnotesHarsh Vardhan JhaNo ratings yet

- K32-Process Manual (Rev 000) TYPICAL ONLYDocument79 pagesK32-Process Manual (Rev 000) TYPICAL ONLYKobus MoolmanNo ratings yet

- EECS 151/251A Fall 2017 Digital Design and Integrated CircuitsDocument45 pagesEECS 151/251A Fall 2017 Digital Design and Integrated CircuitsindranilhNo ratings yet

- 8086 FullDocument72 pages8086 FullNandhini Nachiyar100% (4)

- 1MRK506267-WEN C en REL670 Setting Example 1Document42 pages1MRK506267-WEN C en REL670 Setting Example 1john82% (17)

- Questions From 10 Question Papers: Module 1: Number Systems and CodesDocument4 pagesQuestions From 10 Question Papers: Module 1: Number Systems and Codesvidhya seemanNo ratings yet

- ST7712 DatasheetDocument113 pagesST7712 DatasheetSpecShareNo ratings yet

- Dynamic Speed GovernorDocument18 pagesDynamic Speed GovernorSaroj Kumar33% (3)

- Connect. 611U To The CPUDocument68 pagesConnect. 611U To The CPUVladimirAgeevNo ratings yet

- Experiment-11: Chalamala Sujith Reddy 19CS01009Document8 pagesExperiment-11: Chalamala Sujith Reddy 19CS01009Sujith ReddyNo ratings yet

- Instruction Manual: BE1-951 Overcurrent Protection System Distributed Network Protocol (DNP V3.00)Document32 pagesInstruction Manual: BE1-951 Overcurrent Protection System Distributed Network Protocol (DNP V3.00)govindarulNo ratings yet