Professional Documents

Culture Documents

Electrónica Digital - Manual de Prácticas

Uploaded by

SrebritoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrónica Digital - Manual de Prácticas

Uploaded by

SrebritoCopyright:

Available Formats

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Manual de Prcticas

1. Introduccin. Divisin de las prcticas.

Debido al nmero limitado de elementos de laboratorio, las prcticas sern realizadas en grupos de dos personas como mximo, segn el nmero de alumnos asignados. La realizacin de las prcticas (salvo que se indique lo contrario) se dividirn en tres partes, todas ellas incluidas como puntos diferentes en el enunciado: En primer lugar se debe realizar un estudio terico del problema propuesto. Este estudio deber ser realizado antes de llegar a la sesin de prcticas, y tiene como nalidad evitar posibles errores en la realizacin mediante la comparacin de resultados. En segundo lugar se realizar una simulacin de los circuitos referentes a la prctica en cuestin. sta consistir en la creacin de un modelo en el lenguaje VHDL, a partir se obtendr el comportamiento de los circuitos. En tercer lugar, y una vez realizada la simulacin, pasaremos a la emulacin de los circuitos. La emulacin consistir en el montaje de los circuitos en el panel de entrenamiento con los integrados disponibles en el laboratorio. A continuacin se dar una lista de stos con sus principales caractersticas. Por cada prctica habr que entregar una memoria de su realizacin, en la que se deber incluir las respuestas a las preguntas del enunciado y las tres partes mencionadas anteriormente. Las tres partes en las que se divide la prctica (teora, simulacin y emulacin o montaje) deben tener el mismo resultado; si lo anterior no se cumple, la prctica estar mal realizada y por lo tanto estar suspensa a menos que se indiquen unos motivos razonables para dicha contradiccin.

2. Realizacin de un prctica

A continuacin vamos a resaltar las principales caractersticas de los diferentes apartados de las memorias de la prctica. La secuencia de realizacin de la prctica, y por tanto de la memoria debe ser la mostrada a continuacin. Este hecho es debido a que la probabilidad de fallo en la realizacin de la prctica va aumentando (por la novedad de los dos ltimos apartados), y as una posible discordancia ser debido con una mayor probabilidad al apratado que se est realizando.

2.1. Estudio terico del problema.

Previamente a la asistencia a la sesin de prcticas, se debe realizar el estudio terico del problema propuesto. Este estudio ser tratado como un problema de clase (aumentando de esta forma la lista de problemas propuestos). As mismo deber estar bien estructurado y ser lo suficientemente comprensible para no llevar a equvocos. A la hora de realizar las comparaciones con los resultados de la simulacin y de la emu-

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

lacin, el estudio terico no debe quedarse en obtener una frmula lgica, sino que se deber llegar a una tabla de combinaciones y/o a un cronograma en el que aparezcan todas las seales visibles del problema. Un cronograma no es ms que un esquema en el que se observa el comportamiento de las seales en funcin del tiempo, como el que se puede observar a continuacin. Las transiciones pueden ser ideales (perpendiculares) y siempre conviene retrasar algo las seales de salida con respecto a las transiciones de las seales de entradas que provocan el cambio (ya que estos retrasos provocan una serie de comportamientos que no son observados cuando el cambio es simultneo).Realmente, la nica funcionalidad aadida del cronograma es la inclusin de la dependencia temporal, pero el resto de informacin es la misma que una tabla de combinaciones, y por tanto son equivalentes. Para pasar de un cronograma a una tabla de combinaciones, solamente hay que tomar los valores de las diferentes seales para el mismo intervalo temporal, como se aprecia en la gura

X F tiempo

X 0 1 1 0 0 1 1

Y 1 1 0 0 1 1 0

En el caso de pasar una tabla de combinaciones a un cronograma, el modo de operar es el mismo salvo que no disponemos de la informacin temporal, por lo que impondremos a todas las combinaciones el mismo retraso (el que consideremos oportuno para una mejor visualizacin de las formas de onda). De nuevo, hay que ser muy cuidadoso con la resolucin del estudio terico (tanto en la obtencin de la tabla de combinaciones como en el cronograma) ya que las conclusiones que obtengamos nos servirn para la posterior comparacin con los restantes apartados de la memoria. Este hecho nos servir para evitar posibles equivocaciones en las comparaciones y/o tener justicaciones para posibles discrepancias entre los diferentes apartados.

2.2. Simulacin.

Una vez que se haya realizado el estudio terico del problema, llevaremos a cabo el proceso de simulacin para comprobar la correcta realizacin del estudio terico. Para ello, utilizaremos la simulaciones utilizando un simulador que entiende el lenguaje VHDL. Este simulador es la versin de demostracin del simulador GMVHDL de la empresa Green Mountain

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Computing Inc. (http://www.gmvhdl.com). La versin de evaluacin utilizada se puede encontrar en la siguiente direccin de internet: ftp://ftp.rediris.es/software/msdos/electrcl/ gmvhdl14.zip, al que convendra aadir el chero de ujo sim.bat para evitar la utilizacin de la lnea de comandos en la mayor medida de los posible. Por ser una versin de evaluacin, podis descargaroslo en casa, y realizar las simulaciones fuera del laboratorio. Este simulador tiene como lenguaje de entrada el lenguaje VHDL. Se puede encontrar una extensa documentacin de l en internet, no obstante varios profesores del Departamento hemos editado un manual que est disponible en copistera (tras encargo). Este libro se titula Gua Prctica de Circuitos Electrnicos y Sistemas I, ISBN: 84-95699-15-X. En l podis encontrar informacin sobre este lenguaje y el simulador utilizado, adems de otros simuladores que se utilizarn en otras asignaturas que imparte el Departamento. Otros enlaces con informacin sobre VHDL son los siguientes: http://tech-www.informatik.unihamburg.de/vhdl/ http://www.dte.uvigo.es/vhdl/home.html http://www.escet.urjc.es/~jmartine/Enlaces.htm#VHDL Vamos a dar una breve introduccin a la losofa del modelado de circuitos en VHDL. Cualquier modelo en VHDL se divide en dos partes: entidad y arquitectura. La entidad (palabra clave entity) indica las caractersticas del circuito como si fuera una caja negra, es decir, el nombre que va a tener el circuito y su comunicacin con el exterior. La arquitectura (palabra clave architecture) indica cmo est construido el circuito por dentro; como podemos obtener una misma funcin de multitud de formas, puede haber varias arquitecturas para una misma entidad, as que la arquitectura tambin necesita un nombre. Esta divisin se puede ver en la siguiente gura. ENTIDAD (ENTITY) ARQUITECTURA (ARCHITECTURE) A B A C B C A B C ejemplo1 B C B C A F1 F2 arq2 F1 F2 F1 F2 arq1

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

El cdigo VHDL del ejemplo anterior es el siguiente (solamente utilizaremos la arquitectura arq2): entity ejemplo is port( A, B, C F1, F2 end ejemplo; Nombre Nombre de puertos Tipo de puertos Sentido de puertos

: in bit; : out bit);

architecture arq2 of ejemplo is signal S1, S2, S3 : bit; begin S1 <= B or C after 12ns; S2 <= A and S1 after 14.75ns; S3 <= B and C after 14.75ns; F1 <= S2; F2 <= S3 or S2 after 12ns; end;

Nombre Seales internas Asignacin de seal Operadores Retrasos

Con el cdigo anterior tendramos modelado el circuito, pero no podramos simularlo ya que no le hemos dado ningn valor a las seales de entrada (en nuestro caso A, B, C). Para poder llevar a cabo este paso es necesario modelar un nuevo sistema denominado test, con unas caractersticas especiales. Entidad sin puertos entity test is end test; architecture op of test is signal S1, S2, S3, S4, S5 : bit; component ejemplo port(A, B, C : in bit; F1, F2 : out bit); end component; for all:ejemplo use entity work.ejemplo; begin C1: ejemplo port map (S1, S2, S3, S4); S1 <= 0, 1 after 100ns, 0 after 200ns; S2 <= 1, 0 after 50ns, 1 after 150ns, 0 after 250ns; S3 <= 0, 1 after 150ns; end; Puertos del circuito Declaracin del circuito como componente Conexin de los puertos Formas de onda

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

2.3. Emulacin.

Esta parte, junto con la realizacin de la simulacin, es la que realmente hay que realizar en el laboratorio. Por emulacin se entiende el montaje del circuito a estudiar con los componentes disponibles en el laboratorio. A continuacin vamos a comentar los elementos con los que contamos en el laboratorio para la realizacin de las prcticas. En el laboratorio, se utilizar el panel de entrenamiento para realizar los montajes necesarios. Este panel se muestra en la pgina siguiente, identicando cada parte. El lugar donde se van a realizar los montajes es la regleta de entrenamiento. Cada panel cuenta con dos regletas como la mostrada en la siguiente gura.

A B B A

El conexionado interno de la regleta es el siguiente: Las secciones A, A, B y B son completamente independientes entre s. Las secciones A y A estn conectadas de forma horizontal, es decir, la lnea A es un solo punto de conexin. Luego estas lneas sern utilizadas para seales con un gran nmero de conexiones, como pueden ser la alimentacin y tierra. Las seciones B y B estn conectadas de forma vertical, por lo tanto habr tantos puntos independientes como columnas tengan estas secciones. Esta zona ser utilizada para las seales con un nmero de conexiones relativamente bajo, es decir, las seales internas del circuito. Bsicamente los circuitos se montarn utilizando circuitos integrados (los que vulgarmente se conocen como cucarachas). El aspecto de un circuito integrado es el siguiente

14 13 12 11 10 9 1 2 3 4 5 6

8 7

La numeracin de los pines (conexiones al chip) se realiza empezando por la esquina donde se encuentra el punto sealado, o en su defecto por la esquina izquierda de la muesca central. Este mtodo de numeracin es estndar para todos los componentes y fabricantes.

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

19

13

2 1 7 6

+ -

6

+ -

12 1, interruptor general 2, piloto de encendido general

11

10

3, LEDs indicadores de estado lgico, los cuales sern utilizados para comprobar el estado de las diferentes seales del circuito 6, Conmutadores de programacin (1-0), los cuales sern utilizados para introducir los valores de las seales de entrada 7, Bornes de salida de 5v, el cual ser utilizado para alimentar los diferentes componentes que formarn nuestro circuito. Es obligatorio que est conectado para que los componentes realicen su operacin correctamente. 10, conmutador de frecuencia, el cual ser utilizado para cambiar la frecuencia de la seal de reloj 11, bornes de la salida de reloj 12, Bornes de salida de masa. Los conmutadores de programacin, los relojes y la alimentacin estn referenciadas a esta salida, por lo que es obligatorio que est conectado al circuito para mantener los niveles correctos. 13, display de 7 segmentos, los cuales sern utilizados cuando queramos mostrar los resultados como nmeros decimales. 19, regletas para insercin de componentes, en el cual con los componentes y cables disponibles en el laboratorio se montarn los circuitos.

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

El nombre de los diferentes circuitos integrados siguen una nomenclatura estndar que nos indica las principales caractersticas del componente que estamos manejando. La nomenclatura es como la mostrada a continuacin: FFTTCCCLLL donde: FF son una serie de letras que nos indica el distintivo del fabricante del circuito integrado. TT son una serie de nmeros que nos indica la tecnologa de fabricacin. Las principales tecnologas son: 74, tecnologa TTL, que es la que utilizaremos en las prcticas. 54, tecnologa CMOS CCC son una serie de letras que nos indica las principales caractersticas (de forma cualitativa). Para poder obtener su valor cuantitativo debemos ir a las hojas de especicaciones en su apartado correspondiente. Entre estas caractersticas se encuentran: Velocidad de operacin, la cual puede ser alta y media o baja Consumo de potencia, el cual puede ser alto, medio y bajo LLL son una serie de nmeros que nos indica la funcin lgica que realiza el integrado. As, el siguiente componente nos est indicando las siguientes caractersiticas: SN74LS00 SN --> El fabricante es Texas Instruments 74 --> La tecnologa de fabricacin es TTL LS --> Estamos ante un dispositivo de velocidad y potencia media 00 --> La funcin lgica que realiza es la operacin NAND de dos entradas En las clases de laboratorio, una herramienta fundamental, que siempre debemos tener, son las hojas de caractersticas de los componentes que vamos a utilizar. Seguidamente, vamos a explicar los principales apartados de las hojas de caractersticas de una puerta NAND.

Cdigos del componente N puertas, n entradas, nombre (4 puertas de dos entradas NAND)

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Breve descripcin de la operacin del componente

Tabla de funcin de cada puerta: H = 1 L = 0 X = cualquier cosa

Patillaje, ver la correposndencia en los diagramas (NC = no conectar) (VCC = polarizacin) (GND = masa)

Simbologa estndard, incluye el nombre de las patillas para utilizar la informacin del patillaje

Simbologa tradicional, incluye el nombre de las patillas para utilizar la informacin del patillaje

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Esquemtico, construccin interna de una puerta

Rangos y/o condiciones mximas de operacin

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

10

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Condiciones de operacin

Caractersticas Electrcas

Caractersticas de conmutacin (temporales)

11

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Condiciones de operacin

Caractersticas Electrcas

Caractersticas de conmutacin (temporales)

12

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

Notas importantes sobre la utilizacin del componente, aplicaciones especcas y notas de garanta

13

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

14

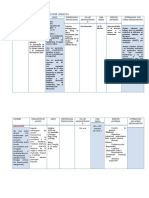

A continuacin mostramos las hojas de especicaciones correspondiente a las puertas NAND de 2 entradas. En las hojas de especicaciones de cualquier componente se muestran los siguientes apartados: Descripcin. En este apartado se muestran los smbolos genricos de las puertas, as como la tabla lgica de la funcin que realiza. Un punto importante de este apartado es que nos muestra el conexionado de las diferentes patillas del integrado, necesario para realizar una conexin correcta. Este conexionado depende del tipo de empaquetamiento (los cuales estarn caracterizados por el aspecto externo que tenga el integrado); por lo tanto, debemos elegir el conexionado de nuestro integrado (debe coincidir el nombre completo) y de su empaquetamiento. En el conexionado nos podemos encontrar con una serie de pines etiquetados como NC. Estos pines no estn conectados al interior del integrado, y por lo tanto no se tienen que conetar. El hecho de que aparezcan es para mantener la simetra del circuito integrado a la hora de conectarlos en el sporte correspondiente, como puede ser una regleta de entrenamiento o un circuito impreso. Puerta a nivel de esquemtico. En este apartado se nos muestra la puerta en su nivel inmediatamente inferior, es decir, una puerta lgica se mostrara con transistores, y una puerta compleja se mostrara a nivel de puertas lgicas. Caractersticas. En este apartado se indicarn las condiciones de operacin recomendadas y las diferentes caractersticas que muestra el circuito para dichas condiciones. Entre estas caractersticas podemos distinguir caractersticas elctricas (tensiones e intensidades) y caractersticas de conmutacin, switching, (diferencias temporales entre transiciones de entrada y salida). Notas importantes. En este ltimo apartado se introducen una serie de consideraciones y consejos de aplicaciones del circuito en cuestin. Como podemos apreciar del esquema de un circuito integrado, para aprovechar espacio siempre hay dos pines (conexiones al chip) en la misma lnea. Por lo tanto, par no provocar cortocircuitos en el interior del integrado, todos los circuitos integrados se deben colocar en la frontera entre las zonas B y B, las cuales se encuentran desconectadas. Tambin se recomienda utilizar las conexiones a travs de cables externos nicamente cuando sea necesario para evitar problemas debido a estos cables y no al posible fallo de conexin del circuito. Uno de los posibles problemas que nos podemos encontrar es que estos cables estn cortados en su interior y no se produce una conexin donde debera haberla. Un dato importante que debermos utilizar de las hojas de especicaciones es el retraso medio de propagacin, para modelar con mayor precisin el comportamiento de las puertas lgicas en el lenguaje VHDL. Este retraso es el valor medio de los valores tPHL y tPLH, los cuales son especicados en las hojas de caractersticas.

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

15

Acontinuacin mostramos las hojas de especicaciones de los componentes de los disponemos en el laboratorio.

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

16

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

17

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

18

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

19

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

20

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

21

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

22

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

23

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

24

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

25

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

26

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

27

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

28

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

29

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

30

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

31

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

32

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

33

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

34

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

35

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

36

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

37

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

38

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

39

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

40

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

41

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

42

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

43

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

44

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

45

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

46

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

47

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

48

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

49

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

50

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

51

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

52

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

53

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

54

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

55

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

56

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

57

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

58

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

59

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

60

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

61

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

62

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

63

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

64

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

65

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

66

Departamento de Ingeniera Electrnica de Sistemas Informticos y Automtica

67

You might also like

- Lab0latorio de CircuitmakerDocument4 pagesLab0latorio de CircuitmakerJose Maria QuintroNo ratings yet

- UF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasFrom EverandUF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasRating: 2.5 out of 5 stars2.5/5 (3)

- 2-Estruturas LabviewDocument21 pages2-Estruturas LabviewRicardo Quispe PerezNo ratings yet

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208From EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208No ratings yet

- Laboratorio 6 Etn 601 I 2016Document5 pagesLaboratorio 6 Etn 601 I 2016Daniel AguilarNo ratings yet

- Diseño e Implementación de Un 4 Bits ALUDocument10 pagesDiseño e Implementación de Un 4 Bits ALUWilber Mendez PerezNo ratings yet

- Introducción a las señales y sistemasFrom EverandIntroducción a las señales y sistemasRating: 4.5 out of 5 stars4.5/5 (3)

- Modelado de sistemas con Simulink y MATLABDocument12 pagesModelado de sistemas con Simulink y MATLABEdgar ZapanaNo ratings yet

- L1 SimulinkDocument10 pagesL1 Simulinkjack1234512345No ratings yet

- Lab Nº4 - Control de Trayectorias - v1-2012-IIDocument6 pagesLab Nº4 - Control de Trayectorias - v1-2012-IIDarkitmetal ValoNo ratings yet

- BarajasOrozco FranciscoJavier8Document10 pagesBarajasOrozco FranciscoJavier8lariza.ortega5360No ratings yet

- Compuertas en Cascada Con VHDLDocument9 pagesCompuertas en Cascada Con VHDLIsmael SuárezNo ratings yet

- Laboratorio n3 (4) Esta Mier Da Se PrendioDocument10 pagesLaboratorio n3 (4) Esta Mier Da Se PrendioJHON JAIRO RAMIREZ MATEUSNo ratings yet

- Practica 3 - Sistemas Segundo OrdenDocument6 pagesPractica 3 - Sistemas Segundo OrdenFransina GutierrezNo ratings yet

- Practica 2Document9 pagesPractica 2Sebastian MayorgaNo ratings yet

- Circuitos Lógicos Tarea 6Document4 pagesCircuitos Lógicos Tarea 6Alejandro StaveleyNo ratings yet

- Lenguaje de Descripción de HardwareDocument4 pagesLenguaje de Descripción de HardwareAlejandro G. EscandonNo ratings yet

- PRACTICA5 LabviewDocument10 pagesPRACTICA5 LabviewSra R GilNo ratings yet

- Laboratorio 2Document13 pagesLaboratorio 2Andre MamaniNo ratings yet

- Circuit Os DigitalesDocument2 pagesCircuit Os DigitalesCarlos Alberto Evangelista BussoNo ratings yet

- MC Control PracticaDocument14 pagesMC Control PracticaAngel Alexis Lopez PerezNo ratings yet

- Informe Practica 2.2Document9 pagesInforme Practica 2.2Oscar RodriguezNo ratings yet

- Reporte Final Mini Computadora Con ALU 18, 175,244 y Flip-FlopDocument12 pagesReporte Final Mini Computadora Con ALU 18, 175,244 y Flip-FlopJuan100% (1)

- Dise Ñ o Comb I NacionalDocument15 pagesDise Ñ o Comb I NacionalWilmer Rueda RamosNo ratings yet

- Pendulo de AutomatizacionDocument14 pagesPendulo de Automatizacioncarlos zevallosNo ratings yet

- Tarea 3 Grupo 42Document68 pagesTarea 3 Grupo 42Edgar Duque0% (1)

- Lab 5 y 6 CorregidoDocument4 pagesLab 5 y 6 CorregidoVictoria BermudezNo ratings yet

- Paso 1 Grupo 208055 3Document17 pagesPaso 1 Grupo 208055 3Jose Luis GonzalezNo ratings yet

- FSM Verilog lab guideDocument14 pagesFSM Verilog lab guideDiego Armando Badilla CastilloNo ratings yet

- Funciones ALU y circuitos lógicos combinacionalesDocument16 pagesFunciones ALU y circuitos lógicos combinacionalesCarlos RodriguezNo ratings yet

- SimulinkDocument24 pagesSimulinkGabriel Marchena ChávezNo ratings yet

- Imtc Lab2 Miranda Jimenez LaraDocument9 pagesImtc Lab2 Miranda Jimenez LaradsfghjkfdNo ratings yet

- Reporte de LecturaDocument12 pagesReporte de LecturaRosalino Mayoral LagunesNo ratings yet

- Verilog PracticasDocument100 pagesVerilog Practicasivanvargas19100% (1)

- Informe 2 MalcaDocument16 pagesInforme 2 MalcaRicardo D. Alca MejiaNo ratings yet

- Modelado de sistemas dinámicos con PowerDEVSDocument4 pagesModelado de sistemas dinámicos con PowerDEVSNELY ARCIBIA ALBARADONo ratings yet

- Practicas Tema 1Document20 pagesPracticas Tema 1Marcos GarciaNo ratings yet

- Foro Simulador MontecarloDocument4 pagesForo Simulador MontecarloCristian RubioNo ratings yet

- Laboratorio No.4Document3 pagesLaboratorio No.4joseNo ratings yet

- Diseño de circuitos combinacionales usando lógica booleanaDocument7 pagesDiseño de circuitos combinacionales usando lógica booleanaSamuel Diaz Parra0% (1)

- Aplicaciones de La Logica DifusaDocument8 pagesAplicaciones de La Logica DifusaStharlin BonillaNo ratings yet

- Apuntes - Electronica Digital - U3 - Montero Corrales Pablo DamianDocument62 pagesApuntes - Electronica Digital - U3 - Montero Corrales Pablo DamiandamianNo ratings yet

- Prácticas Introductorias Al Manejo Del ATP-DRAWDocument14 pagesPrácticas Introductorias Al Manejo Del ATP-DRAWVíctor Hugo Reséndiz Estrada100% (1)

- Informe 8 - Control de ProcesosDocument17 pagesInforme 8 - Control de ProcesosJavier RuizNo ratings yet

- Practica4 Coyago Cacuango RDocument9 pagesPractica4 Coyago Cacuango RSantiago GuilcazoNo ratings yet

- Implementación de Una Planta Con Amplificadores OperacionalesDocument2 pagesImplementación de Una Planta Con Amplificadores OperacionalesSantiago Alfonso Castellanos MaestreNo ratings yet

- Proyecto Final Unidad 1 Armando MoralesDocument7 pagesProyecto Final Unidad 1 Armando Moralesarmando moralesNo ratings yet

- Laboratorio 1 Modelado y Simulacion 4278 y 4281Document7 pagesLaboratorio 1 Modelado y Simulacion 4278 y 4281Cesar BautistaNo ratings yet

- P2 MestanzaDocument12 pagesP2 MestanzaEduardo Mestanza RodriguezNo ratings yet

- 2 FiltracionDocument48 pages2 FiltracionH Marquez R GracielaNo ratings yet

- Simulación circuitos MATLABDocument9 pagesSimulación circuitos MATLABAndres Francisco Parra AcevedoNo ratings yet

- P1 CP-FundamentosDocument12 pagesP1 CP-FundamentosLuis Alarcón PereroNo ratings yet

- Prácticas de Laboratorio Fundamentos de Circuitos Eléctricos 2021BDocument42 pagesPrácticas de Laboratorio Fundamentos de Circuitos Eléctricos 2021BKAGGHGNo ratings yet

- Grupo 4 Lab5Document11 pagesGrupo 4 Lab5Aldair RoblesNo ratings yet

- Práctica #2Document9 pagesPráctica #2Juan Daniel Landin AvilaNo ratings yet

- Formularios en Documentos HTMLDocument26 pagesFormularios en Documentos HTMLSrebritoNo ratings yet

- Programación y Lenguajes-PonenciasDocument266 pagesProgramación y Lenguajes-PonenciasSrebritoNo ratings yet

- Curso Drupal6 MarysalentoDocument565 pagesCurso Drupal6 MarysalentoCarlomagno Gonzalez VillalobosNo ratings yet

- Guia TesinaDocument38 pagesGuia TesinaaguilarmxNo ratings yet

- ILÍADA Canto IDocument222 pagesILÍADA Canto Ipablorlandog2788No ratings yet

- Interpretacion Datos NumericosDocument15 pagesInterpretacion Datos NumericosSrebritoNo ratings yet

- Reconocimiento de La Funcion de La CapacitacionDocument5 pagesReconocimiento de La Funcion de La CapacitacionSrebritoNo ratings yet

- Aws Academy Cloud OperationDocument3 pagesAws Academy Cloud OperationneonaviNo ratings yet

- Metrados Acondicionar A InguilpataDocument150 pagesMetrados Acondicionar A InguilpataHectorNuñezLopezNo ratings yet

- Jefe taller automotorDocument6 pagesJefe taller automotorErlinNo ratings yet

- Consumos culturales de adolescentes y jóvenesDocument29 pagesConsumos culturales de adolescentes y jóvenesgauchofiero99No ratings yet

- Formato para Ficha de Insumos y ConsumosDocument4 pagesFormato para Ficha de Insumos y ConsumosMiranda Rivera PenagosNo ratings yet

- Cuadrocomparativo 130613212527 Phpapp02Document7 pagesCuadrocomparativo 130613212527 Phpapp02B F Aguirre JaquiNo ratings yet

- Causas y Efectos Dela Agotamiento de Los Recursos NaturalesDocument6 pagesCausas y Efectos Dela Agotamiento de Los Recursos NaturalesSANDI MARICRUZ BARRIOS VILLATORONo ratings yet

- Bases Cii-2021Document4 pagesBases Cii-2021Emerson Salinas ZapataNo ratings yet

- Ruta de Basura en ApizacoDocument9 pagesRuta de Basura en ApizacoMgl SantaNo ratings yet

- Codigo Tributario Libro IDocument18 pagesCodigo Tributario Libro IRichard Ramos CutimboNo ratings yet

- Componentes de Una Planta Incineradora de ResiduosDocument2 pagesComponentes de Una Planta Incineradora de ResiduosMiguel CamposNo ratings yet

- Nissan 350 Z 2007 #1279045Document1 pageNissan 350 Z 2007 #1279045Ian FernandezNo ratings yet

- Cuidados interculturales en la salud materna e infantilDocument28 pagesCuidados interculturales en la salud materna e infantilRebeca LoyolaNo ratings yet

- Practica CalificadaDocument4 pagesPractica CalificadaRoder Arnol Torre Salvador100% (1)

- Tarea de Evaluación ContínuaDocument2 pagesTarea de Evaluación ContínuaSophie Von Der SwanzigNo ratings yet

- T3 Álgebra Anaya PDFDocument69 pagesT3 Álgebra Anaya PDFAnonymous IEqF2WIQ7hNo ratings yet

- TemaII Lípidos para BiomoleculasDocument19 pagesTemaII Lípidos para BiomoleculasJavier Yribarren MondejarNo ratings yet

- wuolah-free-GD PRIMARIA TFGDocument8 pageswuolah-free-GD PRIMARIA TFGOposiciones Docentes CuencaNo ratings yet

- Psilocibes ThemushroomsDocument255 pagesPsilocibes Themushroomsfred sanNo ratings yet

- Grupo 3 - Agonistas ColinergicosDocument7 pagesGrupo 3 - Agonistas ColinergicosEnrique Ollarbe CastilloNo ratings yet

- 2006 5 Citroen c4 63953Document218 pages2006 5 Citroen c4 63953Leonardo Reyes CavieresNo ratings yet

- Actividad Final Tema 4 Dinámica Las Leyes de Newton y El Momento LinealDocument17 pagesActividad Final Tema 4 Dinámica Las Leyes de Newton y El Momento LinealAraceli Ramirez VigoNo ratings yet

- Delgado Leandro - UrDocument150 pagesDelgado Leandro - UrLorena Lazo LeivaNo ratings yet

- Presentado Por Gloria Patricia QuinteroDocument9 pagesPresentado Por Gloria Patricia QuinteroMayuryNo ratings yet

- Joven de 20 Años Muere Por Tomar Tapsin Caliente Día de NocheDocument7 pagesJoven de 20 Años Muere Por Tomar Tapsin Caliente Día de NocheVicente100% (1)

- Comentario Del Libro de Las 10 EstrategiasDocument3 pagesComentario Del Libro de Las 10 EstrategiasCarlos León GarridoNo ratings yet

- Cama Profunda Como Sistema Alternativo en Produccion PorcinaDocument8 pagesCama Profunda Como Sistema Alternativo en Produccion PorcinaVictor AbreuNo ratings yet

- Informe de Practicas Pre ProfesionalesDocument24 pagesInforme de Practicas Pre ProfesionalesSusan ArmasNo ratings yet

- CronogramaDocument11 pagesCronogramaJulian Felipe AVILA SILVANo ratings yet

- INFORME 3 - Grupo 3Document8 pagesINFORME 3 - Grupo 3Sandra HumalaNo ratings yet