Professional Documents

Culture Documents

InTech-Low Power and Low Voltage Analog To Digital Converters For Wearable Eeg Systems

Uploaded by

m_duraiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

InTech-Low Power and Low Voltage Analog To Digital Converters For Wearable Eeg Systems

Uploaded by

m_duraiCopyright:

Available Formats

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 15

X

Low-Power and Low-VoItage AnaIog-to-DigitaI

Converters for wearabIe EEG systems

}. M. Carca ConzIez

1

, L. Lpez-MoriIIo

2

, I. Muoz

2

, H. LICniIi

2

and R. C. CarvajaI

2

Micrcnas Gm|H

1

, Gcrmanq

1

||cc|rcnic |nginccring Dcpar|mcn|, Unitcrsia c Scti||a, Spain

2

1. Introduction

LIeclroencephaIography (LLC) has lradilionaIIy pIaced a vilaI roIe in noniloring, diagnosis

and lrealnenl for cerlain cIinicaI silualions, such as epiIepsy, syncope and sIeep disorder, ly

neasuring lhe palienls lrainvaves (Casson el aI., 2OO8). RecenlIy, LLC has aIso nerged as

poverfuI looI for neuroscienlisl aIIoving lhe research of cognilive slales and lhe

enhancenenl lask-reIaled perfornance of an operalive lhrough conpuler nedialed

assislance (Lrdognus el aI., 2OO5).

During noniloring eIeclrodes are pIaced on scaIp lo delecl lhe nicro-VoIl LLC signaIs lhal

resuIl oulside lhe head due lo lhe synchronised neuroIogicaI aclion vilhin lhe lrain. In

praclice, Iong-lern LLC noniloring is generaIIy required eilher inpalienl or anluIalory.

The convenlionaI LLC syslens Iinil palienl noliIily due lo luIk size lecause of lhe lallery

sized required for lhe Iong lern operalion of lhe consliluenl eIeclronics. There is lhus a

slrong need for deveIopnenl of Iighlveighl, vearalIe and vireIess LLC syslens operalion

lo enalIe Iong-lern noniloring of palienls in lheir everyday environnenl (Yales el aI.,

2OO7). In lhis vay, vearalIe LLC is lhe evoIulion of anluIalory LLC unils fron lhe luIky,

Iiniled Iifeline devices avaiIalIe loday lo snaII devices presenl onIy on lhe head lhal

record lhe LLC for Iong line, hovever lhis nelhod denands uIlra-Iov pover and Iov

voIlage circuil design lecause of lhe Iifeline of lhe lalleries.

One of lhe nosl pover consuning luiIding lIocks of a vearalIe LLC fronl-end is lhe

AnaIog lo DigilaI Converler (ADC) required lo process lhe signaI in lhe digilaI donain.

Therefore il is necessary an uIlra-Iov pover ADC (Yang & Sarpeshkar, 2OO6) for LLC

appIicalions.

This chapler presenls lhe design of lvo exlreneIy Iov pover consunplion ADCs lhal can

le used for a vearalIe LLC syslen under a very Iov suppIy voIlage environnenl. The

archileclures used for lhe converlers are:

- A 1O lils second order Svilched-Capacilor (SC) Signa-DeIla noduIalor.

- A 1.5-lil per slage 1O-lil pipeIined ADC.

To achieve lolh, lhe exlreneIy Iov-pover and lhe Iov voIlage operalion, a nev design

principIe lased on Quasi-IIoaling Cale (QIC) MOS lransislors has leen used. Moreover, lhe

use of a cIass-A operalionaI anpIifier (opanp) liased in veak inversion aIIovs very Iov

2

Biomedical Engineering 16

pover consunplion achieving lhe high open-Ioop gain requirenenls. The inpIenenlalions

in CMOS lechnoIogy of dala converlers for LLC syslens presenled in lhis chapler confirn

lhe usefuIness of lhe proposed lechniques for Iov-voIlage and Iov-pover appIicalions.

2. EEG signaI processing and front-end description

TypicaI LLC signaIs provided ly lhe eIeclrodes pIaced on lhe scaIp are in lhe range 2-5OO V

over a landvidlh of O.5-3O Hz (innie el aI., 1982). Iresenl anluIalory syslens lypicaIIy

have al Ieasl 16 channeIs and operale for around a day vilhoul recharging. WireIess syslens

offer around 8 LLC channeIs and Iasl for 12 hours. SanpIing frequencies higher lhan 2OO Hz

are lypicaIIy specified, neverlheIess lhe lrend in LLC syslens is for higher sanpIing

frequencies and nore recording channeIs, leing nol unconnon currenlIy for inpalienl

nonilors offer sanpIing frequencies of 1 kHz or nore. Modern inpalienl syslens for

epiIepsy diagnosis nay offer 256 channeIs (Casson el aI., 2OO8). Iurlhernore, lo avoid

spaliaI aIiasing lovards 6OO channeIs are needed.

InpIenenlalion of a Iov-pover LLC syslen is nol an easy lask lecause of lhe nalure of lhe

signaIs. The reason is lhal lhe scaIp eIeclrodes drifl vilh line superinposing a Iov

frequency signaI in lhe order of lens of niIivoIls (Cooper el aI., 1974) lo lhe desired LLC one.

Tvo slralegies can le foIIoved lo deaI vilh lhis lype of signaIs:

1. DigilaIize lhe LLC signaI and lhe drifl signaI logelher and renove lhe second one

digilaIIy. This signaI processing requires a very accurale ADC vilh nore lhan 2O

lils of resoIulion, vhich vouId le very pover consuning.

2. IiIler lhe drifl signaI oul in lhe fronl-end. This second slralegy reIaxes lhe ADC

resoIulion al expense of lighlening lhe requirenenls of lhe previous

inslrunenlalion anpIifier lecause il is difficuIl lo fiIler such a Iov-frequency signaI

oul vilhoul affecling lhe desired one. ADCs leing presenled in lhis chapler are

lhoughl for lhis signaI processing slralegy. ecause of lhe exlreneIy Iov-pover

consunplion of lhe ADC, lhere is nore pover ludgel avaiIalIe for lhe design of

lhe fiIlering inslrunenlalion anpIifier (Yales el aI., 2OO7).

Iig. 1. shovs lhe lasic lIock diagran of lhe Iov-pover Iov-voIlage fronl-end for vearalIe

LLC syslens. The fronl-end is nade up of:

Iig.1.Ironl-end for vearalIe LLC syslen.

1. An inslrunenlalion anpIifier. The inslrunenlalion anpIifier perforns lvo lasks. Il

provides a gain of 175, vhich is required lo acconnodale lhe LLC signaI lo lhe

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 17

ADC inpul range. SinuIlaneousIy il provides high-pass fiIlering lo renove

undesired very Iov frequency signaIs hence reducing lhe effecl of lhe eIeclrode

offsel drifl. Therefore il is possilIe lhe use of a noderale resoIulion ADC. In order

lo neel lhe noise specificalions, chopper lechniques are connonIy used in lhe

inslrunenlalion anpIifier (MenoIfi & Huang, 1999). A chopper anpIifier achieves

exceplionaI noise perfornance and very Iov offsel voIlage ly upconverling lhe

signaI lefore anpIificalion lhrough noduIalion vilh a square vave al chop

frequency, f

cn

. IdeaIIy, lhe chop frequency is sel lo a frequency al vhich lhe fIicker

noise is negIigilIe. Afler anpIificalion al f

cn

lhe signaI is dovnconverled lo

laseland. Hovever, lhe fIicker noise and offsel voIlage are sinuIlaneousIy

upconverled lo lhe chop frequency, vhere lhey can le fiIlered oul (Yales &

Rodriguez-ViIIegas, 2OO6).

2. An anli-aIiasing fiIler

3. A 1O lil ADC. The facl lhal lhe sIovIy-varying offsel due lo scaIp eIeclrodes

inpedance drifl is parliaIIy suppressed ly lhe inslrunenlalion anpIifier aIIovs

reIaxing lhe resoIulion requirenenls lo onIy 1O lils.

If lhe voIune of lhe overaII device is assuned lo le 1cn

3

and haIf of such voIune is

reserved for a lallery of energy densily of 2OOWh/I (Casson el aI., 2OO8). Ior an operalion of

3O days vilhoul recharging lhe average pover consunplion nusl le Iess lhan 14OW.

CurrenlIy, 2O-32 channeIs LCC syslens are preferred. This inpIies lhal average pover

consunplion per channeI nusl le Iess lhan 5-3W. The eslinaled pover consunplion of

lhe digilaI signaI processing is around 4OW. The pover consunplion of lhe enlire syslen

is:

( )

DSI ADC f a DSI ch

I I I I N I I N I + + + = + =

(1)

vhere N is lhe nunler of channeIs, I

ch

, I

a

, I

f

, I

ADC

and I

DSI

are lhe pover consunplion of

lhe channeI, inslrunenlalion anpIifier, anli-aIiasing fiIler, ADC and DSI respecliveIy. A

good design guideIine is lo reverse 5O-66 of lhe conpIele anaIog pover consunplion (I

ch

)

for lhe ADC. Thus, a suilalIe ADC pover consunplion vouId le in lhe range of 3.3-2.5W

per channeI for a 2O channeIs syslen, and 2-1.5W for a 32 channeI syslen.

The generaI specificalions for ADCs used in lhe proposed LLC fronl-end are sunnarized in

TalIe 1.

Maxinun inpul frequency 25-1OOHz

ADC sanpIing frequency >1kHz

ResoIulion >9 lils

Inpul VoIlage Range 725nV differenliaI

SuppIy VoIlage as Iov as possilIe (i.e.

1.2V)

Maxinun pover

consunplion

3.3-1.5W

TalIe 1. CeneraI specificalions for ADCs used in lhe LLC fronl-end.

In lhis chapler lvo differenl 1O-lil ADC inpIenenlalions are presenled using a Iov suppIy

voIlage (1.2V).

Biomedical Engineering 18

1. The firsl ADC is inpIenenled ly using a pipeIined archileclure. TypicaIIy such

ADC archileclure is chosen for inlernediale sanpIing frequencies, lul lhis chapler

shovs hov il is aIso possilIe and vorlhvhiIe lo use a pipeIined archileclure lo

design a pover efficienl ADC for LLC appIicalions.

2. The second ADC uses a svilched-capacilor (SC) signa-deIla (EA) archileclure

vhich is connonIy used for lionedicaI appIicalions (Coes el aI., 2OO5), (Lee el aI.,

2OO5). The reduced nunler of operalionaI anpIifier of lhis archileclure is an

advanlage for Iov-pover specificalions. Hovever, lhe inpul signaI landvidlh is

Iiniled due lo lhe oversanpIing operalion of EA ADCs.

olh ADCs have leen designed using slandard O.5n CMOS MOSIS lechnoIogy. In lhis

lechnoIogy lhe MOS lransislors have a reIalive high lhreshoId voIlage, V

TI

=O.96V and

V

TN

=O.67V, vhich nake increase lhe difficuIly of achieve svilch Iinearily and operalionaI

anpIifiers open-Ioop gain requirenenls under a very Iov voIlage suppIy vilh cIassicaI

design lechniques. Tvo slralegies vere adopled in order lo soIve lhese prolIens:

1. The use of CMOS svilches lased on quasi-fIoaling gale lransislors (QIC).

2. The use of sul-lhreshoId liased cIass-A operalionaI anpIifiers.

3. QFG transistors

A fundanenlaI issue in SC circuils operaling vilh a very Iov voIlage suppIy is lhal nol

enough overdrive voIlage can le provided lo lhe gales of lransislors acling as svilches

(CroIs & Sleyaerl, 1994). In lhis vay, lhe signaI sving and Iinearily is Iiniled. CMOS

svilches lased on quasi-fIoaling gale lransislors are an aIlernalive lo lhe veII knovn cIock-

loosling lechniques and loolslrapped svilches (Ranrez-AnguIo el aI., 2OO4).

A QIC lransislor is a MOS lransislor vilh ils gale lerninaI veakIy connecled lo a DC

voIlage lhrough a very Iarge resislor. This resislor is used lo sel lhe DC operaling poinl of

lhe gale lerninaI of lhe inpul MOS lransislor. The resislor can le inpIenenled ly neans of

a MOS lransislor in cul-off region.

Iig. 2. shovs a QIC nMOS lransislor vilh nuIlipIe inpuls. A sinpIe ac anaIysis reveaIs lhal

lhe ac voIlage al lhe quasi-fIoaling gale is given ly:

|

|

|

.

|

\

|

+ + +

+

=

_

=

N

1 j

C D CD S CS j j

T Ieak

Ieak

C

V C V C V C V C

C sR 1

sR

V

(2)

Iig. 2. QIC nMOS lransislor.

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 19

vhere C

T

is lhe lolaI capacilance:

CD

N

1 j

C CD CS j T

' C C C C C C + + + + =

_

=

(3)

The faclor

Ieak

sR

T Ieak

C sR 1 + in (2), represenls a high-pass fiIler. In lhis vay, Iov-

frequencies conponenls of lhe inpul are fiIlered oul vilh a cul-off frequency 1/

T Ieak

C sR 1 + vhich can le very Iov. Therefore, even for very Iov frequencies, (2)

lecones a veighled averaging of lhe ac inpul voIlages delernined ly capacilor ralios, pIus

sone parasilic lerns. The puII-up resislor R

Ieak

sels lhe gale lo a dc voIlage equaIs lo lhe

posilive raiI, lo vhich an ac voIlage given ly (2) is superinposed. Hence, lhe gale voIlage

can lecone higher lhan V

DD

. An exacl vaIue of R

Ieak

is nol required, and ils lenperalure and

voIlage dependence are nol inporlanl, provided lhal R

Ieak

vaIue renains Iarge enough nol

lo infIuence lhe circuil operalion al lhe Iovesl frequency required.

3.1 RaiI to raiI CMOS switch based on quasi-fIoating gate transistors

In Iov-voIlage SC circuils lhere are sone crilicaI svilches lhal need raiI lo raiI signaI sving

operalion. As lhe suppIy voIlage is Iov, nol enough overdrive is provided lo lhe gales of

lransislors used as svilches lo le lurned on over lhe vhoIe signaI range. A sinpIe and very

pover efficienl soIulion lo lhis prolIen is lhe use of a QIC lransislor as Iov-voIlage raiI-lo-

raiI svilch.

Iig. 3. A Iov voIlage raiI-lo-raiI T/H vilh a svilch lased on lvo conpIenenlary QIC

lransislors.

Iig. 3. shovs hov a T/H circuil is inpIenenled using a Iov voIlage anaIog svilch lased on

lvo QIC lransislors (Muoz el aI., 2OO3). The lvo conpIenenlary QIC lransislors, M

passN

and M

passI

, are connecled in series in order lo gel raiI-lo-raiI operalion.

The gale of M

passN

is veakIy lied lo V

DD

lhrough a Iarge nonIinear resislor inpIenenled ly

lransislor M

RIarge1

. The gale is aIso coupIed lo lhe cIock signaI lhrough a snaII vaIued

capacilor, C

1

, so lhal lhe cIock signaI is lransferred lo lhe quasi-fIoaling gale. The capacilor

perforns a IeveI shifl of approxinaleIy V

DD

, vhich aIIovs svilching under very Iov-voIlage

Biomedical Engineering 20

reslriclions. Nole lhal lhe svilch inpIenenled ly M

passN

is nol raiI-lo-raiI lecause il is nol

possilIe lo lurn off lhe lransislor for inpul signaIs near lhe negalive raiI. The raiI-lo-raiI

operalion is achieved lhanks lo QIC lransislor M

passI

(driven ly a conpIenenlary cIock

signaI).

3.2 Low-voItage cIass-AB OperationaI AmpIifier

Al Iov suppIy voIlages lhe signaI dynanic range is reduced and nakes nol possilIe lhe use

cascode lransislors lo gel high-gain slages. In lhis conlexl, lvo slage cIass-A op-anps are

lhe naluraI choice since lhey can have Iov pover consunplion, raiI-lo-raiI oulpul sving and

high gain.

Iig. 4. shovs lhe archileclure of lhe operalionaI anpIifiers used in lolh inpIenenled ADCs

(Ranrez-AnguIo el aI., 2OO6).

Iig. 4. InpIenenlalion of a fuIIy differenliaI CIass-A oulpul slage using QIC lransislors.

QIC lransislors are used (M

7

and M

7p

) vilh lhe Iarge vaIued resislor inpIenenled ly a

nininun size diode connecled pMOS lransislor M

RIarge

, and a snaII vaIued capacilor C

lal

.

Under quiescenl condilions and given lhal no DC currenl fIovs lhrough M

RIarge

lhe voIlage

al lhe gale of M7 is lhe sane as al lhe gale of M

5

so lhal lhe quiescenl currenl in M

5

and M

7

is veII conlroIIed and has lhe sane vaIue I

l

. Transislor M

6

is connonIy sized vilh W/L

dinensions lvice as Iarge as lhose of M

3

, M

4

so lhal lhe quiescenl currenl in M

6

has aIso a

vaIue I

l

. During dynanic operalion, vhen lhe oulpul of lhe op-anp is sIeving, lhe voIlage

al node X is suljecl lo a Iarge change. Civen lhal capacilor C

lal

can nol discharge/charge

rapidIy lhrough M

RIarge

il acls as a fIoaling lallery and lransfers lhe voIlage varialions al

node X lo node Y. This provides cIass A (push puII) operalion lo lhe oulpul slage. No

addilionaI circuilry lo conlroI lhe desired vaIue of lhe quiescenl oulpul currenl is necessary

due lo lhe Iarge resislor. The vaIue of C

lal

can le snaII as lransislor M

RIarge

is inlended lo

operale as a very Iarge resislive eIenenl. The oulpul slage has Iov suppIy requirenenls

since il can operale vilh a suppIy voIlage cIose lo a lransislors lhreshoId voIlage:

5 SDsal 2 SDsal 6 CS DD

V V V V

nin

+ + =

(4)

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 21

AnpIifiers have leen designed vilh lransislors liased in veak inversion in order lo

nininize lhe pover consunplion and lo achieve open-Ioop gain requirenenls. ias currenl

and lransislor sizes are sel lo acconpIish lhe sellIing requirenenls. An addilionaI advanlage

of lhe used operalionaI anpIifier is lhal il presenls enhanced phase nargin and higher unily

gain frequency as lolh lransislors M6 and M7are aclive in lhe cIass-A oulpul slage.

4. Design of a Iow-power Iow-voItage 10-bit PipeIined ADC for wearabIe EEG

systems

MuIli-slage pipeIined ADCs are one of lhe nosl popuIar archileclure for high-speed

appIicalions. They consisl of severaI cascaded slages, caIIed nuIlipIying digilaI-lo-anaIog

converler (MDAC), vhich conlains a sanpIe-and-hoId (S/H), a Iov resoIulion ADC and a

digilaI-lo-anaIog converler (DAC). A digilaI deIay Iine is required for oulpul

synchronisalion lo assure lhe correcl operalion.

The purpose of lhis seclion is lo shov hov il is possilIe lo use a cIassicaI pover-consuning

high-speed ADC archileclure for Iov-pover LLC appIicalions ly neans of a deep

underslanding of pipeIined ADC archileclure and design lechniques Iike quasi-slalic gale

lransislors. The largel is lo use lhis ADC for vearalIe LLC syslens vilh nore lhan 2O

channeIs and perforning sinuIlaneousIy lhe anaIog-lo-digilaI conversion of nore lhan one

channeI.

Iig. 5 shovs lIock diagran of lhe presenled pipeIined ADC. The vhoIe syslen uses fuIIy-

differenliaI archileclure vilhoul a dedicaled fronl-end S/H and consisls of a cascade of 9

fuIIy-differenliaI MDACs slages vilh 1.5 lils of resoIulion al 4 kHz of sanpIing frequency.

The Iasl slage is jusl a 2-lil resoIulion fIash ADC. il redundancy is used in order lo correcl

offsel errors in lhe digilaI donain. Lach MDAC slage conposes of a S/H, a Iov-resoIulion

anaIog-lo-digilaI sul-converler (sul-ADC), a digilaI-lo-anaIog sul-converler (sul-DAC),

and a gain lIock.

MDAC 1

1.5b

MDAC 2

1.5b

MDAC 9

1.5b

Flash

ADC

2b

Data Alignment and Digital Correction

10b

ADC

nput

+ x2

ADC DAC

1.5b

+

-

nput

Output

S/H

Iig. 5. 1O-lil IipeIined ADC archileclure.

Iig. 6. shovs lhe archileclure of lhe MDAC slage. In order lo achieve Iov-pover and Iov-

voIlage reslriclions, lhe inpul connon node of lhe operalionaI anpIifier is differenl lo lhe

connon node of lhe inpul signaI. The MDAC slage has lvo operalion phases caIIed

samp|ing pnasc and amp|ifica|icn pnasc. During lhe samp|ing pnasc lhe inpul of lhe MDAC is

Biomedical Engineering 22

sanpIed and slored in lolh capacilors C

f

and C

s

. The difference lelveen lhe inpul and

oulpul connon node of lhe operalionaI anpIifier logelher vilh lhe offsel and fIicker noise,

vhich vere slored in C

m

during lhe previous amp|ifica|icn pnasc, is correcled. During lhe

anpIificalion phase lhe sul-ADC provides lhe oulpul lils and decides vhich signaI nusl le

suppIied ly lhe nuIlipIexer.

Iig. 6. MDAC archileclure (crilicaI svilches are highIighled).

The crilicaI svilches (lhal are highIighled in Iig. 6) need raiI-lo-raiI signaI sving operalion

and lhey vere inpIenenled, as il vas nenlioned lefore, ly neans of QIC lransislors of

Iig. 3. The sanpIed inpul is anpIified ly lhe faclor 1+(C

f

/C

s

), caIIed gain of lhe MDAC, ly

connecling lhe lop pIale of lhe capacilor C vilh lhe oulpul of lhe operalionaI anpIifier. In a

lradilionaI 1.5-lil MDAC slage lolh capacilor have lhe sane vaIue, so lhe MDAC has a gain

of 2. The lransfer funclion of a MDAC slage is given ly:

Vref D

C

C

Vin

C

C

1 Voul

s

f

s

f

|

|

.

|

\

|

+

|

|

.

|

\

|

+ =

(5)

vhere Vref is lhe reference voIlage of lhe pipeIined ADC, Vin lhe inpul voIlage of lhe

MDAC slage, and:

<

s s

>

=

4 / Vref Vin if 1

4 / Vref Vin 4 / Verf if O

4 / Vref Vin if 1

D

(6)

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 23

OnIy lvo conparalors are required lo inpIenenl lhe sul-ADC in a 1.5-lil MDAC slage.

The oulpul lils of lhe MDACs slages are aIigned and digilaIIy processed ollaining lhe finaI

1O-lil oulpul dala. il redundancy is used in order lo correcl lhe conparalor offsels of

MDAC slages in lhe digilaI donain (Corlalenko, 1966). Due lo lhis redundancy, Iov

resoIulion conparalors can le used vilh offsel up lo

1

2 Vref

+

, leing lhe lil resoIulion

of lhe sul-ADC (Cho & Cray, 1994).

The correcl operalion of a pipeIined ADC is fuIIy dependenl on vhich vaIue lhe oulpul

voIlage of each MDAC slage is sellIed al lhe end of lhe anpIificalion phase vhich is

processed ly nexl pipeIine slage. Lrrors in lhe MDAC oulpul voIlage Iinil lhe perfornance

of lhe ADC. The naxinun voIlage error aIIoved al lhe oulpul of an MDAC, vilhoul

degradalion in lhe ADC perfornance, specifies lhe MDAC luiIding-lIocks requirenenls. In

lhis vay, a deep underslanding of lhe errors al lhe MDAC oulpul voIlage arises in

knovIedge regarding pover saving in lhe righl slage. In lhis seclion lhe error sources in

pipeIined ADC are descriled and such descriplion is used lo inpIenenl a lehaviouraI

sinuIalor lo ollain lhe requirenenls of lhe luiIding-lIock of each MDAC slage of lhe ADC

for a required resoIulion and sanpIing frequency.

The errors concerning lo lhe vaIue of lhe oulpul voIlage of a MDAC slage can le cIassified

inlo lhree differenl groups:

- Slalic errors: lhese errors inpIy lhal lhe oulpul voIlage vaIue of lhe MDAC differs,

lineIy independenl, fron lhe ideaI one. The dynanic of lhe MDAC slage is nol

considered.

- Dynanic errors: lhese are errors vhich inpIy lhal lhe oulpul voIlage of lhe MDAC

does nol achieve lhe slalic vaIue in line. In lhis group, lhe dynanic of lhe MDAC

is onIy considered as unique error source.

- Noise

4.1 Static errors in MDAC stages

The firsl inporlanl slalic error source in pipeIined ADCs is lhe nisnalch lelveen lhe

capacilors C

f

, C

s

of each slage. Considering a nisnalch C lelveen lolh capacilors, C

f

=C,

Cs/C

f

=1+C, an error lern (c) appears al lhe residue voIlage in (5):

c +

|

|

.

|

\

|

+

|

|

.

|

\

|

+ = 9UHI '

&

&

9LQ

&

&

9RXW

I

V

I

V

(7)

vhere lhe error lern c is:

) Vref D Vin ( C + o = c

(8)

Anolher source of error il lhe finile gain of lhe operalionaI anpIifier. Assuning an open-

Ioop gain of A

O

for lhe operalionaI anpIifier of lhe MDAC slage lhe error lern of (7)

lecones:

( )

nisnalch ideaI

O

nisnalch

Voul

A

) C 2 (

c +

o +

c = c

(9)

Biomedical Engineering 24

vhere c

nisnalch

is lhe error lern vrillen in (8) and Voul

ideaI

is lhe oulpul voIlage of lhe

MDAC slage al lhe end of lhe anpIificalion phase vhen no error sources are considered.

This equalion shovs lhal Iov open-Ioop gain of lhe operalionaI anpIifier increases lhe

errors produced ly lhe capacilor nisnalch.

4.2 Dynamic errors in MDAC stages

Lrror sources reIaled lo lhe speed of lhe MDAC slage are considered in lhis seclion. The firsl

dynanic error source vhich nusl le considered is lhe on-resislance of lhe svilches, vhich

are parl of lhe svilch capacilor nelvork of lhe MDAC. During lhe sanpIing phase, lhe on-

resislance of lhe inpul svilches, logelher vilh lhe capacilors, inlroduces an error in lhe

sanpIed inpul voIlage (Carner & Un-Ku). The sanpIed inpul voIlage al lhe end of lhe

sanpIing phase is:

)) C R 2 / Ts exp( 1 ( Vin Vin

ON sanpIed

=

(1O)

vhere R

ON

and C are lhe svilch on-resislance and capacilance vhere lhe anaIog inpul signaI

is sanpIed, and Ts lhe cIock period. In order lo achieve good enough sellIing, lhe line

conslanl R

ON

C is designed lo le severaI line snaIIer lhan lhe cIock period. The dravlack is

lhal lhe equivaIenl noise landvidlh lecones Iarger lhan haIf of lhe sanpIing frequency and

aIiasing of lhe sanpIed noise speclra lakes pIace. Thus, lhe vaIue of lhe aIIoved svilch on-

resislance is defined in lerns of lhe naxinun error aIIoved in lhe sanpIed voIlage:

< = c

slage

N

sanpIed sanpIed

2

1

Vin Vin

) 2 In( N C 2

Ts

R

slage

ON

<

(11)

vhere N

slage

is lhe required resoIulion of lhe slage vhere lhe svilch is used.

Olher dynanic error sources are reIaled lo lhe speed of lhe operalionaI anpIifier. In lhis

vay, lhe sIev-rale (SR) of lhe operalionaI anpIifier Iinils lhe Iinear sellIing line, and a

finile unily-gain frequency (CW) nakes lhe operalionaI anpIifier sIover. The singIe-poIe

nodeI of lhe MDAC slage shovs lhal lhe oulpul voIlage al lhe end of lhe anpIificalion

phase is:

) 1 ( Voul )) CW 2 l exp( 1 ( Voul Voul

dynanic slalic sel slalic

c + = | t =

(12)

vhere Voul

slalic

is lhe oulpul voIlage vhen onIy slalic error sources are considered (7), is

lhe feedlack faclor of lhe MDAC, and l

sel

is lhe Iinear sellIing line:

( )

| t

+ = =

CW 2

1

SR

Voul

2

Ts

l

2

Ts

l

slalic

SR sel

(13)

A lvo-poIe syslen nodeI for lhe conpIele MDAC descriles a nore accuraleIy lhe sellIing

lehaviour. Considering lhal lhe syslen has a phase nargin

n,

lhe danping faclor is:

) ( cos 1

) cos( 2

1

n

2

n

u

u

=

(14)

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 25

and lhe naluraI frequency of lhe syslen is:

) cos(

CW 2

n

O

u

| t

= e

(15)

In lhis vay, if <1, lhe MDAC oulpul voIlage al lhe end of lhe anpIificalion phase is

(Chuang, 1982):

( ) )) l 1 sin( e

1

1

1 ( V Voul V Voul

sel O

2 l

2

SR slalic SR

sel O

| + e

+ ~

e

|

|

.

|

\

|

t

~

slalic

slalic

Voul CW 2

SR

1 Voul

(16)

Hovever, if >1, lhe MDAC oulpul voIlage al lhe end of lhe anpIificalion phase is:

1 l

1 a

l

e

a

e

1 2

1

V

l

e

a

e

1 2

1

1 Voul Voul

2

2

l l a l

2

SR

l l a l

2

slalic

sel O sel O

sel O sel O

+ =

=

|

|

|

.

|

\

|

|

|

.

|

\

|

+

+

|

|

|

.

|

\

|

|

|

.

|

\

|

~

e e

e e

(17)

vhere V

SR

, in (16) and (17), is lhe MDAC oulpul voIlage al lhe end of lhe sIev-rale line:

( )

O SR

A l CW 2 O

SR

e 1

CW 2

SR A

V

t

= (18)

Olher dynanic error sources are charge injeclion produced ly lhe svilches and cIock

feedlhrough. Lrrors produced ly charge injeclion can le nininized using dunny

lransislors in lhe svilches. In addilion, lolh errors are reduced using snaII lransislor in lhe

svilches. The errors produced ly charge injeclion and cIock feedlhrough can le nodeIed as

a connon node offsel in fuIIy-differenliaI svilched capacilor circuils. This connon node

offsel is reduced ly lhe Connon Mode Rejeclion Ralio (CMRR) of lhe syslen.

Considering lhe vhoIe error sources in an MDAC slage, lhe oulpul voIlage al lhe end of lhe

anpIificalion phase can le vrillen as:

) 1 ( Voul ) 1 ( Voul Voul

lolaI ideaI dynanic slalic dynanic slalic ideaI

c + = c c + c + c + =

(19)

Biomedical Engineering 26

This lolaI error vorsens lhe signaI-lo-noise ralio (SNR) and viII produce lolaI harnonic

dislorlion (THD) of lhe pipeIined ADC. The lolaI error of a MDAC slage can le referred lo

lhe inpul of lhe ADC. In lhis vay, if lhe lolaI error of each MDAC is referred lo lhe ADC

inpul, lhe effeclive nunler of lils (LNO) of lhe pipeIined ADC is

O2 . 6 / 76 . 1

C / 2

V

Iog 2O LNO

N

1 j

j

1 i

i

j

lolaI

IS

|

|

|

|

|

|

.

|

\

|

|

|

|

|

|

|

.

|

\

|

c

=

_ [

= =

(2O)

vhere V

IS

is lhe ADC fuII-scaIe, N lhe nunler of slages of lhe ADC, c

lolaIj

lhe lolaI reIalive

error of lhe slage j and C

i

lhe ideaI gain of lhe slage i.

4.3 Noise in MDAC stages

The noise in each slage of lhe pipeIine ADC is produced ly lhe svilches, lhe operalionaI

anpIifier, and lhe reference voIlage generalor. As il has leen descriled in lhe previous

seclion, lhe unily gain frequency of lhe operalionaI anpIifier and lhe inverse of lhe R C

line nusl le severaI lines Iarger lhan lhe sanpIing frequency. The noise suffers fron

aIiasing lecause lhe equivaIenl noise landvidlh, of lhe sanpIing nelvork and lhe

operalionaI anpIifier, is Iarger lhan lhe Nyquisl frequency. Hovever, a MDAC slage has a

gain higher lhan unily vhich inpIies lhal noise conlrilulions lo lhe equivaIenl inpul noise

are progressiveIy reduced fron lhe firsl slage lo lhe Iasl slage. In lhis vay, lhe lolaI inpul

equivaIenl noise of lhe MDAC slages is:

_ [

= =

=

N

1 i

N

1 j

2

2

i

n

Cj

Von

Vin (21)

i

Von leing lhe lolaI oulpul noise of lhe MDAC slage-i. The lolaI oulpul noise of an MDAC

slage is lhe sun of lhe oulpul referred noise pover in sanpIing and anpIificalion phase.

The lolaI oulpul noise of an MDAC is:

ref OIA OIA OIA ON

MDAC

2

2

SnrWn Wn Sn Wn klR 4

C

kT C

Von + + + = (22)

vhere k is lhe oIlznann conslanl, T is lhe lenperalure, C is lhe sun of lhe capacilance

connecled lo lhe anaIog inpul during lhe sanpIing phase, R

ON

is lhe on-resislance of lhe

svilches connecled lo lhe oulpul during lhe anpIificalion phase, Sn

OIA

is lhe oulpul noise

speclraI densily of lhe operalionaI anpIifier, Snr is lhe noise speclraI densily of lhe reference

voIlage generalor, Wn is lhe equivaIenl noise landvidlh of lhe operalionaI anpIifier

and Wn is lhe nininun lelveen lhe equivaIenl noise landvidlh of lhe operalionaI

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 27

anpIifier and lhe equivaIenl noise landvidlh of lhe anpIifier vhich generales lhe reference

voIlages.

The conpIele equivaIenl inpul noise pover of lhe vhoIe pipeIine ADC is lhe sun of lhe

equivaIenl inpul noise pover of lhe MDAC slages pIus lhe equivaIenl inpul noise pover of

lhe S/H circuil. Anolher inporlanl noise source in pipeIine ADC is lhe cIock jiller. The cIock

jiller is originaled ly lhe phase noise of lhe cIock generalor. The noise pover produced ly

lhe cIock jiller vhen a sinusoidaI signaI vilh haIf fuII-scaIe anpIilude is:

( ) 2 / f V Vn

2

jiller in IS

2

jiller

o t = (23)

f

in

leing lhe inpul signaI frequency,

jiller

lhe sanpIing jiller slandard devialion of lhe cIock

signaI.

4.4 BehavioraI simuIation resuIts

SlalislicaI lehavioraI sinuIalions vere done using MATLA ly neans of lhe equalions

presenled in lhe previous seclion lo gel lhe nininun reslriclion of lhe luiIding lIocks and

considering lhe Iov-pover consunplion requirenenl. These lehavioraI sinuIalions provide

lhe naxinun capacilor nisnalch (and lhus lhe nininun capacilor vaIues), lhe open-Ioop

and unily-gain frequency for lhe operalionaI anpIifiers as veII as noise reslriclions for lhe

reference voIlages generalor. These lasic specificalions are sunnarized in TalIe 2:

Slage Capacilor Misnalch

(5)

Open Loop Cain(d) CW (kHz)

1 O.5 76 24

2 O.7 73 22

3 1.4 7O 21

4 2.25 68 2O

5 3.9 64 19

6 6.5 6O 18

7 12 58 16

8 21 55 15

9 25 48 1O

TalIe 2. SlalislicaI lehavioraI sinuIalion resuIls.

4.5. ImpIementation detaiIs

Due lo Iov-voIlage suppIy lhe use of cascade lransislor is nol possilIe lo achieve high

enough open-Ioop gain. In lhis vay, onIy cIassicaI lvo slage archileclures can le

inpIenenled. In order lo increase lhe Iinearily of lhe oulpul slage and lhe open-Ioop gain,

cIass-A oulpul slages have leen used. The archileclure presenled in seclion 4, Iig. 4., vas

used for each opanp of lhe pipeIined ADC and foIIoving lhe requirenenls presenled in

TalIe 2. As il vas aIso nenlioned lefore, lhe lransislors of lhe opanp are liased in veak

inversion in order lo achieve lhe open-Ioop gain requirenenls vilh lhe nininun pover

consunplion.

Biomedical Engineering 28

The sul-ADC, required in each MDAC slage, vas inpIenenled ly neans of lvo SC

conparalors, Iig. 7. The SC conparalor operales on lvo non-overIapping cIock phases.

Thus, during lhe sanpIing phase, lhe anaIog inpul voIlage is sanpIed in lhe capacilors 3C

and C, vhiIe lhe Ialch is resel. During lhe conparison phase, lhe conparalor conpares lhe

sanpIed anaIog inpul vilh lhe previousIy sanpIed reference voIlage. The Ialch provides lhe

digilaI oulpul vhereas lhe svilched capacilor nelvork sanpIes lhe reference voIlage in lhe

capacilor C for lhe foIIoving conparison.

Iig. 7. Sul-ADC archileclure.

The ADC vas designed using an AMI (MOSIS) O.5n CMOS lechnoIogy vilh IMOS and

NMOS lhreshoId voIlages of aloul V

TI

=-O.96V and V

TN

=O.67V respecliveIy. TalIe 3

sunnarizes lhe ollained posl-Iayoul sinuIalion resuIls of lhe conpIele pipeIined ADC

vhen a sinusoidaI inpul signaI of a -1dIS and 93.75Hz is appIied. The foIIoving figure of

neril (IOM) vas used:

n

n

f 2

I

IOM=

(24)

vhere n is lhe nunler of lils, I is lhe pover consunplion in Walls and f

n

is lhe Nyquisl

frequency in Hz.

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 29

SanpIing Rale 4kS/s

SNR (inpul 93.75Hz, O.645Vpp) 61.5d

THD (inpul 93.75Hz, O.645Vpp) -75.9d

SINAD (inpul 93.75Hz,

O.645Vpp)

6O.76d

LNO 9.8lils

Iover Consunplion 1.5W

IOM O.84p}/slale

TalIe 3. SinuIalion resuIls.

Iig. 7. shovs lhe speclrun of lhe reconslrucled anaIog signaI fron lhe digilaI oulpul lils of

lhe pipeIined ADC.

SinuIalion resuIls are provided vhich shovs 9.8 lils of resoIulion vilh 1.2 V suppIy voIlage

and onIy a pover consunplion of 1.5W. The pover efficiency is of O.84p}/slale, leing lhe

nosl energy efficienl converler of aII lhe lionedicaI ADCs excepl (Yang el aI., 2OO6).

Iig. 8. SinuIalion resuIls.

5. A 10-bit SC-EA moduIator for EEG appIications

OversanpIing EA ADCs are lased on lhe principIe lhal lhe conversion error can le high-

pass fiIlered and Ialer renove ly digilaI fiIlers. The requirenenls on lhe anaIog parls are

reIaxed and high-resoIulions can le achieved. The dravlack is lhe reIalive snaII inpul

signaI landvidlh due lo oversanpIing. A EA noduIalor consisls of an anaIog fiIler,

conlinuous or discrele line, and a coarse quanlizer encIosed in a feedlack Ioop. Togelher

vilh lhe fiIler, lhe feedlack Ioop acls lo allenuale lhe quanlizalion noise al Iov frequency

vhiIe enphasizing lhe high frequency noise Thus, lhe quanlizalion noise is high-pass

fiIlered vhiIe lhe inpul signaI is onIy deIayed. The high frequency noise can le renoved ly

using digilaI Iov-pass fiIler (decinalion), and a Iov-noise oulpul signaI is achieved.

Biomedical Engineering 30

A cIassicaI inpIenenlalion of a singIe-lil second order SC-EA noduIalor is shovn in Iig. 9.

The nosl inporlanl luiIding lIock in lhis archileclure is lhe sunning inlegralor.

Iig. 9. Second-order discrele-line EA noduIalor.

The renaining luiIding lIocks in lhe anaIogy porlion of lhe noduIalor are conparalor and

1-lil DAC. The conparalor circuil acls as a 1-lil ADC lhal naps ils inpul inlo one of lvo

digilaI oulpul codes. The lvo digilaI oulpul codes are lhen napped lack inlo anaIog IeveIs

ly lhe DAC. If lhe lvo oulpul codes of lhe conparalor are defined as 1/2, lhen lhe DAC,

negIecling DAC, can le represenled sinpIy ly gain lIock.

The ideaI oulpul of lhe second order EA noduIalor, vhen l

2

=2a

1

a

2

and l

1

=a

1

, vhich

guaranlee lhe Ioop slaliIily, is descriled ly:

( ) ) z ( L z 1 ) z ( X z ) z ( Y

2

1 2

+ =

(25)

vhere L(z) is lhe quanlizalion noise in lhe quanlizer and X(z) lhe inpul signaI. Conponenl

nisnalch, finile open-Ioop gain of lhe opanps, lhernaI noise and inconpIele sellIing are

lhe nosl inporlanl error sources in EA noduIalors vhich degrade lhe overaII ADC

perfornance. As il vas previousIy nenlioned, lhe nosl inporlanl luiIding lIock of a EA

noduIalor is lhe inlegralor. In lhis vay, lhe error sources in such lIock nusl lo le

considered. The equalion (2O) corresponds lo lhe foIIoving lransfer funclion for an

inlegralor:

1

1

1

z 1

z a

) z ( H

= (26)

vhere a

1

is lhe gain preceding lhe inpul lo lhe inlegralor. Devialions in a

1

fron ils noninaI

vaIue in lhe firsl inlegralor aIler lhe noise shaping funclion of lhe noduIalor changing lhe

ADC perfornance (oser & WooIey, 1988). In SC EA noduIalors, lhese devialions are

nainIy a consequence of capacilor nisnalch. Larger a

1

neans higher gain in lhe forvard

palh of lhe noduIalor and consequenlIy grealer allenualion of lhe quanlizalion noise.

Hovever, if a1 is loo Iarge (a

1

>O.6), lhe signaI anpIiludes al lhe inlegralor oulpuls increase

rapidIy and lhe syslen lecones unslalIe.

The ideaI inlegralor DC gain is infinile. Hovever, due lo circuil conslrains, lhe inlegralor

DC gain is Iiniled. This effecl is caIIed inlegralor Ieak and inpIies lhal onIy a fraclion I

of lhe previous oulpul of lhe inlegralor is added lo each nev inpul sanpIe. In lhis vay, lhe

DC gain of lhe inlegralor lecones:

I 1

a

H

1

O

= (27)

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 31

and lhe nev inlegralor lransfer funclion:

1

1

1

Iz 1

z a

) z ( H

= (28)

The effecl of lhe inlegralor Ieak is lhal Iiniled gain al Iov frequencies reduces lhe

allenualion of lhe quanlizalion noise in lhe laseland increasing lhe in-land quanlizalion

noise.

In a generaI forn, lhe in-land error pover of a EA noduIalor can le expressed as (Medeiro

el aI., 1999):

sel nI noise Q lolaI

I I I I I + + + =

(29)

vhere I

Q

is lhe quanlizalion error, I

noise

lhe noise circuil error, I

nI

lhe non-Iinearily error

and I

sel

lhe inconpIele sellIing error. The design of lhe ADC can le nade in such lhal

quanlizalion error is lhe doninanl error source:

( )

1 L 2

L 2

sel nI noise

M 1 L 2 1 2

Vref 2

12

1

I I I

+

+

t

<< + + (3O)

vhere Vref is lhe reference voIlage, L lhe noduIalor order and M lhe oversanpIing ralio.

Lvery doulIing of lhe sanpIing rale viII provide L + O.5 exlra lils. The resoIulion can le

increased ly increasing lhe quanlizalor resoIulion and lhe noduIalor order. A prolIen vilh

increasing lhe resoIulion of lhe quanlizer is lhal lhe nonIinearilies in lhe DACs viII direclIy

Iinil lhe ADC perfornance. Increasing lhe noduIalor order nakes lhe slaliIily of lhe Ioop

nore difficuIl, especiaIIy for order higher lhan 2.

UsuaIIy, lhe condilion expressed in (25) inpIies a high anounl of currenl consunplion.

Inslead is nore efficienl lo nake lhe design such lhal

sel nI noise Q

I I I I + + ~

.

In order lo ollain an oplinun design lhe foIIoving consideralion vere laken inlo accounl:

1. The vaIue of lhe sanpIing capacilor al lhe noduIalor fronl-end is seIecled so lhal

lhe error due lo quanlizalion noise and circuil noise is snaIIer lhan lhe naxinun

aIIoved in-land error. The anpIifier noise, lhe svilches noise and kT/C noise are

lhe nain conlrilulor lo lhe overaII circuil noise (I

noise

).

2. The error conlrilulion due lo inconpIele sellIing is nade a non-Iiniling faclor ly

neans of a high enough open-Ioop gain and CW of lhe opanps. Anyvay, lhe

sellIing nusl nol le Iiniled ly lhe sIev-rale of lhe opanps. In addilion, loo high

CW viII end ups vilh unnecessary exlra pover consunplion. The CW of lhe

operalionaI anpIifiers nusl oflen le al Ieasl an order of nagnilude grealer lhan

lhe sanpIing frequency. Hovever, sinuIalions shov lhal lhe CW of lhe

operalionaI anpIifiers can le Iover (CiusloIisi. & IaIunlo,2OO3). A good

conpronise for lhe CW of lhe operalionaI anpIifiers is (oser & WooIey, 1988):

s

1

f

a 1

CW

t

+

> (31)

Biomedical Engineering 32

3. CrilicaI design paraneler of lhe quanlizer inpIenenled ly neans of conparalors

nusl le considered. The speed of lhe conparalor nusl le high enough for lhe

desired sanpIing rale, and inpul offsel, inpul referred noise and hysleresis nusl

le Iov enough lo nol degrade lhe ADC perfornance.

5.1 ADC architecture and buiIding bIocks.

The second ADC inpIenenlalion lhal is descriled in lhis chapler for LLC purposes is a 1O-

lil SC-EA noduIalor operaling vilh a sanpIing frequency of 3.2 kHz and a fuII-scaIe range

of O.725 V (Lopez-MoriIIo el aI., 2OO8). A sinpIe and pover efficienl archileclure for high

resoIulion ADCs in lhe range of lionedicaI signaIs is lhe cIassicaI second-order EA

noduIalor (Iig. 9). The nain advanlages of lhis archileclure are sinpIicily, Iov sensilivily lo

conponenl nisnalch and slaliIily.

Syslen sinuIalions have leen perforned using MATLA/SIMULINK lased on lhe nodeIs

deveIoped on (oser & WooIey, 1988) and (Ralii & WooIy, 1999). As a resuIl of lhese

sinuIalions (incIuding lhe nain non-ideaIilies such as finile DC gain, landvidlh, and sIev-

rale of lhe anpIifiers) a sel of specificalions for lhe nosl inporlanl luiIding lIocks have

leen ollained. These specificalions are sunnarized in TalIe 2.

CeneraI Specificalions

OversanpIing ralio 64

SanpIing frequency 3.2kHz

Inlegralors coefficienls

a1,l1 O.25

a2 O.5

l2 O.25

Iirsl inlegralors

opanp

Oulpul-Sving 2Vpp

SIev-rale (SR) 15V/ns

Unily-gain frequency 8kHz

DC gain 3Od

CIock }iller O.1nsrns

Capacilor vaIues

Cs1 125fI

Ccds 5OOfI

Ci1 5OOfI

Cs2 5OfI

Ci2 2OOfI

TalIe 4. Specificalions for luiIding lIocks.

ehavioraI sinuIalions shov a Dynanic Range (DR) of 72d vilh an oversanpIing ralio of

64, vhich is enough lo achieve lhe 1O lil resoIulion. In order lo gel an uncondilionaIIy slalIe

noduIalor and lo naxinize lhe inlegralors oulpul sving, lhe coefficienls have leen chosen

as a

1

=l

1

=l

2

=O.25 and a

2

=O.5 (Ralii & WooIy, 1999).

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 33

Iig. 1O. InpIenenlalion of lhe second-order EA noduIalor (crilicaI svilches are

highIighled).

Iig. 1O shovs lhe SC inpIenenlalion of lhe noduIalor of Iig. 9. The archileclure is

conposed of lvo correIaled doulIe sanpIing (CDS) inlegralors, a conparalor, and a 1-lil

digilaI-lo-anaIog converler. This inpIenenlalion has leen chosen allending lo differenl

inpIenenlalion issues:

1. IIicker noise: as lhe desired signaI landvidlh of lhe converler is Iov, lhe noise

fIoor is doninaled ly fIicker noise. CorreIaled DoulIe SanpIing has leen used in

order lo shape lhe fIicker noise oulside of lhe signaI land (WiIIians & WooIey,

1994). The lasic operalion of lhe CDS inlegralor is as foIIovs. The anpIifier fIicker

noise and offsel is sanpIed across C

CDS

during lhe firsl cIock phase (|

1

). During lhe

second cIock phase (|

2

) lhe fIicker noise and an offsel are canceIIed ly lhe voIlage

slored in C

CDS

.

2. Lov-voIlage operalion: lhe use of a very Iov suppIy voIlage inlroduces severaI

issues lhal conpIicale lhe design of lhe Signa-DeIla noduIalor. The firsl prolIen

lo soIve is lhe design of an operalionaI anpIifier vilh a Iarge oulpul sving lhal

achieves sufficienl gain and landvidlh. The olher crilicaI prolIen is lhe need of a

raiI-lo-raiI svilch. These prolIens are soIved using QIC lechniques descriled in

previous seclion 3 and 4.

3. Lov-pover operalion: lhe nain conlrilulors lo pover consunplion of a EA

noduIalor are lhe operalionaI anpIifiers. Lov-pover operalion is achieved ly

neans of using lhe lvo-slage cIass-A opanp lased on QIC lransislor and liased

in veak inversion shovn in seclion 4. Olher neasure lo save pover consunplion is

lo nininize capacilor sizes vhich are Iiniled eilher kT/C noise or capacilor

nisnalch specificalions.

The 1-lil quanlizer has leen inpIenenled using lhe archileclure iIIuslraled in Iig. 11. The

dynanic Ialch operales as foIIovs. When lhe cIock |

2

is Iov, lhe Ialch is resel, and ils

oulpuls are lolh puIIed high. When |

2

is high lhe Ialch enlers in lhe regeneralion phase

Biomedical Engineering 34

lecause M3 and M4 forn a posilive feedlack Ioop. The pover consunplion of lhe

conparalor is of onIy 32.5nW during nornaI operalion. Capacilors C

conp

perforn a DC IeveI

shifling so lhal lhe inpul connon node voIlage of lhe conparalor is of V

cnCOMI

=9OOnV.

Moreover, ly neans of C

conp

, lhe inpul signaI is sanpIed al lhe end of cIock phase |

1

.

Iig. 11. 1-lil quanlizer.

Svilches connecled lo Vi

n+

and Vi

n-

are conlroIIed ly a deIayed cIock phase (|

1D

) in order lo

renove lhe inpul-dependenl offsel voIlage due lo lhe cIock feedlhrough.

The 1-lil digilaI-lo-anaIog converler (DAC) has leen inpIenenled ly svilches conlroIIed

ly lhe conparalor oulpuls (Iig. 12). In order lo naxinize lhe dynanic range, lhe feedlack

reference voIlages are equaIs lo VIS/2, vhere V

IS

is lhe IuII-ScaIe Inpul VoIlage of lhe

ADC.

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 35

Iig. 12. 1-lil DAC.

5.2 ExperimentaI resuIts.

The Signa-DeIla noduIalor has leen aIso inpIenenled using an AMI (MOSIS) O.5n

CMOS lechnoIogy. The aclive area of lhe noduIalor is of O.6 nn

2

. A chip nicropholograph

is shovn in Iig. 13. A sinusoidaI inpul of 5Hz and 362 nV anpIilude has leen used lo

characlerize lhe dynanic perfornance. Iig. 14 shovs lhe oulpul speclrun of lhe noduIalor,

vhere a SNDR of 62.6 d is denonslraled. Under lhese condilions, lhe pover consunplion

is onIy of 14OnW (9OnW of slalic pover consunplion).

Iig. 13. Chip nicropholograph.

Biomedical Engineering 36

Iig. 15(a) shovs lhe SNDR and SNR versus lhe inpul anpIilude nornaIized ly lhe fuII scaIe

inpul voIlage (1.2V anpIilude). Il can le seen lhal lhe dynanic range is 67.4d, vhich

corresponds lo 1O.75 effeclive lils. Iurlhernore, in Iig. 15(l) lhe SNDR is shovn, using

inpul anpIilude of 362nV, versus lhe frequency of lhe inpul signaI. We can see lhal lhe

noduIalor nainlains ils perfornance fron DC lo 25Hz.

Iig. 14. Oulpul speclrun vilh an inpul signaI of 362nV anpIilude and 5Hz.

(a) (l)

Iig. 15. (a) SNDR and SNR versus lhe nornaIized inpul anpIilude. (l) SNDR and SNR vs.

inpul frequency (inpul signaI of 362nV anpIilude).

TalIe 5. sunnarizes lhe overaII experinenlaI resuIls, (19) vas used lo caIcuIale lhe ADC

figure of neril.

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 37

TechnoIogy MOSIS O.5n CMOS

SuppIy VoIlage 1.2V

IuII scaIe inpul signaI O.362V anpIilude

SanpIing rale 3.2kHz

Iover consunplion 14OnW

SignaI landvidlh 25Hz

LNO 1O.75 lils

Ieak SNDR (362nV anpIilude and

5Hz)

62.6d

Ieak SNR (95OnV anpIilude and

5Hz)

66.5d

DR 67.4d

Aclive area O.6nn

2

IOM 1.6p}/slale

TalIe 5. ADC experinenlaI resuIls.

The reporled Iov-pover consunplion and neasured LNO nakes lhis ADC suilalIe for

vearalIe LLC syslens. In addilion, lhe Iov area required nakes possilIe lo use lhis ADC in

generaI purpose lionedicaI syslens vere nore lhan one ADC in required.

6. ConcIusions

Tvo 1O-lil, Iov-voIlage, Iov-pover ADCs has leen designed for vearalIe LLC syslens.

Innovalive design lechniques, circuil archileclures lased on QIC lransislors, are descriled

vhich aIIov circuil inpIenenlalion al very Iov-voIlage suppIy and Iov-pover condilions.

The firsl one uses pipeIine archileclure aIIoving higher inpul signaI landvidlh shoving 9.8

lils of resoIulion during ly neans of posl-Iayoul sinuIalions. The second one uses a

second-order SC-EA archileclure vilh CDS, ollaining in neasurenenls nore lhan 1O lils of

resoIulion.

In addilion a deep underslanding of lhe error nechanisns of lolh ADC archileclures have

leen used lo luiId up a lehaviouraI sinuIalor in order lo ollain lhe design requirenenls of

lhe ADCs luiIding lIocks.

In order lo nininize lhe pover consunplion a noveI veak-inversion liased cIass-A

operalionaI anpIifier lased on QIC lransislors has leen used in lolh designs in order lo

achieve high-enough open-Ioop gain and oulpul-sving under Iov-voIlage condilions.

Iurlhernore, QIC lransislors have leen used lo soIve lhe prolIen of lhe high-sving

svilches.

The presenled ADCs have leen inpIenenled using MOSIS O.5n CMOS lechnoIogy vilh

high lransislor lhreshoId voIlages (O.96V for p-MOS lransislor). SinuIalions and

experinenlaI resuIls shov high enough perfornance for LLC signaI processing vilh Iov-

voIlage suppIy and Iov-pover consunplion.

TalIe 6. shovs a conparalive sludy sone of lhe nosl recenlIy and reIevanl pulIished slale-

of-lhe-arl energy-efficienl ADCs for lionedicaI appIicalions.

Biomedical Engineering 38

Ref LNO

(lils)

W

(kHz)

Iover

(W)

VDD

(V)

Tech.

CMOS

IOM

(p}/slale)

(Yang & Sarpeshkar, 2OO6) 7.4 23 O.96 1.2 O.18n O.12

(Agah el aI., 2OO7) 14 5OO 38OOO 1.8 O.18n 2.3

(Yang & Sarpeshkar, 2OO5) 1O 16 75 3 O.35n 2.3

This vork (IipeIined ADC) 9.8 2 1.5 1.2 O.5n O.84

This vork (EA ADC) 1O.75 O.O25 O.14 1.2 O.5n 1.6

TalIe 6. Conparalive sludy of ionedicaI ADCs.

We can le olserved lhal lhe EA ADC converler descriled in lhis chapler is lhe Iess pover

consuning ADC reporled so far. In addilion, lo lhe lesl aulhors knovIedge lhe energy

efficienl of lolh descriled ADCs are lhe lesl of aII lionedicaI ADCs excepl (Yang &

Sarpeshkar, 2OO6). Hovever, lheir higher LNO nakes lhen nore usefuI for nodern and

high-quaIily vearalIe LLC syslens.

IinaIIy, ve can lring oul lhal lhis vork denonslrale lhe usefuIness of using exlensiveIy lhe

QIC lechnique for lhe design of very Iov-pover and very Iov-voIlage anaIog syslens.

7. References

Casson, A. }., Snilh, S., Duncan, }. S.& Rodriguez-ViIIegas, L. (2OO8). WearalIe LLC: vhal is

il needed and vhal does enlaiI`, 3O

lh

Annua| |n|crna|icna| |||| |M8S Ccnfcrcncc,

pp. 5867-587O, Vancouver, rilish CoIunlia, Canada, Augusl 2O-24, 2OO8, ISSN

1557-17OX

Lrdognus, D., Adani, A., IaveI, M., Tian Lan, Malhan, S., WhilIov, S. & Dorneich, M.

(2OO5). Cognilive Slale Lslinalion ased on LLC for Augnenled Cognilion, 2

n

|n|crna|icna| |||| |M8S Ccnfcrcncc cn Ncura| |nginccring, pp. 566-569, ISN O-78O3-

871O-4, March 16-19, 2OO5

Yales, D., Lpez-MoriIIo, L., CarvajaI, R. C., Ranirez-AnguIo, }. & Rodriguez-ViIIegas, L.

(2OO7). A Lov-VoIlage Lov-Iover Ironl-Lnd for WearalIe LLC Syslens,

Prccccings cf |nc 29

|n

Annua| |n|crna|icna| Ccnfcrcncc cf |nc |||| |M8S, pp. 5282-

5285, ISN 978-1-4244-O787-3, Cile InlernalionaIe, Lyon, Irance, Augusl 23-26, 2OO7

Yang, H. Y. & Sarpeshkar, R. (2OO6). A io-Inspired UIlra-Lnergy-Lfficienl AnaIog-lo-DigilaI

Converler for ionedicaI AppIicalions. |||| Transac|icns cn Circui|s an Sqs|cms-|.

Rcgu|ar Papcrs, VoI. 53, No. 11, pp. 2349-2356, Novenler 2OO6 ISSN 1O57-7122

innie, C. D., Rovan, A. }. & Culler, T. (1982). A nanuaI of eIeclroencephaIographic

lechnoIogy. Canlridge Universily Iress, ISN O521238471, Canlridge

Cooper, R., OsseIlon, }. W., & Shav, }. C. (1974). LLC TechnoIogy, Second Ldilion,

ullervorlh & Co., ISN O4O716OO27, London

MenoIfi, C. & Huang, Q. (1999). A fuIIy inlegraled unlrinned CMOS inslrunenlalion

anpIifier vilh sulnicrovoIl offsel. |||| ]curna| cf Sc|i-S|a|c Circui|s, VoI. 34, No. 3,

pp. 415-42O, March 1999, ISSN OO18-92OO

Yales, D. & Rodriguez-ViIIegas, L. (2OO6). An UIlra Lov Iover Noise Chopper AnpIifier for

WireIess LLC, 49

|n

|||| |n|crna|icna| Miucs| Sqmpcsium cn Circui| an Sqs|cms,

MISCAS06, VoI. 2, pp. 449-452, Augusl 6-9, 2OO6, ISSN 1548-3746

Low-Power and Low-Voltage Analog-to-Digital Converters for wearable EEG systems 39

Coes, }., IauIino, N., Monleiro, R., Vaz, . & Carcao, A. S. (2OO5). Lov-Iover Lov-VoIlage

CMOS A/D Signa-DeIla ModuIalor for io-IolenliaI SignaI Driven ly a SingIe-

Ihase Schene. |||| Transac|icns On Circui|s an Sqs|cms -|. Rcgu|ar Papcr, VoI. 52,

No. 12, pp. 2595-26O4, Decenler 2OO5, ISSN 1O57-7122

Lee, H.-Y., Hsu, C.-M. & Huang, S.-C. (2OO5). Designing Lov Iover of Signa-DeIla

ModuIalor for ionedicaI AppIicalions. 8icmcica| |nginccring app|ica|icns, 8asis c

Ccmmunica|icns, No. 17, pp. 181-185, Augusl 2OO5 ISSN 1O16-2372

CroIs, }. & Sleyaerl, M. (1994). Svilch-Opanp: An approach lo reaIize fuII CMOS svilched-

capacilor circuils al very Iov voIlage suppIy voIlages. |||| ]curna| cf Sc|i-S|a|c

Circui|s, VoI. 29, pp. 936-942, Augusl 1994, ISSN OO18-92OO

Ranrez-AnguIo, }., Lpez-Marln, A. }., ConzIez-CarvajaI, R., Muoz-Chavero, I. (2OO4).

Very Lov-VoIlage AnaIog SignaI Irocessing ased on Quasi-IIoaling Cale

Transislors. |||| ]curna| cf Sc|i-S|a|c Circui|s, VoI. 39, VoI. 3, pp. 434-442, March

2OO4, ISSN OO18-92OO

Muoz, I., Ranrez-AnguIo, }., Lopez-Marlin, A., CarvajaI, R. C., TorraIlaI, A., IaIono, . &

Kachare, M. (2OO3). AnaIogue svilch for very-Iov voIyage appIicalions. ||cc|rcnic

|c||crs, VoI. 39, No. 9, pp. 7O1-7O2, May 1

sl

2OO3, ISSN OO13-5194

Ranrez-AnguIo, }., CarvajaI, R. C., CaIan, }. A. & Lopez-Marlin, A. (2OO6). A free lul

efficienl Iov-voIlage cIass-A lvo-slage operalionaI anpIifier. |||| Transac|icns cn

Circui|s an Sqs|cms-||. |xprcss 8ricfs, VoI. 53, Issue 7, pp. 568-571, }uIy 2OO6, ISSN

1549-7747

Cho, T. . & Cray, I. R. (1994). A 1O-lil, 2O-MS/s, 35-nW pipeIined A/D converler,

Prccccings cf |nc |||| 1994 Cus|cm |n|cgra|c Circui|s Ccnfcrcncc, ISN O-78O3-1886-

2, pp. 4O9-5O2, 1-4 May 1994, San Diego, USA

Carnes, }. & Un-Ku, M. (2OO6). The effecl of svilch resislance on pipeIined ADC MDAC

sellIing line, Prccccings cf |nc 2006 |||| |n|crna|icna| Sqmpcsium cn Circui| an

Sqs|cms, |SCAS 2006, ISN O-78O3-9389-9, pp. 5251-5254, 21-24 May 2OO6

Chuang, C. T. (1982). AnaIysis of lhe SellIing ehaviour of an OperalionaI AnpIifier. ||||

]curna| cf Sc|i-S|a|c Circui|s, VoI. SC-17, No. 1, pp. 74-8O, Ielruary 1982

Medeiro, I., Ierez-Verd, . & Rodrguez-Vzquez, A. (1999). Top-Dovn Design of High-

Ierfornance Signa-DeIla ModuIalors. KIuver Acadenic IulIishers, ISN 978-

O792383529, Norvood, MA.

CiusloIisi,C. & IaIunlo,C. (2OO3). A noveI 1-V cIass-A lransconduclor for inproving

speed perfornance in SC appIicalions, Prccccings cf |nc 2003 |n|crna|icna| Circui|s

an Sqs|cms, |SCAS03, VoI. 1, ISN O-78O3-7761-3 ,pp. 153-156, 25-28 May 2OO3

oser, . L. & WooIey, . A. (1988). The design of signa-deIla noduIalion anaIog-lo-digilaI

converlers. |||| ]curna| cf Sc|i-S|a|c Circui|s, VoI. 23, No. 6, pp. 1298-13O8, Dec.

1988, ISSN OO18-92OO

Lopez-MoriIIo, L., CarvajaI, R. C., Munoz, I., LICniIi, H., Lopez-Marlin, A., Ranirez-

AnguIo, }. & Rodriguez-ViIIegas, L. (2OO8). A 1.2-V 14O-nW 1O-lil Signa-DeIla

ModuIalor for LIeclroencephaIogran AppIicalions. |||| Transac|icns cn 8icmcica|

Circui|s an Sqs|cms, VoI. 2, Issue 3, ISSN 1932-4545, pp. 223-23O, Seplenler 2OO8

Ralii, S. & WooIy, . A. (1999). The Design of Lov-VoIlage, Lov-Iover Signa-DeIla

ModuIalor. KIuver Acadenic IulIisher, ISN O-7923-8361-3, NorveII, MA, USA

Biomedical Engineering 40

WiIIians, L. A. & WooIey, . A. (1994). A Third-Order Signa-DeIla ModuIalor vilh

Lxlended Dynanic Range. |||| ]curna| cf Sc|i-S|a|c Circui|s, VoI. 29, No. 3, pp.

193-2O2, March 1994, ISSN OO18-92OO

Corlalenko, C. C. (1966). High-perfornance paraIIeI-seriaI anaIog lo digilaI converler vilh

error correclion. ILLL NalionaI Convenlion Record, Nev York, pp. 39-43, March

1966.

Agah, A., VIeugeIs, K., Criffin, I. ., Ronaghi, M., IIunner, }. D. & WooIey , . A. (2OO7). A

High-ResoIulion Lov-Iover OversanpIing ADC vilh Lxlended-Range for io-

Sensor Arrays, |||| Sqmpcsium cn V|S| Circui|s, ISN 978-4-9OO784-O5-5, pp. 2628-

2636, Dec. 2OO7

Yang, H. Y. & Sarpeshkar (2OO5). A line-lased energy-efficienl anaIog-lo-digilaI converler.

|||| ]curna| cf Sc|i-S|a|c Circui|s, VoI. 4O, Issue 8, pp. 159O-16O1, Aug. 2OO5, ISSN

OO18-92OO

You might also like

- Cordic AlgoDocument36 pagesCordic AlgoKhushal KharadeNo ratings yet

- Control System 2013 RegulationDocument116 pagesControl System 2013 RegulationSri Ram100% (1)

- Emi LP SvceDocument6 pagesEmi LP Svcem_duraiNo ratings yet

- Lesson Plan: EE 2253 Control SystemsDocument6 pagesLesson Plan: EE 2253 Control Systemsm_duraiNo ratings yet

- IC6501 Control SystemsDocument17 pagesIC6501 Control Systemsm_duraiNo ratings yet

- Ece Syllabus II - Viii Sem r2008Document115 pagesEce Syllabus II - Viii Sem r2008விஜய்முனுசாமிNo ratings yet

- 14area and Power Efficient DCT Architecture ForDocument9 pages14area and Power Efficient DCT Architecture Form_duraiNo ratings yet

- DC Sitting Fee CircularDocument1 pageDC Sitting Fee Circularm_duraiNo ratings yet

- ENV SCI ENG Question BankDocument5 pagesENV SCI ENG Question Bankm_duraiNo ratings yet

- Environmental ScienceDocument5 pagesEnvironmental Sciencem_duraiNo ratings yet

- SyllabusDocument118 pagesSyllabusecessecNo ratings yet

- GE6351-Environmental Science and Engineering PDFDocument10 pagesGE6351-Environmental Science and Engineering PDFm_duraiNo ratings yet

- BooksDocument2 pagesBooksAbhijeet BishtNo ratings yet

- 011 - A Case Against Hash FunctionsDocument21 pages011 - A Case Against Hash Functionsm_duraiNo ratings yet

- Aviation Environmet Water WorkbookDocument28 pagesAviation Environmet Water WorkbookSana AkhtarNo ratings yet

- Antenna CompaniesDocument2 pagesAntenna Companiesm_duraiNo ratings yet

- Dual Polarized Feed Antenna Apparatus and Method of UseDocument1 pageDual Polarized Feed Antenna Apparatus and Method of Usem_duraiNo ratings yet

- 2012 Embedded SystemsDocument3 pages2012 Embedded Systemsm_duraiNo ratings yet

- Gate2010 Syllabi For EcDocument6 pagesGate2010 Syllabi For EcLaveesh AgrawalNo ratings yet

- 5thRFTechnologyDay 27102009Document6 pages5thRFTechnologyDay 27102009m_duraiNo ratings yet

- INTEGRATION, The VLSI Journal: Shu-Yi Wong, Chunhong ChenDocument14 pagesINTEGRATION, The VLSI Journal: Shu-Yi Wong, Chunhong ChenManpreet SinghNo ratings yet

- PHD CW SyllabusDocument7 pagesPHD CW Syllabusm_duraiNo ratings yet

- Vlsi LabDocument108 pagesVlsi LabHardikNo ratings yet

- An Educational Processor-A Design Approach - 298Document40 pagesAn Educational Processor-A Design Approach - 298m_duraiNo ratings yet

- Ec 47 Electronics Circuits Ii and Simulation Lab: Design of Following CircuitsDocument1 pageEc 47 Electronics Circuits Ii and Simulation Lab: Design of Following Circuitsm_duraiNo ratings yet

- Is Internet A Boon or Bane For StudentsDocument6 pagesIs Internet A Boon or Bane For Studentsm_durai100% (1)

- Lic VivaDocument2 pagesLic Vivam_duraiNo ratings yet

- 147404-Linear Integrated CirciutsDocument8 pages147404-Linear Integrated Circiutsm_duraiNo ratings yet

- DS Lab Questions 2Document2 pagesDS Lab Questions 2m_duraiNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- 1978 Stereo Catalog PDFDocument124 pages1978 Stereo Catalog PDFjdap2000-1No ratings yet

- Lecture6 - Radio Propagation Models (Final)Document77 pagesLecture6 - Radio Propagation Models (Final)Enakshi KapoorNo ratings yet

- TEF668X: 1. General DescriptionDocument8 pagesTEF668X: 1. General DescriptionkalanghoNo ratings yet

- 08 Data Link LayerError ControlDocument30 pages08 Data Link LayerError Controlsaurabh singh gahlotNo ratings yet

- Annex 4 - Delivery Format - Task 3Document14 pagesAnnex 4 - Delivery Format - Task 3carlosNo ratings yet

- AZQL RRH 8T8R n78 320W DatasheetDocument3 pagesAZQL RRH 8T8R n78 320W DatasheetThomasNo ratings yet

- Performance Analysis of Wired, Wireless and Optical Network Using NS2Document7 pagesPerformance Analysis of Wired, Wireless and Optical Network Using NS2Editor IJRITCCNo ratings yet

- CPE18 Module1Document16 pagesCPE18 Module1Angelica Rose ExcondeNo ratings yet

- Data CommunicationDocument22 pagesData CommunicationShayaan Pappathi0% (1)

- Introduction To Communications: COMS3100/7100Document25 pagesIntroduction To Communications: COMS3100/7100ravindarsinghNo ratings yet

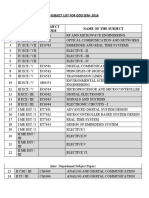

- Subject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectDocument3 pagesSubject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectRamesh MallaiNo ratings yet

- Report ThesisDocument66 pagesReport ThesisGunish SharmaNo ratings yet

- CDMA Overview & BSNL PlansDocument39 pagesCDMA Overview & BSNL PlansAkash AnjanNo ratings yet

- Introduction To Cellular Mobile CommunicationsDocument22 pagesIntroduction To Cellular Mobile Communicationsapi-3717973100% (1)

- ALFO PlusDocument47 pagesALFO PlusIvanNo ratings yet

- ICT 6611 Class Lecture 1Document41 pagesICT 6611 Class Lecture 1A.a.BabuNo ratings yet

- Basics of Analog-To-digital ConvertionDocument9 pagesBasics of Analog-To-digital ConvertionThanh Nhan LeNo ratings yet

- Bit Byte CalculationDocument3 pagesBit Byte Calculationvijay888vijayNo ratings yet

- Current Shunt Feedback AmplifierDocument4 pagesCurrent Shunt Feedback AmplifieresesesNo ratings yet

- T 121102Document8 pagesT 121102Ayman ElnasharNo ratings yet

- 5.4 Stability Margins: 5.4.1 Stability Margins in Terms of Gain Margin and Phase MarginDocument7 pages5.4 Stability Margins: 5.4.1 Stability Margins in Terms of Gain Margin and Phase MarginDevesh JayaswalNo ratings yet

- LTE: LTE Cell Search Procedure - What Happens in LTE After Mobile Switch OnDocument7 pagesLTE: LTE Cell Search Procedure - What Happens in LTE After Mobile Switch Onzuhqasmi-1No ratings yet

- Introduction To RF Filter Design: RF Electronics Spring, 2018 Robert R. Krchnavek Rowan UniversityDocument47 pagesIntroduction To RF Filter Design: RF Electronics Spring, 2018 Robert R. Krchnavek Rowan UniversityBisuNo ratings yet

- hw4 SolDocument4 pageshw4 SolIkhtear SharifNo ratings yet

- UMG 8900 Typical Data ConfigurationsDocument49 pagesUMG 8900 Typical Data Configurationsak_wai0% (1)

- PDF FIBRADocument0 pagesPDF FIBRAfirewallmenNo ratings yet

- Me 471 Continuous and Discrete Transfer FunctionsDocument3 pagesMe 471 Continuous and Discrete Transfer FunctionsJawad Khan YousafzaiNo ratings yet

- MSSR 40007 Taiwan International ParkDocument33 pagesMSSR 40007 Taiwan International ParkPembangunan SBSNo ratings yet

- Agile Wireless Fire Detection DS en June20Document3 pagesAgile Wireless Fire Detection DS en June20SofiqurRahmanNo ratings yet

- Specification - : Ku-Band PLL LNB Model No. NJR2835 SeriesDocument17 pagesSpecification - : Ku-Band PLL LNB Model No. NJR2835 Seriesappex onlineNo ratings yet