Professional Documents

Culture Documents

10 1 1 117

Uploaded by

Anil SainiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

10 1 1 117

Uploaded by

Anil SainiCopyright:

Available Formats

Journal of the Korean Physical Society, Vol. 40, No. 1, January 2002, pp.

47

Design of a New Low-Power 2.4 GHz CMOS LNA

Ickjin Kwon and Hyungcheol Shin

Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Taejon 305-701 (Received 11 February 2001) A 2.4-GHz single-stage CMOS low noise amplier (LNA) structure with ultra low power consumption is proposed. A current reuse technique is used to decrease power dissipation with increasing amplier transconductance for the LNA. Thus, the same amplier transconductance for the LNA will be achieved at decreased power dissipation. Also, due to the use of an inverter-type amplier which has a symmetric structure, the proposed LNA has high linearity. The designed 2.4- GHz LNA using 0.25-m CMOS technology achieves a power gain of 14.7 dB, a noise gure of 2.5 dB, and an IIP3 of 0.5 dBm even at a power consumption of 1.97 mW.

PACS numbers: 84.40.Dc

I. INTRODUCTION CMOS integrated circuit for wireless applications in the 2.4 GHz frequency range are receiving much attention due to their potential for low cost and the prospect of system on a chip integration, although bipolar and GaAs are currently the preferred technology [1,2]. Power consumption is very important in wireless communication system. However, the low-noise amplier (LNA), which is a key building block for the RF front-end of the receiver, typically has high power consumption. While recent works have demonstrated the potential of CMOS LNAs, they generally have diculty in attaining low power consumption to meet the required specications. Previous CMOS LNAs have had a typical power consumption of several tens of milliwatts [36]. In this work, we propose a new CMOS LNA structure which meets the requirement of typical performance with ultra low power consumption. A current reuse technique is applied to increase the amplier transconductance for the LNA without increasing the power dissipation, compared to standard technology. Thus, the same amplier transconductance for the LNA will be achieved at decreased power dissipation. Also, due to the use of an inverter-type amplier which has a symmetric structure, the proposed LNA has high linearity.

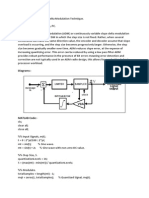

LNA with inductive degeneration at the source. In this topology, a current reuse method is applied to achieve a high transconductance with less current. M1 operates as a common-source stage, and M2 and M3 operate as inverter-type amplier stages. However, they share the same bias current. The signal amplied by M1 is coupled to the gate of M2 by C1 while the source of M2 is bypassed by C2 . The circuit thus saves power through the reuse of the bias current, so a single stage has sucient power gain with minimized low power dissipation. Also, it is possible to achieve high forward gain and low reverse gain. Low reverse gain is desired to provide sucient isolation and to simplify input and output matching. Also,

II. DESIGN OF THE LNA Figure 1 shows a schematic of the proposed CMOS low-noise amplier. The structure is a single- stage

E-mail:

ijkwon@inca.kaist.ac.kr

Fig. 1. Proposed CMOS LNA circuit diagram. M1 operates as a common-source stage, and M2 and M3 operate as inverter-type amplier stages. They share the same bias current. -4-

Design of a New Low-Power 2.4 GHz CMOS LNA Ickjin Kwon and Hyungcheol Shin

-5-

an inverter-type LNA shows better linearity when a symmetric structure is used. The bias voltage, Vg2 , is set to enable the symmetric operating point so that the PMOS and the NMOS networks have the largest dynamic range. The input device M1 is biased through bias tee of Lb and Cb . Ld is implemented as an on-chip spiral inductor. Lout and Cout are used for output matching. The use of inductive degeneration has the benet of simultaneously achieving both input and noise matching. The series feedback in the source provides a real impedance of approximately (gm1 /Cgs1 )Ls to the input, where Ls can be realized with a bond-wire inductor. The input impedance of M1 is given by Zin = j(Lg + Ls ) +

Fig. 2. Theoretical prediction of the noise gure for several power dissipations. An optimum QL of 4.5 is obtained.

1 gm1 Ls + + Rg . jCgs1 Cgs1

(1)

Inductors Ls and Lg form an impedance matching network with the gate capacitance Cgs of M1 . The matching conditions to Rs give Ls = (Rs Rg )Cgs1 , gm1 1

2 o Cgs1

(2)

Lg =

Ls ,

(3)

Fig. 3. Theoretical prediction of the minimum noise gure (NFmin ) versus power dissipation.

where o is the operation frequency. To realize a gain of 15 dB at 2.4 GHz, Ls is of the order of 1 2 nH, which is the range to be implemented as a bondwire. The input matching of the LNA, therefore, requires only one external inductor, Lg . The size of transistor M1 determines the optimum input noise match or, equivalently, sets the quality factor of the input matching network, QL . The power consumption versus noise gure has been optimized with the method described by Shaeer and Lee [3]. The LNA noise factor and the quality factor can be written as

F =1+

Rl Rg + + gd0 Rs Rs Rs

1+2

2 2 QL |c| + [1 + Q2 ] , L 5 5

(4)

zQL =

o (Ls + Lg ) 1 = , Rs o Cgs Rs

(5)

where is 2/3 in the long channel theory and it is higher than 2/3 in the sub-micron technology. Cgs1 can be writ2 ten as 3 W1 L1 Cox . The noise gure (NF) prediction versus quality factor QL for several power dissipations are shown in Fig. 2. The minimum noise gure exists for a particular QL , as shown in Fig. 2. To reduce the effects of induced-gate noise, QL cannot be made arbitrarily large. Additionally, a large QL will result in a large value for Lg , which can cause input matching variances

due to the tolerances of both Lg and the gate capacitance of M1 . The M1 bias current was chosen to be 1 mA, which closely follows the 2-mW power dissipation curve in Fig. 2. Thus, an optimum QL of 4.5 is obtained to avoid the steep slope part of the noise gure curve. The desired QL value gives an optimum gate width, W, of 300 m for transistor M1 at an input signal frequency of 2.4 GHz. The sizes of M2 and M3 were chosen to be the same as M1 . Figure 3 shows a plot of the theoretical minimum noise gure versus power dissipation. In our design, power dissipation is constrained to 2 mW, and the minimum noise gure is predicted to be 2.5 dB.

-6-

Journal of the Korean Physical Society, Vol. 40, No. 1, January 2002

Fig. 4. Power gain (S21 ) and noise gure (NF) of the LNA. LNA achieves a forward gain of 14.7 dB and a NF of 2.5 dB at 2.4 GHz. The power consumption is only 1.97 mW.

Fig. 6. Reverse isolation (S12 ) of the LNA. The reverse isolation is more than 28 dB.

III. RESULTS AND DISCUSSION The LNA is designed for a standard 0.25-m CMOS technology. An HP ADS was used for circuit design and simulation. Figure 4 shows a plot of the power gain (S21 ) and the noise gure (NF) versus frequency for the LNA. At a 2-V supply, the LNA achieves a forward gain of 14.7 dB and a NF of 2.5 dB at 2.4 GHz. The power consumption is only 1.97 mW, and a theoretical minimum noise gure of 2.5 dB is obtained. The bandpass nature of the LNA is shown in Fig. 4. Figure 5 shows the input and the output reection coecients (S11 and S22 ). S11 and S22 are 19.5 dB and 21.6 dB, respectively. The input and the output matchings at 2.4 GHz are very good (below 15 dB). The reverse isolation for the LNA, shown in Figure 6, is good with an isolation of more than 28 dB. A two-tone IP3 simulation was performed on the LNA, and the results are shown in Fig. 7. The two tones were

applied with equal power at 1.499 GHz and 1.501 GHz. The magnitude of the fundamentals and the third-order intermodulation products at the output are shown, and the obtained input-referred third-order intercept point (IIP3) is 0.5 dBm (+15.3 dBm output-referred). The linearity is primarily limited by the output-stage transistors M2 and M3 . Due to the use of an inverter-type amplier which has a symmetric structure, the proposed LNA is very linear. Table 1 shows a summary of the proposed 2.4 GHz CMOS LNA characteristics. Good performance of the LNA was obtained even at a very low power consumption of 1.97 mW.

IV. CONCLUSION In this paper, we have proposed a 2.4-GHz single-stage LNA with ultra low power consumption. The LNA has been designed in a standard 0.25-m CMOS technology.

Fig. 5. Input and output reection coecient (S11 and S22 ) of the LNA. S11 and S22 are 19.5 dB and 21.6 dB, respectively, at 2.4 GHz.

Fig. 7. LNA intermodulation product and IP3 (two-tone simulation). The obtained input-referred third-order intercept point (IIP3) is 0.5 dBm.

Design of a New Low-Power 2.4 GHz CMOS LNA Ickjin Kwon and Hyungcheol Shin Table 1. Summary of the proposed LNA performance. Simulation results 2.4 GHz 14.7 dB 2.5 dB 1.97 mW 2V 0.5 dBm < 28 dB 0.25-m CMOS

-7-

fo Gain NF Power Vdd IIP3 S12 Technology

nology (MOST) and by the Korea Science and Engineering Foundation (KOSEF) through the Micro Information and Communication Remote Object-oriented Systems (MICROS) research center at Korea Advanced Institute of Science and Technology (KAIST), Korea.

REFERENCES

Good noise and gain performances were obtained at a low power consumption of only 1.97 mW. A noise gure of 2.5 dB and a power gain of 14.7 dB were achieved for the proposed LNA. Also, a high IIP3 of 0.5 dBm, which shows the good linearity characteristics, was obtained.

ACKNOWLEDGMENTS This work was supported by the Tera-level Nanodevice project of the Korea Ministry of Science and Tech-

[1] E. Song, S.-I. Chae and W. Kim, J. Korean Phys. Soc. 35, S918 (1999). [2] D. An, E.-H. Rhee, J.-K Rhee and S.-D Kim, J. Korean Phys. Soc. 37, 837 (2000). [3] D. Shaeer and T. Lee, IEEE J. Solid-State Circuits 32, 745 (1997). [4] A. Karanicolas, IEEE J. Solid-State Circuits 3, 1939 (1996). [5] Q. Huang, P. Orsatti and F. Piazza, in Proc. IEEE 1998 Custom Integrated Circuit Conference, 67-70 (1998). [6] B. Floyd, J. Metha, C. Gamero and K. O., in Proc. IEEE 1999 Custom Integrated Circuit Conference, 661664 (1999).

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- JBL DA6502 User Manual20161015813102Document8 pagesJBL DA6502 User Manual20161015813102Ken LocNo ratings yet

- Accessories List 20190425 PDFDocument12 pagesAccessories List 20190425 PDFpepitoNo ratings yet

- Lte Binjai Timur L2100 NMSDocument915 pagesLte Binjai Timur L2100 NMSJefril FaanaNo ratings yet

- Network Slicing 5g Beyond NetworksDocument153 pagesNetwork Slicing 5g Beyond Networksshreyansh100% (6)

- AD9833 Waveform GeneratorDocument20 pagesAD9833 Waveform GeneratorSimão VarelaNo ratings yet

- Digital Comunication 2 MarksDocument22 pagesDigital Comunication 2 Marksshankar100% (2)

- NL 2611cb3 Plus Manual v1 0Document18 pagesNL 2611cb3 Plus Manual v1 0stankevichijusNo ratings yet

- ENGR. Rolando CampillosDocument5 pagesENGR. Rolando CampillosJohnRichieLTanNo ratings yet

- Power Delay Profile: p (τ) multipath channelDocument5 pagesPower Delay Profile: p (τ) multipath channelAli MohamedNo ratings yet

- Atm&Ip Dual Stack (Ran16.0 - 01)Document54 pagesAtm&Ip Dual Stack (Ran16.0 - 01)hekriNo ratings yet

- Lab # 4 Time Response AnalysisDocument7 pagesLab # 4 Time Response AnalysisGökhan YüksekNo ratings yet

- Quick Card T Berd Mts 5800 Ethernet Layer 2 Traffic Quick References en PDFDocument4 pagesQuick Card T Berd Mts 5800 Ethernet Layer 2 Traffic Quick References en PDFThangNo ratings yet

- Ashok Kumar Verma ResumeDocument2 pagesAshok Kumar Verma ResumeManish ChaturvediNo ratings yet

- Unit 1Document175 pagesUnit 1Karthikeya SharmaNo ratings yet

- Adaptive Delta ModulationDocument4 pagesAdaptive Delta Modulationhanishsingla0241No ratings yet

- LTE FemtocellsDocument16 pagesLTE FemtocellsfarrukhmohammedNo ratings yet

- Propagation Channel ModelsDocument17 pagesPropagation Channel Modelsgame__overNo ratings yet

- Lecture Notes ON Satellite Communication: Final Year B. TechDocument30 pagesLecture Notes ON Satellite Communication: Final Year B. Techpradnya patilNo ratings yet

- Switching Mod and Envelope DetectorDocument7 pagesSwitching Mod and Envelope DetectorNiranjan KumarNo ratings yet

- Chapter 9 - Ethernet: CCNA Exploration 4.0Document90 pagesChapter 9 - Ethernet: CCNA Exploration 4.0kiennaNo ratings yet

- One Time PadDocument7 pagesOne Time PadNatasaDabicNo ratings yet

- EEL201 SS Tutorial Sheet 3 PDFDocument1 pageEEL201 SS Tutorial Sheet 3 PDFShubhamMittalNo ratings yet

- Electromagnetic WaveDocument32 pagesElectromagnetic WaveClrs BchnNo ratings yet

- S Parameter BasicsDocument20 pagesS Parameter BasicsMihailNo ratings yet

- IEEE Paper On Mobile and Cellular Technologies Based On The Title Gi FiDocument9 pagesIEEE Paper On Mobile and Cellular Technologies Based On The Title Gi FiSuganya Periasamy100% (2)

- (Chapter 19) Cellular Telephone Concepts (117-124) PDFDocument8 pages(Chapter 19) Cellular Telephone Concepts (117-124) PDFVernaNo ratings yet

- Amateur Technician Exam Study GuideDocument70 pagesAmateur Technician Exam Study GuideJorge Basulto100% (2)

- Wavelet Packet: A Multirate Adaptive Filter For De-Noising of TDM SignalDocument6 pagesWavelet Packet: A Multirate Adaptive Filter For De-Noising of TDM Signalsatya.tvv5820No ratings yet

- LtAP Mini - BrosuraDocument2 pagesLtAP Mini - BrosuraDexter ProNo ratings yet

- Updated Operational Amplifier Selection Guide For Optimum Noise PerformanceDocument2 pagesUpdated Operational Amplifier Selection Guide For Optimum Noise PerformancennliceNo ratings yet