Professional Documents

Culture Documents

Micro Control Adores Pic

Uploaded by

IANROCK0 ratings0% found this document useful (0 votes)

10 views191 pagesCopyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views191 pagesMicro Control Adores Pic

Uploaded by

IANROCKCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 191

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

1

INDICE:

Descripcin Funcional.

Unidades Funcionales.

BIBLIOGRAFIA:

- PIC18F2455_2550_4455_4550 Data Sheet (www.microchip.com)

- PIC Microcontroller: An Introduction to Software & Hardware Interfacing - Huang - Ed.: Thompson

TEMA 3: MICROCONTROLADOR PIC18F4550

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

2

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / INTRODUCCION

MICROCONTROLADORES PIC`s

Los PIC`s de Microchip son los nmero 1 en ventas de microcontroladores

Ventajas de los microcontroladores PIC de Microchip

Amplia gama: gran variedad de familias que permiten adaptar el uC a las

necesidades de cada aplicacin

Herramientas de desarrollo comunes

Gran variedad de unidades funcionales embebidas (temporizadores,

USART,I2C, SPI, unidades de comparacion/captura/PWM, Convertidores

A/D, USB, receptores/transmisores de RF, Ethernet, etc...)

Precios competitivos

Buen soporte (datasheet, libros, notas de aplicacin, seminarios, mucha

informacin disponible en internet)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

3

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / INTRODUCCION

MICROCONTROLADORES PIC`s

Familias de microcontroladores PIC

PIC10: microcontroladores de 8 bits, de bajo coste, de 6 pines y bajas

prestaciones

PIC12: microcontroladores de 8 bits, de bajo coste, de 8 pines y bajas

prestaciones.

PIC16: microcontroladores de 8 bits, con gran variedad de nmero de pines

y prestaciones medias.

PIC18: microcontroladores de 8 bits, con gran variedad de nmero de pines

y prestaciones medias/altas.

PIC24: microcontroladores de 16 bits

dsPIC`s

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

4

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / INTRODUCCION

FAMILIA PIC18

Caractersticas fundamentales:

Arquitectura RISC avanzada Harvard: 16-bit con 8-bit de

datos.

77 instrucciones

Desde 18 a 80 pines

Hasta 64K bytes de programa (hasta 2 Mbytes en ROMless)

Multiplicador Hardware 8x8

Hasta 3968 bytes de RAM y 1KBytes de EEPROM

Frecuencia mxima de reloj 40Mhz. Hasta 10 MIPS.

Pila de 32 niveles.

Mltiples fuentes de interrupcin

Perifricos de comunicacin avanzados (CAN y USB)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

5

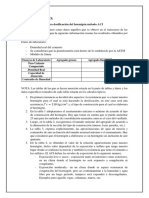

CARACTERISTICAS

Hasta 48MHz

0

10 Canales

PIC18F2455 PIC18F2450 PIC18F4455 PIC18F4450

Hasta 48MHz Hasta 48MHz Hasta 48MHz Frecuencia de Operacin

Memoria de Programa (bytes)

Memoria RAM de Datos (bytes)

Memoria EEPROM Datos (bytes)

Interrupciones

Lneas de E/S

Temporizadores

Mdulos de Comparacin/Captura/PWM (CCP)

Mdulos de Comparacin/Captura/PWM mejorado (ECCP)

Canales de Comunicacin Serie

Canal USB

Puerto Paralelo de Transmisin de Datos (SPP)

Canales de Conversin A/D de 10 bits

MSSP,EUSART

1

2

0

24

4

256

19

24.576

2.048

0

10 Canales

MSSP,EUSART

1

2

0

24

4

256

19

32.768

2.048

1

13 Canales

MSSP,EUSART

1

1

1

35

4

256

20

24.576

2.048

1

13 Canales

MSSP,EUSART

1

1

1

35

4

256

20

32.768

2.048

2

75 (83 ext.)

Comparadores analgicos

Juego de instrucciones

2

75 (83 ext.)

2

75 (83 ext.)

2

75 (83 ext.)

PDIP 28 pines

SOIC 28 pines Encapsulados

PDIP 40 pines

QFN 40 pines

TQFP 40 pines

PDIP 28 pines

SOIC 28 pines

PDIP 40 pines

QFN 40 pines

TQFP 40 pines

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / CARACTERISTICAS FUNDAMENTALES

MICROCONTROLADORES PIC18F2455, PIC18F2550, PIC18F4455 y PIC18F4550

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

6

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / CARACTERISTICAS FUNDAMENTALES

PATILLA1E DEL MICROCONTROLADOR PIC18F4550

1

9

8

7

6

5

4

3

2

11

18

17

16

15

14

13

12

10

19

29

28

27

26

25

24

23

22

21 20

40

39

38

37

36

35

34

33

32

31

30

MCLR/VPP/RE3

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT/RCV

RA5/AN4/SS/HLVDIN/C2OUT

RE0/AN5/CK1SPP

RE1/AN6/CK2SPP

RE2/AN7/OESPP

VDD

VSS

OSC1/CLKI

OSC2/CLKO/RA6

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2

(1)

/UOE

RC2/CCP1/P1A

VUSB

RD0/SPP0

RD1/SPP1

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/AN11/KBI0/CSSPP

RB3/AN9/CCP2/VPO

RB2/AN8/INT2/VMO

RB1/AN10/INT1/SCK/SCL

RB0/AN12/INT0/FLT0/SDI/SDA

VDD

VSS

RD7/SPP7/P1D

RD6/SPP6/P1C

RD5/SPP5/P1B

RD4/SPP4

RC7/RX/DT/SDO

RC6/TX/CK

RC5/D+/VP

RC4/D-/VM

RD3/SPP3

RD2/SPP2

P

I

C

1

8

F

4

4

5

5

P

I

C

1

8

F

4

5

5

0

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

7

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / CARACTERISTICAS FUNDAMENTALES

DIAGRAMA

DE BLOQUES

Table Pointer<21>

inc/dec logic

PCLATU PCLATH

PCU PCL PCH

Address Latch

21

Program Memory

(24/32 Kbytes)

Data Latch

Table Latch

IR

ROM Latch

8

Instruction bus <16>

Instruction

Decode &

Control

State Machines

Control Signals

RA0/AN0

RA2/AN2/VREF-/CVREF

RA4/T0CKI/C1OUT/RCV

OSC2/CLKO/RA6

RA5/AN4/SS/HLVDIN/C2OUT

RA3/AN3/VREF+

RA1/AN1

PORTA

Program Counter

31 Level Stack

STKPTR

20

RB0/AN12/INT0/FLT0/SDI/SDA

RB2/AN8/INT2/VMO

RB4/AN11/KBI0/CSSPP

RB6/KBI2/PGC

RB5/KBI1/PGM

RB3/AN9/CCP2/VPO

RB1/AN10/INT1/SCK/SCL

PORTB

RC0/T1OSO/T13CKI

RC2/CCP1/P1A

RC5/D+/VP

RC7/RX/DT/SDO

RC6/TX/CK

RC4/D-/VM

RC1/T1OSI/CCP2/UOE

PORTC

RD0/SPP0:RD4/SPP4

RD5/SPP5/P1B

PORTD

RB7/KBI3/PGD

RD6/SPP6/P1C

RD7/SPP7/P1D

RE0/AN5/CK1/SPP

RE1/AN6/CK2/SPP

PORTE

RE2/AN7/OESPP

MCLR/VPP/RE3

Band Gap

Reference

USB Voltage

Regulator

Fail-Safe

Clock Monitor

Brown-out

Reset

Watchdog

Timer

Power-on

Reset

Oscillator

Start-up Timer

Power-up

Timer

In-Circuit

Debugger

Single-Supply

Programming

Internal

Oscillator

Block

8MHZ

Oscillator

INTRC

Oscillator

USB

ADC

10-bit

EUSART MSSP CCP2 ECCP1 Comparator

Timer3 Timer2 Timer1 Timer0

Data

EEPROM

BOR

HLVD

VDD, VSS

ICPORTS

T1OSO

T1OSI

OSC2

OSC1

VUSB

MCLR

ICRST

ICPGD

ICPGC

8 8

Address Latch

Data Memory

(2 Kbytes)

Data Latch

Data Address <12>

BSR

inc/dec

logic

Address

Decode

Access

Bank

FSR2

FSR1

FSR0

12 4

12

4

12

W

8 x 8 Multiply

PRODH PRODL

BITOP

8

8

8

3

8 8

8

ALU <8>

8

8

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

8

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

ORGANIZACIN DE MEMORIA:

El uC PIC18F4550 dispone de las siguientes memorias:

Memoria de programa: memoria flash interna de 32.768 bytes

Almacena instrucciones y constantes/datos

Puede ser escrita/leda mediante un programador externo o durante la ejecucin

programa mediante unos punteros.

Memoria RAM de datos: memoria SRAM interna de 2048 bytes en la que estn

incluidos los registros de funcin especial.

Almacena datos de forma temporal durante la ejecucin del programa

Puede ser escrita/leda en tiempo de ejecucin mediante diversas instrucciones

Memoria EEPROM de datos: memoria no voltil de 256 bytes.

Almacena datos que se deben conservar aun en ausencia de tensin de

alimentacin

Puede ser escrita/leda en tiempo de ejecucin a travs de registros

Pila: bloque de 31 palabras de 21 bits

Almacena la direccin de la instruccin que debe ser ejecutada despus de una

interrupcin o subrutina

Memoria de configuracin: memoria en la que se incluyen los bits de configuracin

(12 bytes de memoria flash) y los registros de identificacin (2 bytes de memoria de

solo lectura).

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

9

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

MEMORIA DE CONFIGURACION:

Se trata de un bloque de memoria situado a partir de la posicin 30000H de

memoria de programa (ms all de la zona de memoria de programa de usuario).

En esta memoria de configuracin se incluyen:

Bits de configuracin: contenidos en 12 bytes de memoria flash permiten la

configuracin de algunas opciones del uC como:

Opciones del oscilador

Opciones de reset

Opciones del watchdog

Opciones de la circuiteria de depuracin y programacin

Opciones de proteccin contra escritura de memoria de programa y

memoria EEPROM de datos

Estos bits se configuran generalmente durante la programacin del uC,

aunque tambin pueden ser ledos y modificados durante la ejecucin del

programa.

Registros de identificacin: se trata de dos registros situados en las direcciones

3FFFFEH y 3FFFFFH que contienen informacin del modelo y revisin del

dispositivo. Son registros de solo lectura y no pueden ser modificados por el

usuario.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

10

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

ARQUITECTURA HARDVARD:

El uC PIC18F4550 dispone buses diferentes para el acceso a memoria de

programa y memoria de datos (arquitectura Harvard):

Bus de la memoria de programa:

21 lneas de direccin

16/8 lneas de datos (16 lneas para instrucciones/8 lneas para datos)

Bus de la memoria de datos:

12 lneas de direccin

8 lneas de datos

Esto permite acceder simultneamente a la memoria de programa y a la memoria

de datos. Es decir se puede ejecutar una instruccin (lo que por lo general requiere

acceso a memoria de datos) mientras se lee de la memoria de programa la

siguiente instruccin (proceso pipeline).

Por tanto la ejecucin completa de 1 instruccin (lectura instruccin +ejecucin)

se hace en un 1 ciclo de instruccin (4 T

OSC

). EXCEPCION: las instrucciones que

modifican el contenido del PC requieren 2 ciclos de instruccin.

Ejecucin Instr. N-1

Lectura Instr. N Ejecucin Instr. N

Lectura Instr. N+1 Ejecucin Instr. N+1

Lectura Instr. N+2

Ciclo Instr. N-1 Ciclo Instr. N Ciclo Instr. N+1

Lectura Instr. N-1

Ejecucin Instr. N+2

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

11

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

MEMORIA DE PROGRAMA:

El uC PIC18F4550 dispone una memoria de

programa de 32.768 bytes de memoria de

programa (0000H-7FFFH). Las instrucciones

ocupan 2 bytes (excepto CALL, MOVFF,

GOTO y LSFR que ocupan 4). Por lo tanto la

memoria de programa pueden almacenar hasta

16.384 instrucciones.

La operacin de lectura en posicin de memoria

por encima de 7FFFH da 0como resultado

(equivalente a la instruccin NOP).

Direcciones especiales de la memoria de

programa

Vectorizacin del Reset es 0000H

Vectorizacin de las interrupciones de alta

prioridad es la 0008H.

Vectorizacin de las interrupciones de baja

prioridad es la 0018H.

PC<20:0>

Nivel 1 de la pila

Nivel 31 de la pila

Vector de interrupcin de alta prioridad

.

.

.

Vector de Reset

Vector de interrupcin de baja prioridad

Memoria de Programa Interna

Leidos como 0

0000h

1FFFFFh

200000h

7FFFh

8000h

0018h

0008h

E

s

p

a

c

i

o

d

e

M

e

m

o

r

i

a

d

e

U

s

u

a

r

i

o

21

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

12

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

ALMACENAMIENTO DE INSTRUCCIONES EN MEMORIA DE PROGRAMA:

Primero se almacena la parte baja de la instruccin y luego la parte alta (para las

instrucciones de 4 bytes primero los bytes menos significativos y luego los ms

significativos).

Las instrucciones siempre empiezan en direcciones pares.

00H

F0H

20H

2BH

55H

0FH

20H

63H

88H

EFH

0020H

0021H

0022H

0023H

0024H

0025H

0026H

0027H

0028H

0029H

Memoria de Programa

MOVLW 55H

GOTO 0110H

CPFSEQ 20H

INCF 20H

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

13

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

CONTADOR DE PROGRAMA (PC):

Puntero de 21 bits que indica la direccin en memoria de programa de la instruccin

que se debe ejecutar. Est compuesto por 3 bytes:

PCU: parte superior del PC, registro no directamente accesible; las operaciones de

lectura/escritura sobre este registro se hacen a travs del registro PCLATU

PCH: parte alta del PC, registro no directamente accesible; las operaciones de

lectura/escritura sobre este registro se hacen a travs del registro PCLATH

PCL: parte baja del PC, registro directamente accesible. Una operacin de lectura

sobre PCL provoca que los valores de PCU y PCH pasen a PCLATU y PCLATH

respectivamente. Y una operacin de escritura sobre PCL provoca que los valores

de PCLATU y PCLATH pasen a PCU y PCH respectivamente. El PCL siempre

tiene el bit menos significativo a 0`, debido a que las instrucciones siempre

empiezan en direcciones pares.

0 X X X

PCU PCH PCL

PCLATU PCLATH

PC

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

14

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

LA PILA DE DIRECCION:

La Pila es un bloque de memoria RAM independiente de 31 palabras de 21 bits que

sirve para almacenar temporalmente el valor del PC cuando se produce una llamada a

subrutina o una interrupcin.

El puntero de pila (contenido en el registro STKPTR) es un contador de 5 bits que

indica la posicin actual del final de pila. El contenido del final de pila es accesible

mediante los registros TOSU, TOSH, TOSL.

Cuando se procesa una interrupcin o se ejecutan las instrucciones CALL o RCALL (el

PC est apuntando a la siguiente instruccin) se incrementa el STKPR y se almacena

en el final de pila el valor del PC.

Cuando se ejecutan las instrucciones RETURN, RETLW o RETFIE se copia el valor

almacenado en la cima de pila en el PC y se decrementa el STKPTR.

001934H

00013BH 1

0

3

2

31

30

00H 19H 34H

TOSU TOSH TOSL

Registro de Final de Pila

Top-of-Stack

2

STKPTR

Puntero

de Pila 004078H

001934H

00013BH 1

0

3

2

31

30

00H 40H 78H

TOSU TOSH TOSL

Registro de Final de Pila

Top-of-Stack

3

STKPTR

Puntero

de Pila

CALL 00203CH

RETURN

PILA PILA

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

15

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

REGISTRO STKPTR

STKFUL: Flag de llenado de la pila (en modo escritura nicamente puede ser puesto a 0`):

* STKFUL0`: No se ha producido el llenado o desbordamiento de la pila

* STKFUL1`: Se ha producido el llenado o desbordamiento de la pila

STKUNF: Flag de vaciado de la pila (en modo escritura nicamente puede ser puesto a 0`):

* STKUNF0`: No se ha producido el desbordamiento por vaciado de la pila

* STKUNF1`: Se ha producido el desbordamiento por vaciado de la pila

SP4..SP0: Puntero de pila. Estos 5 bits indican la posicin del final de la pila (valor de 0 a 31)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

16

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

REGISTRO EECON1

EEPGD: Bit de seleccin de acceso a memoria Flash/EERPOM:

* EEPGD0`: Acceso a memoria de datos EEPROM

* EEPGD1`: Acceso a memoria Flash de programa

CFGS: Bit de seleccin de acceso a memoria (Flash programa-EEPROM

datos)/Configuracin:

* CFGS0`: Acceso a memoria de Flash de programa o a memoria de datos EEPROM

* CFGS1`: Acceso a los registros de configuracin de la memoria Flash

FREE: Bit de habilitacin del borrado de una fila en memoria Flash:

* FREE0`: Activada nicamente la opcin de lectura

* FREE1`: Borrado de la fila de la memoria Flash de programa apuntada por TBLPTR en el siguiente

comando de escritura (el bit se pondr a 0` cuando la operacin de borrado se haya completado)

WRERR: Bit de error de escritura en memoria Flash/EEPROM:

* WRERR0`: La operacin de escritura en la memoria Flash/EEPROM se ha llevado a cabo

correctamente

* WRERR1`: Se ha producido un error en la operacin de escritura en la memoria Flash/ EEPROM

WREN: Bit de habilitacin de la operacin de escritura en memoria Flash/EEPROM:

* WREN0`: Operacin de escritura en la memoria Flash/EEPROM deshabilitada

* WREN1`: Operacin de escritura en la memoria Flash/EEPROM habilitada

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

17

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

REGISTRO EECON1 (cont.)

WR: Bit de control de escritura en memoria Flash/EEPROM:

* WR0`: La operacin de escritura en la memoria Flash/EEPROM se ha completado

* WR1`: Inicio de una operacin de borrado/escritura en memoria EEPROM o de las operacin de

borrado y/o escritura en memoria Flash (cuando la operacin termina el bit se pone automticamente

a 0`; por programa solo puede ponerse a 1`)

RD: Bit de control de lectura en memoria EEPROM:

* RD0`: La operacin de lectura en la memoria EEPROM se ha completado

* RD1`: Inicio de una operacin de lectura en memoria EEPROM (cuando la operacin termina el bit

se pone automticamente a 0`; por programa solo puede ponerse a 1`)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

18

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

MEMORIA RAM DE DATOS:

El uC PIC18F4550 dispone una

memoria RAM de datos 2.048 bytes (8

bancos de 256 bytes). Adems dispone

de 160 bytes dedicados a los registros

de funcin especial (SFR`s) situados en

la parte alta del banco 15.

Para acceder a un byte de la memoria

RAM de datos primero debe

seleccionarse el banco al que pertenece

el byte mediante el registro de

seleccin de banco (BSR) y a

continuacin direccionar el byte

dentro del banco. Adems existe una

modalidad de acceso rpido a las 96

posiciones de la parte baja del banco 0

y a los 160 bytes de SFR`s (banco de

acceso rpido).

Los bancos 4, 5, 6 y 7 se utilizan

tambin para el USB.

Mapa de la Memoria

RAM de datos

BSR<3:0>

Access RAM

GPR

GPR

GPR

(1)

GPR

(1)

GPR

(1)

GPR

(1)

GPR

GPR

= 0000

Bank 0

= 0001

Bank 1

= 0010

Bank 2

= 0011

Bank 3

= 0100

Bank 4

= 0101

Bank 5

= 0110

Bank 6

= 0111

Bank 7

FFh

00h

00h

FFh

00h

FFh

00h

FFh

00h

FFh

00h

FFh

00h

FFh

00h

FFh

00h

Unused

Read as 00h

Unused

SFR

FFh

00h

FFh

Bank 15

Bank 8

To

Bank 14

= 1000

= 1110

= 1111

000h

05Fh

060h

0FFh

100h

1FFh

200h

7FFh

800h

6FFh

700h

5FFh

600h

4FFh

500h

3FFh

400h

2FFh

300h

EFFh

F00h

F5Fh

F60h

FFFh

Access RAM Low

Access RAM High

(SFRs)

FFh

00h

5Fh

60h

Banco de Acceso

Rpido

(1): Estos bancos se

utilizan tambin como

buffers RAM para el

USB

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

19

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

REGISTROS DE FUNCION ESPECIAL:

La memoria RAM de datos se compone de registros de propsito general (GPR`s)

y de registros de funcin especial (SFR`s). Los SFR`s son los registros mediante los

cuales se pueden monitorizar/controlar el funcionamiento de la CPU y de las

unidades funcionales del uC.

Se distinguen dos conjuntos de SFR`s:

SFR`s asociados con el ncleo del uC

CPU: WREG, STATUS, BSR, etc...

Interrupciones: INTCON, PIE1, PIR1, IPR1, etc...

Reset: RCON

SFR`s asociados con las unidades funcionales:

Timers: T0CON, TMR1H, TMR1L, T1CON, etc...

Convertidor A/D: ADRESH, ADRESL, ADCON0, ADCON1, etc...

EUSART: TXREG, TXSTA, RCSTA, etc...

CCP: CCPR1H, CCPR1L, CCP1CON, etc...

MSSP: SSPSTAT, SSPDATA, SSPCFG, etc...

Puertos de E/S: TRISA, PORTA, TRISB, PORTB, etc...

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

20

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

REGISTRO STATUS

N: Bit de de valor negativo. Bit utilizado para operaciones con signo (complemento a 2):

* N0`: Resultado de la ltima operacin positivo (MSB a 0`)

* N1`: Resultado de la ltima operacin negativo (MSB a 1`)

OV: Bit de desbordamiento. Bit utilizado para operaciones con signo (complemento a 2).

Indica si se ha producido desbordamiento del 7 bit (bit 6), es decir si se ha producido algn

cambio en el bit 7 del resultado:

* OV0`: No se ha producido desbordamiento en la operacin aritmtica

* OV1`: Se ha producido desbordamiento en la operacin aritmtica

Z: Bit de cero:

* Z0`: El resultado de la operacin aritmtica o lgica ha sido diferente de 0

* Z1`: El resultado de la operacin aritmtica o lgica ha sido 0

DC: Bit de acarreo de dgito (para las instrucciones ADDWF, ADDLW, SUBLW y SUBWF):

* DC0`: No se ha producido acarreo del 4 bit

* DC1`: Se ha producido acarreo del 4 bit

C: Bit de acarreo (para las instrucciones ADDWF, ADDLW, SUBLW y SUBWF):

* DC0`: No se ha producido acarreo del 8 bit

* DC1`: Se ha producido acarreo del 8 bit

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

21

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / ORGANIZACIN DE LA MEMORIA

MODOS DE DIRECCIONAMIENTO:

El modo de direccionamiento es la forma en la que se obtienen el o los datos que

van a ser utilizados en la instruccin. Existen 4 modos de direccionamiento:

inherente, literal, directo e indirecto.

Modo de direccionamiento inherente: en este modo o bien la instruccin no tiene

operando o bien el operando viene especificado en el propio cdigo de operacin de

la instruccin.

RESET ; Realiza un reset por software (los operandos son todos los registros afectados por el reset)

DAW ; Ajuste decimal del acumulador (el operando es el acumulador). Formato BCD

NOP ; No realiza ninguna operacin (no hay operando)

Modo de direccionamiento literal: en este modo el valor del operando viene

indicado de forma explicita en la instruccin.

GOTO 0x100 ; Salto incondicional a la direccin 100H (el operando es 0x100)

MOVLW .23 ; Cargar en el acumulador el valor 23 (el operando es el .23)

Modo de direccionamiento directo: en este modo la direccin en la que se

encuentra el valor del operando viene indicada de forma explicita en la instruccin.

El operando puede ser un byte o un bit:

Mediante la instruccin MOVFF org,dest

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

22

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

SISTEMA DE INTERRUPCIONES:

El uC PIC18F4550 dispone de 21 fuentes de interrupciones. Se distinguen dos

grupos de interrupciones:

Grupo general de interrupciones:

Grupo de interrupciones de perifricos

Interrupcin del SPP

Interrupcin de recepcin de la EUSART

Interrupcin de transmisin de la EUSART

Interrupcin del MSSP

Interrupcin del A/D

Interrupcin del CCP1

Interrupcin del Temporizador 1

Interrupcin de fallo del oscilador

Interrupcin del comparador

Interrupcin del Temporizador 2

Interrupcin de escritura en Flash/EEPROM

Interrupcin de colisin de bus (MSSP)

Interrupcin del deteccin de anomalias en V

DD

Interrupcin del USB

Interrupcin del Temporizador 3

Interrupcin del CCP2

Interrupcin del Temporizador 0

Interrupcin externa 0

Interrupcin externa 1

Interrupcin externa 2

Interrupcin por cambio en PORTB

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

23

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

SISTEMA DE INTERRUPCIONES:

Se dispone de dos niveles de prioridad:

Nivel alto vectorizado en la direccin 0008H

Nivel bajo, vectorizado en la direccin 0018H

Todas las interrupciones pueden ser programadas con cualquiera de las dos

prioridades, salvo la interrupcin externa 0 (que siempre tiene alta prioridad).

Todas las interrupciones disponen de 3 bits de configuracin (excepto la

interrupcin externa 0 que tiene dos):

Bit de habilitacin de interrupcin: permite habilitar a nivel individual la

interrupcin.

Flag de interrupcin: se pone a 1` cuando se produce la condicin de interrupcin

independientemente de si la interrupcin est habilitada o no. Este flag debe

ponerse 0` por software cuando se procesa la interrupcin.

Bit de prioridad de interrupcin: establece si la interrupcin es de alta o de baja

prioidad (este bit no est disponible para la interrupcin externa 0).

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

24

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO RCON

IPEN: Bit de habilitacin de prioridades en las interrupciones

* IPEN0`: Sistema de prioridad en las interrupciones deshabilitado

* IPEN1`: Sistema de prioridad en las interrupciones habilitado

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

25

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO INTCON

GIE/GIEH: Bit de habilitacin global de las interrupciones. Su funcin depende del valor de

IPEN:

IPEN0`:

* GIE0`: Interrupciones deshabilitadas a nivel global

* GIE1`: Interrupciones habilitadas a nivel global

IPEN1`:

* GIEH0`: Interrupciones de alta prioridad deshabilitadas a nivel global

* GIEH1`: Interrupciones de alta prioridad habilitadas a nivel global

PEIE/GIEL: Bit de habilitacin global de las interrupciones de perifricos. Su funcin

depende del valor de IPEN:

IPEN0`:

* PEIE0`: Interrupciones de perifricos deshabilitadas a nivel global

* PEIE1`: Interrupciones de perifricos habilitadas a nivel global

IPEN1`:

* GIEL0`: Interrupciones de baja prioridad deshabilitadas a nivel global

* GIEL1`: Interrupciones de baja prioridad habilitadas a nivel global

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

26

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO INTCON (cont.)

TMR0IE: Bit de habilitacin de la interrupcin de desbordamiento del Temporizador 0

* TMR0IE0`: Interrupcin de desbordamiento del Temporizador 0 deshabilitada

* TMR0IE1`: Interrupcin de desbordamiento del Temporizador 0 habilitada

INT0IE: Bit de habilitacin de la interrupcin externa 0

* INT0IE0`: Interrupcin externa 0 deshabilitada

* INT0IE1`: Interrupcin externa 0 habilitada

RBIE: Bit de habilitacin de la interrupcin por cambio en el Puerto B

* RBIE0`: Interrupcin por cambio en el Puerto B deshabilitada

* RBIE1`: Interrupcin por cambio en el Puerto B habilitada

TMR0IF: Flag de la interrupcin de desbordamiento del Temporizador 0

* TMR0IF0`: No se ha producido desbordamiento del Temporizador 0

* TMR0IF1`: Se ha producido desbordamiento del Temporizador 0

INT0IF: Flag de la interrupcin externa 0

* INT0IF0`: No se ha producido un flanco en la lnea RB0/INT0

* INT0IF1`: Se ha producido un flanco en la lnea RB0/INT0

RBIF: Flag de la interrupcin por cambio en el Puerto B

* RBIF0`: No se ha producido ningn cambio en ninguna de las lneas RB7..RB4

* RBIF1`: Se ha producido algn cambio en alguna de las lneas RB7..RB4

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

27

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO INTCON2

RBPU: Bit de habilitacin de las resistencias de pull-up del Puerto B:

* RBPU0`: Las resistencias de pull-up del Puerto B estn activadas

* RBPU1`: Las resistencias de pull-up del Puerto B estn desactivadas

INTEDG0: Bit de seleccin de flanco de la interrupcin externa 0:

* INTEDG00`: La interrupcin externa 0 se dispara por flanco de bajada

* INTEDG01`: La interrupcin externa 0 se dispara por flanco de subida

INTEDG1: Bit de seleccin de flanco de la interrupcin externa 1:

* INTEDG10`: La interrupcin externa 1 se dispara por flanco de bajada

* INTEDG11`: La interrupcin externa 1 se dispara por flanco de subida

INTEDG2: Bit de seleccin de flanco de la interrupcin externa 2:

* INTEDG20`: La interrupcin externa 2 se dispara por flanco de bajada

* INTEDG21`: La interrupcin externa 2 se dispara por flanco de subida

TMR0IP: Bit de seleccin de prioridad de la interrupcin del Temporizador 0

* TMR0IP0`: Prioridad baja para la interrupcin del Temporizador 0

* TMR0IP1`: Prioridad alta para la interrupcin del Temporizador 0

RBIP: Bit de seleccin de prioridad de la interrupcin por cambio en el Puerto B

* RBIP0`: Prioridad baja para la interrupcin por cambio en el Puerto B

* RBIP1`: Prioridad alta para la interrupcin por cambio en el Puerto B

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

28

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO INTCON3

INT2IP: Bit de seleccin de prioridad de la interrupcin externa 2

* INT2IP0`: Prioridad baja para la interrupcin externa 2

* INT2IP1`: Prioridad alta para la interrupcin externa 2

INT1IP: Bit de seleccin de prioridad de la interrupcin externa 1

* INT1IP0`: Prioridad baja para la interrupcin externa 1

* INT1IP1`: Prioridad alta para la interrupcin externa 1

INT2IE: Bit de habilitacin de la interrupcin externa 2

* INT2IE0`: Interrupcin externa 2 deshabilitada

* INT2IE1`: Interrupcin externa 2 habilitada

INT1IE: Bit de habilitacin de la interrupcin externa 1

* INT1IE0`: Interrupcin externa 1 deshabilitada

* INT1IE1`: Interrupcin externa 1 habilitada

INT2IF: Flag de la interrupcin externa 2

* INT2IF0`: No se ha producido flanco en la lnea RB2/INT2

* INT2IF1`: Se ha producido flanco en la lnea RB2/INT2

INT1IF: Flag de la interrupcin externa 1

* INT1IF0`: No se ha producido flanco en la lnea RB1/INT1

* INT1IF1`: Se ha producido flanco en la lnea RB1/INT1

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

29

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIR1

SPPIF: Flag de la interrupcin de lectura/escritura en el canal de transmisin de datos en

paralelo (SPP)

* SPPIF0`: No se ha producido operacin de lectura/escritura en el SPP

* SPPIF1`: Se ha producido operacin de lectura/escritura en el SPP

ADIF: Flag de la interrupcin del convertidor A/D

* ADIF0`: No se ha completado la conversin A/D

* ADIF1`: Se ha se ha completado una conversin

RCIF: Flag de la interrupcin de recepcin del EUSART

* RCIF0`: El bfer de recepcin del EUSART (RCREG) est vaco

* RCIF1`: El bfer de recepcin del EUSART (RCREG) est lleno

TXIF: Flag de la interrupcin de transmisin del EUSART

* TXIF0`: El bfer de recepcin del EUSART (TXREG) est lleno

* TXIF1`: El bfer de recepcin del EUSART (RCREG) est vaco

SSPIF: Flag de la interrupcin del puerto serie sncrono (SSP)

* SSPIF0`: A la espera de una recepcin/transmisin

* SSPIF1`: Se ha producido una transmisin/recepcin

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

30

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIR1 (cont.)

CCP1IF: Flag de la interrupcin del mdulo 1 de Comparacin/Captura/PWM (CCP1)

Modo Captura:

* CCP1IF0`: No se ha capturado el valor del Temporizador 1

* CCP1IF1`: Se ha capturado el valor del Temporizador 1

Modo Comparacin:

* CCP1IF0`: No se ha producido igualdad con el valor del Temporizador 1

* CCP1IF1`: Se ha producido igualdad con el valor del Temporizador 1

TMR2IF: Flag de la interrupcin de igualdad entre TMR2 y PR2

* TMR2IF0`: No se ha producido igualdad con el valor del Temporizador 2 y el valor del registro PR2

* TMR2IF1`: Se ha producido igualdad con el valor del Temporizador 2 y el valor del registro PR2

TMR1IF: Flag de la interrupcin de desbordamiento del Temporizador 1

* TMR1IF0`: No se ha producido desbordamiento del Temporizador 1

* TMR1IF1`: Se ha producido desbordamiento del Temporizador 1

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

31

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIR2

OSCFIF: Flag de la interrupcin de fallo en el oscilador

* OSCFIF0`: El oscilador funciona correctamente

* OSCFIF1`: Se ha producido un fallo en el oscilador. La seal de reloj ha sido conmutada a INTOSC

CMIF: Flag de la interrupcin del comparador

* CMIF0`: La entrada del comparador no ha cambiado

* CMIF1`: La entrada del comparador ha cambiado

USBIF: Flag de la interrupcin del USB

* USBIF0`: El mdulo USB no ha generado una interrupcin

* USBIF0`: El mdulo USB ha generado una interrupcin

EEIF: Flag de la interrupcin de escritura en las memorias EEPROM/ Flash

* EEIF0`: La operacin de escritura en memoria EEPROM/Flash no se ha iniciado o no ha concluido

* EEIF1`: La operacin de escritura en memoria EEPROM/Flash ha concluido

BCLIF: Flag de la interrupcin de colisin de bus en el SSP

* BCLIF0`: No se ha producido colisin de bus en el SSP

* BCLIF1`: Se ha producido colisin de bus en el SSP

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

32

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIR2 (cont.)

HLVIF: Flag de la interrupcin de deteccin de tensin alta/baja

* HLVIF0`: No se ha detectado ninguna condicin de tensin alta o baja

* HLVIF1`: Se ha detectado ninguna condicin de tensin alta o baja

TMR3IF: Flag de la interrupcin de desbordamiento del Temporizador 3

* TMR3IF0`: No se ha producido desbordamiento del Temporizador 3

* TMR3IF1`: Se ha producido desbordamiento del Temporizador 3

CCP2IF: Flag de la interrupcin del mdulo 2 de Comparacin/Captura/PWM (CCP2)

Modo Captura:

* CCP2IF0`: No se ha capturado el valor del Temporizador 1 ni del Temporizador 3

* CCP2IF1`: Se ha capturado el valor del Temporizador 1 o del Temporizador 3

Modo Comparacin:

* CCP2IF0`: No se ha producido igualdad con el valor del Temporizador 1 ni con el Temporizador 3

* CCP2IF1`: Se ha producido igualdad con el valor del Temporizador 1 o con el Temporizador 3

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

33

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIE1

SPPIE: Bit de habilitacin de la interrupcin de lectura/escritura en el canal de transmisin

de datos en paralelo (SPP)

* SPPIE0`: Interrupcin de lectura/escritura en el SPP no habilitada

* SPPIE1`: Interrupcin de lectura/escritura en el SPP habilitada

ADIE: Bit de habilitacin de la interrupcin del convertidor A/D

* ADIE0`: Interrupcin del convertidor A/D no habilitada

* ADIE1`: Interrupcin del convertidor A/D habilitada

RCIE: Bit de habilitacin de la interrupcin de recepcin del EUSART

* RCIE0`: Interrupcin de recepcin del EUSART no habilitada

* RCIE1`: Interrupcin de recepcin del EUSART habilitada

TXIE: Bit de habilitacin de la interrupcin de transmisin del EUSART

* TXIE0`: Interrupcin de transmisin del EUSART no habilitada

* TXIE1`: Interrupcin de transmisin del EUSART habilitada

SSPIE: Bit de habilitacin de la interrupcin del puerto serie sncrono (SSP)

* SSPIE0`: Interrupcin del puerto serie sncrono (SSP) no habilitada

* SSPIE1`: Interrupcin del puerto serie sncrono (SSP) habilitada

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

34

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIE1 (cont.)

CCP1IE: Bit de habilitacin de la interrupcin del mdulo 1 de Comparacin/Captura/PWM

(CCP1)

* CCP1IE0`: Interrupcin del CCP1 no habilitada

* CCP1IE1`: Interrupcin del CCP1 habilitada

TMR2IE: Bit de habilitacin de la interrupcin de igualdad entre TMR2 y PR2

* TMR2IE0`: Interrupcin de igualdad entre TMR2 y PR2 no habilitada

* TMR2IE1`: Interrupcin de igualdad entre TMR2 y PR2 habilitada

TMR1IE: Bit de habilitacin de la interrupcin de desbordamiento del Temporizador 1

* TMR1IE0`: Interrupcin de desbordamiento del Temporizador 1 no habilitada

* TMR1IE1`: Interrupcin de desbordamiento del Temporizador 1 habilitada

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

35

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIE2

OSCFIE: Bit de habilitacin de la interrupcin de fallo en el oscilador

* OSCFIE0`: Interrupcin de fallo en el oscilador no habilitada

* OSCFIE1`: Interrupcin de fallo en el oscilador habilitada

CMIE: Bit de habilitacin de la interrupcin del comparador

* CMIE0`: Interrupcin del comparador no habilitada

* CMIE1`: Interrupcin del comparador habilitada

USBIE: Bit de habilitacin de la interrupcin del USB

* USBIE0`: Interrupcin del USB no habilitada

* USBIE0`: Interrupcin del USB habilitada

EEIE: Bit de habilitacin de la interrupcin de escritura en las memorias EEPROM/ Flash

* EEIE0`: Interrupcin de escritura en las memorias EEPROM/ Flash no habilitada

* EEIE1`: Interrupcin de escritura en las memorias EEPROM/ Flash habilitada

BCLIE: Bit de habilitacin de la interrupcin de colisin de bus en el SSP

* BCLIE0`: Interrupcin de colisin de bus en el SSP no habilitada

* BCLIE1`: Interrupcin de colisin de bus en el SSP habilitada

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

36

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIE2 (cont.)

HLVIE: Bit de habilitacin de la interrupcin de deteccin de tensin alta/baja

* HLVIE0`: Interrupcin de deteccin de tensin alta/baja no habilitada

* HLVIE1`: Interrupcin de deteccin de tensin alta/baja habilitada

TMR3IE: Bit de habilitacin de la interrupcin de desbordamiento del Temporizador 3

* TMR3IE0`: Interrupcin de desbordamiento del Temporizador 3 no habilitada

* TMR3IE1`: Interrupcin de desbordamiento del Temporizador 3 habilitada

CCP2IE: Bit de habilitacin de la interrupcin del mdulo 2 de Comparacin/Captura/PWM

(CCP2)

* CCP2IE0`: Interrupcin del CCP2 no habilitada

* CCP2IE1`: Interrupcin del CCP2 habilitada

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

37

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO IPR1

SPPIP: Bit de seleccin de prioridad de la interrupcin de lectura/escritura en el canal de

transmisin de datos en paralelo (SPP)

* SPPIE0`: Prioridad baja para la interrupcin de lectura/escritura en el SPP

* SPPIE1`: Prioridad alta para la interrupcin de lectura/escritura en el SPP

ADIP: Bit de seleccin de prioridad de la interrupcin del convertidor A/D

* ADIE0`: Prioridad baja para la interrupcin del convertidor A/D

* ADIE1`: Prioridad alta para la interrupcin del convertidor A/D

RCIP: Bit de seleccin de prioridad de la interrupcin de recepcin del EUSART

* RCIE0`: Prioridad baja para la interrupcin de recepcin del EUSART

* RCIE1`: Prioridad alta para la interrupcin de recepcin del EUSART

TXIP: Bit de seleccin de prioridad de la interrupcin de transmisin del EUSART

* TXIE0`: Prioridad baja para la interrupcin de transmisin del EUSART

* TXIE1`: Prioridad alta para la interrupcin de transmisin del EUSART

SSPIP: Bit de seleccin de prioridad de la interrupcin del puerto serie sncrono (SSP)

* SSPIE0`: Prioridad baja para la interrupcin del puerto serie sncrono (SSP)

* SSPIE1`: Prioridad alta para la interrupcin del puerto serie sncrono (SSP)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

38

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO IPR1 (cont.)

CCP1IP: Bit de seleccin de prioridad de la interrupcin del mdulo 1 de

Comparacin/Captura/PWM (CCP1)

* CCP1IE0`: Prioridad baja para la interrupcin del CCP1

* CCP1IE1`: Prioridad alta para la interrupcin del CCP1

TMR2IP: Bit de seleccin de prioridad de la interrupcin de igualdad entre TMR2 y PR2

* TMR2IE0`: Prioridad baja para la interrupcin de igualdad entre TMR2 y PR2

* TMR2IE1`: Prioridad alta para la interrupcin de igualdad entre TMR2 y PR2

TMR1IP: Bit de seleccin de prioridad de la interrupcin de desbordamiento del

Temporizador 1

* TMR1IE0`: Prioridad baja para la interrupcin de desbordamiento del Temporizador 1

* TMR1IE1`: Prioridad alta para la interrupcin de desbordamiento del Temporizador 1

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

39

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO IPR2

OSCFIP: Bit de seleccin de prioridad de la interrupcin de fallo en el oscilador

* OSCFIE0`: Prioridad baja para la interrupcin de fallo en el oscilador

* OSCFIE1`: Prioridad alta para interrupcin de fallo en el oscilador

CMIP: Bit de seleccin de prioridad de la interrupcin del comparador

* CMIE0`: Prioridad baja para la interrupcin del comparador

* CMIE1`: Prioridad alta para la interrupcin del comparador

USBIP: Bit de seleccin de prioridad de la interrupcin del USB

* USBIE0`: Prioridad baja para la interrupcin del USB

* USBIE0`: Prioridad alta para la interrupcin del USB

EEIP: Bit de seleccin de prioridad de la interrupcin de escritura en las memorias

EEPROM/ Flash

* EEIE0`: Prioridad baja para la interrupcin de escritura en las memorias EEPROM/ Flash

* EEIE1`: Prioridad alta para la interrupcin de escritura en las memorias EEPROM/ Flash

BCLIP: Bit de seleccin de prioridad de la interrupcin de colisin de bus en el SSP

* BCLIE0`: Prioridad baja para la interrupcin de colisin de bus en el SSP

* BCLIE1`: Prioridad alta para la interrupcin de colisin de bus en el SSP

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

40

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

REGISTRO PIE2 (cont.)

HLVIP: Bit de seleccin de prioridad de la interrupcin de deteccin de tensin alta/baja

* HLVIE0`: Prioridad baja para la interrupcin de deteccin de tensin alta/baja

* HLVIE1`: Prioridad alta para la interrupcin de deteccin de tensin alta/baja

TMR3IP: Bit de seleccin de prioridad de la interrupcin de desbordamiento del

Temporizador 3

* TMR3IE0`: Prioridad baja para la interrupcin de desbordamiento del Temporizador 3

* TMR3IE1`: Prioridad alta para la interrupcin de desbordamiento del Temporizador 3

CCP2IP: Bit de seleccin de prioridad de la interrupcin del mdulo 2 de

Comparacin/Captura/PWM (CCP2)

* CCP2IE0`: Prioridad baja para la interrupcin del CCP2

* CCP2IE1`: Prioridad alta para la interrupcin del CCP2

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

41

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

PRIORIDAD DE LAS INTERRUPCIONES:

El bit IPEN del registro RCON permite activar el sistema de prioridades:

IPEN a 0`: todas las interrupciones tienen la misma prioridad y se vectorizan en la

direccin 0008H. Para habilitar globalmente las interrupciones del grupo general de

interrupciones debe ponerse a 1` el GIE del registro INTCON. Para habilitar

globalmente las interrupciones del bloque de interrupciones de perifricos deben

ponerse a 1` los bits GIE y PEIE del registro INTCON. En este caso, ninguna

interrupcin puede interrupcin el tratamiento de otra interrupcin

IPEN a 1`: las interrupciones pueden configurarse con dos niveles de prioridad en

funcin del bit de prioridad de interrupcin (excepto la interrupcin externa 0 que

siempre tendr nivel de prioridad alto):

Bit de prioridad de interrupcin a 0` > Prioridad baja. Las interrupciones de prioridad baja

se vectorizan en la direccin 0018H. Para habilitar globalmente las interrupciones de prioridad

baja hay que poner a 1` el bit GIEL del registro INTCON.

Bit de prioridad de interrupcin a 1` > Prioridad alta. Las interrupciones de prioridad alta

se vectorizan en la direccin 0008H. Para habilitar globalmente las interrupciones de prioridad

alta hay que poner a 1` el bit GIEH del registro INTCON.

Una interrupcin de alta prioridad puede interrumpir el tratamiento de una interrupcin de

baja prioridad. Sin embargo las interrupciones de baja prioridad no pueden interrumpir a las

interrupciones de alta prioridad. Por otra parte las interrupciones de baja prioridad no

pueden interrumpirse entre ellas. Lo mismo ocurre con las interrupciones de alta prioridad.

NOTA: Adems de ser habilitadas globalmente, las interrupciones deben ser habilitadas a

nivel particular mediante su bit de habilitacin de interrupcin.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

42

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

PASOS A SEGUIR PARA TRABA1AR CON INTERRUPCIONES:

1. Configurar el dispositivo asociado a la interrupcin (Temporizadores, EUSART,

convertidor A/D, etc..).

2. Habilitar a nivel global las interrupciones del grupo correspondiente mediante los bits

GIE/GIEH y PEIE/GIEL del registro INTCON

3. Habilitar a nivel individual la interrupcin mediante el bit de habilitacin.

4. Establecer la prioridad de la interrupcin mediante el bit de prioridad (solo si

previamente se ha activado el sistema de prioridad de interrupciones, IPEN1`)

5. En la direccin de vectorizacin correspondiente (0008H o 0018H, segn el caso)

aadir el cdigo de tratamiento de la interrupcin que debe incluir:

Identificacin de la interrupcin: dado que varias interrupciones pueden vectorizarse

en la misma direccin, se deben comprobar los flags de las interrupciones habilitadas

para saber cual de ellas ha provocado el salto a la direccin de vectorizacin.

Borrado del flag de interrupcin: el flag de interrupcin debe ser borrado por software

una vez la interrupcin ha sido identificada. De esta forma se evita que cuando finalice

la rutina de tratamiento se vuelva a procesar la misma interrupcin.

Cdigo de procesado de la interrupcin: por ltimo hay que escribir el cdigo de

tratamiento de la interrupcin que depender de cada aplicacin.

El cdigo de tratamiento de la interrupcin siempre debe terminar con la instruccin

RETFIE.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

43

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

PROCESO DE TRATAMIENTO DE UNA INTERRUPCION:

1. Se produce la condicin de disparo de la interrupcin (desbordamiento del

temporizador, recepcin de un dato en la EUSART, etc...).

2. Si la interrupcin est habilitada, el uC almacena en la pila la direccin de la

instruccin que deba haberse ejecutado a continuacin y escribe en PC la direccin de

vectorizacin de la interrupcin. Adems el uC pone el bit de habilitacin global de

interrupciones (GIE, GIEH o GIEL segn corresponda) a 0` para que ninguna

interrupcin del mismo nivel que la se est tratando puede interrumpir el proceso.

3. Se ejecuta el cdigo de tratamiento de la interrupcin que deber hallarse en la

direccin de la vectorizacin (se comprueba que interrupcin ha generado el salto a la

direccin de vectorizacin, se borra el flag de interrupcin correspondiente y se

ejecuta el cdigo asociado a dicha interrupcin.

4. La ltima instruccin del cdigo de tratamiento de la interrupcin es RETFIE.

Cuando se ejecuta esta instruccin, el uC vuelve a poner a 1` el bit de habilitacin

global de interrupciones (GIE, GIEH o GIEL) y escribe en el PC la direccin que

haba almacenado en la pila de forma que se continu con la ejecucin del programa a

partir del punto en el que haba sido interrumpido.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

44

TEMA 3: MICROCONTROLADOR PIC18F4550

DESCRIPCION FUNCIONAL / SISTEMA DE INTERRUPCIONES

Plantilla Codigo en ~C :

#include <p18F4550.h> // Declaracin de librerias

void R_Int_Alta(void); // Declaracin de la rut. de tratamiento de interr. de alta prioridad

#pragma code Vector_Int_Alta=0x08 // Vectorizacin de las interrupciones de alta prioridad

void Int_Alta (void)

{

_asm GOTO R_Int_Alta _endasm

}

#pragma code

#pragma interrupt R_Int_Alta // Rutina de tratamiento de las interrupciones de alta prioridad

void R_Int_Alta (void)

{

// Codigo Rutina de Interrupcion

..

..

}

void main (void) {

// Bucle sin Fin

while (1) {

}

}

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

45

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / INTRODUCCIN

El uC PIC18F4550 dispone de una serie de Unidades Funcionales que le

permiten:

Realizar tareas especficas especializadas (conversion A/D,

transmisin/recepcin de datos, generacin de seales digitales con

temporizaciones programables, etc...)

Optimizar el rendimiento del uC, ya que estas unidades trabajan en paralelo

a la CPU permitiendo que sta se centre en otras tareas como procesado de

datos, clculos, movimiento de datos, etc...

Las Unidades Funcionales ms importantes del uC PIC18F4550 son:

Temporizador 0

Puertos de E/S

Canal de transmisin de datos en paralelo (SPP)

Canal de comunicacin serie EUSART

Mdulo analgico de comparacin

Convertidor A/D

Unidad de Comparacin/Captura/PWM (CCP)

Unidad de Comparacin/Captura/PWM mejorada (ECCP)

Temporizador 1

Temporizador 2

Temporizador 3

Canal de comunicacin serie MSSP

Canal de comunicacin serie USB

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

46

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTOS DE E/S:

El uC PIC18F4550 dispone 5 puertos de E/S que incluyen un total de 35 lneas

digitales de E/S:

Todas las lneas digitales de E/S disponen de al menos una funcin alternativa

asociada a alguna circuiteria especifica del uC. Cuando una lnea trabaja en el

modo alternativo no puede ser utilizada como lnea digital de E/S estndar.

PUERTO LINEAS DE ENTRADA/SALIDA

PORTA

PORTB

PORTC

PORTE

PORTD

7 LINEAS DE ENTRADA/SALIDA

8 LINEAS DE ENTRADA/SALIDA

6 LINEAS DE ENTRADA/SALIDA+ 2 LINEAS DE ENTRADA

8 LINEAS DE ENTRADA/SALIDA

3 LINEAS DE ENTRADA/SALIDA + 1 LINEAS DE ENTRADA

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

47

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

DIAGRAMA DE BLOQUES

GENERICO DE UN PIN DE E/S:

REGISTROS DE UN PUERTO DE E/S:

Cada puerto de E/S tiene asociado 3

registros:

Registro TRIS: mediante este

registro se configuran cada una de

las lneas de E/S del puerto como

ENTRADA (bit correspondiente a

1`) o como SALIDA (bit

correspondiente a 0`) .

Registro PORT: mediante este

registro se puede leer el nivel de pin

de E/S y se puede establecer el valor

del latch de salida.

Registro LAT: mediante este

registro se puede leer o establecer el

valor del latch de salida

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

48

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTO A:

Dispone de 7 lneas de E/S. Las funciones alternativas son:

RA0: entrada analgica (AN0)/ entrada de comparacin (C1IN-)

RA1: entrada analgica (AN1)/ entrada de comparacin (C2IN-)

RA2: entrada analgica (AN2)/ entrada de comparacin (C2IN+)

RA3: entrada analgica (AN3)/ entrada de comparacin (C1IN+)

RA4: entrada de reloj del Temporizador 0 (T0CKI)/salida de comparacin (C1OUT)

RA5: entrada analgica (AN4)/ salida de comparacin (C2OUT)/HLVDIN entrada

de deteccin de tensin alta/baja

RA6: entrada del oscilador principal (OSC2)/salida de seal de reloj (CLK0)

En el reset las lneas RA0, RA1, RA2, RA3 y RA5 se configuran como lneas de entrada

analgicas. Para poder utilizarlas como lneas digitales de E/S hay que desactivar la

funcin analgica:

// Se desactiva la funcin de entrada analgica para las lneas RA0, RA1, RA2, RA3 y RA4

ADCON1 = 0x0F

// Configura los comparadores para entrada digital, para las lneas RA0, RA1, RA2 y RA3

CMCON = 0x07 ;

// Se configuran RA5, RA4, RA3 y RA2 como entradas y RA1 y RA0 como salidas

TRISA = 0x3C

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

49

REGISTRO ADCON1

VCFG1: Bit de configuracin de la tensin de referencia V

REF-

:

* VCFG10`: V

REF-

se conecta a V

SS

* VCFG11`: V

REF-

se conecta a la lnea fsica RA2

VCFG0: Bit de configuracin de la tensin de referencia V

REF+

:

* VCFG10`: V

REF+

se conecta a V

DD

* VCFG11`: V

REF+

se conecta a la lnea fsica RA2

PCFG3..PCFG0: Bits configuracin de los puertos de conversin A/D. Mediante estos bits se

establecen que lneas fsicas (RA5..RA0, RB4..RB0, RE1 y RE0) van a trabajar como entradas

del convertidor A/D (Ver Tabla de configuracin de lneas de conversin A/D).

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

50

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

Tabla de configuracin de lneas de conversin A/D:

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

51

REGISTRO CMCOM

C2OUT: Bit de salida del comparador 2:

Cuando C2INV0`

Si C2_Vin+ > C2_Vin > C2OUT1`

Si C2_Vin+ < C2_Vin > C2OUT0`

Cuando C2INV1`

Si C2_Vin+ < C2_Vin > C2OUT1`

Si C2_Vin+ > C2_Vin > C2OUT0`

C1OUT: Bit de salida del comparador 1:

Cuando C1INV0`

Si C1_Vin+ > C1_Vin > C1OUT1`

Si C1_Vin+ < C1_Vin > C1OUT0`

Cuando C1INV1`

Si C1_Vin+ < C1_Vin > C1OUT1`

Si C1_Vin+ > C1_Vin > C1OUT0`

C2INV: Bit de inversin del comparador 2

* C2INV0`: Comparador C2 NO invertido

* C2INV1`: Comparador C2 invertido

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

52

REGISTRO CMCOM

C2INV: Bit de inversin del comparador 2

* C2INV0`: Comparador C2 NO invertido

* C2INV1`: Comparador C2 invertido

C1S: Bit de conmutacin de la entrada del comparador (CM2..CM0110).

* CIS0`: Pin C1_Vin+ conectado a pin RA3/ Pin C2_Vin+ conectado a pin RA2

* CIS1`: Pin C1_Vin+ conectado a pin RA0/ Pin C2_Vin+ conectado a pin RA1

CM2..CM0: Bits de seleccin del modo de comparacin

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

-

+

RA0

RA3

-

+

RA1

RA2

OFF (se lee '0')

OFF (se lee '0')

CM2..CM0=000

A

A

A

A

C1

C2

-

+

RA0

RA3

RA4

-

+

RA1

RA2

C1OUT

OFF (se lee '0')

CM2..CM0=001

A

A

D

D

C1

C2

-

+

RA0

RA3

-

+

RA1

RA2

CM2..CM0=010

A

A

A

A

C1

C2

-

+

RA0

RA3

RA4

-

+

RA1

RA2

RA5

CM2..CM0=011

A

A

A

A

C1

C2

-

+

RA0

RA3

-

+

RA1

RA2

CM2..CM0=100

A

A

D

A

C1

C2

-

+

RA0

RA3

RA4

-

+

RA1

RA2

RA5

CM2..CM0=101

A

A

D

A

C1

C2

-

+

RA0

RA3

-

+

RA1

RA2

CM2..CM0=110

A

A

A

A

C1

C2

-

+

RA0

RA3

-

+

RA1

RA2

OFF (se lee '0')

OFF (se lee '0')

CM2..CM0=111

D

D

D

D

C1

C2

C1OUT

C2OUT

C1OUT

C2OUT

C1OUT

C2OUT

C1OUT

C2OUT

CS=0

CS=1

VREF

CS=0

CS=1

C1OUT

C2OUT

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

53

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTO B:

Dispone de 8 lneas de E/S. Las funciones alternativas son:

RB0: entrada analgica (AN12)/ interrupcin externa 0 (INT0)/entrada de fallo

del ECCP (FLT0)/entrada de datos del SPI (SDI)/lnea de datos del I

2

C (SDA)

RB1: entrada analgica (AN10)/ interrupcin externa 1 (INT1)/lnea de reloj del

SPI (SDI)/lnea de reloj del I

2

C (SDA)

RB2: entrada analgica (AN8)/ interrupcin externa 2 (INT2)/salida de datos del

USB (VCMO)

RB3: entrada analgica (AN9)/ lnea de E/S del CCP2 (CCP2)/salida de datos del

USB (VPO)

RB4: entrada analgica (AN11)/ interrupcin por cambio en pin (KBI0)/ salida de

CS del SSP (CSSP)

RB5: interrupcin por cambio en pin (KBI1)/ lnea de programacin (PGM)

RB6: interrupcin por cambio en pin (KBI2)/ lnea de programacin (PGC)

RB7: interrupcin por cambio en pin (KBI3)/ lnea de programacin (PGD)

Resistencias de pull.up: Todas las lneas del puerto B disponen de resistencias de pull-

up internas que pueden ser activadas poniendo el bit RBPU del registro INTCON2 a

0` (RPBU1` despus de un reset). Si un lnea del puerto B se configura como

salida la resistencia de pull-up correspondiente se desactiva automticamente.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

54

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTO B (cont.):

Por defecto, en el reset las lneas RB4..RB0 estn programadas como entradas

analgicas. Existen dos formas de configurar RB4..RB0 como lneas de E/S digitales:

Poniendo a 0` el bit PBADEN del registro de configuracin CONFIG3H> en el

reset RB4..RB0 se configuran como lneas de E/S digitales

Si PBADEN1` (valor por defecto) se pueden configurar RB4..RB0 como lneas del

E/S digitales desactivando la funcin analgica:

// Se desactiva la funcin de entrada analgica para las lneas RB0, RB1, RB2, RB3 y RB4

ADCON1 = 0x07

// Se configuran RB7, RB6, RB5 y RB4 como entradas y RB3, RB2, RB1 y RB0 como salidas

TRISB = 0xF0

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

55

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

INTERRUPCIONES DEL PUERTO B:

Interrupcin externa 0:

Flag de interrupcin: bit INT0IF (INTCON)

Bit de habilitacin: bit INT0IE (INTCON)

Seleccin de flanco: bit INTEDG0 (INTCON2): 0`->fl. bajada/`1`-> fl. subida

Prioridad: la interrupcin 0 siempre tiene prioridad alta

Si se produce un flanco en la lnea RB0 (flanco de subida o de baja dependiendo del

valor del bit INTEDG0) se pone el flag INT0IF a 1`. Si el bit de habilitacin INT0IE

est a 1` y las interrupciones estn habilitadas a nivel global se genera una

interrupcin y el uC pasa a ejecutar el cdigo situado a partir de la posicin 0008H.

Interrupcin externa 1:

Flag de interrupcin: bit INTCON3.INT1IF

Bit de habilitacin: bit INTCON3.INT1IE

Seleccin de flanco: bit INTCON2.INTEDG1: 0`->fl. bajada/`1`-> fl. subida

Prioridad: bit INT1IP (INTCON3): 0`->pr. baja/`1`->pr. alta

Si se produce un flanco en la lnea RB1 (flanco de subida o de baja dependiendo del

valor del bit INTEDG1) se pone el flag INT1IF a 1`. Si el bit de habilitacin INT1IE

est a 1` y las interrupciones estn habilitadas a nivel global se genera una

interrupcin y el uC pasa a ejecutar el cdigo situado a partir de la posicin 0008H o

0018H (segn el nivel de prioridad establecido).

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

56

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

INTERRUPCIONES DEL PUERTO B (cont.):

Interrupcin externa 2:

Flag de interrupcin: bit INTCON3.INT2IF

Bit de habilitacin: bit INTCON3.INT2IE

Seleccin de flanco: bit INTCON2.INTEDG2: 0`->fl. bajada/`1`-> fl. subida

Prioridad: bit INTCON3.INT2IP: 0`->pr. baja/`1`->pr. alta

Si se produce un flanco en la lnea RB2 (flanco de subida o de baja dependiendo del

valor del bit INTEDG2) se pone el flag INT2IF a 1`. Si el bit de habilitacin INT2IE

est a 1` y las interrupciones estn habilitadas a nivel global se genera una

interrupcin y el uC pasa a ejecutar el cdigo situado a partir de la posicin 0008H o

0018H (segn el nivel de prioridad establecido).

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

57

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

INTERRUPCIONES DEL PUERTO B (cont.):

Interrupcin por cambio en pines RB7..RB4:

Flag de interrupcin: bit RBIF (INTCON)

Bit de habilitacin: bit RBIE (INTCON)

Prioridad: bit RBIP (INTCON2): 0`->pr. baja/`1`->pr. alta

Solo puede asociarse a las lneas RB7..RB4 que hayan sido configuradas como

entrada. Cada vez que se produce un cambio en estas lneas se pone a 1` el flag

RBIF. Si el bit de habilitacin RBIE est a 1` y las interrupciones estn

habilitadas a nivel global se genera una interrupcin y el uC pasa a ejecutar el

cdigo situado a partir de la posicin 0008H 0018H (segn el nivel de prioridad

establecido).

Si se utiliza est interrupcin no es aconsejable hacer ~polling del puerto B. Antes de

salirse de la rutina de tratamiento de la interrupcin hay que hacer lo siguiente:

Acceder al puerto B con cualquier instruccin excepto MOVFF, para deshacer la

desigualdad entre valor antiguo y nuevo valor

Poner a 0` el bit RBIF

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

58

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTO C:

Dispone de 5 lneas de E/S (RC0, RC1, RC2, RC6 y RC7) y 2 lneas de solo entrada

(RC4 y RC5). Las funciones alternativas son:

RC0: salida del oscilador del Temp. 1 (T1OSO)/ entrada de contador de los

Temp. 1 y 3 (T13CKI)

RC1: entrada del oscilador del Temp. 1 (T1OSI)/ lnea de E/S del CCP2 (CCP2)/

salida OE del transceiver del USB (UOE)

RC2: lnea de E/S del CCP1 (CCP1)/ salida PWM del ECCP1 (P1A)

RC4: lnea menos del bus USB (D-) / lnea de entrada del USB (VM)

RC5: lnea ms del bus USB (D-) / lnea de entrada del USB (VP)

RC6: salida de transmisin del EUSART (TX)/ lnea de reloj del EUSART (CK)

RC7: entrada de recepcin del EUSART (RX)/ lnea de datos sncrona del

EUSART (DT)/ salida de datos del SPI (SDO)

En el reset todas las lneas del puerto C quedan configuradas como entradas digitales.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

59

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTO D:

Dispone de 8 lneas de E/S. Las funciones alternativas son:

RD0: lnea de datos del SPP (SPP0)

RD1: lnea de datos del SPP (SPP1)

RD2: lnea de datos del SPP (SPP2)

RD3: lnea de datos del SPP (SPP3)

RD4: lnea de datos del SPP (SPP4)

RD5: lnea de datos del SPP (SPP5) / salida PWM del ECCP1 (P1B)

RD6: lnea de datos del SPP (SPP6) / salida PWM del ECCP1 (P1C)

RD7: lnea de datos del SPP (SPP7) / salida PWM del ECCP1 (P1D)

Resistencias de pull.up: Todas las lneas del puerto D disponen de resistencias de

pull-up internas que pueden ser activadas poniendo el bit RDPU del registro PORTE

a 1` (RPDU0` despus de un reset). Si un lnea del puerto D se configura como

salida la resistencia de pull-up correspondiente se desactiva automticamente.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

60

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / PUERTOS DE E/S

PUERTO E:

Dispone de 3 lneas de E/S (RE0, RE1 y RE2) y 1 lnea de solo entrada (RE3). Las

funciones alternativas son:

RE0: entrada analgica (AN5)/ salida de reloj 1 del SPP (CK1SPP)

RE1: entrada analgica (AN6)/ salida de reloj 2 del SPP (CK2SPP)

RE2: entrada analgica (AN7)/ salida de habilitacin del SPP (OESPP)

RE3: Lnea de reset externo (MCLR) / lnea de programacin (VPP)

En el reset todas las lneas RE2..RE0 se configuran como entradas analgicas. Para

poder utilizarlas como lneas digitales de E/S hay que desactivar la funcin analgica:

// Se desactiva la funcin de entrada analgica para las lneas RE0, RE1 y RE2

ADCON1 = 0x0F

// Se configuran RE2 y RE1 como entradas y RE0 como salida

TRISE = 0x06

La lnea RE3 por defecto tiene la funcin de Reset del uC. Si se desea desactivar la

funcin de Reset y utilizar RE3 como lnea de entrada digital hay que poner a 0` el

bit MCLRE del registro de configuracin CONFIG3H.

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

61

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / CANAL DE COMUNICACIN SERIE EUSART

CANAL DE COMUNICACIN SERIE EUSART:

Caractersticas fundamentales:

Modos de trabajo:

Modo asncrono de 8 bits

Modo asncrono de 9 bits

Modo sncrono Maestro

Modo sncrono Esclavo

Auto-activacin por deteccin de dato recibido

Deteccin automtica de velocidad de comunicacin (baudrate)

Transmisin y deteccin de carcter de BREAK (bus LIN)

En este tema solo se tratar el modo asncrono bsico (8 y 9 bits).

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

62

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / CANAL DE COMUNICACIN SERIE EUSART

REGISTRO TXSTA

CSRC: Bit seleccin de la fuente de seal de reloj para el modo sncrono:

* CSRC0`: Modo Esclavo (seal de reloj externa)

* CSRC1`: Modo Maestro (seal de reloj generada internamente)

TX9: Bit de habilitacin del modo de 9 bits en transmisin:

* TX90`: Se habilita el modo de 8 bits en transmisin

* TX91`: Se habilita el modo de 9 bits en transmisin

TXEN: Bit de habilitacin de la transmisin:

* TXEN0`: Transmisin deshabilitada

* TXEN1`: Transmisin habilitada

SYNC: Bit de seleccin del modo de trabajo del EUSART

* SYNC0`: Seleccin del modo asncrono

* SYNC1`: Seleccin del modo sncrono

SENDB: Bit de envo del carcter de BREAK en modo asncrono

* SENDB0`: Envo del carcter de transmisin BREAK completado

* SENDB1`: Se enviar un carcter BREAK en la prxima transmisin (se pone a 0` por hardware

cuando finaliza el envo)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

63

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / CANAL DE COMUNICACIN SERIE EUSART

REGISTRO TXSTA (cont)

BRGH: Bits de seleccin del modo de alta velocidad de comunicacin (baudrate) en modo

asncrono:

* BRGH0`: Se selecciona baja velocidad de comunicacin

* BRGH1`: Se selecciona alta velocidad de comunicacin

TRMT: Bit de status del registro de desplazamiento de transmisin:

* TMRT0`: Registro de desplazamiento de transmisin ocupado

* TMRT1`: Registro de desplazamiento de transmisin vaco

TX9D: Valor del 9 Bit en transmisin (puede utilizarse como bit de paridad o para distinguir

entre direccin o dato en los buses maestro-esclavo)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

64

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / CANAL DE COMUNICACIN SERIE EUSART

REGISTRO RCSTA

SPEN: Bit de activacin del puerto serie:

* SPEN0`: Puerto serie desactivado

* SPEN1`: Puerto serie activado (se configuran las lneas RC6/TX/CK y RC7/RX/DT como lneas del

puerto serie)

RX9: Bit de habilitacin del modo de 9 bits en recepcin:

* RX90`: Se habilita el modo de 8 bits en recepcin

* RX91`: Se habilita el modo de 9 bits en recepcin

SREN: Bit de habilitacin de la recepcin simple en modo sncrono Maestro:

* SREN0`: Se deshabilita la recepcin simple

* SREN1`: Se habilita la recepcin simple

CREN: Bit de habilitacin de la recepcin:

* CREN0`: Recepcin deshabilitada

* CREN1`: Recepcin habilitada

ADDEN: Bit de habilitacin de la deteccin de direccin en el modo asncrono de 9 bits:

* ADDEN0`: Deteccin de direccin deshabilitada (todos los bytes recibidos en el registro de

desplazamiento de recepcin son procesados independientemente del valor del 9 bit recibido)

* ADDEN1`: Deteccin de direccin habilitada (solo se procesa un byte recibido en el registro de

desplazamiento de recepcin si el 9 bit est a 1`)

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

65

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / CANAL DE COMUNICACIN SERIE EUSART

REGISTRO RCSTA (cont)

FERR: Bit de error de formato (solo lectura):

* FERR0`: No se ha producido error de formato

* FERR1`: Se ha producido error de formato

OERR: Bit de error de sobrescritura (solo lectura):

* FERR0`: No se ha producido error de sobrescritura

* FERR1`: Se ha producido error de sobrescritura

RX9D: Valor del 9 bit recibido

DEPARTAMENTO DE INGENIERIA ELECTRONICA

UNIVERSIDAD POLITECNICA DE VALENCIA

66

TEMA 3: MICROCONTROLADOR PIC18F4550

UNIDADES FUNCIONALES / CANAL DE COMUNICACIN SERIE EUSART

REGISTRO BAUDCON

ABDOVF: Bit de desbordamiento de auto-deteccin de la velocidad de comunicacin:

* ADBOVF0`: No se ha producido desbordamiento durante la auto-deteccin

* ABDOVF1`: Se ha producido desbordamiento durante la auto-deteccin (debe ponerse a 0` por

software)

RCIDL: Bit de status de la operacin de recepcin:

* RCIDL0`: Hay una operacin de recepcin en marcha

* RCIDL1`: No hay ninguna operacin de recepcin en marcha

SCKP: Bit de seleccin de polaridad de la seal de reloj en modo sncrono:

* SCKP0`: El dato est disponible en el nivel bajo de la seal de reloj (despus del flanco de bajada)

* SCKP1`: El dato est disponible en el nivel alto de la seal de reloj (despus del flanco de subida)

BRG16: Bit de habilitacin del generador de velocidad de comunicacin de 16 bits:

* BRG160`: Generador de velocidad de comunicacin de 8 bits (solo SPBRG)

* BRG161`: Generador de velocidad de comunicacin de 16 bits (SPBRG y SPBRGH)

WUE: Bit de habilitacin del modo de auto-activacin en modo asncrono:

* WUE0`: Modo de auto-activacin deshabilitado

* WUE1`: Modo de auto-activacin habilitado (cuando se detecta un flanco de bajada en la lnea RX se

pone a 1` el flag RCIF)

DEPARTAMENTO DE INGENIERIA ELECTRONICA