Professional Documents

Culture Documents

FPGA Design Flow & Experiment 1

Uploaded by

Faid MuzahidOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FPGA Design Flow & Experiment 1

Uploaded by

Faid MuzahidCopyright:

Available Formats

ELE655 LAB MANUAL FPGA Design Flow for Xilinx

SEPT2011

Page | 1

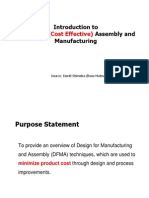

ELE655 LAB MANUAL 1. Design Entry may have two alternatives: a) Performing HDL coding for synthesis as the target (Xilinx HDL Editor) b) Using Cores (Xilinx Core Generator) 2. Functional Simulation of Synthesizable HDL code (MTI Model Sim) 3. Design Synthesis (Xilinx project navigator) 4. Design implementation (Xilinx Design Manager) The stages are linked as follows:

SEPT2011

VERILOG HDL/VERILOG CODE DESIGN ENTRY

FUNCTIONAL SIMULATION

SYNTHESIS

POST SYNTHESIS SIMULATION

IMPLEMENTATION

TIMING SIMULATION

PROGRAM ONTO FPGA

Design Entry The first stage of Xilinx design flow is a design entry process. A design must be specified either a schematic editor or HDL text-based tool

Functional Simulation The functional simulation of the design is used to verify functionality of the design assuming zero delay in simulation. The simulation is performed before the design is implemented as hardware. Testbenches (Verilog HDL) or text fixtures are used to specify circuit stimuli and responses. Simulation can be divided as functional and timing simulation. Functional simulation verifies that the designs specifications are correctly coded . Timing simulation operates with real delays (results of Page | 2

ELE655 LAB MANUAL

SEPT2011

device implementation) and is used for verification of implemented design. Timing data are given in an .sdf file (Standard Delay Format) . Xilinx supports functional and timing simulations at different points of the design flow: Register Transfer Level (RTL) simulation Post-synthesis functional simulation (Pre-NGDBuild) Post-implementation back-annotated timing simulation.

Design Synthesis After simulation, synthesis is performed and the target technology (choice of a particular FPGA device family) is selected. The output of the synthesis process is creation of gate level netlist (Electronic Design Interchange Format - EDIF). The EDIF netlist is used as input file to Xilinx Implementation tool and specifies how the core will be implemented.

Design Implementation Design implementation includes the following steps: i) ii) Translate - EDIF netlist must be converted into Native Generic Database file (NGD) Map the UCF(User Constraint File) file is an input into a MAP program that maps logical design to Xilinx FPGA. Place and Route(PAR) the mapped design is ready to be placed and routed. The output is a fully routed NCD file.

iii)

The implement design process generated review reports such as Map report and PAR report. To improve the design, changes can be made at process properties, constraints and source files.

Program onto FPGA Programming on the Xilinx device can be made as follows: Creation of a programming file (BIT) to program FPGA Generate a PROM, ACE, JTAG file for debugging or to download to device Use iMPACT to program the device through programming cable.

Xilinx FPGA, as an SRAM-based programmable PLD, must be configured with the configuration bitstream. The configuration bitstream is generated from the fully routed NCD file, by means of a BitGen program.

Page | 3

ELE655 LAB MANUAL

SEPT2011

EXPERIMENT 1: COMBINATIONAL LOGIC BLOCKS (MULTIPLEXER AND INCREMENTER)

Objective: To implement and test multiplexer and incrementer in Instruction Fetch (IF) of MIPS. The series of labs will be conducted in this course and it has ultimate objective to implement and simulate in Verilog the MIPS pipeline datapath.

(a)Multipler

(b) Incrementer by 1

IF Stage Figure 1 IF Stage in MIPS and its components (a) multiplexer (b) incrementer

In lab #1, you are required to write modules for multiplexer and incrementer as given in Figure 2.. Once these modules have been written, write their test benches to simulate possible inputs as provided in Figure 3. Synthesize the modules and capture the RTL schematic of the modules.

Page | 4

ELE655 LAB MANUAL

SEPT2011

Source files

module mux ( a , b , s e l , y ) ; input[31:0]a,b; inputsel; output[31:0]y; assigny=sel?a:b; endmodule

module incr ( pcin , pcout ) ; i n p u t [ 3 1 : 0 ] pcin ; o u t p u t [ 3 1 : 0 ] pcout ; a s s i g n y = pcin + 1 ; endmodule

(a) (b) Figure 2 (a) Verilog Code for multiplexer Testbenches:

i n c l u d e mux . v module t e s t mu x ; / / Wire P o r t s wi r e [ 3 1 : 0 ] Y; / / Re g i s t e r De c l a r a t i o n s r e g [ 3 1 : 0 ] A, B; regsel; MUX mux1 ( Y, A, B, s e l ) ; / / i n s t a n t i a t e t h e mux initialbegin A = 32 hAAAAAAAA; B = 32 h55555555 ; s e l = 1 b1 ; #10 ; A = 32 h00000000 ; #10 s e l = 1 b1 ; #10 ; B = 32 hFFFFFFFF ; #5 ; A = 32 hA5A5A5A5 ; #5 ; s e l = 1 b0 ; B = 32 hDDDDDDDD; #5 ; s e l = 1 bx ; end a lways @(A or B or s e l ) #1 $ d i s p l a y ( At t = %0d s e l = %b A = %h B = %h Y = %h , $ t ime , s e l , A, B, Y) ; endmodule / / t e s t includeincr.v module t e s t ( ) ; / / P o r t Wi res wi r e [ 3 1 : 0 ] IncrOu t ; / / Re g i s t e r De c l a r a t i o n s r e g [ 3 1 : 0 ] A; INCR i n c r 1 ( I n c rOu t , A) ; / / i n s t a n t i a t e t h e i n c r eme n t e r initialbegin #10 A=3; #10 ; A=15; #10 A=64; #5 ; end a lways @(A) #1 $ d i s p l a y ( Time = %0d\tA=%0d\ t I n c rOu t=%0d , $ t ime , A, I n c rOu t ) ; endmodule / / t e s t

(b) Verilog Code for incrementer

Figure 3 Testbench for multiplexer and incrementer

Page | 5

You might also like

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- VLSI Lab Manual - 2022-1Document54 pagesVLSI Lab Manual - 2022-1SuhailNo ratings yet

- Lab ManualDocument36 pagesLab ManualKeerthana SahadevanNo ratings yet

- Birla Institute of Technology & Science, Pilani Lab Sheet - 1Document7 pagesBirla Institute of Technology & Science, Pilani Lab Sheet - 1SATYAVRAT SHARMANo ratings yet

- Lab Report FpgaDocument34 pagesLab Report FpgaMuhammad Furqan JavedNo ratings yet

- Lab 1Document5 pagesLab 1sean_bostic7193No ratings yet

- EC8661 VLSI Design Lab ManualDocument76 pagesEC8661 VLSI Design Lab ManualN.S.Priyanga 33100% (3)

- DVCon Europe 2015 TA5 1 PaperDocument7 pagesDVCon Europe 2015 TA5 1 PaperJon DCNo ratings yet

- Experiment-1 Realization of Logic Gates: Cycle-IDocument57 pagesExperiment-1 Realization of Logic Gates: Cycle-Irameshkumar_aNo ratings yet

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaNo ratings yet

- Lab9 - Counters, Timers, and Real-Time ClockDocument6 pagesLab9 - Counters, Timers, and Real-Time Clockwert1a2No ratings yet

- DD&CO Full Lab ManualDocument45 pagesDD&CO Full Lab ManualHarshitha SinghNo ratings yet

- Lab 07Document10 pagesLab 07api-241454978No ratings yet

- Verilog: Advantages of HDL Based Design TechniqueDocument9 pagesVerilog: Advantages of HDL Based Design TechniqueRafiqul IslamNo ratings yet

- Chapter 7 Parameters Task and Function in VerilogDocument34 pagesChapter 7 Parameters Task and Function in Veriloghieu27718No ratings yet

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- DSD ReportDocument14 pagesDSD Report22051774No ratings yet

- FPGA Lab 07Document14 pagesFPGA Lab 07Zain AlamgirNo ratings yet

- VlogDocument14 pagesVlogUday KumarNo ratings yet

- Ecad and Vlsi Lab ManualDocument125 pagesEcad and Vlsi Lab Manualsameer7mohammadNo ratings yet

- Basic Verilog Programs FileDocument33 pagesBasic Verilog Programs FileDaniel Anderson72% (18)

- SystemC N BehaviorCoding Section2Document110 pagesSystemC N BehaviorCoding Section2jasonturfNo ratings yet

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- Programming FPGAsDocument38 pagesProgramming FPGAssayuri8910No ratings yet

- H.D.L - Lab: For IV Semester B.EDocument76 pagesH.D.L - Lab: For IV Semester B.EvijaykannamallaNo ratings yet

- EdSim51 - Example ProgramsDocument12 pagesEdSim51 - Example ProgramserwanblogNo ratings yet

- VHDL Lab Manual PDFDocument21 pagesVHDL Lab Manual PDFashwani_agrawal50% (2)

- Digital Design BEC30503 Instruction Sheet: Lab No. Lab Title Semester Session Lab Durations Independent StudiesDocument30 pagesDigital Design BEC30503 Instruction Sheet: Lab No. Lab Title Semester Session Lab Durations Independent StudiesKarti ViveygenNo ratings yet

- ESD Manual StudentsDocument55 pagesESD Manual StudentsNimesh PrajapatiNo ratings yet

- Lab 6Document11 pagesLab 6vivek2mbNo ratings yet

- USB ThermometerDocument40 pagesUSB ThermometerTheodøros D' SpectrøømNo ratings yet

- Verilog HDL: A Guide To Digital Design DS TH I and SynthesisDocument62 pagesVerilog HDL: A Guide To Digital Design DS TH I and SynthesisSharan ChaitanyaNo ratings yet

- MikroC Introduction Lab ReportDocument9 pagesMikroC Introduction Lab ReportGREATJUSTGREATNo ratings yet

- Verification ConceptsDocument33 pagesVerification Conceptsamigottp100% (1)

- Xilinx Lab RecordDocument76 pagesXilinx Lab RecordDivya SantoshiNo ratings yet

- 05 Systemc TutorialDocument32 pages05 Systemc TutorialjasonturfNo ratings yet

- VLSI Lab Manual Student Copy 21-22 04.10.21Document76 pagesVLSI Lab Manual Student Copy 21-22 04.10.21RanjithNo ratings yet

- HDL Lab Manual VTUDocument63 pagesHDL Lab Manual VTUSyed MisbahNo ratings yet

- Alarm Clock Project Final ReportDocument14 pagesAlarm Clock Project Final ReportArkadip Ghosh20% (5)

- Lab 7Document9 pagesLab 7zaqNo ratings yet

- Chapter1: Introduction To VerilogDocument15 pagesChapter1: Introduction To Verilogarunguptha_gsNo ratings yet

- Lab Manual NBADocument14 pagesLab Manual NBASHAMINDRA SENNo ratings yet

- PWM Driver VerilogDocument24 pagesPWM Driver Veriloglizhi0007No ratings yet

- VLSI Lab Record 2023Document47 pagesVLSI Lab Record 2023HARISABARISH J 21ECNo ratings yet

- 3.HDL Modeling 2Document44 pages3.HDL Modeling 2Himanshu PatraNo ratings yet

- C What HappensDocument192 pagesC What Happenschopsticks_phc100% (2)

- Lab1 111 PDFDocument16 pagesLab1 111 PDFGoran MiljkovicNo ratings yet

- C What Happens EbookDocument192 pagesC What Happens EbookIzhar Rosli100% (1)

- COMP600 Spring Lab#2Document7 pagesCOMP600 Spring Lab#2jassica sahiNo ratings yet

- Digital Signal Processing Lab: CODE NO: EC05177 List of ExperimentsDocument33 pagesDigital Signal Processing Lab: CODE NO: EC05177 List of ExperimentsSai SaranyaNo ratings yet

- CPS Lab Report FinalDocument38 pagesCPS Lab Report Finaldevikam230354ecNo ratings yet

- Inverter Using SimulinkDocument8 pagesInverter Using SimulinkprakashroutNo ratings yet

- Experiment - 5: - Write Programs To Implement 2:4 and 3:8 Decoders UsingDocument11 pagesExperiment - 5: - Write Programs To Implement 2:4 and 3:8 Decoders UsingSaarthak GuptaNo ratings yet

- FPGA-Based-System-Design LAB JOURNAL 2Document56 pagesFPGA-Based-System-Design LAB JOURNAL 2talha42103No ratings yet

- Midterm Report Format PDFDocument25 pagesMidterm Report Format PDFLucy HeartfilliaNo ratings yet

- 2SIT325-21P Network Performance Evaluation-TaskSheetDocument5 pages2SIT325-21P Network Performance Evaluation-TaskSheetNarendraNo ratings yet

- Verilog HDL: Dr. Shoab KhanDocument61 pagesVerilog HDL: Dr. Shoab KhanSufyan AsgharNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Bedia CLS 40 45 GBDocument36 pagesBedia CLS 40 45 GBkadir kayaNo ratings yet

- Table and Graph CriteriaDocument3 pagesTable and Graph Criteriaapi-271250844No ratings yet

- Laboratory Requirements For ISO/IEC 17025: Accreditation of Radon Indoor Measurements Based On CR-39 Nuclear Track DetectorsDocument17 pagesLaboratory Requirements For ISO/IEC 17025: Accreditation of Radon Indoor Measurements Based On CR-39 Nuclear Track DetectorsChong CongNo ratings yet

- Differential EquationDocument17 pagesDifferential EquationAashika DhareNo ratings yet

- Online Food Ordering System MiniDocument11 pagesOnline Food Ordering System Minijwala reddy83% (47)

- BioFluid Mechanics 1Document29 pagesBioFluid Mechanics 1roxannedemaeyerNo ratings yet

- 1piece Exam - Week 11 Solution (Geas)Document14 pages1piece Exam - Week 11 Solution (Geas)Elguapito DelisciusoNo ratings yet

- Structural Design 2Document43 pagesStructural Design 2Meymuna AliNo ratings yet

- 1716,1734,1751,1769 - Highrise and Earthquake Resistant ConstructionDocument34 pages1716,1734,1751,1769 - Highrise and Earthquake Resistant ConstructionFAB RAHINo ratings yet

- 02 Bateria 12V - 150AHDocument2 pages02 Bateria 12V - 150AHRafael AlvarezNo ratings yet

- Iohexol USP42NF37Document5 pagesIohexol USP42NF37John Alejandro Restrepo GarciaNo ratings yet

- Jet Powered BoatDocument22 pagesJet Powered BoatMagesh OfficialNo ratings yet

- L071ME4182DFADocument81 pagesL071ME4182DFAmegamech23No ratings yet

- Lab Report Instructions - Isolation of Cinnamaldehyde - SP16Document4 pagesLab Report Instructions - Isolation of Cinnamaldehyde - SP16Al SharptonNo ratings yet

- Xii Chemistry MCQ (Haloalanes & Haloarenrs)Document7 pagesXii Chemistry MCQ (Haloalanes & Haloarenrs)SanjanasanjuNo ratings yet

- Catamaran AnalysisDocument83 pagesCatamaran AnalysisbhukthaNo ratings yet

- Arduino - Wikipedia PDFDocument70 pagesArduino - Wikipedia PDFJheremy BayonetaNo ratings yet

- ElcometerDocument228 pagesElcometerMohammedMudassirNo ratings yet

- Question Bank-JavaDocument3 pagesQuestion Bank-Javarachana saiNo ratings yet

- ASME Boiler Feed WaterDocument30 pagesASME Boiler Feed WaterHendri KurniawanNo ratings yet

- EagleBurgmann - API682 4th Facts, Innovations, SolutionsDocument26 pagesEagleBurgmann - API682 4th Facts, Innovations, SolutionsTasawwur Tahir100% (1)

- 02 Sub-Surface Exploration 01Document24 pages02 Sub-Surface Exploration 01kabir AhmedNo ratings yet

- SDS-PAGE PrincipleDocument2 pagesSDS-PAGE PrincipledhashrathNo ratings yet

- Alex H.: Penguin ProjectDocument13 pagesAlex H.: Penguin Projectapi-504550016No ratings yet

- Production of Hard Grade Bitumen For Using in High Modulus Asphalt ConcreteDocument18 pagesProduction of Hard Grade Bitumen For Using in High Modulus Asphalt ConcretePanjiNo ratings yet

- Slides Prepared by John S. Loucks St. Edward's University: 1 Slide © 2003 Thomson/South-WesternDocument34 pagesSlides Prepared by John S. Loucks St. Edward's University: 1 Slide © 2003 Thomson/South-WesternHRish BhimberNo ratings yet

- AlternatorDocument14 pagesAlternatorTaraknath MukherjeeNo ratings yet

- Bearing Reliability Improvement-SKFDocument55 pagesBearing Reliability Improvement-SKFAbdulrahman AlkhowaiterNo ratings yet

- Behavior of Structure Under Blast LoadingDocument32 pagesBehavior of Structure Under Blast Loadingramyashri inalaNo ratings yet

- Western Dragon V3 Updated PDFDocument19 pagesWestern Dragon V3 Updated PDFMark Moldez94% (17)