Professional Documents

Culture Documents

CRC Gen

Uploaded by

master_junoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CRC Gen

Uploaded by

master_junoCopyright:

Available Formats

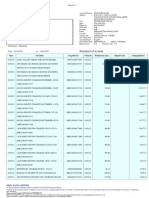

CRC Generator for Verilog or VHDL

By Evgeni Stavinov, OutputLogic.com

Description

CRC Generator is a command-line application that generates Verilog or VHDL code for CRC of any data width between 1 and 1024 and polynomial width between 1 and 1024. The code is written in C and is cross-platform compatible

Parameters

language: verilog or vhdl data_width : data bus width {1..1024} poly_width : polynomial width {1..1024} poly_string : a string that describes CRC polynomial. Examples: 05 = x5+x2+1 8005 = x16 + x15+ x2+ 1

Note: string representation (0x05, 0x8005) doesnt include highest degree coefficient in polynomial representation (x5 and x16 in the above examples)

Output Examples

[1] C:\OutputLogic> crc-gen usage: crc-gen language data_width poly_width poly_string parameters: language : verilog or vhdl data_width : data bus width {1..1024} poly_width : polynomial width {1..1024} poly_string : polynomial string in hex example: usb crc5 = x^5+x^2+1 crc-gen verilog 8 5 5 Copyright 2009 OutputLogic.com

[2] C:\OutputLogic> crc-gen verilog 8 5 05

//----------------------------------------------------------------------------// Copyright (C) 2009 OutputLogic.com // This source file may be used and distributed without restriction // provided that this copyright statement is not removed from the file // and that any derivative work contains the original copyright notice // and the associated disclaimer. // THIS SOURCE FILE IS PROVIDED "AS IS" AND WITHOUT ANY EXPRESS // OR IMPLIED WARRANTIES, INCLUDING, WITHOUT LIMITATION, THE IMPLIED // WARRANTIES OF MERCHANTIBILITY AND FITNESS FOR A PARTICULAR PURPOSE. //----------------------------------------------------------------------------// CRC module for // data[7:0] // crc[4:0]=1+x^2+x^5; // module crc( input [7:0] data_in, input crc_en, output [4:0] crc_out, input rst, input clk); reg [4:0] lfsr_q, lfsr_c; assign crc_out = lfsr_q; always @(*) begin lfsr_c[0] = lfsr_q[0] ^ lfsr_q[2] ^ lfsr_q[3] ^ data_in[0] ^ data_in[3] ^ data_in[5] ^ data_in[6]; lfsr_c[1] = lfsr_q[1] ^ lfsr_q[3] ^ lfsr_q[4] ^ data_in[1] ^ data_in[4] ^ data_in[6] ^ data_in[7]; lfsr_c[2] = lfsr_q[0] ^ lfsr_q[3] ^ lfsr_q[4] ^ data_in[0] ^ data_in[2] ^ data_in[3] ^ data_in[6] ^ data_in[7]; lfsr_c[3] = lfsr_q[0] ^ lfsr_q[1] ^ lfsr_q[4] ^ data_in[1] ^ data_in[3] ^ data_in[4] ^ data_in[7]; lfsr_c[4] = lfsr_q[1] ^ lfsr_q[2] ^ data_in[2] ^ data_in[4] ^ data_in[5];

end // always always @(posedge clk, posedge rst) begin if(rst) begin lfsr_q <= {5{1'b1}}; end else begin lfsr_q <= crc_en ? lfsr_c : lfsr_q; end end // always endmodule // crc

[3] C:\OutputLogic> crc-gen verilog 8 16 8005 //----------------------------------------------------------------------------// Copyright (C) 2009 OutputLogic.com // This source file may be used and distributed without restriction // provided that this copyright statement is not removed from the file // and that any derivative work contains the original copyright notice // and the associated disclaimer. // THIS SOURCE FILE IS PROVIDED "AS IS" AND WITHOUT ANY EXPRESS // OR IMPLIED WARRANTIES, INCLUDING, WITHOUT LIMITATION, THE IMPLIED // WARRANTIES OF MERCHANTIBILITY AND FITNESS FOR A PARTICULAR PURPOSE. Copyright 2009 OutputLogic.com

//----------------------------------------------------------------------------// CRC module for // data[7:0] // crc[15:0]=1+x^2+x^15+x^16; // module crc( input [7:0] data_in, input crc_en, output [15:0] crc_out, input rst, input clk); reg [15:0] lfsr_q, lfsr_c; assign crc_out = lfsr_q; always @(*) begin lfsr_c[0] = lfsr_q[8] ^ lfsr_q[9] ^ lfsr_q[10] ^ lfsr_q[11] ^ lfsr_q[12] ^ lfsr_q[13] ^ lfsr_q[14] ^ lfsr_q[15] ^ data_in[0] ^ data_in[1] ^ data_in[2] ^ data_in[3] ^ data_in[4] ^ data_in[5] ^ data_in[6] ^ data_in[7]; lfsr_c[1] = lfsr_q[9] ^ lfsr_q[10] ^ lfsr_q[11] ^ lfsr_q[12] ^ lfsr_q[13] ^ lfsr_q[14] ^ lfsr_q[15] ^ data_in[1] ^ data_in[2] ^ data_in[3] ^ data_in[4] ^ data_in[5] ^ data_in[6] ^ data_in[7]; lfsr_c[2] = lfsr_q[8] ^ lfsr_q[9] ^ data_in[0] ^ data_in[1]; lfsr_c[3] = lfsr_q[9] ^ lfsr_q[10] ^ data_in[1] ^ data_in[2]; lfsr_c[4] = lfsr_q[10] ^ lfsr_q[11] ^ data_in[2] ^ data_in[3]; lfsr_c[5] = lfsr_q[11] ^ lfsr_q[12] ^ data_in[3] ^ data_in[4]; lfsr_c[6] = lfsr_q[12] ^ lfsr_q[13] ^ data_in[4] ^ data_in[5]; lfsr_c[7] = lfsr_q[13] ^ lfsr_q[14] ^ data_in[5] ^ data_in[6]; lfsr_c[8] = lfsr_q[0] ^ lfsr_q[14] ^ lfsr_q[15] ^ data_in[6] ^ data_in[7]; lfsr_c[9] = lfsr_q[1] ^ lfsr_q[15] ^ data_in[7]; lfsr_c[10] = lfsr_q[2]; lfsr_c[11] = lfsr_q[3]; lfsr_c[12] = lfsr_q[4]; lfsr_c[13] = lfsr_q[5]; lfsr_c[14] = lfsr_q[6]; lfsr_c[15] = lfsr_q[7] ^ lfsr_q[8] ^ lfsr_q[9] ^ lfsr_q[10] ^ lfsr_q[11] ^ lfsr_q[12] ^ lfsr_q[13] ^ lfsr_q[14] ^ lfsr_q[15] ^ data_in[0] ^ data_in[1] ^ data_in[2] ^ data_in[3] ^ data_in[4] ^ data_in[5] ^ data_in[6] ^ data_in[7];

end // always always @(posedge clk, posedge rst) begin if(rst) begin lfsr_q <= {16{1'b1}}; end else begin lfsr_q <= crc_en ? lfsr_c : lfsr_q; end end // always endmodule // crc

Copyright 2009 OutputLogic.com

About the Author

Evgeni Stavinov is the creator and main developer of OutputLogic.com. Evgeni has more than 10 years of diverse design experience in the areas of FPGA logic design, embedded software and communication protocols. He holds MSEE from University of Southern California and BSEE from Technion Israel Institute of Technology. For more information contact evgeni@outputlogic.com

About OutputLogic.com

OutputLogic.com is a web portal that offers online tools for FPGA and ASIC designers.

The MIT License

Copyright 2009 OutputLogic.com Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions: The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software. THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

Copyright 2009 OutputLogic.com

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Separation, Delegation, and The LegislativeDocument30 pagesSeparation, Delegation, and The LegislativeYosef_d100% (1)

- Lucky Chops - CocoDocument6 pagesLucky Chops - CocoLe Poulet De KFCNo ratings yet

- AFN 132 Homework 1Document3 pagesAFN 132 Homework 1devhan12No ratings yet

- Qualifications approved for direct entry to MRICSDocument7 pagesQualifications approved for direct entry to MRICSJohn BernalteNo ratings yet

- Book 1Document9 pagesBook 1Samina HaiderNo ratings yet

- DeclarationDocument6 pagesDeclarationzdvdfvsdvsNo ratings yet

- Statement of Account: Date Narration Chq./Ref - No. Value DT Withdrawal Amt. Deposit Amt. Closing BalanceDocument4 pagesStatement of Account: Date Narration Chq./Ref - No. Value DT Withdrawal Amt. Deposit Amt. Closing BalanceSiraj PNo ratings yet

- SENSE AND SENSIBILITY ANALYSIS - OdtDocument6 pagesSENSE AND SENSIBILITY ANALYSIS - OdtannisaNo ratings yet

- Application For Membership: Insert CCT MBA Logo Here 6/F Joshua Center, Taft Ave, Ermita, Metro ManilaDocument2 pagesApplication For Membership: Insert CCT MBA Logo Here 6/F Joshua Center, Taft Ave, Ermita, Metro ManilaAnne florNo ratings yet

- Spec Pro Case DoctrinesDocument4 pagesSpec Pro Case DoctrinesRalph Christian UsonNo ratings yet

- Ventilador PLV-100 Manual en EspañolDocument34 pagesVentilador PLV-100 Manual en Españoladpodesta5No ratings yet

- B.E., B.S., B.Ed. (H), DPT, BA/LL.B (Test Based) B.E., B.S., B.Ed. (H), DPT, BA/LL.B (Test Based) B.E., B.S., B.Ed. (H), DPT, BA/LL.B (Test Based)Document1 pageB.E., B.S., B.Ed. (H), DPT, BA/LL.B (Test Based) B.E., B.S., B.Ed. (H), DPT, BA/LL.B (Test Based) B.E., B.S., B.Ed. (H), DPT, BA/LL.B (Test Based)Anas ArifNo ratings yet

- People Vs PalmaDocument3 pagesPeople Vs PalmaNunugom SonNo ratings yet

- 10-Cisa It Audit - BCP and DRPDocument27 pages10-Cisa It Audit - BCP and DRPHamza NaeemNo ratings yet

- Dizon vs. CA - GR No. 101929 - Case DigestDocument2 pagesDizon vs. CA - GR No. 101929 - Case DigestAbigail Tolabing100% (1)

- (WWWDocument5 pages(WWWnosena1267No ratings yet

- ACL-ASDocument12 pagesACL-ASSatyam Pathak100% (1)

- Chapter06 ProblemsDocument2 pagesChapter06 ProblemsJesús Saracho Aguirre0% (1)

- Commencement of A StatuteDocument110 pagesCommencement of A StatutePrasun Tiwari80% (10)

- People vs Solayao ruling on admission of homemade firearm evidenceDocument1 pagePeople vs Solayao ruling on admission of homemade firearm evidenceMaria Victoria Dela TorreNo ratings yet

- Recorte Apis 1Document35 pagesRecorte Apis 1ENZO SEBASTIAN GARCIA ANDRADENo ratings yet

- International Aviation Safety Assessment Assessor’s ChecklistDocument23 pagesInternational Aviation Safety Assessment Assessor’s ChecklistViktor HuertaNo ratings yet

- Trust Deed Foreclosure ChecklistDocument40 pagesTrust Deed Foreclosure Checklistautumngrace100% (1)

- Characteristics of SovereigntyDocument9 pagesCharacteristics of SovereigntyVera Mae RigorNo ratings yet

- Organisational StructureDocument2 pagesOrganisational StructureAkshat GargNo ratings yet

- A Study On Maintenance Under Muslim Law: Haridharan SDocument10 pagesA Study On Maintenance Under Muslim Law: Haridharan SSaurabh YadavNo ratings yet

- Mutual Fund Industry Study - Final BEDocument45 pagesMutual Fund Industry Study - Final BEPrerna KhoslaNo ratings yet

- Aaaa RTM DIAMOND PDFDocument49 pagesAaaa RTM DIAMOND PDFMaphosa Nhlapo100% (4)

- Proposed Rule: Income Taxes: Partnership Equity For ServicesDocument9 pagesProposed Rule: Income Taxes: Partnership Equity For ServicesJustia.comNo ratings yet

- IAS 27: Consolidated andDocument31 pagesIAS 27: Consolidated andashiakas8273No ratings yet