Professional Documents

Culture Documents

Direct Memory Access o DMA

Uploaded by

George AlexisCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Direct Memory Access o DMA

Uploaded by

George AlexisCopyright:

Available Formats

(Direct Memory Access o DMA).

El acceso directo a memoria es una caractersticas de las computadoras y microprocesadores modernos que permite que ciertos subsistemas de hardware dentro de la computadora puedan acceder a la memoria del sistema para la lectura y/o escritura, independientemente de la unidad central de procesamiento (CPU). De lo contrario, la CPU tendra que copiar cada porcin de dato desde el origen hacia el destino, haciendo que sta no est disponible para otras tareas. Los subsistemas de hardware que utilizan DMA pueden ser: controladores de disco duro, tarjetas grficas, tarjetas de red, tarjetas de sonido y tarjetas aceleradoras. Tambin es utilizado para la transferencia de datos dentro del chip en procesadores con mltiples ncleos. DMA es esencial en los sistemas integrados. Caractersticas generales del DMA Aquellas computadoras que tienen canales DMA pueden transferir datos desde y hacia los dispositivos con menos utilizacin de CPU que aquellas computadoras sin canales DMA. Bsicamente una transferencia DMA consiste en copiar un bloque de memoria de un dispositivo a otro. Esa transferencia se lleva a cabo por el controlador DMA, en lugar del CPU. El controlador DMA es generalmente un chipset de la placa madre. En computadoras sin DMA, el CPU generalmente se ocupa completo durante toda la operacin de lectura o escritura de la memoria y, por lo tanto, no est disponible para realizar otras tareas. Con DMA, el CPU puede iniciar la transferencia, luego realizar otras operaciones mientras la transferencia est en progreso y luego recibir una interrupcin del controlador de DMA una vez que la transferencia termina. Sin DMA se utiliza el modo PIO para la comunicacin de perifricos con la memoria y de instrucciones de load/store en el caso de chips con multincleos. DMA es til en aplicaciones en tiempo real y en el procesamiento de flujos de datos. Tipos de transferencia DMA o Acceso directo a memoria * DMA por robo de ciclo: es uno de los mtodos ms usados, ya que requiere poca utilizacin del CPU. Esta estrategia utiliza uno o ms ciclos de CPU para cada instruccin que se ejecuta. Esto permite alta disponibilidad del bus del sistema para la CPU, aunque la transferencia de datos se har ms lentamente. * DMA por rfagas: esta estrategia consiste en enviar el bloque de datos solicitado mediante una rfaga empleando el bus del sistema hasta finalizar la transferencia. Permite una altsima velocidad, pero la CPU no podr utilizar el bus de sistema durante el tiempo de transferencia, por lo que permanece inactiva. * DMA transparente: esta estrategia consiste en emplear el bus del sistema cuando la CPU no lo necesita. Esto permite que la transferencia no impida que la CPU utilice el bus del sistema; pero la velocidad de transferencia es la ms baja posible. * DMA Scatter-gather: esta estrategia permite transmitir datos a varias reas de memoria en una transaccin DMA simple. Equivale al encadenamiento de mltiples peticiones DMA

simples. Su objetivo es librar a la CPU la tarea de la copia de datos e interrupciones de entrada/salida mltiples. url = http://www.alegsa.com.ar/Dic/acceso%20directo%20a%20memoria.php

OTRA FUENTE: TECNOLOGICO DE ESTUDIOS SUPERIORES DE ECATEPEC (arquitectura de computadores) http://tese.edu.mx/tese2010/ (AADO SOLO LAS COSAS NUEVAS) CONTROLADOR DMA DMA, del ingls Direct Memory Access) permite a cierto tipo de componentes de ordenador acceder a la memoria del sistema para leer o escribir independientemente de la CPU principal. DMA es una caracterstica esencial en todos los ordenadores modernos, ya que permite a dispositivos de diferentes velocidades comunicarse sin someter a la CPU a una carga masiva de interrupciones.

SECUENCIA DE EVENTOS Una operacin de E/S por DMA se establece ejecutando una corta rutina de inicializacin. Consiste en varias instrucciones de salida para asignar valores iniciales a: AR: Direccion de memoria de la regin de datos de E/S (buffer de entrada/salida). WC: Nmero N de palabras de datos a transferir. IOBUF

Una vez inicializado, el DMA procede a transferir datos entre IOBUF y el dispositivo de E/S. Se realiza una transferencia cuando el dispositivo de E/S solicite una operacin de DMA a travs de la lnea de peticin del DMAC. Despus de cada transferencia, se decrementa el valor de WC y se incrementa el de AR. La operacin termina cuando WC=0, entonces el DMAC (o el perifrico) indica la conclusin de la operacin enviando al procesador una peticin de interrupcin.

OTRA FUENTE ESTA ES LA MAS DETALLADA

ACCESO DIRECTO A MEMORIA INCONVENIENTES DE LA E/S PROGRAMADAS Y CON INTERRUPCIONES La E/S con interrupciones, aunque mas eficiente que la sencilla E/S programada, requiere la intervencin activa del procesador para transferir datos entre la memoria y el modulo de E/S y cualquier transferencia de datos que debe seguir un camino a travs del procesador. INCONVENIENTES: La velocidad de transferencia de E/S esta limitada por la velocidad a la cual el procesador puede comprobar y dar servicio a un dispositivo. El procesador debe dedicarse a la gestin de la transferencia de E/S; se debe ejecutar cierto nmero de instrucciones por cada transferencia de E/S. FUNCIONAMIENTO DEL DMA El DMA requiere un mdulo adicional en el bus del sistema. Este es capaz de imitar al procesador y de recibir el control del sistema cedido por el procesador.

Necesita dicho control para transferir datos a, y desde memoria a travs del bus del sistema. Para hacerlo, el mdulo DMA debe utilizar el bus slo cuando el procesador no lo necesita, o debe forzar al procesador a que suspenda temporalmente su funcionamiento. Esta tcnica es la ms comn y se denomina robo de ciclo, puesto que el mdulo DMA roba un ciclo de bus.

Cuando el procesador desea leer o escribir un bloque de datos, enva una orden al mdulo de DMA, incluyendo la siguiente informacin. Si se solicita una lectura o escritura, utilizando la lnea de control de lectura o escritura entre el procesador y el mdulo DMA. La direccin del dispositivo de E/S en cuestin, indicada a travs de las lneas de datos. La posicin inicial de memoria a partir de donde se lee o se escribe, indicada a travs de la lneas de datos y almacenada por el mdulo de DMA en su registro de direcciones. El numero de palabras a leer o escribir, tambin indicado a travs de las lneas de datos y almacenando en el registro de cuenta de datos.

PUNTOS DE RUPTURA PARA EL DMA Y LAS INTERRUPCIONES EN UN CICLO DE INSTRUCCIN El mdulo de DMA transfiere el bloque completo de datos, palabra a palabra directamente desde o hacia, la memoria, sin que tenga que pasar a travs del procesador. Cuando a terminado la transferencia, el mdulo DMA enva una seal de interrupcin al procesador; pues este solo interviene al comienzo y al final de la transferencia. Nos muestra en que momento del ciclo de instruccin puede detenerse el procesador.

CONFIGURACIONES ALTERNATIVAS El DMA puede configurarse de diversas formas: nico Bus, DMA independiente Todos los mdulos comparten el mismo bus del sistema. El mdulo DMA , actuando como un procesador suplementario utiliza E/S programada para intercambiar datos entre la memoria y un modulo de E/S a travs de un mdulo DMA. Esta configuracin, si bien es la ms econmica, es claramente ineficiente, igual que con las e/s programadas controlada por el procesador , la transferencia de cada palabra consume dos ciclos de bus.

Bus nico, DMA-E/S integrados El numero de ciclos de bus necesarios puede reducirse sustancialmente si se integra las funciones de DMA y de E/S Existe un camino entre el mdulo de DMA y uno o mas mdulos de E/S que no incluye al bus del sistema. La lgica de DMA puede ser parte de un mdulo de E/S o puede ser un modulo separado que controla a uno o ms mdulos de E/S.

BUS DE E/S Los puntos anteriores se los lleva algo ms lejos conectando los mdulos de E/S a un modulo de DMA mediante un bus de E/S. Esto reduce a uno el nmero de interfaces de E/S en el modulo DMA , permite una configuracin fcilmente ampliable.

En todos estos casos, el bus del sistema, que el mdulo DMA comparte con el procesador y la memoria, es usado por el mdulo de DMA slo para intercambiar datos con la memoria . Este intercambio de datos entre los mdulos de DMA y E/S se produce fuera del bus del sistema. http://www.slideshare.net/imburguan/acceso-directo-a-memoria?from=fblanding

You might also like

- Trabajo Sobre Los Controladores DMADocument5 pagesTrabajo Sobre Los Controladores DMAVictor ManuelNo ratings yet

- 4.7 Servicios de La Gestión de MemoriaDocument4 pages4.7 Servicios de La Gestión de MemoriaMiguel Quispe CruzadaNo ratings yet

- 10 11sistemas DistribuidosDocument13 pages10 11sistemas Distribuidoschristian merchanNo ratings yet

- 1-Algoritmo de Dijkstra. Un Tutorial InteractivoDocument5 pages1-Algoritmo de Dijkstra. Un Tutorial Interactivojuanle_12No ratings yet

- Las Métricas de Complejidad de HalsteadDocument3 pagesLas Métricas de Complejidad de HalsteadJavier TrujilloNo ratings yet

- Minería de Datos Aplicada A La Evaluación Docente. Caso Práctico UniandesDocument16 pagesMinería de Datos Aplicada A La Evaluación Docente. Caso Práctico UniandesCarlos MartinezNo ratings yet

- Análisis del proyecto de softwareDocument32 pagesAnálisis del proyecto de softwareSergio Saucedo100% (2)

- Mapa Conceptual Arquitectura Del HarvardDocument1 pageMapa Conceptual Arquitectura Del HarvardDeny Martinez AzpeitiaNo ratings yet

- Práctica 1.1. Evolución de Las Aplicaciones WebDocument2 pagesPráctica 1.1. Evolución de Las Aplicaciones WebDeivid's ProduccionesNo ratings yet

- Preguntas de ProgramacionDocument4 pagesPreguntas de ProgramacioncochauefsfaNo ratings yet

- Sistemas de Informacion TransaccionalesDocument12 pagesSistemas de Informacion TransaccionaleskamenkazeNo ratings yet

- Diseño de La Interfaz de UsuarioDocument14 pagesDiseño de La Interfaz de UsuarioCarlos CalatayudNo ratings yet

- Cableado estructurado guía SENADocument19 pagesCableado estructurado guía SENADokkoDaniVargasNo ratings yet

- Arquitectura de SoftwareDocument22 pagesArquitectura de SoftwareNoelia Iquize BaldelomarNo ratings yet

- Procesador AMD Athlon XPDocument9 pagesProcesador AMD Athlon XPAlexis GabrielNo ratings yet

- Investigación-Unidad-2 Ing de Software-DisenoDocument19 pagesInvestigación-Unidad-2 Ing de Software-Disenodarka lolNo ratings yet

- Jerarquia de ArchivosDocument127 pagesJerarquia de Archivospokemon196No ratings yet

- ACA 1 - Investigacion Ciencia y TecnologiaDocument6 pagesACA 1 - Investigacion Ciencia y TecnologiaJAIRO ANDRES GOMEZ CUASPUDNo ratings yet

- Introduccion A Base de Datos AccessDocument20 pagesIntroduccion A Base de Datos AccessCristian BarríaNo ratings yet

- Proyecto Integral de Fundamentos de Base de DatosDocument2 pagesProyecto Integral de Fundamentos de Base de Datossevchenko17No ratings yet

- Desarrollo Adaptativo de SoftwareDocument7 pagesDesarrollo Adaptativo de SoftwareMarcos Guadalupe Hoyo MataNo ratings yet

- Programacion de Circuitos Combinacionales Con HDLDocument11 pagesProgramacion de Circuitos Combinacionales Con HDLTaz Hernandez De0% (2)

- AA3 Estructura de DatosDocument23 pagesAA3 Estructura de DatosDavid HernandezNo ratings yet

- Manual Basico de Mantenimiento Preventivo y Correctivo (Jean)Document70 pagesManual Basico de Mantenimiento Preventivo y Correctivo (Jean)Lissett Yuruani Lobo PalaciosNo ratings yet

- Roger Caamal Santiago Unidad6 Fundamentos de Base de Datos-.Isc j4Document31 pagesRoger Caamal Santiago Unidad6 Fundamentos de Base de Datos-.Isc j4Roger CaamalNo ratings yet

- EXPO Herramientas CaseDocument30 pagesEXPO Herramientas CaseKriptza GomezNo ratings yet

- FORMATO HOJA DE VIDA NASA CXHACXHA (1) DianaDocument4 pagesFORMATO HOJA DE VIDA NASA CXHACXHA (1) DianaDianita PerdomoNo ratings yet

- Sistemas Distribuidos CoordinaciónDocument12 pagesSistemas Distribuidos CoordinaciónSergio GonzalezNo ratings yet

- Ventajas y Desventajas de 3 SGBDDocument3 pagesVentajas y Desventajas de 3 SGBDOsvaldo BorreroNo ratings yet

- 2.7 Los Canales de EntradaDocument4 pages2.7 Los Canales de EntradaDiego NavaNo ratings yet

- Retos Actuales Del Ingeniero InformáticoDocument9 pagesRetos Actuales Del Ingeniero InformáticoAlan J Mast SantNo ratings yet

- 4 - Herramientas Case 1Document8 pages4 - Herramientas Case 1SAYARUG57No ratings yet

- Esquema de Conexión de Un Data CenterDocument20 pagesEsquema de Conexión de Un Data CenterStewart Segura GutarraNo ratings yet

- Bitácora 06 (Calculadora Rmi)Document10 pagesBitácora 06 (Calculadora Rmi)Ronal Farroñan ValderaNo ratings yet

- Cuadro ComparativoDocument3 pagesCuadro ComparativoFernando Rios Roman100% (1)

- Ensayo Base de Datos OOs V02 - DgualeDocument7 pagesEnsayo Base de Datos OOs V02 - DgualedolferguNo ratings yet

- Actividad Final Unidad 4 y 5Document6 pagesActividad Final Unidad 4 y 5Zamuel CastilloNo ratings yet

- Algoritmos - Diseño EstructuradoDocument151 pagesAlgoritmos - Diseño EstructuradoJuan Sebastian Mejia RinconNo ratings yet

- Modelos Proceso SoftwareDocument6 pagesModelos Proceso SoftwareBenjamín EscobarNo ratings yet

- Capa de Transporte Del Modelo TCP PDFDocument24 pagesCapa de Transporte Del Modelo TCP PDFJulieta García Da RosaNo ratings yet

- Cuadro ComparativoDocument5 pagesCuadro ComparativoAlfredo Avendaño SerranoNo ratings yet

- Tarea 6 Modelos ArquitectónicosDocument6 pagesTarea 6 Modelos ArquitectónicosLily GuamanticaNo ratings yet

- Calidad TI UTM México Conceptual Mapa ComparativoDocument3 pagesCalidad TI UTM México Conceptual Mapa ComparativoeffrainnNo ratings yet

- Diseño y análisis de una red para satisfacer las necesidades del usuarioDocument4 pagesDiseño y análisis de una red para satisfacer las necesidades del usuarioDisa AgAgNo ratings yet

- Aplicaciones Distribuidas GpsDocument5 pagesAplicaciones Distribuidas GpsEnrique ÁlvarezNo ratings yet

- Arquitectura Orientada A ServiciosDocument3 pagesArquitectura Orientada A ServiciosMarisol Triple SNo ratings yet

- Consultas SQL y cursoresDocument8 pagesConsultas SQL y cursoresAngel Luis Tovar PazNo ratings yet

- Escalabilidad de Redes WanDocument17 pagesEscalabilidad de Redes WanYessenia Ramos MartinezNo ratings yet

- Características de Diseño de Una RedDocument16 pagesCaracterísticas de Diseño de Una RedGeorge Luis0% (1)

- Redes de Comunicaciones ConmutadasDocument5 pagesRedes de Comunicaciones ConmutadasJoselin QuijijeNo ratings yet

- Ensayo BdooDocument5 pagesEnsayo BdooAldair Martinez LujanNo ratings yet

- Integracion de Aplicaciones DistribuidasDocument13 pagesIntegracion de Aplicaciones DistribuidasCarlos HernandezNo ratings yet

- TP3 Relevamiento y RequerimientosDocument6 pagesTP3 Relevamiento y RequerimientosInteligencia Artificial UnamNo ratings yet

- Cuadro Comparativo Modelos de Calidad de SoftwareDocument4 pagesCuadro Comparativo Modelos de Calidad de SoftwareSergio Camilo Alacon Granados0% (1)

- Mecanismos de Recuperacion de La SGBDDocument3 pagesMecanismos de Recuperacion de La SGBDCarlosCoutiñoNo ratings yet

- Configuración y autenticación del protocolo PPP enDocument7 pagesConfiguración y autenticación del protocolo PPP enNubia Manchay RomeroNo ratings yet

- Sesion04 Arreglo de ObjetosDocument12 pagesSesion04 Arreglo de Objetosepintado15No ratings yet

- Capas Del Software de eDocument4 pagesCapas Del Software de eYenifer Boscan100% (1)

- Acceso Directo A La MemoriaDocument5 pagesAcceso Directo A La MemoriaGalindo Molle CarlosNo ratings yet

- Prácticas de redes de datos e industrialesFrom EverandPrácticas de redes de datos e industrialesRating: 4 out of 5 stars4/5 (5)

- Ejercicios TEMA6 SsooDocument4 pagesEjercicios TEMA6 SsooDaniel GallegoNo ratings yet

- Taller 1 Flex SimDocument48 pagesTaller 1 Flex Simcascarita25% (4)

- Aplicaciones en El Plano de Viviendas: SketchupDocument110 pagesAplicaciones en El Plano de Viviendas: Sketchupgianella alfaro leonNo ratings yet

- STEP 7 - Funciones de Sistema y Funciones Estándar para El TI-S7-ConverterDocument106 pagesSTEP 7 - Funciones de Sistema y Funciones Estándar para El TI-S7-ConverterMartin Gomez Lopez0% (1)

- Tecnologías para El Desarrollo de Aplicaciones WebDocument6 pagesTecnologías para El Desarrollo de Aplicaciones WebcahecazNo ratings yet

- 3.1 Posicionamiento en Buscadores - SEODocument27 pages3.1 Posicionamiento en Buscadores - SEOxdpablo328No ratings yet

- 4.1.4.5 Packet Tracer - Configuring and Verifying A Small Network InstructionsDocument3 pages4.1.4.5 Packet Tracer - Configuring and Verifying A Small Network Instructionsdavid662No ratings yet

- Solemne 1 - 1900 - PautaDocument7 pagesSolemne 1 - 1900 - PautaDiego SepulvedaNo ratings yet

- Escáner de puertos SuperScan y FPort: características y usoDocument10 pagesEscáner de puertos SuperScan y FPort: características y usoSantiago Lopez GonzalzNo ratings yet

- Trabajo Final EstadisticaDocument5 pagesTrabajo Final EstadisticaAlandmrNo ratings yet

- Generaciones de ComputadorDocument14 pagesGeneraciones de ComputadorCésar José Eliud LozadaNo ratings yet

- Especialidad INFORMÁTICA, Scouts VenezuelaDocument10 pagesEspecialidad INFORMÁTICA, Scouts VenezuelaAlfonzo AlbaricoqueNo ratings yet

- Manual PL-SQL EspañolDocument166 pagesManual PL-SQL EspañolAprender Libre100% (1)

- Linux Magazine 11Document53 pagesLinux Magazine 11ian salinas100% (13)

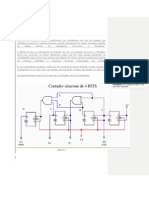

- Contadores síncronos (paralelosDocument11 pagesContadores síncronos (paralelosWilliams Molina EspirituNo ratings yet

- Microprocesador 8087Document10 pagesMicroprocesador 8087javierromualdosantosNo ratings yet

- Mi Granito de Java Patrones Parte 1Document19 pagesMi Granito de Java Patrones Parte 1Henry FayolNo ratings yet

- Tema2 Ecuaciones Exponenciales y Logaritmicas-SistemasDocument25 pagesTema2 Ecuaciones Exponenciales y Logaritmicas-SistemasdaguiNo ratings yet

- Descripción de Las Diferencias Entre Los Tipos de DatosDocument2 pagesDescripción de Las Diferencias Entre Los Tipos de DatosFranciscaValdésNo ratings yet

- Intro VPNDocument10 pagesIntro VPNleadrosfNo ratings yet

- Balanceadores de CargaDocument8 pagesBalanceadores de CargaPolaco FerrariNo ratings yet

- Convocatoria Recibidor Pagador Tiempo Completo 58 Plazas 03062016Document1 pageConvocatoria Recibidor Pagador Tiempo Completo 58 Plazas 03062016lucasNo ratings yet

- Axxon NextDocument18 pagesAxxon NextYanisaSilvaNo ratings yet

- RegNotas 02332880 20 F02019 B31302 28616Document5 pagesRegNotas 02332880 20 F02019 B31302 28616JavierParionaCardenasNo ratings yet

- Cracking de AplicacionesDocument26 pagesCracking de AplicacionesMax TutorialesNo ratings yet

- Sistemas ExpertosDocument4 pagesSistemas ExpertosCamilo EsquivelNo ratings yet

- Protocolos para acceso recursos compartidos SMB/CIFS y NFSDocument23 pagesProtocolos para acceso recursos compartidos SMB/CIFS y NFSomaguenoNo ratings yet

- Programação de CLP Siemens Simatic Step7 em Grafcet (Espanhol)Document216 pagesProgramação de CLP Siemens Simatic Step7 em Grafcet (Espanhol)Wellington FabioNo ratings yet

- Mantenimiento CorrectivoDocument3 pagesMantenimiento CorrectivoCarolina TorresNo ratings yet

- KitProg User Guide - PDF 2.ESPAÑOLDocument54 pagesKitProg User Guide - PDF 2.ESPAÑOLJuancarlos ArrietaNo ratings yet