Professional Documents

Culture Documents

3 Phase AC DC Converter With High Power Factor

Uploaded by

dsistheaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

3 Phase AC DC Converter With High Power Factor

Uploaded by

dsistheaCopyright:

Available Formats

Three-phase AC/DC converter with high power factor

B.-R. Lin and T.-Y. Yang Abstract: The paper presents a three-phase AC/DC converter to achieve power-factor correction, harmonics elimination, DC-bus-voltage regulation and neutral-point-voltage compensation. The proposed converter can achieve bidirectional power-ow capability. Therefore the converter can be applied for active power-lter operation. Two legs are adopted in the proposed converter to achieve three-level pulse-width modulation (PWM) and control the line currents to be sinusoidal waves in phase with supply voltages. Three control loops, DC-link-voltage control, neutral-point-voltage compensation and line current control, were used in the control scheme to achieve DC-bus-voltage regulation, to balance neutral-point voltage and to draw the sinusoidal line currents. The mathematical model of the converter was derived and the control scheme is provided. The effectiveness of the proposed control scheme is veried through computer simulation and experiments.

Introduction

Power pollution owing to the use of power converters results in serious power-quality problems in distribution and transmission systems. Thus, international standards such as IEC 1000-3-2 [1] are dened to restrict the harmonic contents on the AC-source current. Passive power lters were widely used to reduce harmonic currents. However, the main drawbacks of passive lters are xed compensation characteristics, bulk and heavy weight, and series and parallel resonances with the system impedance. Activewave-shaping techniques based on pulse-width-modulated (PWM) schemes have been proposed in [26] to eliminate harmonics and compensate reactive power so that a sinusoidal line current with nearly unity power factor is drawn from the supply voltage. The conventional threephase bidirectional converter is shown in Fig. 1a. Six active switches were used in the converter to achieve power-factor correction, draw sinusoidal line currents from the AC source and obtain a constant DC-link voltage on the DC side. Bipolar PWM voltage waveforms are generated on the AC terminal voltages. However, the series connection of active switches should be adopted in the conventional threephase two-level AC/DC converter for medium- or highvoltage applications. Multilevel converters [7, 8] and inverters [912] adopted series connection of power semiconductors with the low-voltage stress to achieve the medium-voltage applications. Normally, there are some clamped devices in the circuit to generate a multilevel voltage waveform on the AC terminal. These clamped devices can be active switches [8] shown in Fig. 1b, clamped

r IEE, 2005 IEE Proceedings online no. 20045203 doi:10.1049/ip-epa:20045203 Paper rst received 12th July 2004 and in nal revised form 3rd February 2005. Originally published online: 8th April 2005 The authors are with the Power Electronics Research Laboratory, Department of Electrical Engineering, National Yunlin University of Science and Technology, Touliu City, Yunlin 640, Taiwan E-mail: linbr@pine.yuntech.edu.tw IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

diodes [7, 9] shown in Fig. 1c and ying capacitors [9] shown in Fig. 1d. Sixteen active switches, two capacitors and three boost inductors are used in the switch-clamped converter shown Fig. 1b. Three boost inverters, 16 active switches, six clamped diodes and two capacitors are adopted in the diode-clamped converter shown in Fig. 1c. For the capacitor-clamped converter shown in Fig. 1d, 16 switches, three boost inductors and four capacitors are used. The drawbacks of the multilevel converters are a complex control scheme and the need to use large semiconductors in the converters. The use of fewer power semiconductors used in the multilevel converters or inverters is welcome during to design and implement the low-cost products with three-level PWM operation. This paper presents a new three-phase AC/DC converter to achieve power-factor correction, obtain a constant DClink voltage and balance neutral point voltage. Three-phase sinusoidal currents are drawn from the AC source. The proposed AC/DC converter has fewer power semiconductors in the circuit than conventional three-level PWM converters shown in Figs. 1b1d. Two converter legs are used in the circuit to achieve three-level PWM operation. Four active switches are used in each converter leg. Three boost inductors, two capacitors and eight active switches are used in the proposed converter. Two control loops are used in the proposed control scheme. Therefore, the cost of the proposed converter is less than that of a conventional threelevel converter. A hysteresis-based current controller and a proportional-plus-integral-(PI) based voltage controller are used in the inner and outer control loop to achieve current command tracking and DC bus voltage regulation, respectively. 2 Circuit conguration

Figure 2 gives the proposed three-phase AC/DC converter. Three inductors are connected between the AC source and the AC side of the converter. Two split capacitors are used on the DC side to maintain the constant DC-bus voltage and reduce the voltage ripple. The phase c of AC source is directly connected to the midpoint of the split DC capacitors. Two legs are used in the converter to achieve

757

sa sb sc

L, r Ta1 isa L, r isb L, r isc Ta2 a

Tb1 Tc1 b Tb2 a

dc

c Tc2

dc

sa

Rs,Ls

Ta1 a

Tb1 b

Tc1

Ta

ip

p

C1

iL

Rs,Ls sc isb isc Ta2 Tb2

c Tc2

Tb Tc in n

C2

C2

load

R ,L sb isa s s

io C1 o

other where x a, b and y 1, 2. Based on the circuit topology, the voltage stress of power switches Tx2 and Tx2 is equal to half the DC bus voltage and the voltage stress of Tx1 and Tx1 is equal to the DC-link voltage. No clamped diode and ying capacitor is used in the proposed converter compared with the neutral-point-clamped (NPC) converter and ying-capacitor converter. Two independent power switches Tx1 and Tx2 (x a, b) are adopted in each converter leg to generate three different voltage levels on the AC terminal voltages vac and vbc, respectively. A PI-based voltage controller is used in the outer loop to regulate the DC-bus voltage. In the inner control loop, the hysteresisbased current controller is used to achieve line current commands tracking. 3 System analysis

load

b Ta1 isa r, L r, L r, L T'a1 T'a2 T'b1 T' Da2 b2 c i sa sa

sb isb

Da1 Tb1 Tb2 a b

Db1 Tc1 Tc2

Dc1

ip C1

iL

Ta2

sa

sc

isc

o c C2 C2 Dc2 in

T'c1 T'c2 Db2

r, L

Ta1 Ta2

Tb1 Tb2 + Ca a Ca T'b2 T'b1 d

Tc1

Cb +

Tc2

Cc

load

i sb sb

io

C1

It is assumed that all passive elements and power semiconductors in the proposed converter are ideal. The output voltage is assumed constant during one switching period. Four active switches are used in each converter leg. The split DC-side capacitor voltages are assumed to be equal, i.e. vC1 vC2 vdc/2. The proposed three-phase converter can be separated into two subcircuits shown in Fig. 3. In Fig. 3a the line voltage vsac vsavsc is supplied to the AC terminal between converter leg a and neutral point c. The AC terminal voltage vac can be used to control the line current isa. The line voltage vsbc is supplied to AC terminal between converter leg b and neutral point c, as shown in Fig. 3b. The AC terminal voltage vbc is used to control line current isb. Based on the on and off states of

sc

isc

r, L

T'a2 T'a1

c C c

C1

load

r, L

dc

vdc p T a2 2L, 2r isa vsac a C2 T a 1 in n a vdc T b2 load 2L, 2r isb vsbc b C1 Tb1 T b 2 io c vc 1 ip p iL T a1 T a 2 io c vC2 ip C1 iL v

bC b T'c2 T'c1

C1

Fig. 1

Conventional three-phase AC/DC converter

a Two-level topology b Three-level switch-clamped topology c Three-level capacitor-clamped topology d Three-level diode-clamped topology

vdc

vsa vsb mv

sc

L, r isa L, r isb L, r isc T a 1 Ta 1

Ta2 T a2 a Tb 1

Tb2 T b2

ip C1 io

p i L vC 1

c b T b 1 in vC 2 n

leg a

leg b C2 vc 2 n T b 1 in

Fig. 2 ters

Proposed reduced-switch-count three-level AC/DC conver-

three-level PWM operation on the AC side, regulate the DC-bus voltage and draw sinusoidal line currents from the AC source. Four active switches are used in each converter leg. Power switches Txy and T0 xy are complementary each

758

Fig. 3

Two subcircuits of the proposed converter

a Converter leg-a b Converter leg-b

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

load

load

vdc Ta2 2L, 2r isa vsac a T a1 T a1 T a 2 load io c ip C1 p iL vC1

C2 in n

vC 2

to obtain AC-terminal voltage vac 0 and DC-side current ip in 0. Line current isa increases (or decreases) in this state if the line voltage vsac is positive (or negative). Figure 4c shows the third operating state in the leg a. Switch T0a1 is turned on and AC the terminal voltage vac vC2 vdc/2. The DC-side current in isa. Since the boost inductor voltage is positive, line current isa increases in this operating state. The same approach can be used to analysis three operating states in the converter leg b and to control line current isb. Based on the switching states of the proposed converter shown in Table 1, the AC-terminal voltages and DC-side currents can be expressed as:

0 vac Ta1 Ta2 vC1 Ta1 vC2

1 2 3 4 5

a vdc Ta2 2L, 2r C1 isa vsac T a1 T2 a load io a T a1 c ip p iL

0 vbc Tb1 Tb2 vC1 Tb1 vC2

ip Ta1 Ta2 isa Tb1 Tb2 isb

0 0 in Ta1 isa Tb1 isb 0 0 io Ta1 Ta2 isa Tb1 Tb2 isb isc

vC1

C2 in n

vC 2

b vdc Ta2 2L, 2r C1 isa vsac T a1 T2 a load io ip p iL vC1

a

T a1

C2 in n

vC 2

Fig. 4

a State 1 b State 2 c State 3

Three valid operating states in converter leg a

where vC1 and vC2 are capacitor voltages of C1 and C2 respectively, ip, io and in are DC-side currents owing into the points p, c and n respectively. If two capacitor voltages vC1 and vC2 are equal, three voltage levels (vdc/2, 0 and vdc/ 2) are generated on the AC-terminal voltages vac and vbc, and ve different voltage levels (vdc, vdc/2, 0, vdc/2, and vdc) are generated on the voltage vab. The rst and second states are selected during the positive line voltage in order to generate two voltage levels vdc/2 and 0 on the AC terminal to neutral point and to control line current. On the other hand, the second and third operating states are selected during the negative line voltage to generate voltage levels 0 and vdc/2 on the AC terminal to the neutral point and to control line current. The balance three-phase voltages are supplied from the AC source. Therefore the sum of instantaneous three-phase voltages is zero. According to the KVL analysis on the AC side of the converter, the system behavior of the converter can be expressed as disa t fvsa t risa t vac vcm g=L dt & ' 2vac t vbc t vsa t risa t =L 3 3 ' & 2vac t vbc t =L % vsa t 6 3 3 disb t fvsb t risb t vbc vcm g=L dt & ' 2vbc t vac t vsb t risb t =L 3 3 & ' 2vbc t vac t =L vsb t 3 3

power switches, there are three valid switching states in each converter leg, as shown in Fig. 4. Two legs are used in the proposed converter, the total number of valid switching states in the proposed converter are nine (32 9). Table 1 shows nine switching states, the corresponding AC terminal voltages and DC side currents. Figure 4a gives the equivalent circuit of the rst operating state. Switches Ta1 and Ta2 are turned on to achieve the AC-side voltage vac vC1 vdc/2 and the DC-side current ip isa. The positive line current isa will charge capacitor C1. The voltage across the inductor L is negative because each DC-side capacitor voltage is greater then line voltage (vdc/24vsac and vsbc) so that line current isa decreases in this operating state. Figure 4b shows the equivalent circuit of the second operating state. Active switches Ta1 and T0a2 are turned on

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

where vac and vbc are AC-side-to-neutral-point-voltages, isa and isb are line currents, and r and L are series equivalent resistance and inductance of the boost inductor. The KCL equations on the DC side of the converter can be given as dvC1 dvC2 ip iL ; C 2 in iL 8 C1 dt dt where C1 and C2 are DC-side capacitors, and iL is the load current on the DC bus. Figure 5 shows the equivalent circuit of the proposed converter based on (1)(8). Computer simulation of the proposed converter can be

759

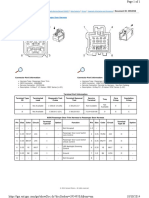

Table 1: Possible switching states of the proposed converter

Switching signals State 1 2 3 4 5 6 7 8 9 Ta1 1 1 1 1 1 1 0 0 0 Ta2 1 1 1 0 0 0 X X X Tb1 1 1 0 1 1 0 1 1 0 Tb2 1 0 X 1 0 X 1 0 X AC-side voltages Vac VC1 VC1 VC1 0 0 0 vC2 vC2 vC2 vbc vC1 0 vC2 VC1 0 vC2 VC1 0 vC2 vab 0 vC1 vdc /2 vdc vC1 vdc /2 0 VC2 vdc /2 vdc vC2 vdc /2 0 DC-side currents ip isa+isb isa isa isb 0 0 isb 0 0 in 0 0 isb 0 0 isb isa isa isa isb

Assume vC1 vC2 vdc /2; X: dont care

vsa

isa

r, L vac + ip io in iL p + vC 1 c +v C2 n

vsb n vsc

isb

r, L

isc

r, L

vbc

where Kp and Ki are the proportional and integral gains of the voltage controller, respectively. A unit sinusoidal waveform generator is used in the control scheme to obtain the balanced and sinusoidal waveforms in phase with ACsource voltages. These two sinusoidal reference waveforms are expressed as ' ua t sinot 10 ub t sinot 2p=3 Based on (9) and (10), the generated line currents of phases a and b from the outer voltage-control loop are expressed as isa t Is ua t Is sinot isb t Is ub t Is sinot 2p=3 11 12

Fig. 5

Equivalent circuit of the proposed converter

obtained using the circuit model in Fig. 5 to draw the sinusoidal line currents with low harmonic content from the AC source and to regulate the DC bus voltage. 4 Control scheme

load

Four control goals will be achieved in the proposed control scheme: (a) The AC/DC converter draws sinusoidal line currents with low current distortion from the AC source. (b) The input power factor is close to unity. (c) The DC-link voltage is equal to the desired voltage value (d) The neutral point voltage is compensated. Figure 6 gives block diagrams of the proposed control scheme. To obtain the amplitude of the line current command and keep the DC-link voltage constant, a proportional-plus-integral (PI) voltage controller is used in the outer loop. First, the DC-bus voltage vdc is measured and compared with the DC-link voltage command v* . The dc voltage error Dvdc v* vdc is sent to the PI voltage dc controller to obtain the amplitude of line current command: Z 9 Is Kp vdc vdc Ki v vdc dt dc

If the neutral-point voltage is unbalanced in the proposed converter, a neutral-point-voltage compensator based on a proportional gain is used to balance the neutral-point voltage. A small direct current from the neutral point compensator is added to the output of the DC-link-voltage controller. To suppress the effect of DC bus-voltage ripple on the output of the neutral-point voltage compensator. A low-pass lter is adopted to obtain the average capacitor voltages VC1 and VC2. A current limiter is added on the output of the neutral-point voltage compensator to avoid three-phase unbalanced currents from the AC source. Therefore current commands for phases a and b are given as i t isa t KVC2 VC1 sa i t isb t KVC2 VC1 sb 13 14

Hysteresis current comparators are used in the inner loop to track line current commands. Line currents isa and isb are measured and compared with the reference line currents i* sa

VC2 + vdc + vdc vsavsc VC1 PI

limiter isa Is isa + + isb + + i + isb i sa sa i + i sb sb vsac + + hys (isa ) hys (isb ) sign(vsac ) sign(vsbc ) PWM generator Ta1 T a1 Ta 2 T a 2 Tb1 T b1 Tb 2 T b 2

sin (t) PLL circuit sin (t - 2 /3) vsbc

Fig. 6

760

Block diagram of the control scheme

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

Table 2: PWM signals for each converter leg

sign(vsxc) 1 1 0 0 hys(Disx) 1 0 1 0 x a, b; X: dont care Operating state 2 1 3 2 Tx1 1 1 0 1 Tx2 0 1 X 0

vsa isa Ta1 0

Ta2 signvsac f1 hysDisa g

16

0

Tb1 signvsbc f1 signvsbc gf1 hysDisb g 17 Tb2 signvsbc f1 hysDisb g where signvsxc & hysDisx & 1; ifvsxc 40 0; ifvsxc o0 18

Ta2

vac

19 20

1; ifDisx 4h 0; ifDisx o h

5 ms a vsb isb Tb1 0 20 A 200 V vbc 0 5 ms b

and x a, b, and h is a hysteresis-current band. During the positive line voltage vsac, the power switch Ta1 is turned on and Ta1 is turned off. The operating states 1 (Ta2 turns on) and 2 (Ta2 turns off) are used to control line current and to generate AC side voltage vac vdc/2 and 0, respectively. During the negative line voltage vsac, the power switch Ta2 is turned off. The operating states 2 (Ta1 turns on) and 3 (Ta1 turns off) are used to control line current and generate AC side voltage vac 0 and -vdc/2, respectively. Owing to the derived PWM signals in each converter leg, three voltage levels are generated for the AC terminal voltages vac and vbc and ve voltage levels are given for the voltage vab. Three sinusoidal line currents with nearly unity power factor are drawn from the AC source. The DC-bus voltage equals the desired voltage value. The neutral-point voltage is compensated in the proposed control scheme. 5 Simulation and experimental results

Tb 2

Fig. 7 Simulation results of mains voltage, line current and PWM signals

a Converter leg a b Converter leg b

761

The effectiveness of the proposed converter was veried through computer simulation and experiments. The

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

400 V

20 V 20 V

400 V

20 V

20 V 20 A 200 V

and i* . Line current errors Disa and Disb are sent to sb hysteresis comparators to generate the proper PWM signals for active switches in each converter leg. Three operating states can be selected in each converter leg. The rst operating state can be selected to generate the AC terminal voltage vac vdc/2 and to decrease the line current isa. The second operating state is selected to obtain AC terminal voltage vac 0 and to increase or decrease the line current if the line voltage is positive or negative, respectively. The third operating state is used to the increase line current and generate a low-voltage level vac vdc/2 at the AC terminal. Therefore the rst and second operating states in each converter leg can be selected to control line current during the positive line voltages vsac and vsbc. The second and third operating states are adopted during the positive line voltages to control line current. If the sign of the line voltage and the output of the hysteresis-current comparator are given, then the PWM signals for active switches can be generated. Table 2 gives the relationship between the detected signals and the corresponding PWM signals. Based on Table 2, the derived PWM signals are expressed as Ta1 signvsac f1 signvsac gf1 hysDisa g 15

computer-software package MATLAB/SIMULINK was used in the adopted system to draw the balanced sinusoidal line currents from the AC source, to maintain a constant DC link voltage and to achieve power-factor correction. The circuit parameters of the adopted converter in the simulation are: line voltage 220 VRMS, line frequency 60 Hz, L 2 mH, r 0.1 O, C1 C2 1100 mF, and vC1 vC2 400 V. The hysteresis-current band is equal to 0.5A. Figure 7 shows the simulated results of phase voltage, current and PWM signals in each converter leg. Figure 8 shows the simulated results of three-phase voltages and currents in the rectication and inversion operations. In the rectier the mode, the three-phase line currents are in phase with the phase voltage. In the inverter mode, the power factor of line current is nearly negative unity. Figure 9 shows the simulated results of three AC-terminal voltages. Three voltage levels are generated for the AC-terminal voltages vac and vbc and ve voltage levels are achieved for the voltage vab. Figure 10 gives the simulated results of two DC-side capacitor voltages. These two capacitor voltages are almost balanced. A scale-down laboratory prototype circuit was implemented to verify the performance of the adopted system. The circuit parameters and the system specications in the experimental prototype are: line voltage: 110VRMS/60 Hz, L 1 mH, r 0.1 O, C1 C2 1100 mF, vC1 vC2 200 V, and hysteresis band: 0.5 A. A digital signal processor

v sa

v sb

v sc 50 V 10 V 5 ms vsa isa Ta1 Ta 2 5 ms 10 V 10 V vC 1 400 V

isa

isb

isc

10 A

vC 2 400 V

(vC 1 vC 2 ) 0V 5 ms a v sa v sb v sc 50 V

Fig. 10

Simulation results of split DC capacitor voltages

10 A

isa

isb

isc 3

Fig. 8

Simulation results of three-phase voltages and currents

a

a Rectication mode b Inversion mode

vsb 400 V

vac 0

isb

Tb1 vbc 0 400 V 3 Tb2

5 ms 800 V vab 0 4

Fig. 9 Simulation results of AC terminal voltages in the proposed converter

Fig. 11 Experimental results of mains voltage, line current and PWM signals

a Converter leg a b Converter leg b vsa, vsb: 50 V/division isa, isb: 10 A/division Ta1, Ta2, Tb1, Tb2: 10 V/division Time: 5 ms/division

(TMS320C32) was adopted as the kernel in the implementation of a digital controller. Since eight switches are used in the converter, eight gate drive circuits with isolated DC sources were implemented to drive active switches. Figure 11 shows the experimental waveforms of the source voltage, current and PWM signals for converter legs a and b. The line currents are almost in phase with the source voltages, respectively. Figure 12 shows the experimental

762

waveforms of source voltage vsa and AC-terminal voltages. Three voltage levels vdc/2, 0 and vdc/2 are generated for the voltages vac and vbc, and ve voltage levels vdc, vdc/2, 0, vdc/

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

vsa 1 1

vac 2

vbc 3 vab

vsa vsb vsc

4 isa isb isc

Fig. 12 Experimental results of AC terminal voltage of the proposed converter

vs: 100 V/division vac, vbc, vab : 400 V/division Time: 5 ms/division

7

vsa

isa

2 and vdc are achieved for the voltage vab. Figure 13a gives the experimental waveforms of three-phase voltages and line currents under the rectication and inversion operations. Three sinusoidal line currents are drawn from the AC source. Tables 3 and 4 shows the measured power factor and total harmonic distortion for the different output powers. Based on the measured results at the rated power of 1.5 kW, the total harmonic distortion of line current is 3.5% and power factor of AC source is 0.992. Figure 13b gives the measured waveforms of mains voltages and line currents under the inversion mode. The line current is phase shifted 1801 with respect to source voltage. Figure 14 shows the harmonic components of line current isa. The maximum harmonic current in phase a is fth order of line frequency. The fth-harmonic current is 3.3% of the fundamental current. The measured waveforms of the capacitor voltages and voltage variation are shown in Fig. 15. The voltage variation between two capacitor voltages is about 5 V. The split DC-bus capacitor voltages are almost balanced. Figure 16 shows the dynamic response of the DC-link voltage and three-phase line currents from 700 W to 1350 W. The settling time of the DC bus voltage is about three cycles of the AC source. The voltage drop due to load change is about 10 V. Based on the simulation and experimental results, sinusoidal line currents with nearly unity power factor are drawn from the AC source. 6 Conclusion

vsb

isb

vsc

isc

Fig. 13 Experimental results for three-phase voltages and line currents

a Rectication mode b Inversion mode vsaBvsc: 100 V/division isaBisc: 10 A/division Time: 10 ms/division

Table 3: Measured power factor of the proposed converter under the different output powers

Output 100 power (W) Power factor 0.98 300 500 800 1100 1350

0.99

0.99

0.991

0.991

0.992

This paper presents a new three-phase AC/DC converter with power-factor correction. Two converter legs were used in the proposed circuit to draw the sinusoidal line currents from the AC source. Eight active switches and two split DC capacitors are used in the converter to achieve three-level PWM operation. The proposed AC/DC converter has fewer power semiconductors than conventional three-phase three-level AC/DC converters. Three control loops were used in the control scheme to achieve power factor correction, DC bus-voltage-regulation and neutral-point voltage-balance. Bidirectional power ow can be achieved in the proposed converter. Simulation and experimental results were presented to verify the effectiveness of the

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

Table 4: Measured THD of the proposed converter under the different output powers

Output power (W) Total harmonic distortion (%) 100 300 500 800 1100 1350

8.3

6.4

4.6

4.2

3.7

3.5

adopted control scheme. The proposed converter can be applied to AC motor drive systems, UPS and active power lters.

763

3.30% 2.97% 2.64% 2.31% i i sa,n sa,1 1.98% 1.65% 1.32% 0.99% 0.66% 0.33% 0% 2 4 6 8 10 12 14 16 18 20 22 24

harmonic magnitude as a% of the fundamental amplitude

Fig. 14

Measured harmonic components of line current isa

200 V

vC 2 200 V

(vC 1 vC 2 ) 3

400 V

vC 1

vdc

isaisc

Fig. 15

Experimental results of split DC capacitor voltages

Fig. 16 Experimental results of the proposed converter from 700 W to a 350 W

isaBisc: 5 A/division vdc: 20 V/division Time: 20 ms/division

(vc1, vc2, vc1 Dvc2): 5 V/division Time: 10 ms/division

References

1 IEC 61 1000-3-2: Electromagnetic compatability. Limits. Limits for harmonic current emissions (equipment input current r16A per phase), 2004. 2 Zhang, R., Lee, F.C., Boroyevich, D., and Mao, H.: New high power, high performance power converter systems, IEEE Trans., 2000, PE-15, (3), pp. 456463 3 Ho, Y.K.E., Hui, S.Y.R., and Lee, Y.-S.: Characterization of single-stage three-phase power-factor-correction circuit using modular single-phase PWM DC-to-DC converters, IEEE Trans., 2000, PE-15, (1), pp. 6271 4 Stankovic, A.V., and Lipo, T.A.: A novel control method for input output harmonic elimination of the PWM boost type rectier under unbalanced operating conditions, IEEE Trans., 2001, PE-16, (5), pp. 603611 5 Malinowski, M., Jasinski, M., and Kazmierkowski, M.P.: Simple direct power control of three-phase PWM rectier using space-vector modulation (DPC-SVM), IEEE Trans., 2004, IE-51, (2), pp. 447454 6 Ledezma, E., McGrath, B., Munoz, A., and Lipo, T.A.: Dual ACdrive system with a reduced switch count, IEEE Trans., 2001, IA-37, (5), pp. 13251333

7 Lin, B.-R., and Wei, T.-C.: Analysis and implementation of a threephase two-leg neutral point clamped converter based on space vector PWM for power factor correction, IEE Proc. Electric Power Applications, 2004, 151, (1), pp. 3846 8 Qiao, C., and Smedley, K.: Three-phase unity power factor star connected switch (VIENNA) rectier with unied constantfrequency integration control, IEEE Trans, 2003, PE-18, (4), pp. 952957 9 Rodriguez, J., Lai, J.-S., and Peng, F.Z.: Multilevel inverters: a survey of topologies, controls, and applications, IEEE Trans, 2002, IE-49, (4), pp. 724738 10 Pou, J., Pindado, R., Boroyevich, D., and Rodriguez, P.: Limits of the neutral-point balance in back-to-back-connected three-level converters, IEEE Trans., 2004, PE-19, (3), pp. 722731 11 Visser, A.J., Enslin, J.H.R., and Mouton, H.: Transformerless series sag compensation with a cascaded multilevel inverter, IEEE Trans., 2002, IE-49, (4), pp. 824831 12 Tourkhani, F., Viarouge, P., and Meynard, T.A.: A simulationoptimization system for the optimal design of a multilevel inverter, IEEE Trans., 1999, PE-14, (6), pp. 10371045

764

IEE Proc.-Electr. Power Appl., Vol. 152, No. 3, May 2005

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Quality ManualDocument34 pagesQuality Manualchao gao100% (9)

- CH 3 Revision Worksheet 2 Class 6 CSDocument1 pageCH 3 Revision Worksheet 2 Class 6 CSShreyank SinghNo ratings yet

- War As I Knew ItDocument2 pagesWar As I Knew ItShreyansNo ratings yet

- Eastern Bank Limited: Name: ID: American International University of Bangladesh Course Name: Faculty Name: Due DateDocument6 pagesEastern Bank Limited: Name: ID: American International University of Bangladesh Course Name: Faculty Name: Due DateTasheen MahabubNo ratings yet

- On The Backward Problem For Parabolic Equations With MemoryDocument19 pagesOn The Backward Problem For Parabolic Equations With MemorykamranNo ratings yet

- Stress and Strain - Axial LoadingDocument18 pagesStress and Strain - Axial LoadingClackfuik12No ratings yet

- Non-Hazardous Areas Adjustable Pressure Switch: 6900P - Piston SensorDocument2 pagesNon-Hazardous Areas Adjustable Pressure Switch: 6900P - Piston SensorDiana ArredondoNo ratings yet

- MAS-02 Cost Terms, Concepts and BehaviorDocument4 pagesMAS-02 Cost Terms, Concepts and BehaviorMichael BaguyoNo ratings yet

- VKC Group of Companies Industry ProfileDocument5 pagesVKC Group of Companies Industry ProfilePavithraPramodNo ratings yet

- Personal Information: Witec Smaranda 11, A3 Bis, Blvd. Chisinau, Bucharest, Romania 0040722597553Document6 pagesPersonal Information: Witec Smaranda 11, A3 Bis, Blvd. Chisinau, Bucharest, Romania 0040722597553MirelaRoșcaNo ratings yet

- 25 - Marketing Channels - Value Networks.Document2 pages25 - Marketing Channels - Value Networks.zakavision100% (1)

- Dolby Atmos Specifications PDFDocument24 pagesDolby Atmos Specifications PDFVanya ValdovinosNo ratings yet

- Upload 1 Document To Download: Ergen DedaDocument3 pagesUpload 1 Document To Download: Ergen DedakNo ratings yet

- Shear Wall Design PDFDocument9 pagesShear Wall Design PDFjk.dasgupta100% (2)

- EE FlowchartDocument1 pageEE Flowchartgoogley71No ratings yet

- Document 20Document3 pagesDocument 20api-586815209No ratings yet

- Mitsubishi Forklift Fg30nm Service ManualDocument22 pagesMitsubishi Forklift Fg30nm Service Manualbridgetsilva030690rqd100% (130)

- X606 PDFDocument1 pageX606 PDFDany OrioliNo ratings yet

- About UPSC Civil Service Examination Schedule and Subject ListDocument4 pagesAbout UPSC Civil Service Examination Schedule and Subject Listjaythakar8887No ratings yet

- ShinojDocument4 pagesShinojArish BallanaNo ratings yet

- Second Division: Republic of The Philippines Court of Tax Appeals Quezon CityDocument8 pagesSecond Division: Republic of The Philippines Court of Tax Appeals Quezon CityCamille CastilloNo ratings yet

- Curriculum Vitae H R VijayDocument8 pagesCurriculum Vitae H R VijayvijaygowdabdvtNo ratings yet

- PraxiarDocument8 pagesPraxiara_roy003No ratings yet

- UNECE-Turkey-TCDO-Rail Freight Traffic in Euro-Asian LinksDocument20 pagesUNECE-Turkey-TCDO-Rail Freight Traffic in Euro-Asian LinksArseneNo ratings yet

- Unit 8 - Week 7: Assignment 7Document3 pagesUnit 8 - Week 7: Assignment 7Nitin MoreNo ratings yet

- Guide On Multiple RegressionDocument29 pagesGuide On Multiple RegressionLucyl MendozaNo ratings yet

- Note 2958296 Pre-Implementation Steps: Create Table TypeDocument3 pagesNote 2958296 Pre-Implementation Steps: Create Table Typevishnu900890No ratings yet

- Maths VIII FA4Document3 pagesMaths VIII FA4BGTM 1988No ratings yet

- Wilcox - Umn - 0130E - 12886 - Competency RevisedDocument160 pagesWilcox - Umn - 0130E - 12886 - Competency RevisedShasteen Bautista SantosNo ratings yet

- OMS - Kangaroo Mother CareDocument54 pagesOMS - Kangaroo Mother CareocrissNo ratings yet